За последние годы в области вычислительной техники произошли существенные изменения

| Вид материала | Лекция |

- А. В. Воронин ПетрГУ, г. Петрозаводск За последние годы в лесопромышленном комплексе, 48.78kb.

- Информатизация образовательного учреждения, 20.47kb.

- «Материаловедение», 378.79kb.

- Закупочная логистика содержание, 151.07kb.

- Тема: «Система складирования в логистической системе», 157.07kb.

- Гильдия Управляющих Документацией, о задача, 36.6kb.

- Общественное мнение о деятельности судебных и правоохранительных органов в Республике, 79.71kb.

- Уважаемые участники семинара, коллеги, 137.99kb.

- Программа дисциплины по кафедре Вычислительной техники микропроцессорные системы, 464.96kb.

- Программа дисциплины по кафедре Вычислительной техники Теория автоматов, 406.16kb.

7.1. ОБЩИЕ ПОНЯТИЯ, ТЕРМИНЫ И ХАРАКТЕРИСТИКИ

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими частями вычислительной машины или системы. Их можно классифицировать по роли в системе и механическому исполнению.

В зависимости от назначения ЗУ можно разделить на три крупных класса:

- внутренняя память;

- буферная память;

- внешняя память.

Устройства внутренней памяти непосредственно участвуют в процессе преобразования информации, обмениваясь данными с процессором ЭВМ или вычислительной системы.

Внешняя память содержит большие массивы информации, хранит их в течение длительного времени и обменивается данными с внутренней памятью.

Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью.

По способу записи и считывания информации все ЗУ можно разделить на следующие типы:

- оперативные запоминающие устройства (ОЗУ), которые относятся к внутренней памяти и предназначены для хранения данных, участвующих в текущих вычислениях. В связи с этим, быстродействие ОЗУ во многом определяет скорость работы ЭВМ. В зависимости от способа построения ячейки памяти (ЯП) ОЗУ подразделяются на статические и динамические схемы памяти. Ниже будет подробно изложено различие между указанными подтипами схем памяти.

- постоянные запоминающие устройства (ПЗУ) предназначены для хранения программ, констант, таблиц элементарных функций и т.д. В свою очередь, по способу записи информации они подразделяются на:

- масочные, информация в которые записывается в процессе производства;

- однократно программируемые или прожигаемые (ППЗУ), запись информации в которые осуществляется путем пережигания плавких перемычек, изготовленных, как правило, из тугоплавких металлов;

- многократно программируемые или репрограммируемые с ультрафиолетовым стиранием информации (РППЗУ);

- многократно программируемые с электрическим стиранием (ЭСППЗУ).

К основным техническим характеристикам ЗУ относятся:

- емкость или максимально возможный объем хранимой информации. Емкость ЗУ обычно измеряют в Кбитах (1024 бита);

- организация ЗУ - количество и разрядность хранимых слов. Например, указание емкости ЗУ в виде 8Кх8 означает, что в ЗУ емкостью 64 Кбит хранится 8 К слов по 8 разрядов;

- быстродействие ЗУ оценивается временем считывания, записи и обращения. Временем считывания называется интервал времени между появлением сигнала считывания и моментом появления информации на выходе. Аналогично, временем записи называют время от момента появления сигнала записи до ее завершения. Обращением к ЗУ называют операцию, в результате которой происходит считывание или запись информации. Временем обращения является интервал между двумя последовательными обращениями к ЗУ.

7.2. МИКРОСХЕМЫ ПЗУ

В настоящее время выпускается значительное количество различных типов ПЗУ, емкость которых лежит в пределах от десятков бит до нескольких Мбит, время выборки - от десятков нс до сотен нс и шириной выборки, обычно равной байту или полубайту.

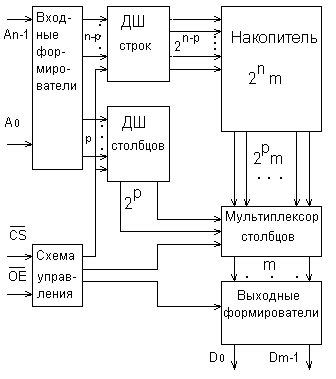

Подавляющее большинство ПЗУ строятся по структурной схеме, приведенной на рис. 7.1.

Рисунок 7.1. Структурная схема ПЗУ с комбинированной выборкой

Выходные формирователи преобразуют адресный код, поступающий на входы А0...Аn-1 во внутренние сигналы управления, которые подаются на дешифраторы строк и столбцов (ДШ Ст) и (ДШ Столб). Дешифратор строк возбуждает одну из 2n-p строк, к которой может быть подключено до 2p ячеек памяти (ЯП). В зависимости от типа запоминающего элемента, используемого в ЯП, на вход мультиплексора столбцов поступает либо логические “0”, либо логические “1”. Дешифратор столбцов вырабатывает адресный код одного из 2p столбца и мультиплексор передает на выходные формирователи информацию, записанную в выбранную ЯП. Как правило, запись информации в накопитель означает подключение или отключение запоминающего элемента от шины строки. Выходные формирователи служат для преобразования внутренних логических сигналов в стандартные логические уровни, чаще всего типа ТТЛ. Схема управления позволяет перевести внутренние блоки ПЗУ в режим малого потребления тока и выходные формирователи - в третье состояние или лог. “1” (для выходов типа ОК).

В масочных ПЗУ программирование состоит в изготовлении или неизготовлении элемента связи между строкой и ЯП. Выпуск таких микросхем ПЗУ экономически целесообразен только при значительных объемах производства, т.е. только тогда, когда аппаратура, где используются такие ПЗУ прошла стадию опытной эксплуатации.

Наибольший интерес для разработчиков аппаратуры представляют микросхемы ПЗУ программируемые в условиях потребителя.

В табл. 7.1. приведены основные параметры широко используемых на практике однократно программируемых ПЗУ серии 556.

Таблица 7.1. Параметры ППЗУ серии 556

| Тип ИС | Зарубежный аналог | Емкость бит | Время выборки, нс | Ток потреб., мA | Тип выхода | Исходное состоян. выхода |

| 556РТ4 556РТ5 556РТ7 556РТ11 556РТ17 556РТ18 155РЕ3 | 3601 3604 S82S191 93427С 3624A HM777661-5 N8223B | 256х4 512х4 2Кх8 256х4 512х8 2Кх8 32х8 | 70 70 80 45 50 60 50 | 130 190 200 130 175 180 110 | ОК ОК ТС ТС ТС ТС ОК | 0 1 0 0 1 0 0 |

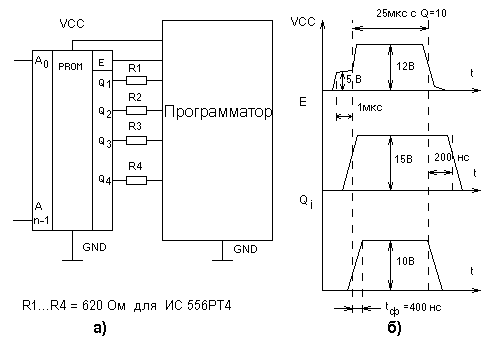

На рис.7.2, в качестве примера, показана схема подключения ППЗУ К556РТ4 к программатору и временные диаграммы основных сигналов в режиме программирования.

Рисунок 7.2. Схема подключения ППЗУ к программатору (а) и временные диаграммы сигналов в режиме программирования (б).

Для программирования ППЗУ в схему вводятся специальные формирователи (на структурной схеме рис.7.1. не показаны), которые позволяют создать импульсы тока, пережигающие плавкие перемычки. При программировании ПЗУ на выходы, вход управления CS и вывод питания подаются импульсы напряжения, фиксированной длительности и амплитуды от программатора. Адрес пережигаемой перемычки определяется кодом, поданным на адресные входы А0...Аn-1. В одном цикле можно программировать только один разряд, а контроль программирования осуществляется после каждого цикла.

РППЗУ (EPROM - Erasable Programmable Read Only Memory) представляют собой самый распространенный в последнее время тип программируемых ПЗУ. Все содержимое памяти таких ПЗУ можно стереть с помощью ультрофиолетового (УФ) излучения. Для этого в корпусе микросхемы имеется окно, закрытое кварцевым стеклом, через которое проходит УФ излучение. Длительность стирания равна 30 мин при длине волны 400 нм и энергетической освещенности 100 Вт/м2. Обычно используются кварцевые лампы ДРТ-220 и ДРТ 375. После этого микросхема может быть снова запрограммирована. Допустимое число циклов перепрограммирования зависит от типа ЯП и составляет от нескольких десятков до десятков тысяч. Как правило в ЯП микросхем РППЗУ используются МОП транзисторы, имеющие структуру металл - нитрид - окисел - полупроводник (МНОП) или “плавающий” затвор.

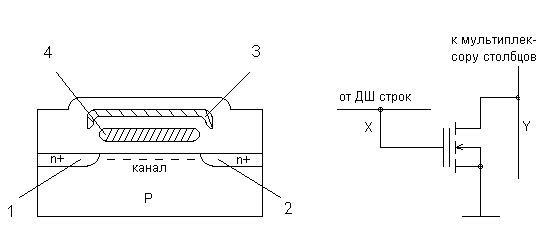

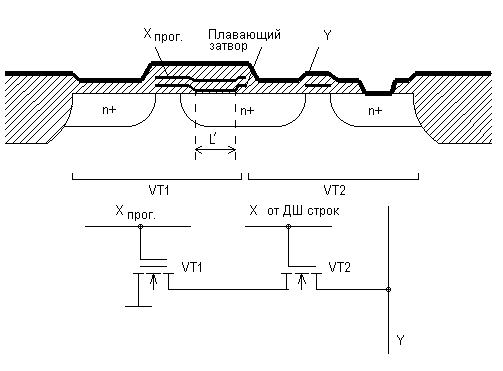

На рис. 7.3 показана структура и электрическая схема ЯП.

Рисунок 7.3. Структура и электрическая схема ЯП РППЗУ.

РППЗУ. Область 1 является истоком транзистора и одновременно частью общей шины, проходящей в направлении перпендикулярно чертежу. Сток 2 соединен с металлической шиной столбца. Два затвора транзистора выполнены из сильно легированного поликремния (т.е. имеют низкое сопротивление). Верхний затвор 3 - управляющий, совмещен с шиной строки, нижний 4, предназначен для хранения заряда, - “плавающий”. Толщина окисла между плавающим затвором и подложкой, с одной стороны, и управляющим затвором - с другой, составляет 0.02....0.04 мкм, длина канала 1...2 мкм.

В случае хранения логической “1” на плавающем затворе существует отрицательный заряд электронов и пороговое напряжение по управляющему затвору Uпор1 получается высоким (несколько вольт). Если хранится логический “0”, то заряд на плавающем затворе равен нулю или положителен, тогда пороговое напряжение Uпор0 низкое (или даже отрицательное). Разность пороговых напряжений связана с величиной заряда: Uпор1 - Uпор0 = Q/Cд , где Cд = ee0S/d - емкость между затвором управления и подложкой; S - площадь затвора; d - суммарная толщина диэлектрика между двумя затворами и между плавающим затвором и подложкой. Так как токи утечки диэлектрика ничтожно малы, то время хранения, являющееся важнейшим параметром элемента памяти, большое. По оценкам оно превышает 10 лет при повышенной температуре, когда токи утечки максимальны.

В режиме считывания на выбранную строку поступает напряжение, лежащее в пределах Uпор0... Uпор1, а на остальные строки - напряжение меньшее, чем Uпор0. В выбранной строке транзисторы будут открыты или закрыты, в зависимости от хранимой информации. Следовательно, в столбце, к которому подключен транзистор с низким порогом (Uпор0) будет протекать ток, а в столбцах, к которым подключены транзисторы с записанной “1” - ток будет отсутствовать. Эта разница улавливается усилителем считывания и передается на выходные формирователи.

В режиме программирования напряжение на шине выбранного столбца устанавливается высоким (Uyпрог ~ 10В), если необходимо записать логическую “1”. В противном случае, Uyпрог = 0. Напряжение на шине выбранной строки также устанавливается высоким, причем Uxпрог > Uyпрог. Программирование основано на инжекции горячих электронов в окисел у стокового конца канала. Так как напряжение на управляющем затворе выше, чем на стоке, в диэлектрике существует вертикальная составляющая вектора напряженности электрического поля, благодаря которой инжектированные в окисел электроны дрейфуют к плавающему затвору и накапливаются на нем. Ток через диэлектрик очень мал (единицы микроампер), поэтому время программирования одной ЯП весьма велико. Режимы работы микросхем РППЗУ иллюстрирует табл. 7.2.

Таблица 7.2. Режимы работы РППЗУ

| Режим работы | Выводы микросхемы | |||||

| A |  |  | PR | UPR | D | |

| Хранение Считывание Запрет выхода Программирование (запись) Запрет программирования Подтверждение записи | X A A A A A | H L L L H L | X L H H H L | X H H L L H | UCC UCC UCC UPR UPR UPR | Z D Z D D D |

Примечание. В табл. 7.2 знаками H и L обозначены высокий и низкий уровни напряжения, соответственно; Z - высокоимпедансное состояние выхода.

Сигнал

осуществляет выбор микросхемы. Если на этот вход подан высокий уровень напряжения, то микросхема находится в режиме пониженного потребления мощности. Высокий уровень на входе

осуществляет выбор микросхемы. Если на этот вход подан высокий уровень напряжения, то микросхема находится в режиме пониженного потребления мощности. Высокий уровень на входе  переводит выходы микросхемы в третье состояние, но не в режим малого потребления.

переводит выходы микросхемы в третье состояние, но не в режим малого потребления.В режиме программирования на вход

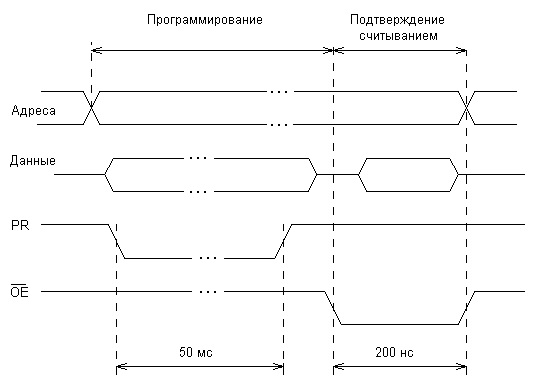

подается низкий уровень напряжения. К дополнительному выводу UPR прикладывается напряжение программирования (указывается на корпусе микросхемы, обычно 21 или 12 В). Адрес ЯП, в которую будет производиться запись, задается с помощью сигналов, подаваемых на выводы А0...Аn, а записываемые данные подаются на выходы D0...Dm. Запись информации осуществляется по низкому уровню сигнала PR, длительность которого должна быть не менее 50мс (рис. 7.4).

подается низкий уровень напряжения. К дополнительному выводу UPR прикладывается напряжение программирования (указывается на корпусе микросхемы, обычно 21 или 12 В). Адрес ЯП, в которую будет производиться запись, задается с помощью сигналов, подаваемых на выводы А0...Аn, а записываемые данные подаются на выходы D0...Dm. Запись информации осуществляется по низкому уровню сигнала PR, длительность которого должна быть не менее 50мс (рис. 7.4).

Рисунок 7.4 Временная диаграмма работы РППЗУ в режимах программирования и контрольного считывания.

После стирания УФ излучением содержимое всех ЯП равно “1”. В режиме программирования, определенные заранее биты слова переводятся из состояния “1” в “0”. После этого производится цикл контрольного считывания записанной информации (по низкому уровню сигнала

), в котором сравнивается информация, считанная из ПЗУ, с контрольными данными. Запись информации в РППЗУ осуществляется пословно.

), в котором сравнивается информация, считанная из ПЗУ, с контрольными данными. Запись информации в РППЗУ осуществляется пословно.Для записи 8К слов указанным способом необходимо 6 мин 40с, а на запись 32К слов - 26 мин 40сек. Для сокращения времени программирования почти в 5 раз фирма Intel предложила другой способ записи, суть которого кратко можно сформулировать следующим образом:

1. Установить UPR = 21В, UCC = 6В.

2. Осуществляется запись в течении 1 мс и производится контроль записанных данных.

3. Если запись прошла, то переходим к следующему слову, иначе повторяем 2.

4. Если запись повторялась N раз, осуществить дополнительную запись, длительностью 4N мс.

5. Установить UPR = 5,0В, UCC = 5,0В.

6. Осуществить считывание и подтверждение всех данных. Обычно второй этап заканчивается при N=2, поэтому среднее время записи составляет 10 мс.

Основные параметры отечественных БИС РППЗУ приведены в табл. 7.3

Таблица 7.3. Основные параметры отечественных РППЗУ

| Тип РППЗУ | Организация | Время выборки, нс | Потребляемая мощность в режиме обращен./хранения | Напряжение питания /программирования |

| К573РФ2 К573РФ4 К573РФ7 К573РФ8 К573РФ10 К1626РФ1 | 2Кґ8 8Кґ8 32Кґ8 32Кґ8 2Кґ8 8Кґ8 | 450 300 350 350 450 200 | 580/200 400 600/200 500/150 150/15 150/5 | 5/25 5/21 5/12,5 5/12,5 5/21 5/12,5 |

Еще больший интерес для разработчиков аппаратуры представляют ЭСППЗУ, которые обладают следующими возможностями:

1. Стирание и запись информации в рабочем состоянии устройства, смонтированного на плате.

2. Пословное стирание и запись информации.

По сравнению со считыванием, стирание и запись осуществляются медленнее и требуют ~ 10мс.

Процессы программирования и считывания в этих элементах протекает также, как и в рассмотренных выше элементах РППЗУ. Однако основаны они на тунельном эффекте. На рис.7.5. приведена структура и электрическая схема ЯП ЭСППЗУ.

Рисунок 7.5 Структура и электрическая схема ЯП ЭСППЗУ.

Левую часть структуры образует транзистор с плавающем затвором (VT1). Слой диэлектрика, ограниченный зоной L' и отделяющий плавающий затвор от стока VT1, имеет очень малую толщину - порядка 10 нм (тунельно-тонкий диэлектрик). При программировании на шину Хпрогвыбранной строки подают высокое напряжение (20В). Если на плавающий затвор надо ввести заряд (запрограммировать лог. “1”), то на стоке надо установить нулевое напряжение. В этом случае происходит тунелирование электронов на плавающий затвор. Если же надо записать “0”, то на стоке устанавливают такое же напряжение, как и на управляющем электроде. Для стирания (удаления заряда) на управляющий затвор необходимо подать нулевое напряжение, а на сток - высокое. Тогда электроны совершают обратный переход - с плавающего затвора на сток.

Транзистор VT2 предназначен для программирования только выбранных строк. В невыбранных строках транзистор VT2 закрыт, тем самым исключается попадание высокого напряжения на стоки остальных транзисторов.

Достоинством рассмотренного элемента является возможность стирания информации в произвольной ЯП. Причем время программирования мало (` 1 мс), а количество циклов перепрограммирования составляет 105. Площадь же такого элемента памяти в 3-4 раза больше, чем у ЯП РППЗУ (30-40 литографических единиц в квадрате), поэтому информационная емкость микросхем ПЗУ во столько же раз меньше.

Основные параметры отечественных БИС ЭСППЗУ приведены в табл. 7.4. Следует отметить, что отечественные БИС ЭСППЗУ значительно уступают по своим параметрам лучшим зарубежным аналогам. Так например лучшие зарубежные образцы (микросхемы фирм Seeq, Atmel и др.) имеют информационную емкость > 1 Мбит, время выборки менее 30 нс при потребляемой мощности 100 ... 200 мВт.

Таблица 7.4. Основные параметры отечественных ЭСППЗУ

| Тип ЭСППЗУ | Организация | Время выборки, нс | Потребляемая мощность в режиме обращения/хранения | Напряжение питания/программирования |

| К1601РР1 K1601PP3 К1611РР1 К1624РР1 К1801РР1 К1609РР1 К573РР1 К1609РР3 | 1Кґ8 2Кґ8 8Кґ8 32Кґ8 4Кґ8 2Кґ8 8Кґ8 8Кґ8 | 1800 1600 300 400 550 350 300 250 | 625/300 850/400 600/300 420/105 450/225 600/300 200/30 550/225 | 5/-12 5/-12 5/21 5/24 5/24;18 5/21 5/5 5/21 |

7.3. МИКРОСХЕМЫ ОЗУ

Микросхемы ОЗУ предназначены для записи и хранения данных, непосредственно участвующих в процессе вычислений, и являются основой для построения сверхоперативной памяти ЭВМ, кэш памяти и блоков основной оперативной памяти. Как известно ОЗУ подразделяются на статические и динамические. Наибольшее распространение получили микросхемы динамической памяти (ДОЗУ) благодаря своей большой информационной емкости, малой потребляемой мощности и относительно низкой стоимости. Именно на этих микросхемах строится основная оперативная память, емкость которой в ЭВМ даже относительно невысокой производительности может достигать единиц - десятков Мбайт. Перспективным является также использование ДОЗУ для построения буферной памяти большой емкости (до 128 Мбайт и более), расположенной между быстрым процессором и сравнительно медленными накопителями на магнитных дисках.

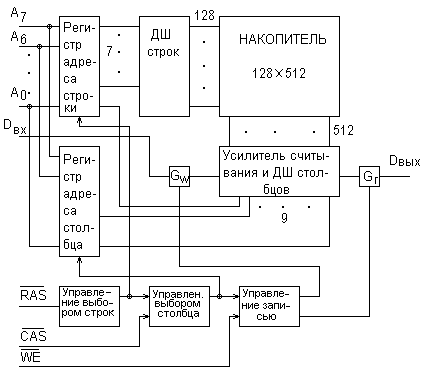

Устройство и принцип работы ДОЗУ рассмотрим на примере БИС К565РУ5, имеющей организацию 64Кґ1, структурная схема которой приведена на рис. 7.6.

Рисунок 7.6. Структурная схема ДОЗУ.

В состав микросхемы входят следующие блоки:

- регистры адреса строки и столбца, предназначенные для приема и хранения адреса выбранной ЯП;

- дешифраторы строк и столбцов, преобразующие адреса во внутренние сигналы управления. Причем ДШ столбцов конструктивно совмещен с усилителями считывания, количество которых равно числу столбцов в накопителе;

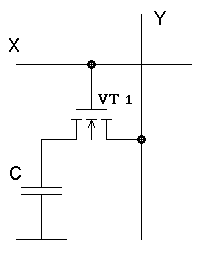

- накопитель, имеющий организацию 128 строк на 512 столбцов, на пересечении которых расположены ЯП. В динамических схемах памяти функцию элемента памяти выполняет специально созданный конденсатор, который подключается к разрядным шинам через транзистор VT1 (рис. 7.7). В такой ЯП информация представляется в виде наличия или отсутствия заряда на конденсаторе. Поскольку время хранения заряда на конденсаторе ограничено в следствии наличия токов утечки, предусматривают периодическое восстановление (регенерацию) состояния конденсатора, а, следовательно, и записанной в него информации.

Рисунок 7.7 Ячейка памяти ДОЗУ.

Запись информации в ЯП производится при одновременной подаче напряжений на адресную X и разрядную Y шины. Напряжение на шине Х открывает транзистор VT1 и конденсатор С либо заряжается, если на шине Y присутствует высокий уровень напряжения, либо разряжается, если на Y низкий уровень. При считывании напряжение высокого уровня подается только на адресную шину Х. При этом конденсатор С через открывшийся транзистор VT1 подключается ко входу усилителя считывания, который представляет собой модифицированный RS триггер. В зависимости от величины заряда, накопленного на конденсаторе, триггер устанавливается либо в одно устойчивое состояние (соответствующее, например, лог. 1), либо в другое. Так как в этот момент параллельно конденсатору С подключается паразитная емкость разрядной шины, то происходит разрушение информации, записанной в ЯП. Это приводит к необходимости после каждого считывания восстанавливать хранящуюся информацию, что в свою очередь увеличивает время цикла обращения к ДОЗУ;

- вентили GW и GR, преобразующие внешние информационные сигналы во внутренние и наоборот;

- блоки управления выбором строк, столбцов и записью.

В зависимости от управляющих сигналов

(ROW ACCESS STROB),

(ROW ACCESS STROB),  (COLUMN ACCES STROB) и

(COLUMN ACCES STROB) и  (WRITE ENABLE) микросхемы ДОЗУ могут работать в следующих основных режимах (см. табл. 7.5): запись, считывание, считывание-модификация-запись, регенерация тактовым сигналом

(WRITE ENABLE) микросхемы ДОЗУ могут работать в следующих основных режимах (см. табл. 7.5): запись, считывание, считывание-модификация-запись, регенерация тактовым сигналом  .

.Таблица 7.5. Таблица истинности ДОЗУ

|  |  | А | Dвх | Dвых | Режим работы |

| H H L L L L | H L H L L L | X X X L L H | X X Перебор адресов A A A | X X X 0 1 X | Z Z Z Z Z D | Хранение Хранение Регенерация Запись “0” Запись “1” Считывание |

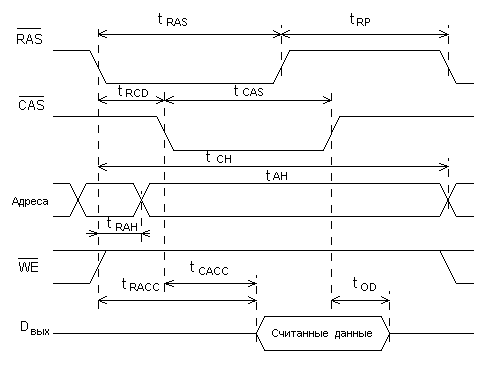

В режиме считывания информации на адресные входы сначала подаются восемь старших бит адреса (А8-А15), которые записываются в регистр адреса строки по низкому уровню сигнала

, а затем подаются младшие восемь бит (А0...А7), которые фиксируются в регистре-защелке адреса столбца сигналом

, а затем подаются младшие восемь бит (А0...А7), которые фиксируются в регистре-защелке адреса столбца сигналом  . Для обеспечения правильной работы ДОЗУ адреса и сигналы

. Для обеспечения правильной работы ДОЗУ адреса и сигналы  и

и  необходимо подавать в строгой последовательности, так как это показано на рис. 7.8, а. Считанные данные появятся на выходе Dвых с задержкой tRACC (tCACC) относительно сигнала

необходимо подавать в строгой последовательности, так как это показано на рис. 7.8, а. Считанные данные появятся на выходе Dвых с задержкой tRACC (tCACC) относительно сигнала  (

( ) и будут удерживаться на нем время tOD после снятия сигнала

) и будут удерживаться на нем время tOD после снятия сигнала  . После окончания считывания при смене старших бит адреса должна быть выдержана пауза tRP, необходимая для восстановления состояния внутренних цепей микросхемы.

. После окончания считывания при смене старших бит адреса должна быть выдержана пауза tRP, необходимая для восстановления состояния внутренних цепей микросхемы.

Рисунок 7.8(а) Временная диаграмма работы ДОЗУ в режиме считывания.

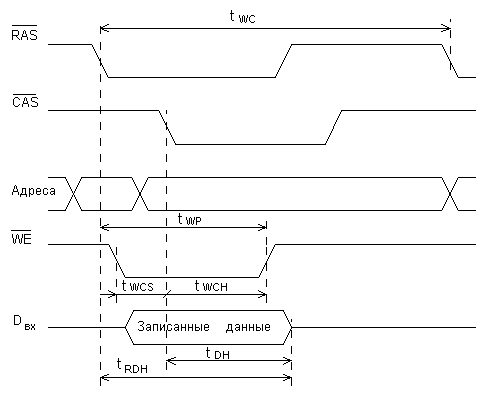

Рисунок 7.8(б) Временная диаграмма работы ДОЗУ в режиме записи.

В режиме записи порядок подачи адресных и управляющих сигналов аналогичен рассмотренному. Сигнал

должен быть подан за определенное время tWCS (рис. 7.8, б) до перехода сигнала

должен быть подан за определенное время tWCS (рис. 7.8, б) до перехода сигнала  на низкий уровень и удерживаться относительно этого перехода также заданное время (tWCH). Данные, также должны удерживаться в течение времени tDH относительно отрицательного фронта сигнала

на низкий уровень и удерживаться относительно этого перехода также заданное время (tWCH). Данные, также должны удерживаться в течение времени tDH относительно отрицательного фронта сигнала  .

.Для обеспечения работы микросхем памяти без сбоев необходимо учитывать длительности импульсов, пауз между ними, взаимный сдвиг во времени. Перечень временных параметров ДОЗУ включает в себя десятки наименований и подробно приводится в справочной литературе.

Как уже отмечалось выше время хранения информации на запоминающем конденсаторе ограничено. Поэтому для надежного сохранения записанной в накопителе информации выполняется режим принудительной регенерации сигналом

. Регенерация осуществляется путем перебора адресов строк в сопровождении каждого адреса сигналом

. Регенерация осуществляется путем перебора адресов строк в сопровождении каждого адреса сигналом  при пассивном состоянии сигнала

при пассивном состоянии сигнала  = 1 за время, не превышающее период регенерации.

= 1 за время, не превышающее период регенерации.Период регенерации ДОЗУ сильно уменьшается с увеличением температуры. До недавнего времени он для большинства серийно выпускаемых микросхем памяти (емкостью до 64 Кбит) не превышал 2 мс при температуре 70°С, а число строк регенерации не превышало 128. В ДОЗУ емкостью 256 Кбит и 1 Мбит период регенерации увеличен до 8 мс при числе строк регенерации 512, а у микросхем памяти емкостью 4 Мбита - до 16 мс при числе строк регенерации 1024.

Помимо перечисленных режимов большинство современных микросхем ДОЗУ могут работать в режиме “страничного” считывания. В этом режиме после записи старшей части адреса в регистр адреса строки, в усилителях считывания запоминается вся информация, содержащаяся в выбранной строке. Если адрес следующего требуемого бита информации отличается от предыдущего только младшей частью, то нет необходимости вновь обновлять содержимое регистра адреса строки, так как требуемый бит уже содержится во внутреннем буфере памяти. Изменяя только младшую часть адреса можно считывать на выход микросхемы содержимое внутреннего буфера, который получил название страницы. В этом случае время обращения к ДОЗУ уменьшается почти в 3 раза, что существенно повышает быстродействие ЭВМ.

В настоящее время отечественные БИС ДОЗУ представлены в основном микросхемами серии К565, основные технические характеристики которых представлены в табл. 7.6. За последние годы емкость микросхем ДОЗУ резко увеличилась и уже сейчас ряд японских фирм (HITACHI, FUJITSU, TOSHIBA) серийно выпускают микросхемы с организацией 4Мґ4, 16Мґ1. Имеются также сообщения об изготовлении экспериментальных образцов БИС памяти емкостью 256 Мбит и даже 1 Гбит.

Таблица 7.6. Основные параметры ДОЗУ

| Тип ДОЗУ | Емкость бит | Время выборки, нс | Время цикла, нс | Период регенерации, мс | Потребляемая мощность, мВт | |

| хранение | обращение | |||||

| К565РУ3Г K565РУ5Б К565РУ7В К565РУ8А К565РУ9Б ТС11000С МВ8141000 | 16К 64К 256К 256К 1М 1М 4М | 200 120 150 100 150 85 80 | 370 230 340 350 200 120 150 | 2 2 8 8 8 8 16 | 40 22 28 - - - - | 460 250 360 370 420 385 350 |

Одним из основных недостатков БИС ДОЗУ является необходимость восстановления информации, что приводит к потерям времени и, соответственно, к снижению производительности ЭВМ. В связи с этим проводятся разработки микросхем, в которых динамическая память совмещена на одном кристалле с устройством регенерации. Такие ДОЗУ с точки зрения пользователя являются статическими, и их называют квазистатическими.

Микросхемы статических ОЗУ (СОЗУ) значительно уступают по информационной емкости БИС ДОЗУ. Однако их значительно более высокое быстродействие и простота применения делают этот тип памяти незаменимым при построении блоков сверхоперативной памяти и кэш памяти.

В зависимости от организации микросхемы СОЗУ подразделяются на одно- и многоразрядные. Многоразрядные схемы позволяют записывать или считывать информацию словами, причем разрядность слова обычно равна байту или полубайту. По способу управления СОЗУ принято делить на асинхронные и тактируемые. Эти различия проявляются в организации временной работы микросхемы, которые будут рассмотрены ниже.

Структуру этих микросхем и принцип работы рассмотрим на примере БИС К537РУ17 с организацией 8Кх8. В состав микросхемы входят: входные формирователи, дешифраторы адреса строк и столбцов, накопитель, схема записи/считывания, устройства ввода/вывода и логика управления. Подавляющее большинство блоков БИС имеют такое же функциональное назначение, что и в микросхемах ПЗУ. Основное отличие СОЗУ от рассмотренных выше схем памяти заключается в принципах построения ЯП.

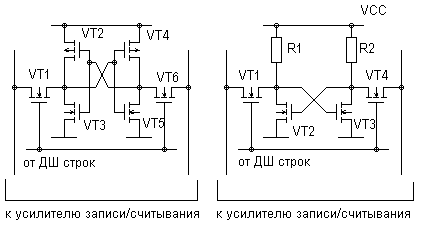

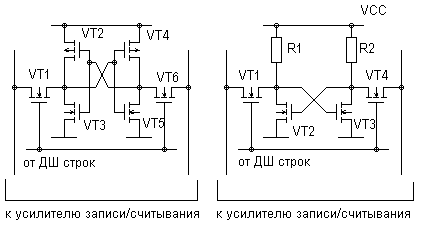

В настоящее время наиболее перспективными являются БИС СОЗУ, выпускаемые по КМОП или Би-КМОП (биполярные и полевые транзисторы на одном кристалле) технологии. В этих микросхемах ЯП представляет собой RS триггер, построенный на двух КМОП инверторах (рис. 7.9, а). Выходы RS триггера подключены к разрядным шинам через проходные транзисторы VT1, VT6. В режиме хранения ДШ строк поддерживает низкий потенциал на шине выборки, проходные транзисторы закрыты и RS триггер сохраняет ранее установленное состояние. При этом ЯП практически не потребляет ток. В режиме выборки потенциал на затворах транзисторов VT1 и VT6 устанавливается выше порогового, что приводит к их отпиранию. Тем самым выходы RS триггера подключаются к разрядным шинам, по которым требуемая информация поступает на входы усилителя считывания и дальше на выход микросхемы. При записи информации усилитель записи в зависимости от поступивших на вход данных формирует на разрядных шинах парафазные сигналы. Через открытые транзисторы VT1 и VT6 эти сигналы поступают на RS триггер, устанавливая его в требуемое состояние. Рассмотренная КМОП ЯП занимает на кристалле БИС в 1,5...2 раза больше площадь, чем n-МОП ЯП. Однако ее существенно меньшая мощность потребления предопределяет выбор в ее пользу.

| а) | б) |

Рисунок 7.9 Электрическая схема ЯП СОЗУ.

Еще меньшую площадь на кристалле занимает ЯП, электрическая схема которой приведена на рис. 7.9, б. В ней нагрузочные транзисторы заменены резисторами, изготовленными из высокоомного поликремния. Последнее позволяет размещать их непосредственно над транзисторами, что приводит к сокращению площади, занимаемой ЯП, в 4 раза по сравнению с КМОП ЯП.

| а) | б) |

Рисунок 7.9 Электрическая схема ЯП СОЗУ.

Режимы работы СОЗУ иллюстрирует табл. 7.7.

Таблица 7.7. Таблица истинности СОЗУ

| CS2 |  |  | А0 - А12 | I/O0 - I/O7 | Режим работы |

| Y L L L L | Y H H H H | X X X L H | X L L H H | X A A A A | Z 0 1 D0- D7 Z | Хранение Запись 0 Запись 1 Считывание Запрет выхода |

Примечание. Y - любая комбинация сигналов

, CS2, за исключением

, CS2, за исключением  =0, CS2=1.

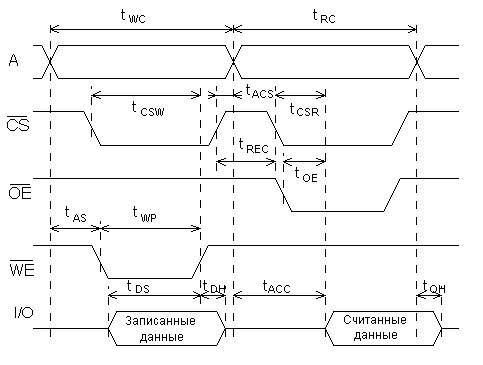

=0, CS2=1.В динамическом режиме работы СОЗУ на подачу адресных, информационных и управляющих сигналов накладываются определенные временные ограничения. При записи информации вначале подают адресный код, затем с некоторой задержкой tAS сигнал записи WE (рис. 7.10). Сигналы выбора кристалла CS должны быть установлены до положительного фронта сигнала WE за время tCSW, а информационные сигналы IO - за время tDS и удерживаться после него время tDH. Для правильной записи длительность низкого уровня сигнала WE должна быть не менее времени tWP, а сигналы CS могут быть сняты не ранее времени tACS до окончания цикла записи. Длительность паузы между двумя соседними сигналами CS не должна быть меньше времени tREC.

Рисунок 7.10 Временная диаграмма работы СОЗУ.

В цикле считывания порядок подачи сигналов сохраняется, но изменяется состояние входов WE и OE. Время появления выходного сигнала определяется параметрами tACC, tOE и tCSR.

Как уже указывалось выше микросхемы СОЗУ подразделяются на асинхронные и тактируемые. В тактируемых ОЗУ необходимо при каждом адресном обращении к микросхеме сигнал CS подавать импульсом, а сигналы записи и разрешения выходов могут иметь форму импульса или уровня напряжения. Это требование обусловлено тем, что переход микросхемы в активное состояние осуществляется только по фронту (положительному или отрицательному) сигнала CS. В асинхронных микросхемах на форму сигналов CS не накладывается никаких ограничений.

Отечественные микросхемы СОЗУ существенно различаются по своим техническим характеристикам и изготавливаются как по биполярной, так и МОП технологиям. В табл. 7.8 приведен состав серий СОЗУ и их основные характеристики.

Таблица 7.8. Основные параметры серий СОЗУ

| Серия | Емкость. бит | Время цикла, нс | Напряжение питания, В | Мощность Вт | Технология |

| К500 K1500 К185 К541 К132 К565 К1809 К537 К1603 К581 К561 К6500 | 16ґ4, 64ґ4 1Kґ1, 4Kґ1 64ґ4, 1Kґ4 4Kґ1, 16Kґ1 64ґ1, 64ґ9 1Kґ4, 4Kґ1 8Kґ1, 16Kґ1 1Kґ1, 1Kґ4, 4Kґ1 4Kґ4, 2Kґ8, 16Kґ1, 64Kґ1 1Kґ1, 1Kґ16 1Kґ1, 1Kґ4, 4Kґ1 2Kґ8, 8Kґ8, 64Kґ1 256ґ4 2Kґ8, 256ґ1, 1Kґ1 | 20...40 6...35 45...500 100...170 55...85 450 880 70...500 790 200 800 4 | -5,2 -4,5 5 5 5 5 5 5 5 6 6...12 4; -2,4 | 0,6...1,1 0,6...1,1 0,4...1,0 0,3...0,5 0,4...0,9 0,4 0,6 0,02...0,4 0,03 0,4 0,15 1,6 | ЭСЛ ЭСЛ ТТЛ ТТЛ n-МОП n-МОП n-МОП КМОП КМОП КМОП КМОП GaAs |

Наиболее развитый функциональный состав имеет серия К537, которая включает в себя более 20 типономиналов микросхем, отличающихся информационной емкостью (от 1024 до 65536 бит), организацией (одноразрядная и словарная), быстродействием (более чем в 5 раз), потребляемой мощностью. Несмотря на большое количество различных типономиналов СОЗУ, выпускаемых у нас в стране, они существенно уступают лучшим зарубежным образцам и прежде всего по быстродействию, у которых время цикла составляет менее 10 нс.

СПИСОК ЛИТЕРАТУРЫ

- Угрюмов Е.П. Проектирование элементов и узлов ЭВМ: Учеб. пособие для спец. ЭВМ вузов.- М.: Высш. шк., 1987.- 318 с.

- Потемкин И.С. Функциональные узлы цифровой автоматики.-М.: Энергоатомиздат, 1988.- 320 с.

- Алексенко А.Г., Шагурин И.И. Микросхемотехника: Учеб. пособие для вузов.- М.: Радио и связь, 1990.- 496 с.

- Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник.- М.: Радио и связь, 1990.- 304 с.

- Цифровые и аналоговые интегральные микросхемы. Справочное пособие/С.В.Якубовский, Л.И.Ниссельсон и др.; Под ред. С.В.Якубовского.- М.: Радио и связь, 1990.- 496 с.

- Шило В.Л. Популярные цифровые микросхемы: Справочник.- М.: Радио и связь, 1987.- 352 с.

- Петровский И.И., Прибыльский А.В. и др. Логические ИС КР1533, КР1554: Справочник.- М.:БИНОМ, 1993.

- Применение интегральных микросхем памяти: Справочник/А.А.Дерюгин, В.В.Цыркин и др.; Под ред. А.Ю.Гордонова, А.А.Дерюгина.- М.: Радио и связь, 1994.- 232 с.

- Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. Микросхемы ЦАП и АЦП: Справочник/О.Н.Лебедев и др.; Под ред. А.И.Ладика и А.И.Сташкевича.- М.: Радио и связь,1994.- 248 с.

- Цифровые интегральные микросхемы: Справочник/ П.П.Мальцев, Н.С.Долидзе и др.- М.: Радио и связь, 1994.- 240 с.