За последние годы в области вычислительной техники произошли существенные изменения

| Вид материала | Лекция |

- А. В. Воронин ПетрГУ, г. Петрозаводск За последние годы в лесопромышленном комплексе, 48.78kb.

- Информатизация образовательного учреждения, 20.47kb.

- «Материаловедение», 378.79kb.

- Закупочная логистика содержание, 151.07kb.

- Тема: «Система складирования в логистической системе», 157.07kb.

- Гильдия Управляющих Документацией, о задача, 36.6kb.

- Общественное мнение о деятельности судебных и правоохранительных органов в Республике, 79.71kb.

- Уважаемые участники семинара, коллеги, 137.99kb.

- Программа дисциплины по кафедре Вычислительной техники микропроцессорные системы, 464.96kb.

- Программа дисциплины по кафедре Вычислительной техники Теория автоматов, 406.16kb.

6.1. ТРИГГЕРЫ. ОСНОВНЫЕ ПОНЯТИЯ И КЛАССИФИКАЦИЯ

Триггеры - элементарные автоматы, содержащие элемент памяти и схемы управления им. При подаче на управляющие входы триггера соответствующих сигналов он устанавливается, как правило, в одно из двух устойчивых состояний, которое сохраняется в течении заданного времени после окончания действия входных сигналов.

Состояние триггера определяется значением выходного сигнала Q на прямом выходе. Обычно триггер имеет и инверсный выход с сигналом

. Стандартные серии ИС содержат большое количество различных триггеров, отличающихся друг от друга способом записи информации, принципом функционирования и т.д. Поэтому технически грамотное применение готовых триггеров зависит от понимания принципов их функционирования и ограничений по входным и управляющим сигналам. Помощь же в этом может оказать их классификация, приведенная ниже.

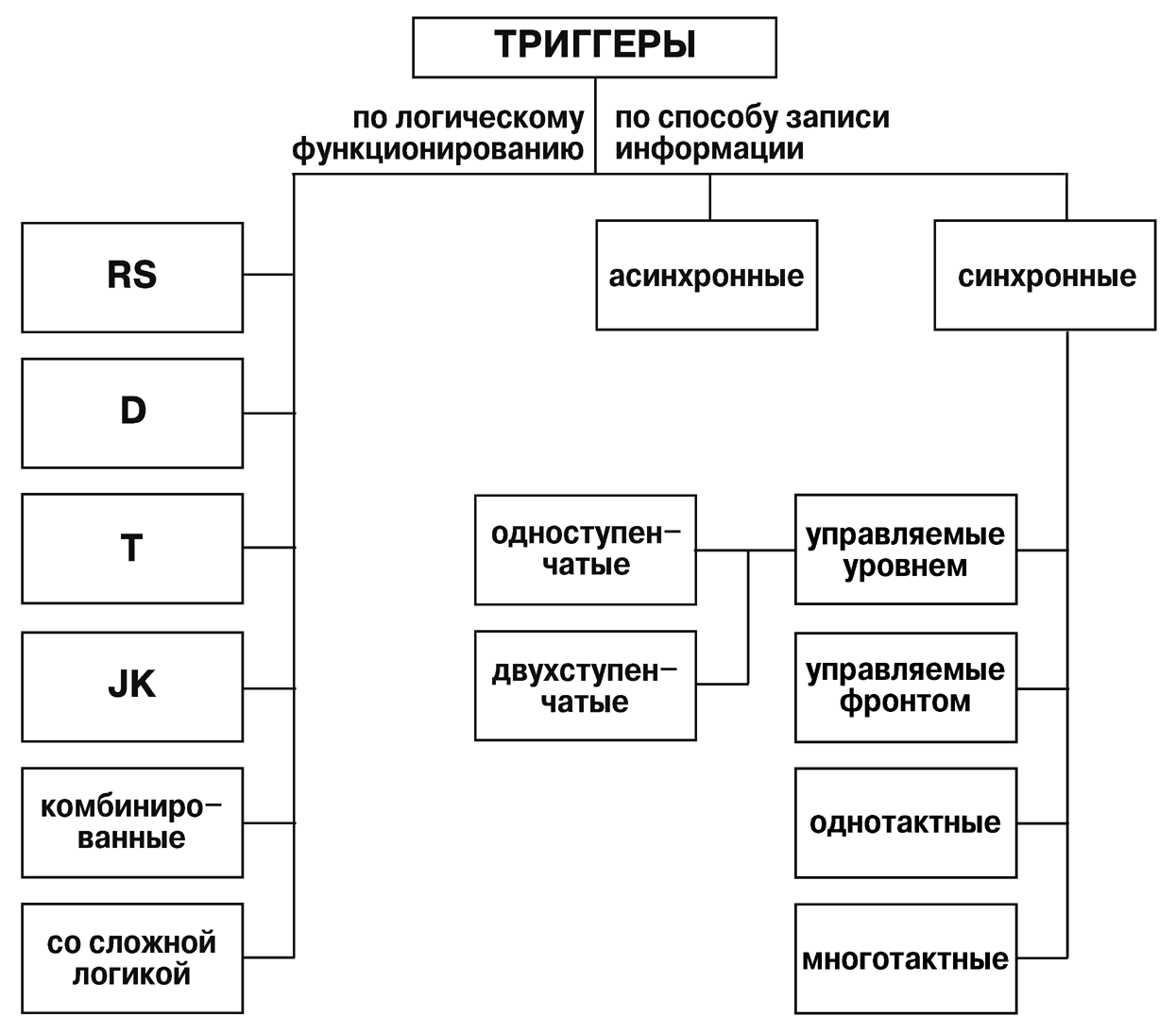

. Стандартные серии ИС содержат большое количество различных триггеров, отличающихся друг от друга способом записи информации, принципом функционирования и т.д. Поэтому технически грамотное применение готовых триггеров зависит от понимания принципов их функционирования и ограничений по входным и управляющим сигналам. Помощь же в этом может оказать их классификация, приведенная ниже.Классификация триггеров может быть проведена по признакам логического функционирования и способу записи информации (рис.6.1).

Рисунок 6.1 Классификация триггеров

По логическому функционированию различают триггеры RS-, D-, T-, DV-, TV-, JK- типов. В комбинированных триггерах совмещаются одновременно несколько из указанных типов, а триггеры со сложной входной логикой характеризуются наличием многих входных сигналов, связанных между собой некоторыми логическими зависимостями.

Триггеры RS типа имеют два входа раздельной установки в нулевое и единичное состояние. Воздействие по входу S (set-установка) переводит триггер в единичное состояние, а воздействие по входу R (reset - сброс) - в нулевое. Одновременная подача сигналов S и R не допускается.

Триггер типа D (от слова delay - задержка) принимает информацию по одному входу. Его состояние повторяет входной сигнал, с задержкой, определяемой тактовым сигналом.

Триггер типа Т (от слова toggle - защелка) называется счетным триггером. Он изменяет свое состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал.

Триггеры типов DV и TV отличаются от своих прототипов D и T дополнительным входом V. Если на этот вход подан высокий уровень напряжения, то триггеры функционируют как прототипы. Если же на входе V низкий уровень напряжения, то триггеры находятся в режиме хранения и не воспринимают изменения информации на входах.

Триггер типа JK - универсален, с раздельной установкой нулевого и единичного состояний. В отличии от RS триггера в нем не запрещена одновременная подача сигналов на оба входа. Причем одновременная подача логической единицы на оба входа переводит его в счетный режим, и триггер начинает функционировать аналогично триггеру типа Т относительно тактового входа. При раздельном использовании входов установка триггера в единичное состояние осуществляется по входу J, а в нулевое - по входу K.

В комбинированных триггерах совмещаются несколько режимов. Например, комбинированным является триггер типа RST с входами установки единичного и нулевого состояний, а также счетным.

Примером триггера со сложной входной логикой может служить JK триггер, у которого имеется несколько входов J и K. Причем как по входам J, так и по входам K выполняется логическая операция И.

По способу записи информации различают асинхронные (нетактируемые) и синхронные (тактируемые) триггеры. В асинхронных триггерах переход в новое состояние вызывается изменениями информационных входных сигналов. В тактирумых же триггерах такой переход происходит только после подачи специальных тактовых сигналов, которые обычно обозначаются буквой C (clock).

В зависимости от числа тактовых сигналов различают одно- и многотактные триггеры.

По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем или фронтами. Управление уровнями означает, что при одном уровне триггер воспринимает изменения входных сигналов, а при другом - сохраняет неизменное состояние. При управлении фронтами разрешение на переключение триггера дается в момент перепада тактового сигнала (на его фронте или спаде). В другие моменты триггер не воспринимает изменения входных сигналов независимо от уровня тактового сигнала. Такие триггеры называются триггерами с динамическим управлением.

Управляемые уровнем триггеры делятся на одноступенчатые и двухступенчатые. В одноступенчатых поступление соответствующего уровня разрешает переключение в новое состояние. Двухступенчатые триггеры состоят из входного и выходного каскадов и управляются таким образом, что переход в новое состояние происходит в обеих ступенях поочередно. В частности, в однотактном двухступенчатом триггере один из уровней тактового сигнала разрешает прием информации во входную ступень, в то время как выходные сигналы, снимаемые со второй ступени, остаются неизменными. Другой уровень тактового сигнала разрешает передачу нового состояния во вторую ступень.

6.2. ОДНОСТУПЕНЧАТЫЕ ТРИГГЕРЫ

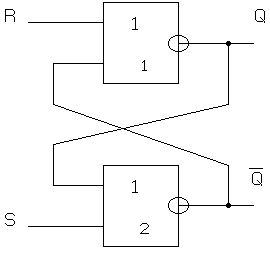

6.2. ОДНОСТУПЕНЧАТЫЕ ТРИГГЕРЫСхема простейшего RS триггера получается, если включить кольцом два элемента ИЛИ-НЕ (рис.6.2). Пока на обоих управляющих входах R и S уровни сигналов не активны, в данном случае равны “0”, триггер находится в одном из двух устойчивых состояний. Если сигнал на выходе Q равен “1”, то, как видно из схемы, этот единичный сигнал, поступая по цепи положительной обратной связи на вход элемента 2, вызывает появление на выходе

сигнал с нулевым уровнем. В свою очередь нулевой уровень с выхода

сигнал с нулевым уровнем. В свою очередь нулевой уровень с выхода  , поступая на вход элемента 1, поддерживает выход Q в состоянии 1. Иначе говоря, при входных сигналах R и S, равных “0”, появившаяся по любой причине на выходе Q единица будет сама себя поддерживать по цепи обратной связи сколь угодно долго.

, поступая на вход элемента 1, поддерживает выход Q в состоянии 1. Иначе говоря, при входных сигналах R и S, равных “0”, появившаяся по любой причине на выходе Q единица будет сама себя поддерживать по цепи обратной связи сколь угодно долго.В силу симметрии схемы, триггер будет столь же устойчив и в своем противоположном - нулевом состоянии, когда сигнал на выходе Q равен “0”.

В табл. 6.1. приведены все возможные состояния RS триггера.

Рисунок 6.2 RS – триггер на элементах ИЛИ-НЕ

Таблица 6.1

| R | S | Qn+1 | Режим |

| 0 0 1 1 | 0 1 0 1 | Qn 1 0 X | Хранение Установка Сброс Запрещенная комбинация |

Замечание: для обозначения исходного состояния триггера в табл. 6.1 используется символ Qn, новое же состояние триггера будем обозначать как Qn+1.

Если на оба входа RS триггера подать высокие уровни, то на его выходах появятся нули. При этом нарушается присущее триггерам условие противофазности сигналов на прямом и инверсном выходах. Если же теперь одновременно снять единицы со входов R и S, то оба логических элемента начнут переключаться в единичное состояние. Поскольку на обоих входах элементов 1 и 2 триггера присутствуют низкие уровни, то они оба будут стремиться переключиться в единичное состояние. Однако это невозможно, так как появление “1” на одном из выходов триггера обусловливает сохранение нуля на другом. В зависимости от коэффициентов усиления, скоростей переходных процессов и ряда других факторов единица может установиться как на прямом, так и на инверсном выходе. В связи с тем, что в этой ситуации заранее нельзя предсказать на каком выходе появится “1”, то комбинация R = S = 1 считается запрещенной.

В режимах установки и сброса на длительность сигналов управления накладываются временные ограничения, которые обусловлены тем, что процесс переключения заканчивается тогда, когда по цепи обратной связи на вход триггера приходит сигнал, дублирующий входное воздействие. Тогда минимально допустимая длительность R- и S-сигналов будет равна: tp = 2t (t - время задержки распространения сигнала логического элемента).

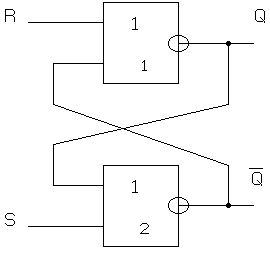

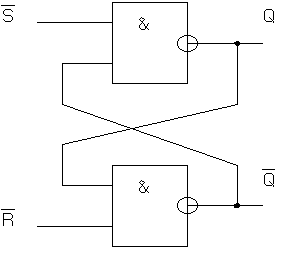

На рис. 6.3 показана электрическая схема RS триггера, построенного на элементах И-НЕ. В силу законов дуальности этот триггер функционирует по отношению к RS триггеру, показанному на рис. 6.2, с точностью наоборот. В режиме хранения на обоих входах должны быть не нули, а единицы; сигналы управления

и

и  имеют активно низкий уровень, а одновременная подача двух нулей на входы запрещена. Следует отметить, что рассмотренные схемы RS триггеров являются основой для построения практически всех, более сложных триггеров.

имеют активно низкий уровень, а одновременная подача двух нулей на входы запрещена. Следует отметить, что рассмотренные схемы RS триггеров являются основой для построения практически всех, более сложных триггеров.

Рисунок 6.2 RS – триггер на элементах ИЛИ-НЕ.

Рисунок 6.3 RS-триггер на элементах И-НЕ.

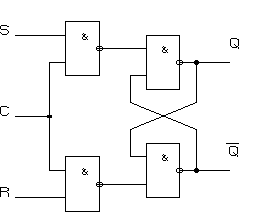

Рассмотренные выше схемы RS-триггеров относятся к асинхронным. Тактируемый RS-триггер, схема которого представлена на рис. 6.4 синхронизируется высоким уровнем тактового сигнала C. Если на вход C подан низкий уровень напряжения, то на выходах элементов 1 и 2 независимо от состояния входов R и S будут присутствовать высокие уровни напряжения. Эти уровни удерживают асинхронный RS-триггер, образованный элементами 3 и 4, в режиме хранения. При подаче на вход С логической единицы схема функционирует как обычный RS-триггер.

Рисунок 6.4 Синхронный RS-триггер.

Характерной особенностью схемы на рис. 6.4 является то, что в течение всего промежутка времени, когда С = 1, любые изменения управляющих сигналов на входах R и S передаются на выход. Поэтому о такой схеме говорят, что она “прозрачна” по R- и S-входам.

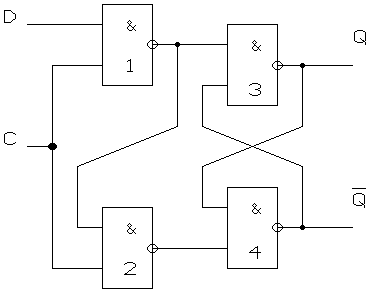

Схема одноступенчатого тактируемого уровнем D-триггера легко может быть получена из схемы синхронного RS-триггера: с помощью дополнительной связи с выхода элемента 1 на вход элемента 2 однофазный вход данных D превращается в парафазный и подается на R- и S-входы триггера, образованного элементами 3 и 4. D-триггер функционирует аналогично тактируемому RS-триггеру (рис. 6.5.).

При С = 1 D-триггер прозрачен, т.е. любое изменение информации на входе D передается на выход. По отрицательному фронту тактового сигнала в триггере запоминается (защелкивается) то состояние, которое было на входе D непосредственно перед этим моментом. Отсюда и происходит еще одно название этого триггера - защелка (latch).

Рисунок 6.5. Синхронный D-триггер.

В DV-триггерах параллельно сигналу С на входные элементы заведен еще один разрешающий сигнал V (от valve - клапан), который воздействует на D-триггер аналогично сигналу С.

Поскольку информация в D-триггере фиксируется по отрицательному фронту тактового сигнала С, то для правильного функционирования всякие изменения данных на входе D должны прекратиться за некоторое время до среза С-сигнала (tsu) и удерживаться в течение некоторого времени (th) после него. Кроме того быстродействие D-триггера характеризуется временем задержки распространения сигнала от входа С (tpQ,C) и минимальной длительностью тактового сигнала (tpC).

В состав стандартных серий ИС входят D-триггеры-защелки, такие, например, как К155ТМ5, К155ТМ7, К561ТМ3 и др.

6.3. ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

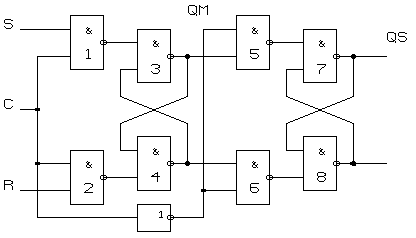

На рис. 6.6 приведена схема, состоящая из двух последовательно включенных синхронных RS-триггеров, первый из которых называется ведущим или М-триггером (master - хозяин), а второй - ведомым или S-триггером (slave - раб). Благодаря общему синхросигналу С схема функционирует как единое целое и называется двухступенчатым или MS-триггером (master-slave flip-flop).

Рассмотрим работу MS-триггера. Если на вход С подан высокий уровень напряжения, то информация со входов R и S поступает на выход QM. При этом состояние S-триггера не изменяется, так как на входы элементов 5 и 6 поступает низкий уровень напряжения (С = 0). Информация с выхода QM запишется в S-триггер только тогда, когда на входы элементов 5 и 6 поступит разрешающий сигнал, т.е. единица. Это может произойти только в том случае, если на вход С будет подан ноль. При С = 0 блокируется М-триггер, и информация с управляющих входов R и S не может поступить на выход. Таким образом ни при С = 0, ни при С = 1 MS-триггер непрозрачен по управляющим входам R и S. Сказанное отражает важное свойство MS-триггера: запись информации в него происходит по отрицательному фронту тактового сигнала.

| М-триггер | S-триггер |

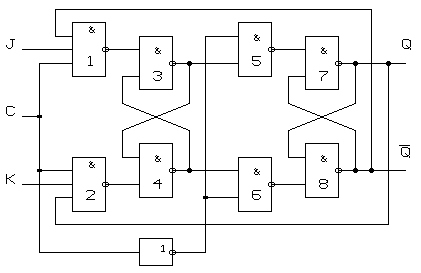

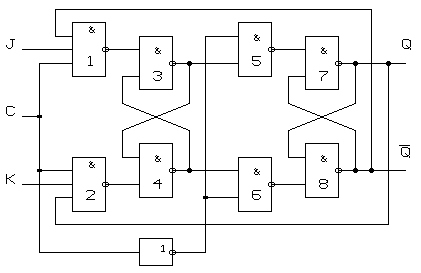

Рассмотренный MS-триггер является основой для построения широко распространенного JK-триггера, электрическая схема которого приведена на рис. 6.7. Отличительной особенностью этого триггера является наличие перекрестных обратных связей с выходов на входные элементы 1 и 2.

Рисунок 6.7. Двухступенчатый JK-триггер.

Если на входы J и K подан ноль, то на выходах элементов 1 и 2 будет высокий уровень напряжения независимо от состояния остальных входов. Триггер первой ступени находится в режиме хранения, а следовательно информация с его выходов будет перезаписываться во вторую ступень по каждому отрицательному фронту тактового сигнала С. Поскольку при этом состояние выходов Q не изменяется, то говорят, что триггер находится в режиме хранения. Предположим, что на выходе Q - низкий уровень напряжения, а на входы подана комбинация J = 1, K = 0. Высокий уровень на входе С установит триггер первой ступени в единичное состояние, которое по срезу синхросигнала запишется во вторую ступень. Таким образом, вход J выполняет функции S-входа. В силу симметрии схемы легко показать, что воздействие по К входу переводит триггер в “0”. Из сказанного следует, что при разноименных уровнях на входах J и K JK-триггер ведет себя также, как и синхронный RS-триггер.

Рассмотрим работу триггера при J = K = 1. Для RS-триггера такое состояние входов запрещено. Пусть на выходе Q - низкий уровень, который поступая по цепи обратной связи на вход элемента 2, будет удерживать его выход в единичном состоянии. Сигнал с инверсного выхода Q разрешает прохождение синхросигнала С на триггер первой ступени, который установится в единичное состояние. По отрицательному фронту тактового сигнала единичное состояние триггера первой ступени запишется во второй триггер и на его выходе установится новое состояние, т. е. Q = 1. Этот уровень разрешит прохождение сигналов через элемент 2, что приведет к изменению состояния триггера на противоположное после прихода очередного среза тактового сигнала. Так как при J = K = 1 триггер меняет свое состояние на противоположное по каждому отрицательному фронту тактового сигнала, то такой режим работы получил название счетный.

Кратко функционирование JK-триггера описывает табл. 6.2.

Таблица 6.2. Таблица истинности JK-триггера

| С | J | K | Qn+1 | Режим |

| Х | 0 0 1 1 | 0 1 0 1 | Qn 0 1  | хранение сброс установка счетный |

Для обозначения отрицательного фронта тактового сигнала С используется символ “стрелка вниз”. Еще раз подчеркнем, что для JK-триггера важен не уровень тактового сигнала, а его перепад.

В состав серии 155 входит JK-триггер К155ТВ1, построенный по схеме близкой к показанной на рис. 6.7.

Рисунок 6.7. Двухступенчатый JK-триггер.

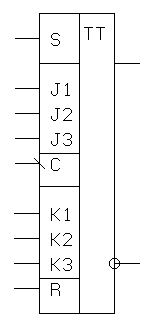

В отличии от прототипа у него по три входа J и K, которые объединены логическим И. Это позволяет выполнять логическое умножение управляющих сигналов. Раздельные асинхронные входы R и S позволяют устанавливать триггер в нулевое и единичное состояние независимо сигналов на остальных входах. Для обозначения фронта тактового сигнала, по которому происходит запись информации используется наклонная черта. Условное графическое обозначение (УГО) этого триггера приведено на рис. 6.8.

Рисунок 6.8. УГО JK-триггера К155ТВ1.

6.4. ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ

Триггеры с динамическим управлением записью информации (триггеры, управляемые фронтами тактовых сигналов) допускают изменять входные данные при любом уровне тактовых сигналов без возникновения ошибок функционирования. В этих схемах тактовый сигнал активен лишь на коротком интервале в окрестностях фронта или спада импульса.

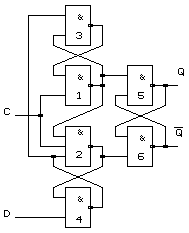

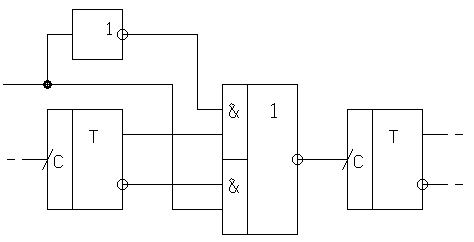

Ярким представителем триггеров с динамическим управлением является D триггер, схема которого показана на рис. 6.9 (так называемая схема трех триггеров). Рассмотрим работу этого триггера.

Если на вход С подан низкий уровень напряжения, то на выходах элементов 1 и 2 независимо от состояния входа D будут присутствовать высокие уровни. Это означает, что RS триггер, образованный элементами 5 и 6, будет находиться в режиме хранения. При С = 1 изменение информации на входе D, также, не приводит к переключению триггера. Убедимся в этом. Пусть на выходе Q триггера присутствует высокий уровень напряжения, а информация на входе D изменяется с высокого уровня на низкий. Так как на выходе Q высокий уровень, то на выходе элемента 1 был низкий уровень, а на выходе элемента 2 - высокий. После изменения информации на входе D выход элемента 4 переключится из “0” в “1”. Эта единица, поступая на вход элемента 3, переведет RS- триггер, образованный элементами 1 и 3, в режим хранения, а следовательно, состояние выхода элемента 1 не изменится. Низкий уровень с выхода элемента 1, поступая на вход элемента 2 по цепи обратной связи, будет удерживать его выход в единичном состоянии. Таким образом, информация на входах RS-триггера, образованного элементами 5 и 6, не изменится, следовательно, не изменится и состояние выходов триггера. Аналогичные рассуждения можно привести и для противоположного состояния триггера.

Рисунок 6.9. Схема D триггера.

Рассмотрим процессы, протекающие в триггере, в режиме записи. Предположим, что на выходе Q - низкий уровень, на входе D - высокий, а на тактовом входе - низкий. При этом на выходах элементов 1...3 будет присутствовать логическая 1, а на выходе элемента 4 - 0. Поступление на вход С положительного фронта вызовет изменение состояния выхода элемента 1 из “1” в “0”. Состояние же выходов элементов 2...4 не изменится. Это изменение приведет к установлению на выходе триггера новой информации Q = 1. Аналогичные процессы происходят в триггере и при записи логического нуля, с той разницей, что изменяется состояние RS-триггера, образованного элементами 2 и 4. Таким образом информация на выходе триггера повторяет данные на входе с задержкой на такт.

Важной особенностью рассмотренного триггера является то, что он может работать в счетном режиме. Для этого необходимо соединить его инверсный выход

со входом D.

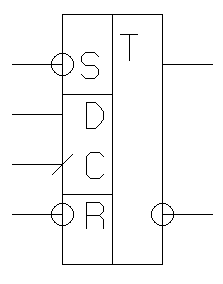

со входом D.Триггеры с динамическим управлением входят в состав практически всех серий микросхем, наиболее распространенным из которых является ИС ТМ2. В состав микросхемы ТМ2 входит два идентичных D триггера, имеющих асинхронные входы сброса R и установки S. Запись информации в триггер происходит по положительному фронту тактового сигнала. Кратко функционирование триггера описывает табл. 6.3.

Таблица 6.3. Таблица истинности триггера ТМ2

| S | R | C | D | Qn+1 | Режим |

| 0 1 1 1 1 | 1 0 1 1 1 | Х Х % % Х | Х Х 0 1 Х | 1 0 0 1 1 | установка сброс запись “0” запись “1” неопределенность |

Для правильного функционирования триггера на подачу входных сигналов накладываются определенные временные ограничения: входные данные должны быть установлены за время tSU до прихода положительного фронта тактового сигнала на входе D и удерживаться на нем в течении времени tH после окончания действия этого же фронта. Эти времена существенным образом отличаются для различных серий микросхем и приво - дятся в справочной литературе. Функциональное обозначение триггеров ТМ2 показано на рис. 6.10.

Рисунок 6.10. УГО триггера ТМ2.

Помимо рассмотренного триггера ТМ2 в состав серий микросхем входят и другие триггеры с динамическим управлением такие, например, как ТМ8 (четыре триггера в одном корпусе) и ТМ9 (шесть триггеров в одном корпусе).

6.5. РЕГИСТРЫ

Регистрами называются устройства, выполняющие операции приема, хранения и передачи слов, и предназначенные для построения на их основе многоразрядных схем памяти, преобразователей последовательного кода в параллельный и обратно, сдвигателей и т.д.

По способу записи слова в регистры они делятся на параллельные, последовательные (сдвигающие) и параллельно-последовательные (универсальные).

В параллельных регистрах запись слова происходит одновременно во все разряды регистра. Последовательные регистры характеризуются последовательной записью слова, начиная с младших или старших разрядов. Последовательно-параллельные регистры имеют входы и выходы, как для параллельной, так и для последовательной записи и выдачи информации. На основе таких регистров осуществляются операции преобразования из последовательного кода в параллельный и обратно.

Наиболее распространенными являются статические регистры. Каждому разряду слова, записанному в такой регистр, соответствует свой разряд регистра, выполненный на основе триггера, чаще всего типа RS, D или JK. Разряды регистра нумеруются в порядке нумерации разрядов в слове.

Находят также применение динамические регистры (обычно в составе БИС), в которых функция запоминания информации реализуется конденсатором или индуктивностью. В виду того, что интервал хранения информации в накопительном элементе ограничен саморазрядом, то в динамических регистрах предусматривается цикл регенерации хранимых данных.

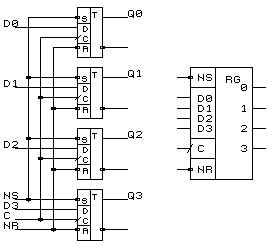

Параллельные регистры представляет собой совокупность триггеров, имеющих общие сигналы управления и синхронизации и индивидуальные входы и выходы. На рис. 6.11 приведена электрическая схема и УГО четырехразрядного параллельного регистра построенного на синхронных D-триггерах.

Рисунок 6.11. Схема и функциональное обозначение регистра.

Регистр имеет входы установки NS и сброса NR (активно низкие), запись информации в него происходит по положительному фронту тактового сигнала С одновременно во все разряды.

В стандартные серии микросхем входит большое количество 4-х и 8-ми разрядных параллельных регистров. В регистре ИР15 имеются специальные входы разрешения записи EWR1 и EWR2, осуществляющие управление режимами записи/хранения. Выходы этого регистра выполнены по схеме с тремя состояниями, что позволяет использовать их при работе с общей шиной. Восьмиразрядные регистры представлены такими микросхемами как ИР23, ИР27, ИР35, отличающиеся набором управляющих сигналов и схемами выходов. В регистре ИР22 запись информации осуществляется по высокому уровню тактового сигнала. При построении регистров с разрядностью больше 8 используют стандартные 4-х или 8-ми разрядные регистры, у которых управляющие и тактовые входы объединены.

Регистры сдвига (последовательные регистры) представляют собой цепочку взаимосвязанных поразрядных схем и предназначены для сдвига слова на один разряд вправо или влево. Различают однонаправленные и реверсивные регистры сдвига.

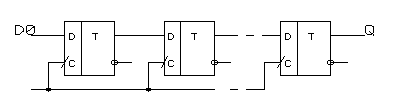

Структура сдвигающих регистров со сдвигом на один разряд вправо показана на рис. 6.12, где в качестве запоминающего элемента используются синхронный D триггер.

Рисунок 6.12 Структура регистра со сдвигом вправо.

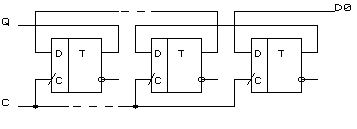

Для построения регистра со сдвигом влево необходимо изменить направление связей в схеме на рис.6.12, так как это показано на рис. 6.13.

Рисунок 6.13 Структура регистра со сдвигом влево.

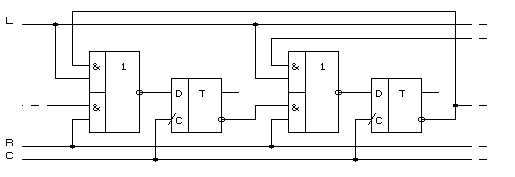

Реверсивные регистры сдвига позволяют осуществлять сдвиг информации как влево так, и вправо. Фрагмент электрической схемы регистра сдвига приведен на рис.6.14.

Рисунок 6.14 Фрагмент схемы реверсивного регистра сдвига.

Если на вход R (сдвиг “вправо”) подан высокий уровень напряжения (при этом на вход L должен быть подан логический “0”), то регистр осуществляет сдвиг информации вправо. При противоположной комбинации управляющих сигналов (R = 0, L = 1) сдвиг информации будет происходить влево. Со всех триггеров берутся инверсные данные, так как необходимо компенсировать инверсию элемента И-ИЛИ-НЕ.

Так же как и параллельные регистры, регистры сдвига широко представлены в стандартных сериях ИС. Эти микросхемы позволяют выполнять последовательный ввод информации - последовательно-параллельный вывод (ИР8), параллельный ввод - последовательный вывод (ИР9, ИР10), последовательно - параллельный ввод и параллельный вывод (ИР11, ИР16) со сдвигом информации как влево, так и вправо. Причем регистры сдвига выпускаются как 4-х разрядные, так и 8-разрядные. При построении регистров сдвига с разрядностью больше 8 необходимо объединить их управляющие и тактовые входы, а входы последовательного ввода информации подключаются к одноименным выходам предыдущего разряда.

6.6. СЧЕТЧИКИ

Счетчики применяются в различных цифровых устройствах и строятся их разрядных схем, связанных друг с другом и содержащим триггеры и логические схемы.

Специфичной для счетчиков является операция инкремента (или декремента), т.е. изменение его содержимого на единицу. Счетчики прежде всего характеризуются модулем счета М, который определяет цикличность изменения состояния счетчика. Они классифицируются по значению модуля, направлению счета, способу организации межразрядных связей.

По значению модуля счета различают двоичные (М=2n), двоично-кодированные с произвольным модулем (c произвольным модулем, но кодированием состояний двоичными кодами), счетчики с десятичным кодированием и др.

По направлению счета счетчики делятся на суммирующие (прямого счета), вычитающие (обратного счета) и реверсивные (с изменением направления счета).

По способу организации межразрядных связей различают счетчики с последовательным, параллельным и комбинированными переносами.

Двоичные счетчики имеют модуль счета равный М=2n, а его состояние выражается двоичным кодом. Если рассмотреть таблицу состояний счетчика (табл. 6.4), то из нее следует, что триггер младшего разряда переключается от каждого входного сигнала.

Таблица 6.4. Таблица состояний счетчика

| Прямой счет | Обратный счет | ||||

| Q2 | Q1 | Q0 | Q2 | Q1 | Q0 |

| 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 1 1 1 1 0 0 0 0 | 1 1 0 0 1 1 0 0 | 1 0 1 0 1 0 1 0 |

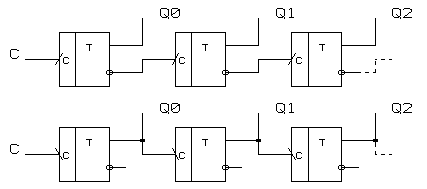

Триггер первого разряда переключается при изменении состояния триггера нулевого разряда и т.д. Следовательно, счетчики можно построить в виде цепочки последовательно включенных счетных триггеров. Для суммирующих счетчиков, изменение состояния следующего триггера происходит только тогда, когда выходной сигнал предыдущего триггера изменяется из единицы в ноль (для вычитающих – из нуля в единицу). Поэтому, суммирующие счетчики могут быть построены на тактируемых Т-триггерах с синхронизацией по отрицательному фронту тактового сигнала. Эквивалент первого варианта - схема из последовательно соединенных счетных триггеров, тактируемых положительным фронтом тактового сигнала, у которых тактовые сигналы снимаются не с прямого выхода, а с инверсного. Схемы суммирующих счетчиков показаны на рис. 6.15.

Рисунок 6.15 Схемы суммирующих счетчиков.

Схемы вычитающих счетчиков обратны суммирующим по фронтам срабатывания счетных триггеров (рис. 6.16).

Рисунок 6.16 Схемы вычитающих счетчиков.

Полученные счетчики называют последовательными, так как в них каждый последующий триггер переключается выходным сигналом предыдущего. Последовательные счетчики отличаются простотой схемы, но обладают низким быстродействием. Максимальная частота переключения таких счетчиков определяется быстродействием младшего триггера.

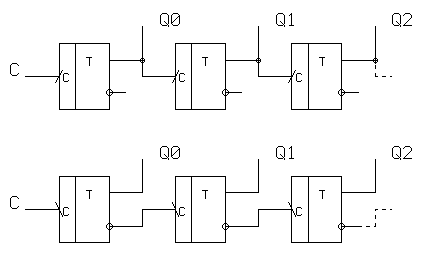

Параллельные счетчики характеризуются тем, что в них все разряды переключаются практически одновременно. На рис. 6.17 показан фрагмент схемы параллельного счетчика. Выходные сигналы поступают на счетный вход триггера через многовходовую схему И, на остальные входы которой заведены выходные сигналы со всех предыдущих разрядов. Поэтому при поступлении тактовых сигналов переключаться будут только те триггеры, у которых все предыдущие выходы были в единичном состоянии.

Рисунок 6.17 Фрагмент схемы параллельного счетчика.

Частотные возможности параллельных и последовательных счетчиков в режиме деления частоты идентичны, так как в обоих случаях определяются быстродействием триггера младшего разряда.

Реверсивные счетчики изменяют направление счета под воздействием управляющего сигнала или при смене точки подачи считаемых сигналов. В первом случае схема имеет управляющий и счетный входы, во втором - два счетных входа.

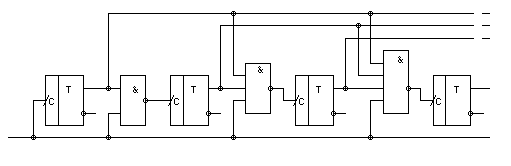

Наиболее распространенный способ построения реверсивных счетчиков - переключение межразрядных связей. Как следует из сравнения рис. 6.15 и 6.16, суммирующие и вычитающие счетчики отличаются только точкой съема сигнала, подаваемого с предыдущего разряда на последующий. Таким образом для получения реверса достаточно управлять выбором источника сигнала, что легко достигается введением в схему счетчика мультиплексора 2 в 1 (рис.6.18)

Рисунок 6.18 Фрагмент схемы реверсивного счетчика.

В стандартные серии микросхем входит большое количество двоичных и двоично-десятичных счетчиков. К последовательным счетчикам относятся ИС типа ИЕ5, ИЕ15 (ИЕ14), ИЕ19 (ИЕ20). Причем в счетчике ИЕ15 имеются входы предварительной загрузки числа. К реверсивным счетчикам относятся микросхемы ИЕ7 (ИЕ6), ИЕ13, ИЕ17, ИЕ18. Реверсивные счетчики, как правило, имеют входы предварительной загрузки числа, а реверс счета у них осуществляется обоими способами, описанными выше. Параллельные суммирующие счетчики представлены микросхемами ИЕ10 (ИЕ9). Замечание: в скобках указаны двоично-десятичные счетчики.

Для получения счетчиков с коэффициентом пересчета больше М = 2n используется их каскадное включение. В последовательных счетчиках выход предыдущего счетчика соединяется с тактовым входом последующего, а их цепи установки или сброса объединяются. В реверсивных счетчиках, как правило, имеются специальные выходы группового переноса, которые соединяются с соответствующими счетными входами более “старшего” счетчика.

Для реализации счетчиков с произвольным модулем счета используется два основных способа. В основе первого способа лежит метод исключения лишних комбинаций по цепи сброса, во втором - установка исходного числа.

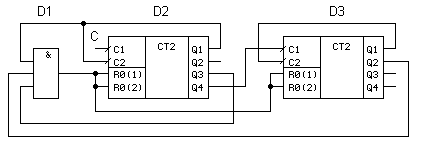

Первый способ рассмотрим на примере построения счетчика с коэффициентом пересчета 37. Так как заданный модуль счета больше 16, то для реализации этого счетчика необходимо использовать два четырехразрядных счетчика. Пусть это будут микросхемы ИЕ5. ИС типа ИЕ5 представляют собой последовательные двоичные четырехразрядные счетчики, у которых первый триггер имеет индивидуальный тактовый вход С1, а его выход Q1 не соединен с остальными разрядами счетчика. Старшие триггеры счетчика соединены последовательно так, как это показано на рис. 6.15. Входы асинхронного сброса триггеров объединены и выведены на внешние выводы R0, R1 через логический вентиль 2И-НЕ. Сброс триггеров счетчика в нулевое состояние происходит по высокому уровню на входах R0 и R1. Электрическая схема счетчика с модулем счета 37 показана на рис.6.19.

Рисунок 6.19 Схема счетчика с модулем счета 37.

Внешний сигнал синхронизации подается на вход С1 счетчика D2. Его выход Q1 соединен со входом С2. Вход С1 счетчика D3 подключен к выходу Q4 счетчика D2. В процессе подсчета импульсов счетчик последовательно принимает состояния от 0 до 36. После чего он должен сброситься в ноль, т.е. все оставшиеся комбинации (от 37 до 255) должны быть исключены. Для этого, как только на его выходах появится число 3710 = 1001012 должен выработаться сигнал сброса. Его легко получить, если объединить логическим И выходы Q1, Q3 и Q6 счетчика. Эту функцию выполняет вентиль 3И (элемент D1 на рис. 6.19), выход которого подключен к входам сброса счетчиков. Из рассмотренного примера следует, что для построения счетчика с произвольным модулем счета по методу исключения лишних комбинаций необходимо представить заданный коэффициент пересчета в двоичном коде. Выходы счетчика, веса которых соответствуют весам единиц в полученном двоичном числе, подсоединить ко входам логического вентиля И, выход которого подключить ко входам сброса счетчиков. К недостаткам рассмотренного метода следует отнести появление на выходах счетчика в последнем такте счета коротких импульсов, которые могут повлечь за собой сбои в работе аппаратуры. Кроме этого, этот способ не применим при построении вычитающих счетчиков.

В основе метода предварительной загрузки числа лежит способ исключения начальных состояний для суммирующего счетчика. При этом счет начинается с того числа, которое было предварительно записано в счетчик. Модуль счета определяется в соответствии с выражениями:

M = 2n - 1 – Х - для суммирующего счетчика;

М = X+1 - для вычитающего счетчика;

где Х - предварительно загружаемое число.

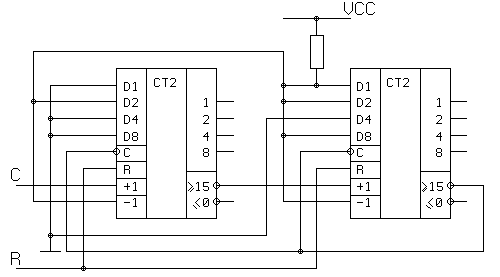

На рис. 6.20 в качестве примера показана схема суммирующего счетчика с модулем счета М = 77, построенного на микросхемах ИЕ7.

Рисунок 6.20 Схема счетчика с модулем счета 77.

Предварительная запись числа в этот счетчик происходит, если на вход стробирования С будет подан отрицательный импульс. Для осуществления прямого счета на вход “+1” подаются положительные импульсы, а на вход “-1” - высокий уровень напряжения. После заполнения счетчика выходы устанавливаются в состояние высокого уровня, а на выходе прямого переноса появится отрицательный импульс. Именно этот импульс и используется для предварительной записи числа. В рассматриваемом примере это число будет равно Х = 256 - 1 - 77 = 17810 (101100102). В соответствии с полученным числом входы счетчиков D0...D7 подключаются либо к нулевому потенциалу, либо через резистор к положительному выводу источника питания.

Аналогичным образом строятся и вычитающие счетчики с произвольным коэффициентом пересчета. При этом счетные импульсы подаются на вход “-1”, вход “+1” подключается к выводу питания, а сигнал предварительной записи снимается с выхода “

” старшего счетчика.

” старшего счетчика.