Популяризаторские работы по Русской логике представлены на сайте

| Вид материала | Изложение |

СодержаниеГлава восьмая Частотный детектор. Фазовый детектор. |

- Программа и описание курса Лекция «Андеррайтинг владельцев бизнеса» Специфика работы, 74.06kb.

- Которая была проведена с участием редакции сайта «Политучеба», 830.24kb.

- Оценка программы Вданной лекции ( шаг 2 ) представлены литературные источники и базы, 308.47kb.

- Анализ методической работы мбоу «сош №15» за 2010 2011 учебный год, 197.04kb.

- Курсовая работа, 193.69kb.

- Удк 519. 816 Способ представления термов в логике предикатов первого порядка. Алгоритм, 184.64kb.

- Техническое задание мбоу толстомысенской сош №7: «Варианты учебных планов подростковой, 160.12kb.

- М. М. Розенталь принципы диалектической логики глава V понятие в диалектической логике, 1324.47kb.

- Интернет, как информационно-образовательная среда, 70.95kb.

- Доклады и тезисы представлены в авторской редакции. Сподробными материалами конференции, 2528.5kb.

Глава восьмая

ПРОЕКТИРОВАНИЕ МПА НА БАЗЕ ПЛИС.

8.1. ОПТИМАЛЬНОЕ ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ СИСТЕМ УПРАВЛЕНИЯ.

Международный валютный фонд (МВФ) потребовал от России ликвидации ведущих технических вузов: МВТУ им. Баумана, МЭИ, МАИ, ЛПИ, НПИ и др. (р/с «Резонанс», 23.09.2003). В настоящее время идёт медленное тотальное уничтожение Российского образования и науки. «Вымирают» целые кафедры технических вузов, т.е. целые, зачастую уникальные, научные направления, Плодятся лишь псевдонаучные гуманитарные «академии» по выращиванию болтунов и демагогов. В этих условиях минимальной задачей старшего поколения советских инженеров и учёных, проспавших Советский Союз, является неукоснительная передача всего накопленного опыта и знаний новой генерации инженеров и учёных. Нельзя забывать, что в «технари» даже в советские времена шла наиболее талантливая молодёжь, тем более теперь. Это будущее России.

В связи с разгромом советской электроники все разработчики лихо набросились на зарубежную элементную базу, поскольку здесь не нужно напрягать интеллект. Однако требования безопасности России диктуют безусловный переход на отечественную элементную базу. В цифровой и даже аналоговой электронике такой переход возможен лишь за счёт базовых матричных кристаллов (БМК).

Мне как инженеру с 30-летним стажем хотелось бы помочь в деле проектирования молодым проектировщикам цифровой электроники. Разумеется, все мои рекомендации следует воспринимать критически, пытаясь найти альтернативное, возможно, более приемлемое решение. Разработчик – это прежде всего мыслитель, притом талантливый.

Частотный детектор.

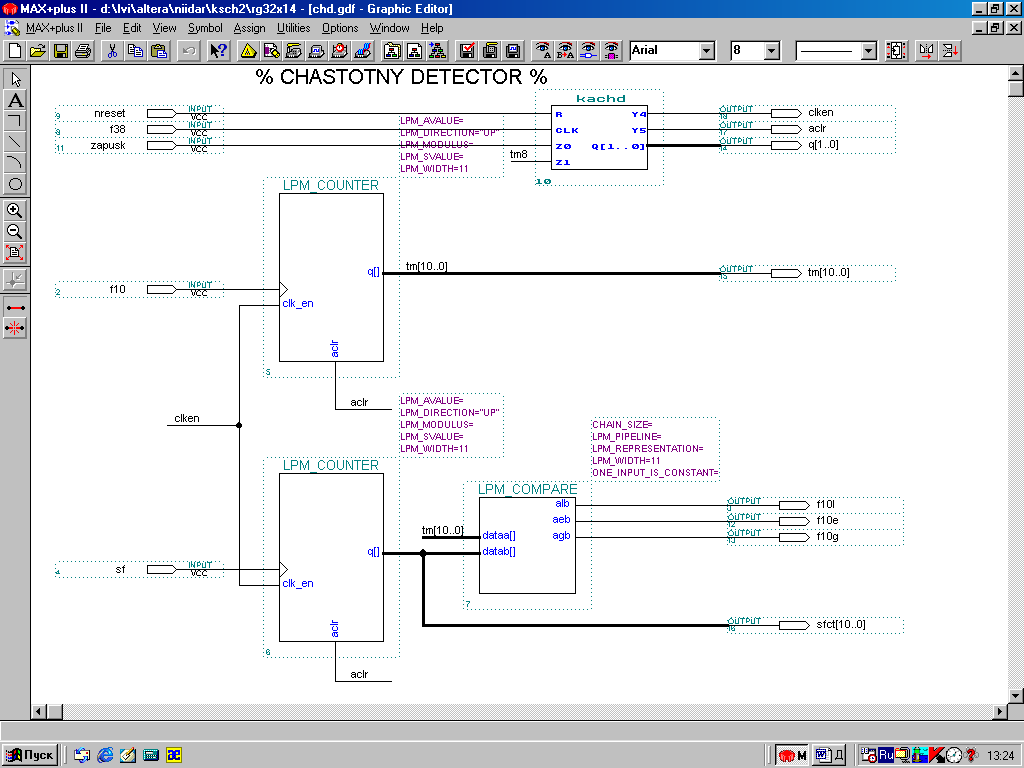

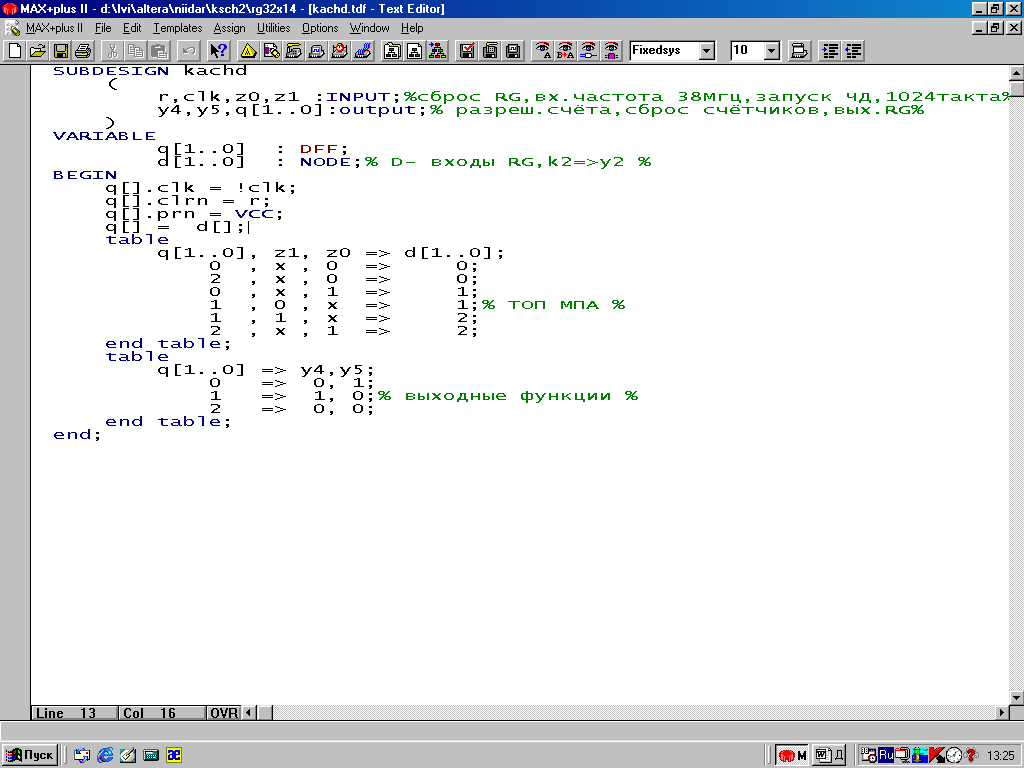

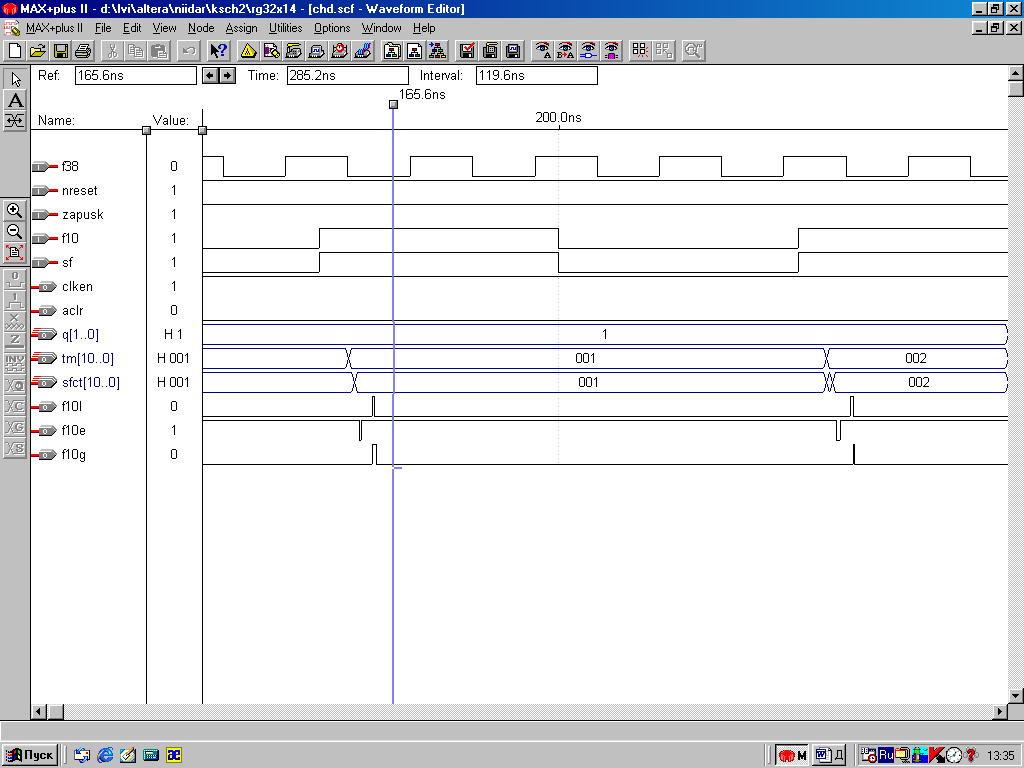

Частотный детектор (ЧД) сравнивает частоту на выходе синтезатора частоты (СЧ) с эталонной частотой 10 МГц и выдаёт результат в виде сигналов «больше», «меньше» или «равно». Схема ЧД состоит из двух счётчиков и конечного автомата (КА).

Начало

Y4

0

1

1

0

Конец

0

1

Y5

a0

a1

a2

Y1 – «больше»,

Y2 – «меньше»,

Y3 – «равно»,

Y4 – разрешение счёта,

Y5 – сброс счётчиков.

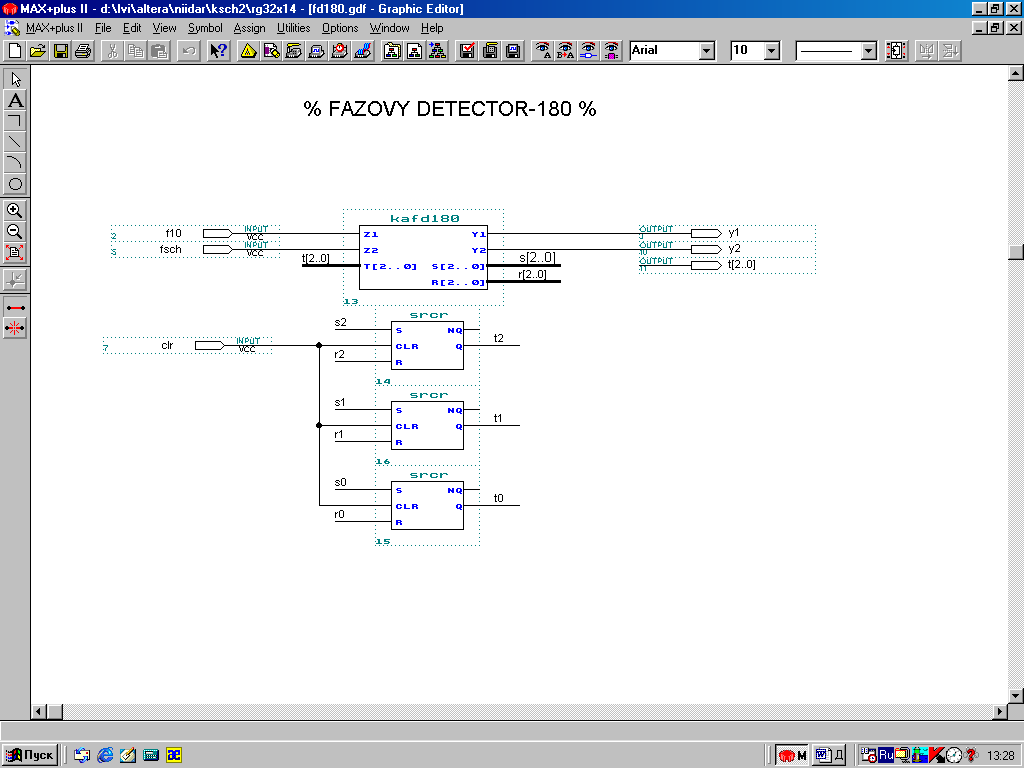

Фазовый детектор.

Фазовый детектор (ФД) определяет сдвиг по фазе между опорным сигналом 10 МГц и сигналом на выходе синтезатора частоты.

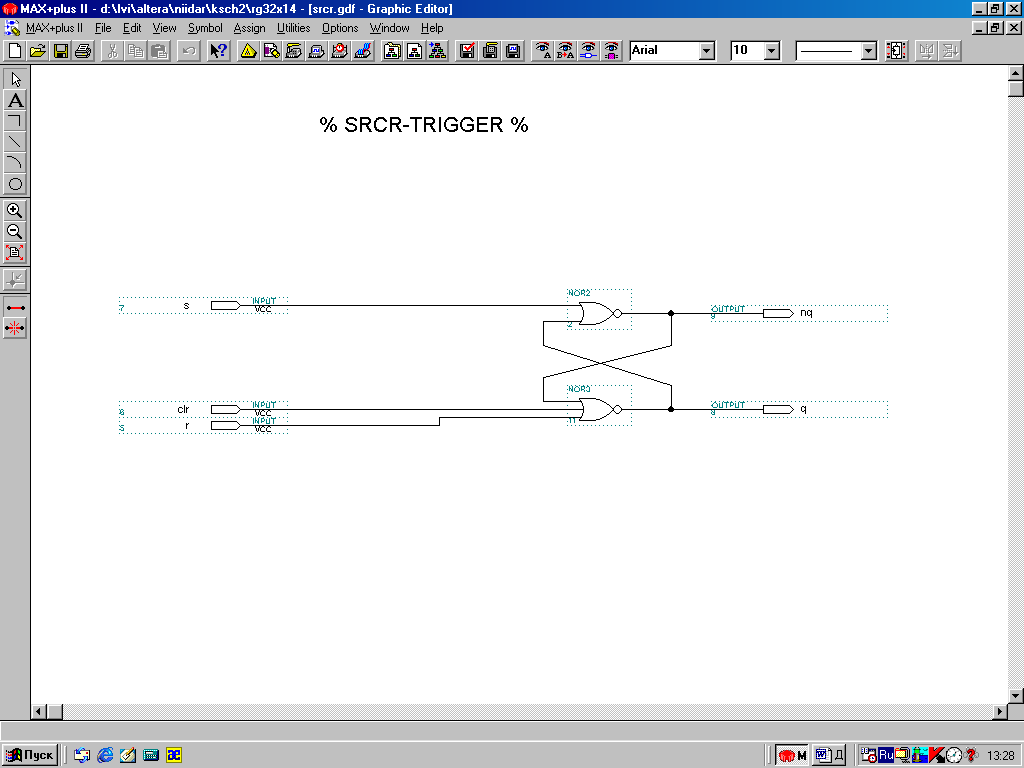

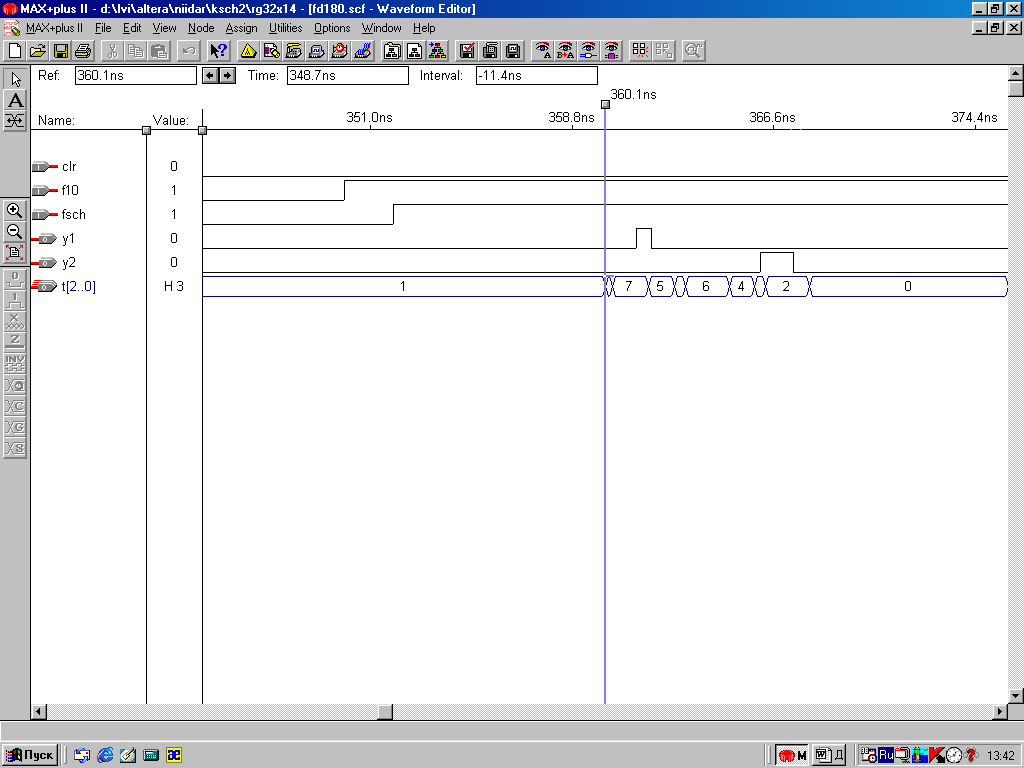

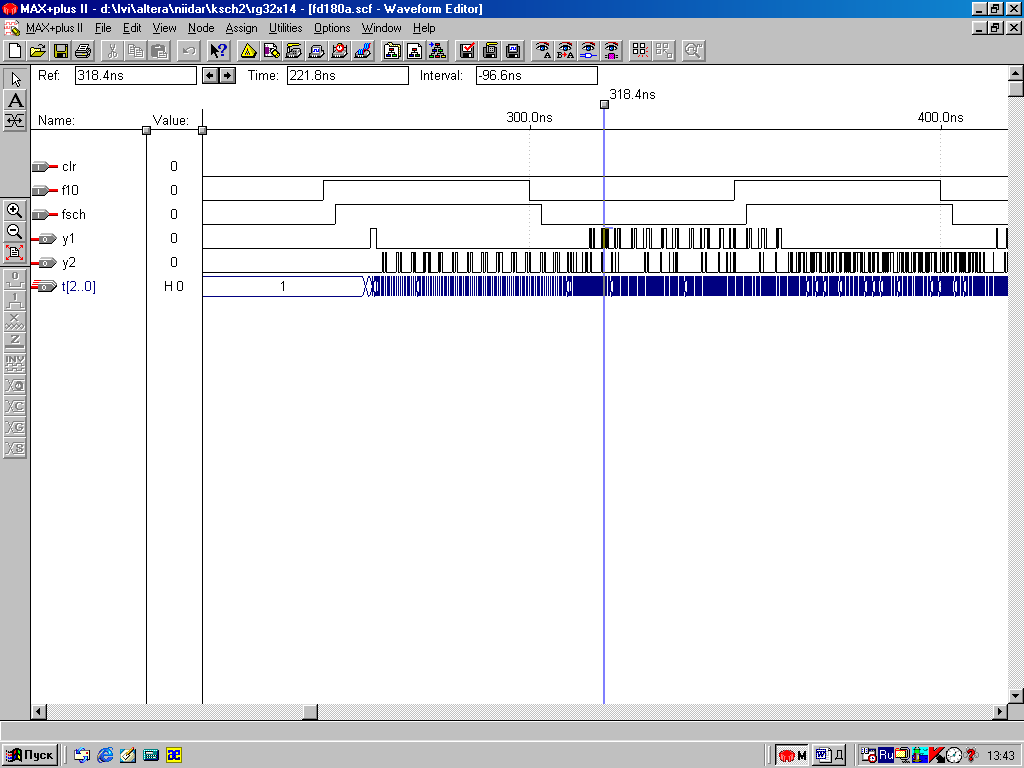

Для нормальной работы КА требуется высокое быстродействие ПЛИС. Поскольку необходимо отслеживать разность фаз не хуже 2нс за период 100нс, а тактовая частота не превышает 38 МГц, то КА должен быть асинхронным. Пришлось создать предельно «отжатые» SR-триггеры со входом сброса (они представлены на рисунке). У этого триггера есть незначительный недостаток в режиме обнуления, но к нему нет претензий в рабочем режиме. Кроме того, во избежание гонок, пришлось применить оригинальное противогоночное кодирование, когда состояния не просто развязываются по-Баранову, а обеспечивается переход в любое состояние при изменении только одного бита в кодах состояний.

Последняя диаграмма свидетельствует о срыве работы КА по причине недостаточного быстродействия ПЛИС. Если разность фаз не превышает 1нс, то КА не успевает отслеживать переходы из одного состояния в другое.

a0

Началоо

0

1

a1

1

0

1

0

Y1

a2

a4

1

0

Y2

a5

0

1

a7

a6

a3

Конец

a0

1

0

ГСА КА фазового детектора