Популяризаторские работы по Русской логике представлены на сайте

| Вид материала | Изложение |

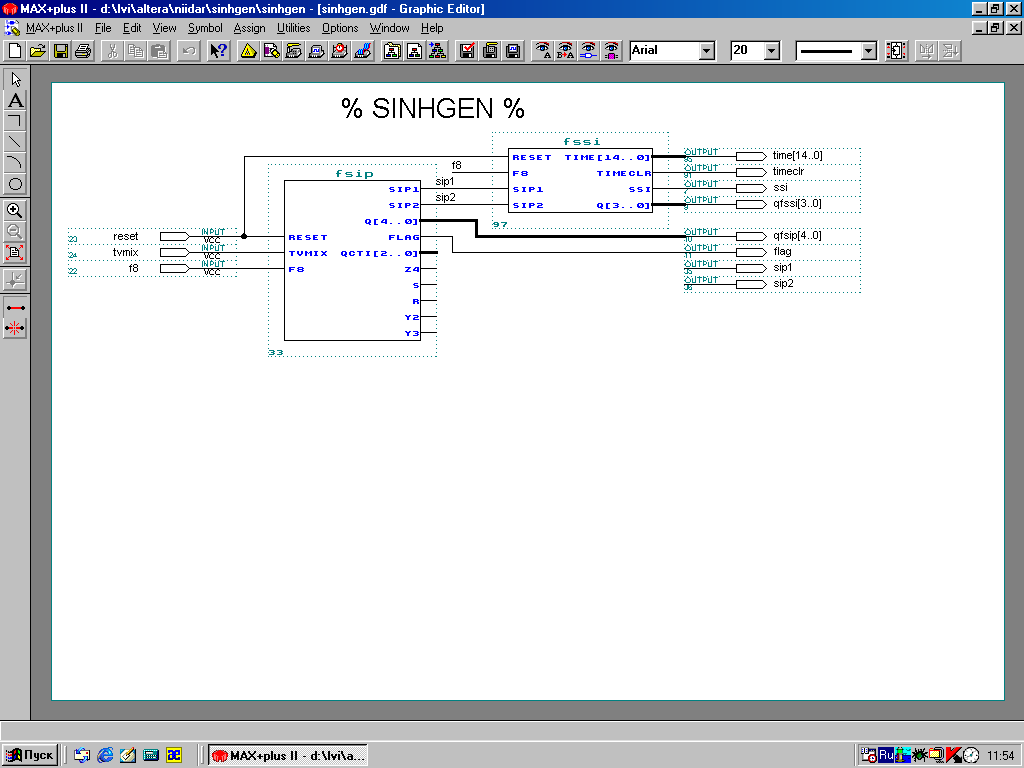

СодержаниеТелевизионный цифровой синхрогенератор. |

- Программа и описание курса Лекция «Андеррайтинг владельцев бизнеса» Специфика работы, 74.06kb.

- Которая была проведена с участием редакции сайта «Политучеба», 830.24kb.

- Оценка программы Вданной лекции ( шаг 2 ) представлены литературные источники и базы, 308.47kb.

- Анализ методической работы мбоу «сош №15» за 2010 2011 учебный год, 197.04kb.

- Курсовая работа, 193.69kb.

- Удк 519. 816 Способ представления термов в логике предикатов первого порядка. Алгоритм, 184.64kb.

- Техническое задание мбоу толстомысенской сош №7: «Варианты учебных планов подростковой, 160.12kb.

- М. М. Розенталь принципы диалектической логики глава V понятие в диалектической логике, 1324.47kb.

- Интернет, как информационно-образовательная среда, 70.95kb.

- Доклады и тезисы представлены в авторской редакции. Сподробными материалами конференции, 2528.5kb.

КДУ.

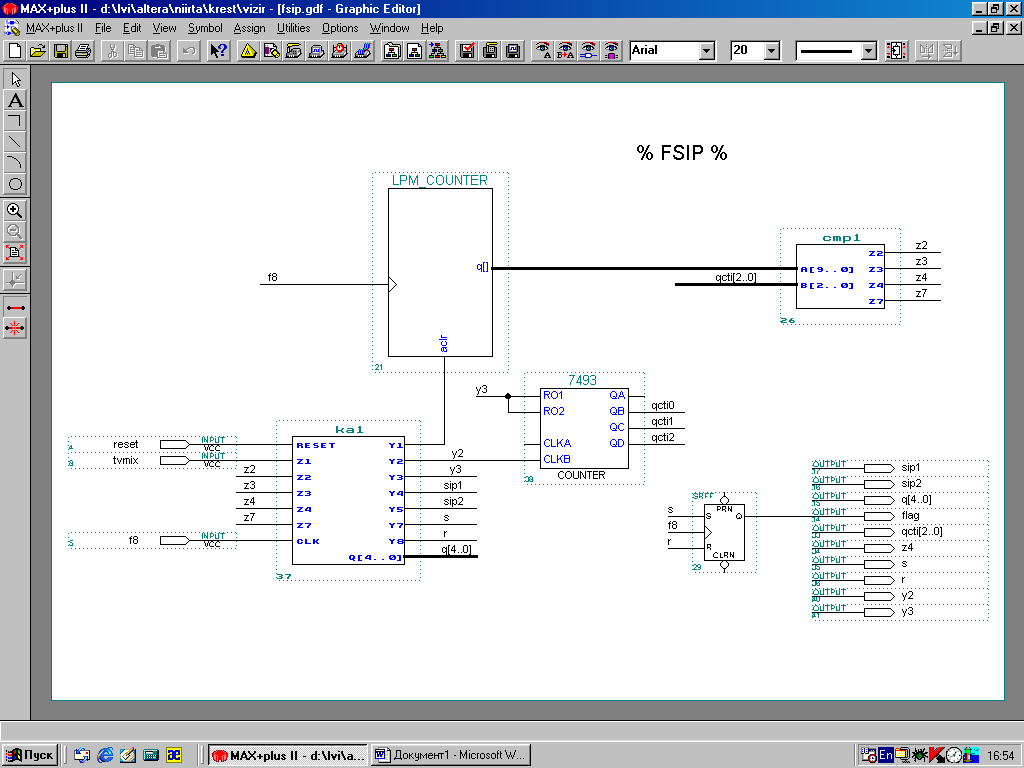

Телевизионный цифровой синхрогенератор.

title "comparator";

constant c32=20;

constant c64=40;

SUBDESIGN cmp1

(

a[9..0],b[2..0]: input; % вход от Т64,вход от СТИ %

z2,z3,z4,z7 : output;%32мкс,64мкс,5имп.,пауза>25мкс%

)

BEGIN

z2 = (a[] > 255-c32)&(a[] < 255+c32);

z3 = (a[] > 511-c64)&(a[] < 511+c64);

z4 = (b[] == 5);

z7 = (a[] > 200);

end;

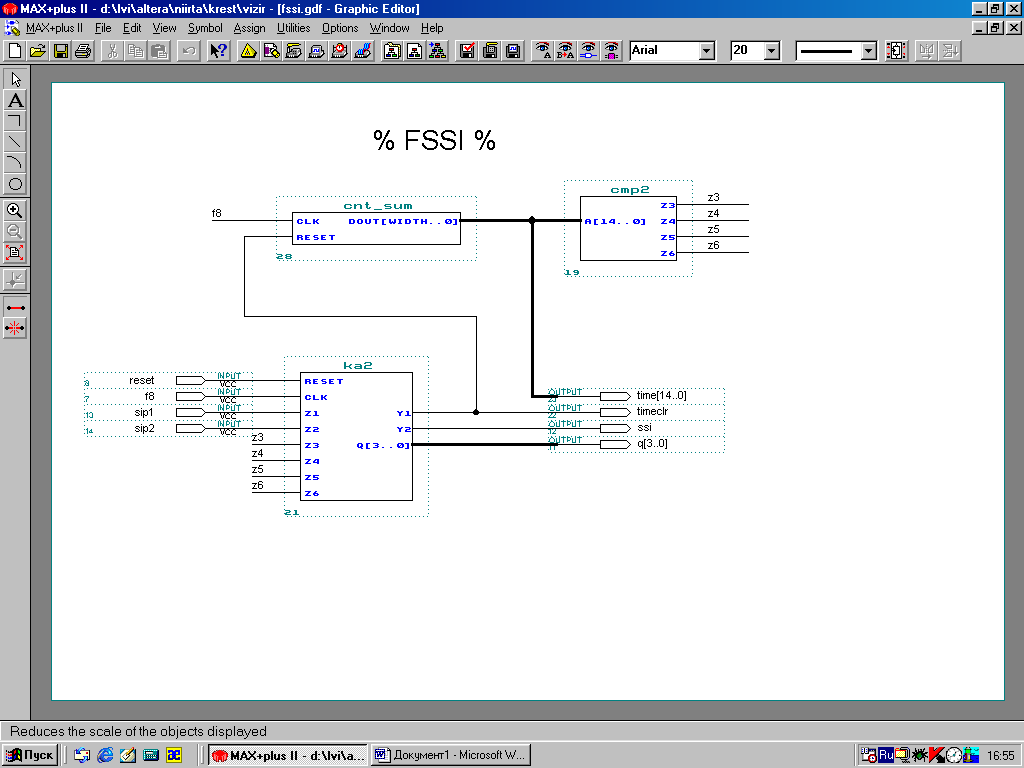

title "cmp2";

constant t4=30;% 4мкс %

constant t64=479;% 60мкс %

constant t672=5376;% 672мкс %

constant t640=5120;%640мкс %

SUBDESIGN cmp2

( a[14..0] : input; % вход от Т1280 %

z3,z4,z5,z6 : output;% 672мкс,640мкс,60мкс,4мкс%

)

BEGIN

z3 = a[] == t672;

z4 = a[] == t640;

z5 = a[] == t64;

z6 = a[] == t4;

end;

end;

TITLE "Timer";

parameters (width = 15);

assert (width >= 0)

report "Значение параметра должно быть больше чем %" width

severity error;

subdesign cnt_sum

(

clk : input;

reset : input;

dout[width..0] : output;

)

variable

rg[width..0] : dff;

begin

rg[].clrn = !reset;

rg[].clk = clk;

rg[].d = rg[].q+1;

dout[] = rg[].q;

end;

INCLUDE "dff";

SUBDESIGN ka1

(

reset,z1,z2,z3,z4 : INPUT;%сброс RG,видеосмесь,32мкс,64мкс,5имп.%

z7, clk : input; % пауза>25мкс,входная частота 8Мгц%

y1,y2,y3,y4,y5: output;%сброс Т64,имп-с счёта для СТИ,сброс СТИ,%

% СИП-1,СИП-2%

y7,y8,q[4..0]: OUTPUT;%уст.флаг,сбросить флаг,выходы RG%

)

VARIABLE

q[4..0] : DFF;

d[4..0] : NODE;% D- входы RG %

BEGIN

q[].clk = clk;

q[].clrn = reset;

q[].prn = VCC;

q[] = d[];

table

q[4..0], z7, z4, z3, z2, z1 => d[4..0];

0 , x , x , x , x , 0 => 0;

0 , x , x , x , x , 1 => 1;

1 , x , x , x , x , 1 => 1;

1 , x , x , x , x , 0 => 2;

2 , x , x , x , x , 0 => 2;

4 , x , x , x , x , x => 2;

14 , x , x , x , x , x => 2;

2 , x , x , x , x , 1 => 3;

3 , x , x , x , x , 1 => 3;% ТОП МПА %

3 , x , x , 0 , x , 0 => 4;

3 , x , x , 1 , x , 0 => 5;

5 , x , x , x , x , x => 6;

6 , x , x , x , x , 0 => 6;

7 , x , x , x , 0 , 0 => 5;

6 , x , x , x , x , 1 => 7;

7 , x , x , x , x , 1 => 7;

7 , x , x , x , 1 , 0 => 8;

10 , x , x , x , x , 0 => 8;

8 , x , x , x , x , x => 9;

9 , x , x , x , x , 0 => 9;

9 , 0 , x , x , x , 1 => 10;

10 , x , x , x , x , 1 => 10;

9 , 1 , 1 , x , x , 1 => 11;

18 , x , x , x , x , x => 12;

12 , x , x , x , x , 0 => 12;

13 , x , 0 , x , x , 0 => 12;

12 , x , x , x , x , 1 => 13;

13 , x , x , x , x , 1 => 13;

13 , x , 1 , x , x , 0 => 14;

17 , x , 1 , x , x , 0 => 14;

9 , 1 , 0 , x , x , 1 => 15;

19 , x , x , x , x , x => 16;

16 , x , x , x , x , 0 => 16;

17 , x , 0 , x , x , 0 => 16;

16 , x , x , x , x , 1 => 17;

17 , x , x , x , x , 1 => 17;

11 , x , x , x , x , x => 18;

15 , x , x , x , x , x => 19;

end table;

table

q[4..0] => y1,y2,y3,y4,y5,y7,y8;

0 => 1, 0, 1, 0, 0, 0, 1;

1 => 1, 0, 0, 0, 0, 0, 0;

2 => 0, 0, 1, 0, 0, 0, 0;

3 => 0, 0, 0, 0, 0, 0, 0; % выходные функции %

4 => 1, 0, 0, 0, 0, 0, 0;

5 => 1, 0, 0, 0, 0, 0, 0;

6 => 0, 0, 0, 0, 0, 0, 0;

7 => 0, 0, 0, 0, 0, 0, 0;

8 => 1, 1, 0, 0, 0, 0, 0;

9 => 0, 0, 0, 0, 0, 0, 0;

10 => 0, 0, 0, 0, 0, 0, 0;

11 => 0, 0, 1, 0, 1, 1, 0;

12 => 0, 1, 0, 0, 1, 0, 0;

13 => 0, 0, 0, 0, 1, 0, 0;

14 => 1, 0, 0, 0, 0, 0, 0;

15 => 0, 0, 1, 1, 0, 0, 1;

16 => 0, 1, 0, 1, 0, 0, 0;

17 => 0, 0, 0, 1, 0, 0, 0;

18 => 0, 0, 0, 0, 1, 0, 0;

19 => 0, 0, 0, 1, 0, 0, 0;

end table;

end;

title "FSSI";

INCLUDE "dff";

SUBDESIGN ka2

( reset,clk,z1,z2 :INPUT;%сброс RG,вх.частота 8Мгц,СИП-1,СИП-2%

z3,z4,z5,z6 :input;% 672мкс,640мкс,60мкс,4мкс%

y1,y2,q[3..0]:output;%сброс Т1280,ССИ,вых.RG%

)

VARIABLE

q[3..0] : DFF;

d[3..0] : NODE;% D- входы RG %

BEGIN

q[].clk = clk;

q[].clrn = reset;

q[].prn = VCC;

q[] = d[];

table

q[3..0], z6, z5, z4, z3, z2, z1 => d[3..0];

0 , x , x , x , x , 0 , 0 => 0;

0 , x , x , x , x , x , 1 => 1;

1 , x , x , x , x , x , 1 => 1;

10 , x , x , x , x , x , 1 => 1;

1 , x , x , x , x , x , 0 => 2;

2 , x , x , x , 0 , x , x => 2;

2 , x , x , x , 1 , x , x => 3;

5 , x , 1 , x , x , 0 , x => 3;

3 , x , x , x , x , x , x => 4;

4 , 0 , x , x , x , x , x => 4;

4 , 1 , x , x , x , x , x => 11;

11 , x , x , x , x , x , x => 5;% ТОП МПА %

5 , x , 0 , x , x , x , x => 5;

5 , x , 1 , x , x , 1 , x => 6;

0 , x , x , x , x , 1 , 0 => 6;

6 , x , x , x , x , 1 , x => 6;

6 , x , x , x , x , 0 , x => 7;

7 , x , x , 0 , x , x , x => 7;

7 , x , x , 1 , x , x , x => 8;

10 , x , 1 , x , x , x , 0 => 8;

8 , x , x , x , x , x , x => 9;

9 , 0 , x , x , x , x , x => 9;

9 , 1 , x , x , x , x , x => 12;

12 , x , x , x , x , x , x => 10;

10 , x , 0 , x , x , x , x => 10;

end table;

table

q[3..0] => y1,y2;

0 => 1, 0;

1 => 1, 0;

2 => 0, 0;

3 => 1, 0;

4 => 0, 0;

5 => 0, 1; % выходные функции %

6 => 1, 0;

7 => 0, 0;

8 => 1, 0;

9 => 0, 0;

10 => 0, 1;

11 => 1, 1;

12 => 1, 1;

end table;

end;