Популяризаторские работы по Русской логике представлены на сайте

| Вид материала | Изложение |

- Программа и описание курса Лекция «Андеррайтинг владельцев бизнеса» Специфика работы, 74.06kb.

- Которая была проведена с участием редакции сайта «Политучеба», 830.24kb.

- Оценка программы Вданной лекции ( шаг 2 ) представлены литературные источники и базы, 308.47kb.

- Анализ методической работы мбоу «сош №15» за 2010 2011 учебный год, 197.04kb.

- Курсовая работа, 193.69kb.

- Удк 519. 816 Способ представления термов в логике предикатов первого порядка. Алгоритм, 184.64kb.

- Техническое задание мбоу толстомысенской сош №7: «Варианты учебных планов подростковой, 160.12kb.

- М. М. Розенталь принципы диалектической логики глава V понятие в диалектической логике, 1324.47kb.

- Интернет, как информационно-образовательная среда, 70.95kb.

- Доклады и тезисы представлены в авторской редакции. Сподробными материалами конференции, 2528.5kb.

Синтезатор частоты.

Синтезатор частоты (СЧ) построен на ИМС фирмы Analog Device AD9854. Она имеет два выхода, один из них квадратурный. По двум каналам установлены ФНЧ и усилители мощности. Этот узел обладает высокой универсальностью. Он может быть использован в цифровых телевизионных и радиопередатчиках, в телевизионных генераторах испытательных сигналов (ГИС). Принципиальная схема СЧ представлена на рисунке.

Особенности создания проекта для БМК.

Прежде, чем приступать к проектированию цифрового устройства (ЦУ) на БМК, необходимо разработать его на основе ПЛИС. Поскольку у меня есть опыт работы с ПЛИС лишь ф. Altera, то речь будет идти о комплектующих и инструментарии этой фирмы. Для относительно несложных проектов вполне достаточно САПР MAX+PLUS II. Если в вашем ЦУ предполагается использование нескольких быстродействующих процессоров, то, учитывая требования технологии «система на кристалле» (System on Chip – SoC), следует отдать предпочтение САПР Excalibur.

Проект должен быть выполнен в тексто-графическом формате [26], что обеспечит его «прозрачность». Разработка ЦУ является микропрограммированием, т.е. ей присущи все недостатки мини-, миди- и макропрограммирования (ассемблеры и языки высокого уровня): невозможно создать «прозрачную» текстовую программу, особенно, если её листинг превышает сотню страниц. Тексто-графическое исполнение облегчает выполнение требований по структурированному программированию. Кстати, обязательное требование размещения любого блока, модуля и т.п. в одном экране. Это облегчит восприятие проекта в целом.

В качестве языков микропрограммирования используются AHDL, VHDL, VeryLog. Самым простым и самым популярным из них является AHDL. Автор также отдаёт предпочтение этому языку (чем проще, тем талантливее). Однако в качестве стандарта принят VHDL. Фирмы, владеющие технологиями БМК, весьма неохотно берут проекты, выполненные на AHDL. Фирма «Ангстрем», наиболее серьёзное предприятие, имеющее многолетний опыт разработок на основе БМК, разместила информацию о своих возможностях на сайте rem.ru.

Прежде, чем передавать проект для реализации на БМК, рекомендуется проверить его в макетном исполнении на ПЛИС. И только при остром цейтноте можно пропустить этот этап. Перевод проекта из системы MAX+PLUS II в OrCAD представляет дополнительную головную боль. Правда, если вам удастся договориться с ф. «Ангстрем», то эту неблагодарную работу за дополнительную плату фирма возьмёт на себя. Полная верификация проекта с учётом реальных задержек также выполняется в OrCAD. Вполне возможно, что после верификации вам придётся заняться подгонкой схемы под заданное быстродействие.

При бортовом исполнении проекта следует обратить самое пристальное внимание на радиационную стойкость: этот параметр должен быть 2У, во всяком случае не хуже 1У.

Контролепригодность.

Появление стандарта на контролепригодность [4,54] ПЛИС, БМК и т.п. предопределило введение тестового порта с сигналами: CLK (тактовая частота тестирования), TMS (разрешение тестирования), TDI (вход тестовых данных) и TDO (выход тестовых данных).

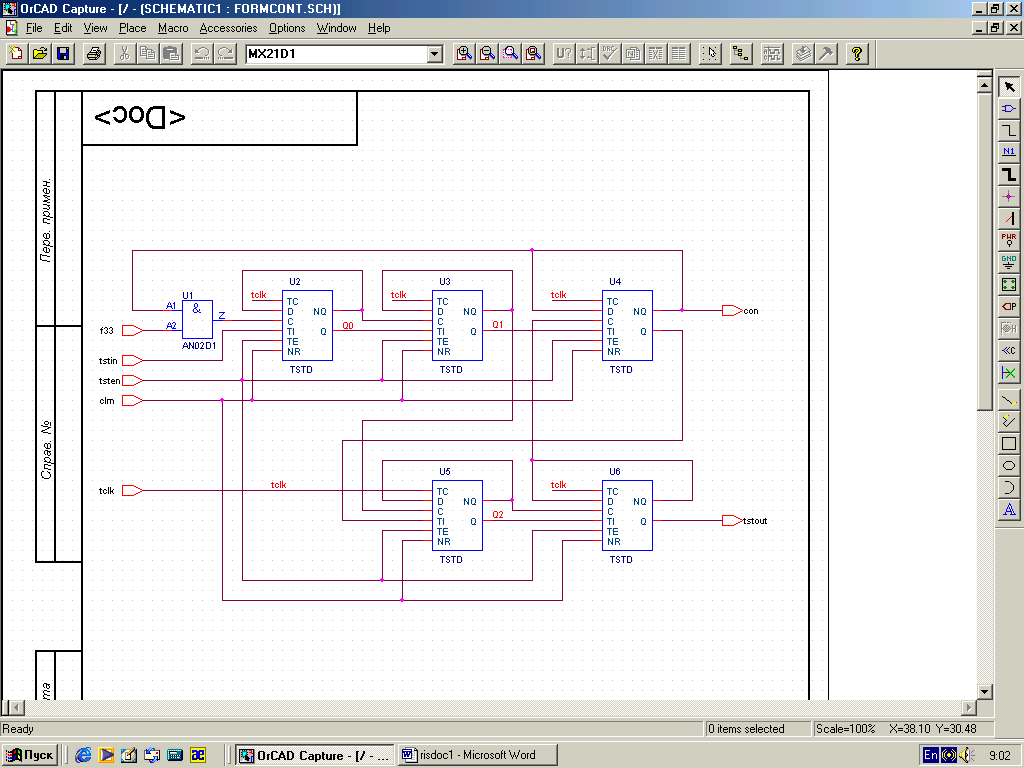

Схема одного из вариантов тестируемого триггера [34] представлена на рисунке 1, счётчик на основе этого триггера изображён на рис. 2.

Рис.1. Схема тестируемого D-триггера.

Рис.2. Схема тестируемого счётчика.

На рис.1 использованы следующие обозначения: С (рабочая частота тактирования), ТC (тактовая частота тестирования), TЕ (разрешение тестирования), D (вход рабочих данных), TI (вход тестовых данных) и TDO (выход тестовых данных), NR (активно-низкий сброс).

Разумеется, на основе тестируемого триггера можно построить не только счётчик, но и любой микропрограммный автомат (МПА). Однако, пока не будет создана соответствующая библиотека стандартных тестируемых элементов с оптимальной топологией, все усилия разработчика по обеспечению контролепригодности будут тщетны.

Использование сквозной линии : CLK и TMS требует использование глобальных связей. Такая возможность предусмотрена в ПЛИС ф. “Altera”, но её нет в БМК ф. «Ангстрем». Кроме того, в САПР «Ангстрем» до сих пор в библиотеке стандартных элементов нет контролепригодных элементов памяти (ЭП). С большим трудом удалось доказать безусловную необходимость таких программ. Такая «недальновидность» характерна для всех известных мне отечественных разработчиков. Всё, что реализовано на БМК с использованием ЭП (более 100 проектов), неконтролепригодно. Кстати, это в первую очередь должен знать Заказчик, поскольку в противном случае все заверения разработчика о том, что он гарантирует хоть какую-то полноту контроля, являются блефом. Обычно наш Заказчик требует 80%-полноту контроля. САПР моделирования неисправностей и проверки полноты контроля типа CAMELOT не всем по карману, поэтому мы всю жизнь обманывали друг друга. Заказчик же делал вид, что нам верил. В настоящее время такое положение вещей недопустимо. Раньше мы оправдывали свою беспомощность большими аппаратными затратами, теперь этого «козыря» у разработчиков нет.

Несколько слов о JTAG-интерфейсе. Несмотря на все его достоинства [34], он не обеспечивает входной контроль БМК. Поэтому, получив БМК от изготовителя, вы не сумеете убедиться в его исправности, если не выполните все те требования, о которых говорилось выше.

До сих пор все разработки с точки зрения контролепригодности вопиюще безграмотны. При проектировании топологии заказных КМОП БИС даже не рассматривается структура тестируемого триггера (“Chip News, №2, 2003, с.5-13). Разработки на БМК даже у профессионалов советской выучки грешат подобными недостатками. Поэтому я настоятельно рекомендую руководителям разрабатывающих подразделений введение аттестации цифровиков хотя бы в объёме «Азбуки разработчика цифровых устройств» [37]. Более того, вполне допустим анализ уровня исполнения проекта внешними разработчиками-профессионалами. Требуется введение вневедомственной ревизионной службы по контролю технического уровня исполнения проекта (цифровой и аналоговой части, помехозащите, стыковке ПЛИС и БМК с МП и т.п.), в том числе и по контролепригодности с полнотой тестирования.

Вслед за контролепригодностью возникает проблема синтеза тестов. Имея контролепригодную схему, можно автоматизировать в определённой степени синтез тестов. Для этого САПР должна уметь на основе введённой схемы строить тест для заранее заданных наборов сигналов на входах определённого элемента схемы. Теоретически можно построить тест, эквивалентный тривиальному, т.е. со 100% - полнотой контроля. Длина такого теста может быть вполне разумной. Одновременно с решением вопросов контролепригодности, необходимо предусмотреть и самодиагностируемость(LSSD, BILBO). Все эти проблемы подробно рассмотрены в прекрасной книге Беннетса [4], перевод которой выполнил профессионал в области диагностики, проф. ХПИ Леонид Викторович Дербунович.

8.2. О недостатках САПР MAX+PLUS II.

Широкое внедрение ПЛИС фирмы Altera в практику цифровых разработок связано не только с достоинствами этих микросхем, но и не в последнюю очередь с появлением отечественной литературы по данному вопросу[2]. Десять лет тому назад появление САПР ПЛИС Xilinx сопровождалось такими сложностями, что применять эту систему в практических разработках не было ни малейшего желания. В прекрасном практическом курсе [2] не только разобран весь процесс проектирования, но ещё и приложен компакт-диск с самой САПР. Это уже выше всех ожиданий, поскольку покупка MAX+PLUS II обошлась бы разработчику в $1000.

Но как же поступают наши и зарубежные разработчики, получив в руки такое мощное оружие. Очень просто: они рисуют схемы в графическом редакторе. В МИФИ такой подход называют вентильным мышлением. Я называю подобный метод технологией мартышки с арифмометром. Обиднее всего то, что данную «технологию» используют безусловно талантливые и высокопрофессиональные разработчики с прекрасной математической подготовкой.

Слабым утешением может служить тот факт, что зарубежные цифровики ещё более безграмотны. У отечественных разработчиков начинает просыпаться интерес к синтезу микропрограммных автоматов, хотя это и происходит спустя 30 лет после выхода в печать популяризаторских работ[3,22].

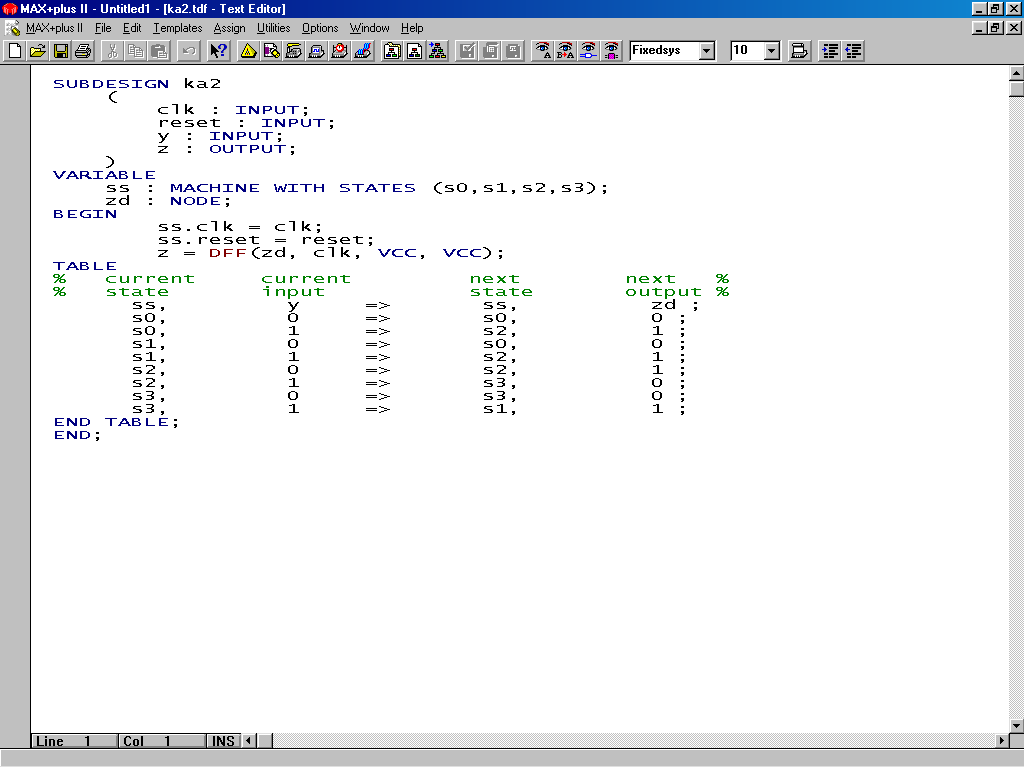

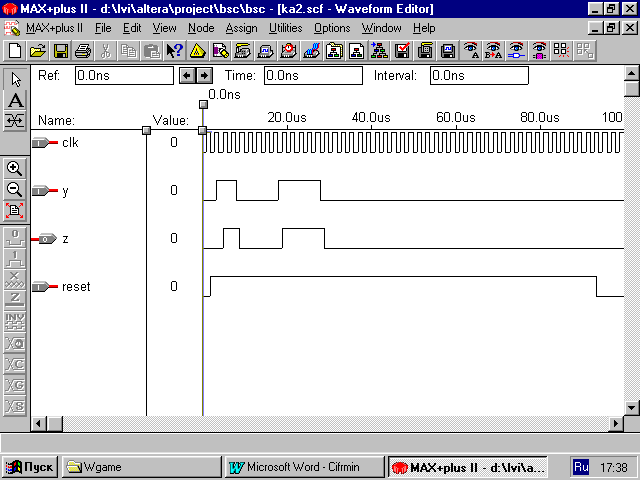

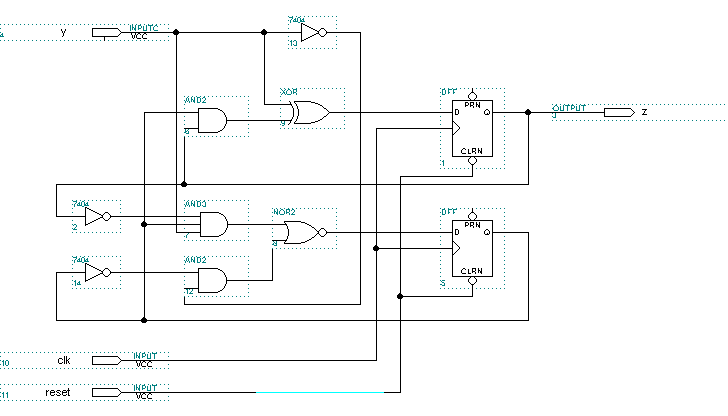

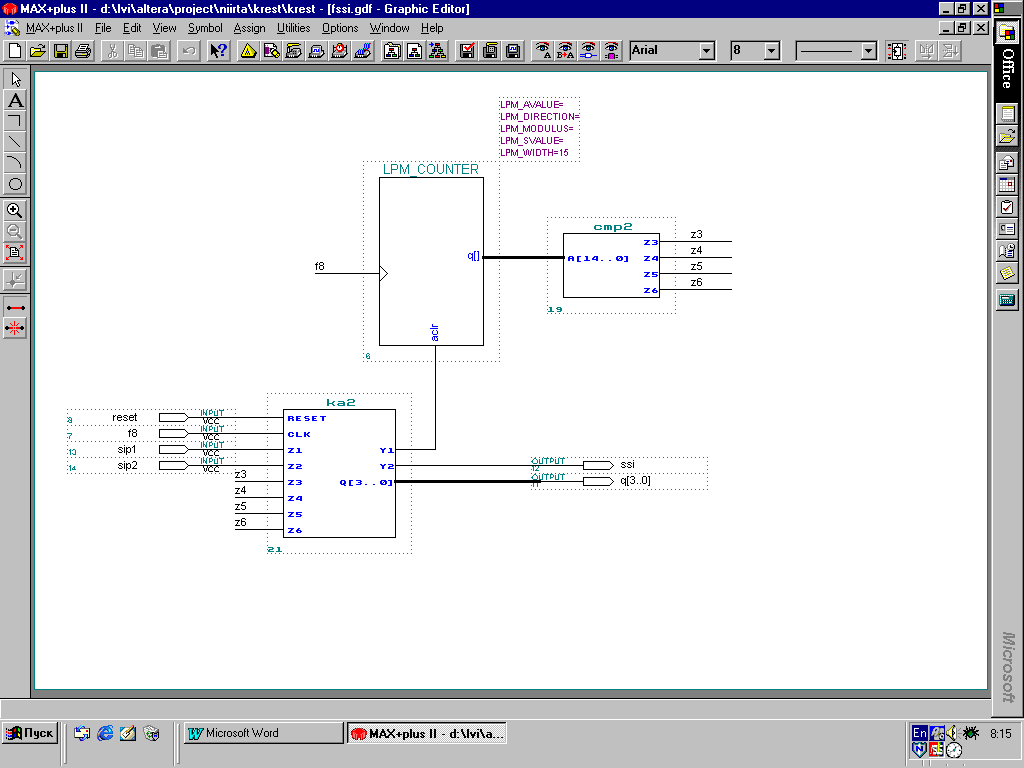

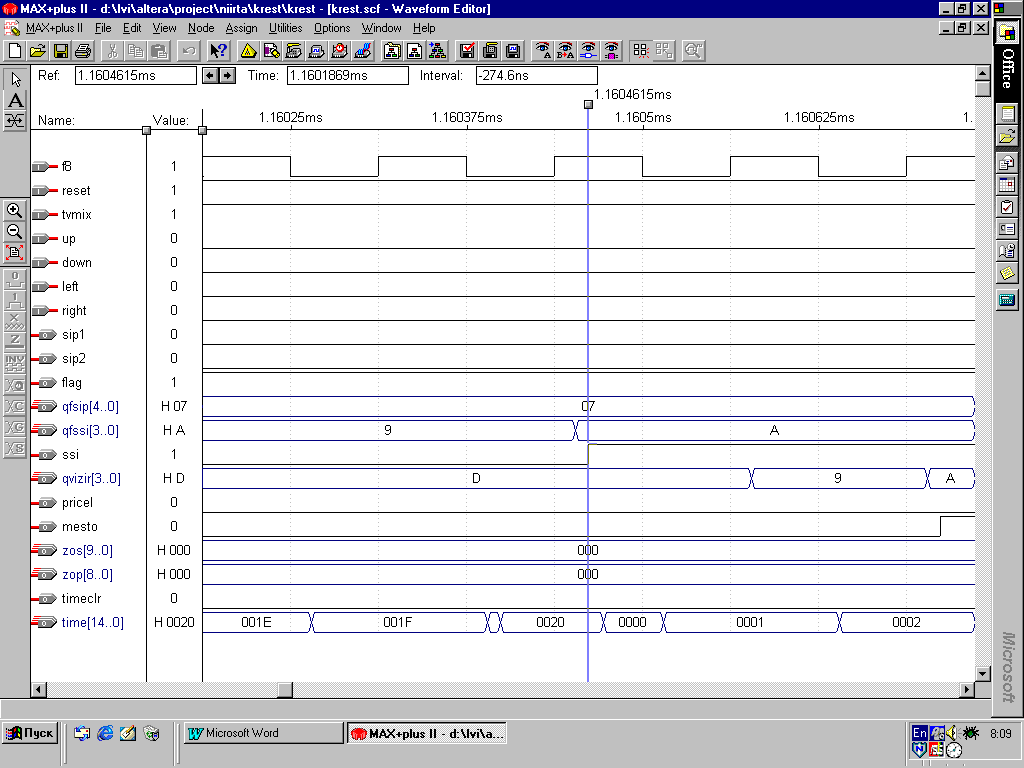

А «передовой Запад» демонстрирует своё невежество даже в таком суперважном программном продукте как MAX+PLUS II. На рис. 1 представлен файл ka2.tdf(в оригинале moore2.tdf) микропрограммного автомата(МПА), позаимствованный из фирменных материалов. После трансляции файла ka2.tdf и симуляции файла ka2.scf были получены временные диаграммы работы этого МПА(рис.2). Если не полениться и вручную проверить работу описанного в файле ka2.tdf МПА, то мы получим иные временные диаграммы (рис.3). Кстати, пришлось вначале формально построить МПА, а потом нарисовать его схему в графическом редакторе (рис.4). Симулятор и в данном случае подтвердил промашку фирмы. После анализа огрехов фирмы Altera был найден способ автоматического решения проблемы. Это фундаментальная ошибка, поскольку она не позволяет использовать формальный синтез МПА. Подобная оплошность свидетельствует не только о беспомощности разработчиков фирмы, но и о безграмотности западных цифровиков, т.к. вопиющая ошибка не была обнаружена за рубежом вплоть до появления САПР в России, т.е. в течение по меньшей мере 5 лет.

SUBDESIGN ka2

(

clk : INPUT;

reset : INPUT;

y : INPUT;

z : OUTPUT;

)

VARIABLE

ss : MACHINE WITH STATES (s0,s1,s2,s3);

zd : NODE;

BEGIN

ss.clk = clk;

ss.reset = reset;

z = DFF(zd, clk, VCC, VCC);

TABLE

% current current next next %

% state input state output %

ss, y => ss, zd ;

s0, 0 => s0, 0 ;

s0, 1 => s2, 1 ;

s1, 0 => s0, 0 ;

s1, 1 => s2, 1 ;

s2, 0 => s2, 1 ;

s2, 1 => s3, 0 ;

s3, 0 => s3, 0 ;

s3, 1 => s1, 1 ;

END TABLE;

END;

Р

ис. 1

Р

ис. 2

Рис. 3

Рис.4

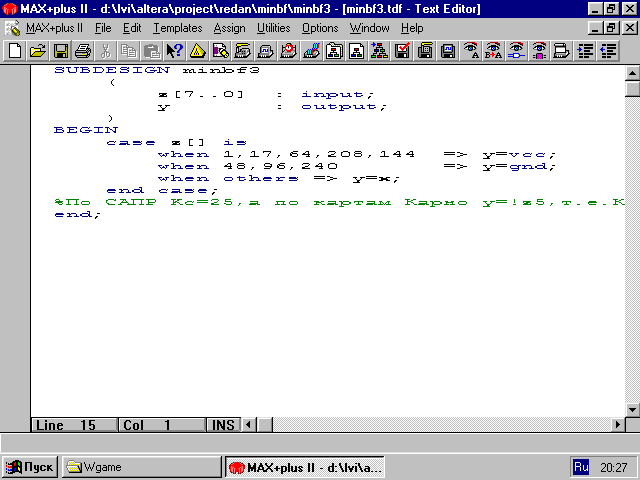

П

роверим работу САПР на примере минимизации логической функции от 8 переменных. Функция У задана таблицей истинности в виде 10-чных и двоичных наборов z(10), z(2) соответственно.

| Z(10) | Z(2) | Y |

| 1 | 00000001 | 1 |

| 17 | 00010001 | 1 |

| 64 | 01000000 | 1 |

| 208 | 11010000 | 1 |

| 144 | 10010000 | 1 |

| 48 | 00110000 | 0 |

| 96 | 01100000 | 0 |

| 240 | 11110000 | 0 |

После минимизации по методу обобщённых кодов[22] получаем результат:

Y = z5’, где апостроф означает инверсию, что в 25 раз проще функции, выданной САПР MAX+PLUS II.

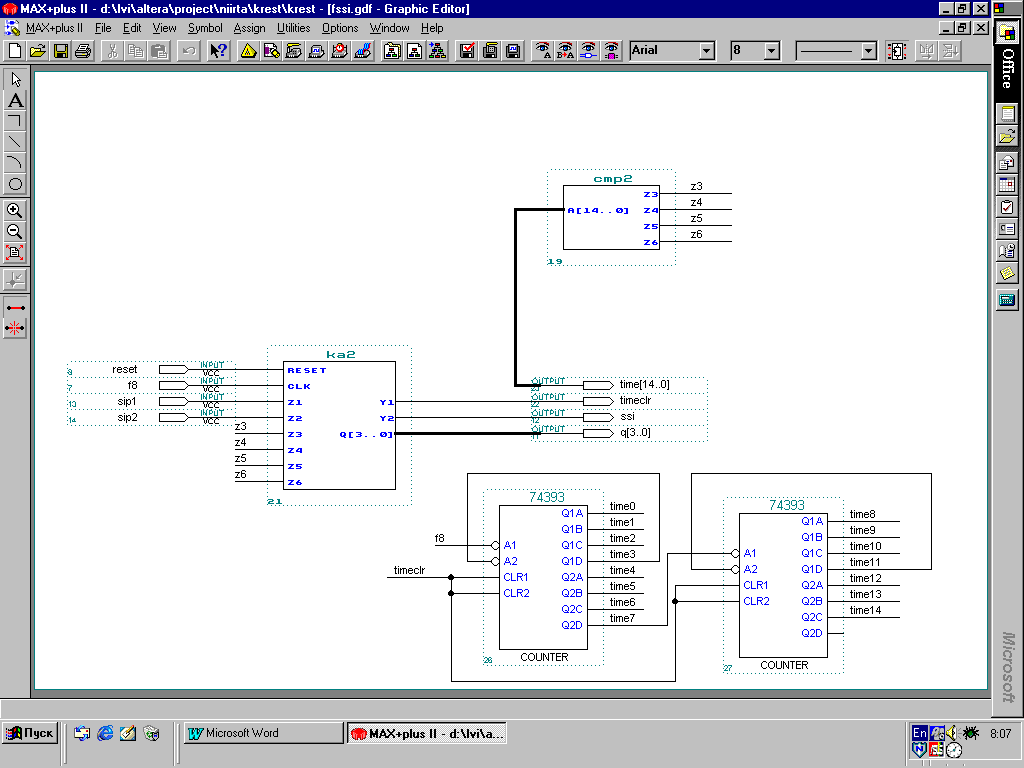

Дополнительный недостаток САПР заключается ещё и в том, что некоторые мегафункции некорректно работают в определённых ситуациях(например, LPM_COUNTER в проектах fssi.gdf, fsip.gdf). Приходится заменять их на стандартные счётчики. Иногда и эта мера не спасает – приходится менять алгоритм работы автомата, вводя лишний, ничем не мотивированный сброс.

Кроме того, реализация SR-триггера на элементах ИЛИ-НЕ также привела к непредсказуемым эффектам. Пришлось заменить на стандартный SR-триггер из библиотеки элементов(см. fsip.gdf).

Вызывает нарекания пользователей и работа с двухпортовой памятью(см. probaram.tdf). При трансляции, например, запрашивается количество выводов ПЛИС.

Мой опыт работы с САПР MAX+PLUS II относительно невелик. Однако он не помешал в течение одной недели выловить глобальную погрешность САПР ф. Altera. Это говорит, во-первых, о простоте AHDL и САПР в целом, а во-вторых, о жёсткой необходимости владения инструментом формального синтеза МПА. Общий стаж цифровых разработок составляет более четверти века, что позволяет мне высказать некоторые рекомендации.

Во-первых, профессионал – это не тот, кто всё знает, а тот специалист, кто умеет ориентироваться в море информации и осваивать новые перспективные направления.

Во-вторых, при освоениии новых технологий, дабы не превратиться в мартышку с арифмометром, нужно знать азбуку своей профессии. Для цифровика эта азбука заключается в следующем:

- Алгебра логики.

- Карты Карно на 8 - 12 переменных как наиболее эффективный способ ручной минимизации Булевых функций.

- Метод обобщённых кодов как наиболее эффективный машинный метод минимизации Булевых функций от большого числа переменных(32 и более).

- Формальный синтез МПА.

- Эвристические методы синтеза последовательностных схем.

Без знания этих основ цифровик не имеет права на звание инженера. Синтез МПА фундаментально и элегантно изложен в [3]. Однако эта элегантность и математическая строгость не позволили подавляющему большинству инженеров освоить формальный синтез. Эвристические методы прекрасно и просто описаны у Гутникова[14].

Метод обобщённых кодов был разработан в конце 60-х годов на 21-й кафедре Академии им. Дзержинского д. т. н. Мавренковым Леонидом Трофимовичем. Дальнейшее развитие метода и доведение его до инженерных методик было выполнено сотрудниками этой кафедры к.т.н. Кустенко А.С., к.т.н. Кузнецовым Н.В. и к.т.н. Салтыковым Ю.А.(см. "Вопросы оборонной техники", 1972 г.).

Все 5 пунктов «цифрового букваря» достаточно просто изложены в техническом руководстве по материалам лекций, прочитанных автором в 1976г. для ведущих специалистов НИИРТА[22], а также в “Азбуке разработчика цифровых устройств”[37].

Кроме вышеперечисленного ликбеза разработчику-цифровику необходимо осваивать и классическую логику. Связано это с тем, что 21 век называют веком искусственного интеллекта (ИИ). Задачи ИИ будут решать цифровики. Но фундаментом ИИ являются логика суждений и силлогистика. Классическая мировая логика в этом плане дремуче невежественна. Проблемы этих дисциплин с инженерной точки зрения абсолютно прозрачны и впервые решены в России[27 – 43], а также на сайте narod.ru], посему их результатами первыми должны воспользоваться российские инженеры.

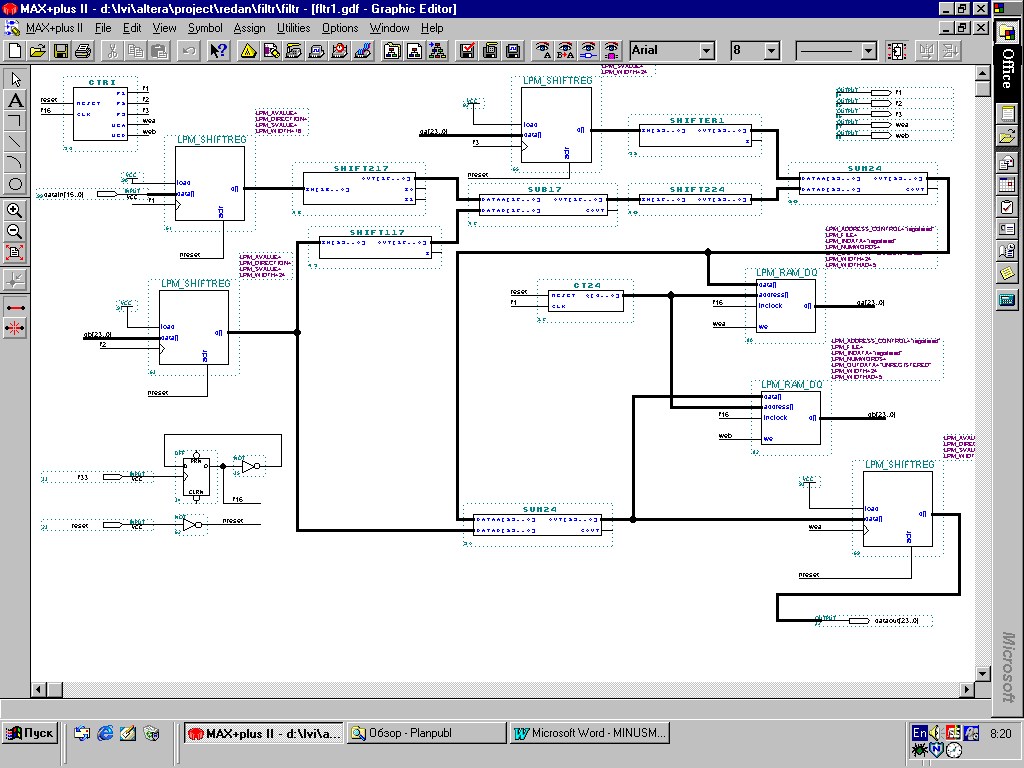

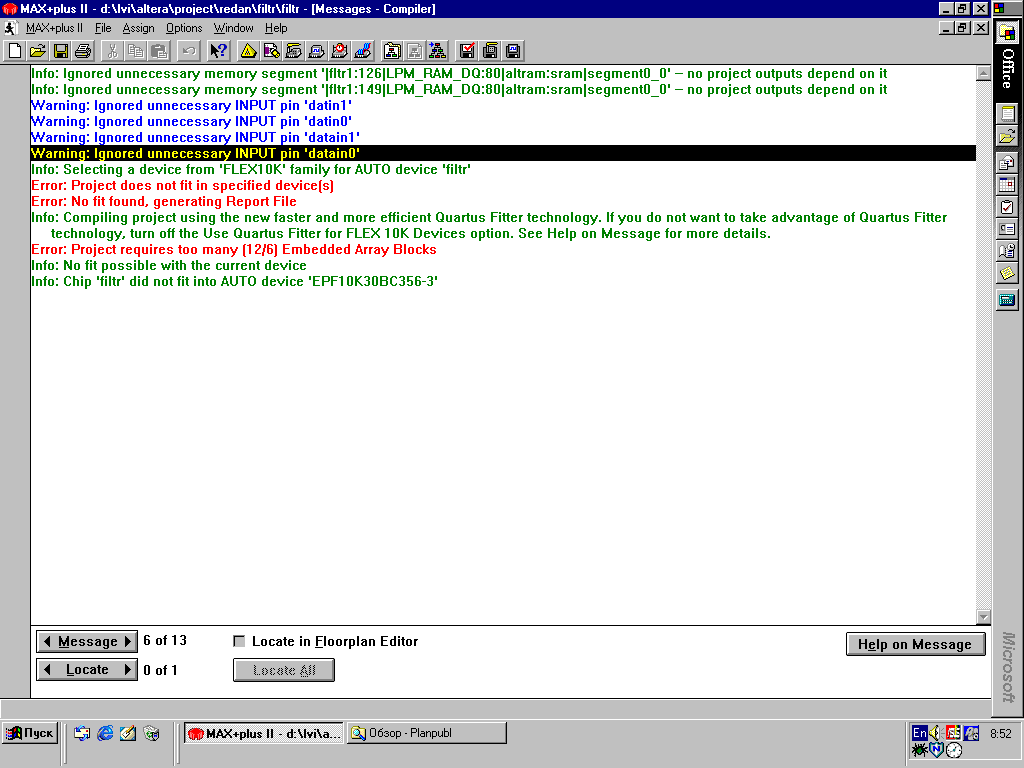

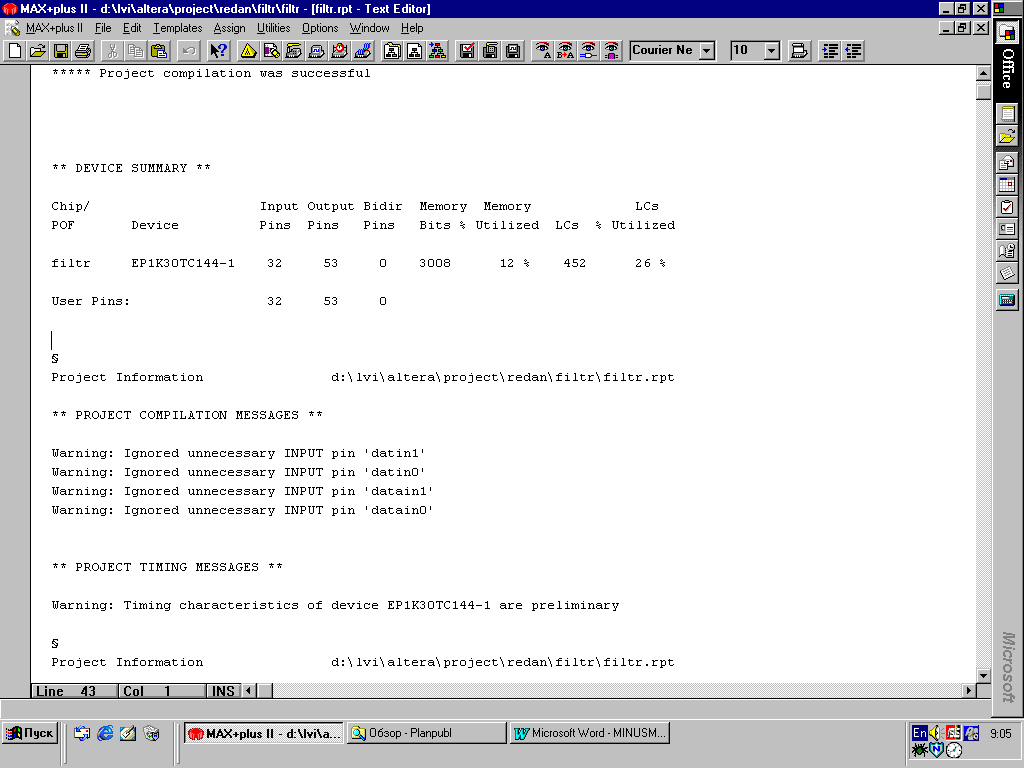

На вышеприведённом рисунке представлен проект цифрового фильтра второго порядка. После трансляции он занял 25% объёма ПЛИС EPF10K20. После добавления к нему аналогичного фильтра FLTR1.GDF, т.е. тоже 25% объёма EPF10K20, была получена схема:

Вместо ожидаемых 50% транслятор выдал сообщение о нехватке памяти. После замены EPF10K20 на ACEX1K(EP1K30TC144-1) трансляция прошла успешно.

** DEVICE SUMMARY **

Chip/ Input Output Bidir Memory Memory LCs

POF Device Pins Pins Pins Bits % Utilized LCs % Utilized

filtr EP1K30TC144-1 32 53 0 3008 12 % 452 26 %

User Pins: 32 53 0

§

Project Information d:\lvi\altera\project\redan\filtr\filtr.rpt

Из распечатки файла filtr.rpt видно, что проект занял бы не более 50% ПЛИС EPF10K20.

Работа 2-портового ОЗУ вызывает много вопросов(см. ramridp в otv81int, we & !clk = we & clk)

Групповые операции присвоения тоже иногда приводят к неожиданностям.

SUBDESIGN karam1

% контроллер динамической памяти %

(

z1,z2,z3,z4,z5 : input;% RESET,прошли 4096 тактов,2 тактa,WRITE,READ %

z6,z7,z8,clk : input;% прошли 3 тактa,прошли 507 тактов,kr %

y1,y2,y3,y4,y5,y6,y8 : output;% nWE,nRAS,nCAS,nCS,DQM,CKE,запуск таймера %

y9,y10,y11,y12,y13,y14 : output; % A10,READY - готовность к работе,выдать адрес 0227h,выдать AdrStr,выдать AdrBank,выдать AdrStlb %

y15,y16,y17,y18,y19 : output; % сигнал готовности данных для записи в ОЗУ,EOW-End of Write,EOR-End of Read,A[10..9]/A[1..0],Fcta %

q[5..0] : output;% вых. регистра КА %

)

VARIABLE

q[5..0],qy[19..1] : DFF;

d[5..0],dy[19..1],f[19..1] : NODE;% d - входы RG %

BEGIN

q[].clk = clk;

q[].clrn = !z1;

q[].prn = VCC;

q[].d = d[];

qy[].clk = clk;

qy[].clrn = !z1;

qy[].prn = VCC;

qy[].d = dy[];

table

q[5..0],z8,z7,z6,z5,z4,z3,z2,z1 => d[5..0];

11 , x, x, x, x, x, x, x, 1 => 0;

0 , x, x, x, x, x, x, x, 1 => 0;

0 , x, x, x, x, x, x, x, 0 => 1;

1 , x, x, x, x, x, x, 0, x => 1;

1 , x, x, x, x, x, x, 1, x => 2;

2 , x, x, x, x, x, x, x, x => 3;

3 , x, x, x, x, x, x, x, x => 4;

4 , x, x, x, x, x, 0, x, x => 4;

4 , x, x, x, x, x, 1, x, x => 5;

5 , x, x, x, x, x, x, x, x => 6;

6 , x, x, x, x, x, 0, x, x => 6;

6 , x, x, x, x, x, 1, x, x => 7;

7 , x, x, x, x, x, x, x, x => 8;

8 , x, x, x, x, x, x, x, x => 9;

9 , x, x, x, x, x, x, x, x => 10;

10 , x, x, x, x, x, 0, x, x => 10;

10 , x, x, x, x, x, 1, x, x => 11;

11 , x, x, x, 0, 0, x, x, 0 => 11;

18 , x, x, x, x, x, x, x, x => 11;

37 , x, x, x, x, x, x, x, x => 11;

11 , x, x, x, 0, 1, x, x, 0 => 12;

12 , x, x, x, x, x, x, x, x => 13;

13 , x, x, x, x, x, 0, x, x => 13;

13 , x, x, x, x, x, 1, x, x => 14;

14 , x, x, x, x, x, x, x, x => 15;

15 , x, x, x, x, x, x, x, x => 16;% ТОП МПА %

16 , x, x, x, x, x, x, x, x => 17;

17 , x, x, x, x, x, 0, x, x => 17;

17 , x, x, x, x, x, 1, x, x => 18;

11 , x, x, x, 1, x, x, x, 0 => 19;

19 , x, x, x, x, x, x, x, x => 20;

20 , x, x, x, x, x, 0, x, x => 20;

20 , x, x, x, x, x, 1, x, x => 21;

21 , x, x, x, x, x, x, x, x => 22;

22 , x, x, x, x, x, x, x, x => 23;

23 , x, x, x, x, x, x, x, x => 24;

24 , x, x, x, x, x, x, x, x => 25;

25 , x, 0, x, x, x, x, x, x => 25;

25 , x, 1, x, x, x, x, x, x => 26;

30 , 0, 1, x, x, x, x, x, x => 26;

26 , x, x, x, x, x, x, x, x => 27;

27 , x, x, x, x, x, x, x, x => 28;

28 , x, x, x, x, x, x, x, x => 29;

29 , x, x, x, x, x, x, x, x => 30;

30 , x, 0, x, x, x, x, x, x => 30;

30 , 1, 1, x, x, x, x, x, x => 31;

31 , x, x, x, x, x, x, x, x => 32;

32 , x, x, x, x, x, 0, x, x => 32;

32 , x, x, x, x, x, 1, x, x => 33;

33 , x, x, x, x, x, x, x, x => 34;

34 , x, x, x, x, x, x, x, x => 35;

35 , x, x, x, x, x, x, x, x => 36;

36 , x, x, x, x, x, x, x, x => 37;

end table;

table

q[5..0] => f19,f18,f17,f16,f15,f14,f13,f12,f11,f10,f9,f8,f6,f5,f4,f3,f2,f1;

0 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 0, 0, 0, 0;

1 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 1, 0, 1, 1, 1;

2 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 1, 0, 1, 0, 0, 1, 0, 0;

3 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 0, 0, 0, 1;

4 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

5 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 0, 0, 0, 1;

6 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

7 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 1 , 0 , 0, 0, 1, 0, 0, 0, 0, 1;

8 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 1, 1, 1, 1;

9 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 0, 0, 0, 1;

10 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 0, 0, 1, 1, 1, 1;

11 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 1 , 0, 0, 0, 0, 1, 1, 1, 1;

12 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 0, 1, 1, 1;

13 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

14 => 0 , 0 , 0 , 0 , 0 , 0 , 1 , 1 , 0 , 0 , 0, 0, 1, 0, 0, 1, 0, 1;

15 => 0 , 0 , 0 , 0 , 1 , 1 , 1 , 0 , 0 , 0 , 1, 0, 1, 0, 0, 0, 1, 0;

16 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 0, 0, 0, 1;

17 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 0, 0, 1, 1, 1, 1;

18 => 0 , 0 , 0 , 1 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 1, 1, 1, 1;% таблица выходных функций %

19 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 0, 1, 1, 1;

20 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

21 => 0 , 0 , 0 , 0 , 0 , 0 , 1 , 1 , 0 , 0 , 0, 0, 1, 0, 0, 1, 0, 1;

22 => 0 , 0 , 0 , 0 , 0 , 1 , 1 , 0 , 0 , 0 , 1, 0, 1, 0, 0, 0, 1, 1;

23 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 1, 1, 1, 1;

24 => 0 , 1 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 1, 1, 1, 1;

25 => 1 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

26 => 0 , 0 , 0 , 0 , 0 , 0 , 1 , 1 , 0 , 0 , 0, 0, 1, 0, 0, 1, 0, 1;

27 => 0 , 0 , 0 , 0 , 0 , 1 , 1 , 0 , 0 , 0 , 1, 0, 1, 0, 0, 0, 1, 1;

28 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 1, 1, 1, 1;

29 => 0 , 1 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 0, 0, 0, 1;

30 => 1 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

31 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 1, 0, 1, 1, 1, 1;

32 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 1, 1, 0, 1, 1, 1, 1;

33 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 0, 0, 0, 1;

34 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 1, 1, 1, 1;

35 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 1, 1, 1, 1;

36 => 0 , 0 , 1 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 1, 1, 1, 1;

37 => 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0 , 0, 0, 0, 0, 1, 1, 1, 1;

end table;

dy[6..1] = f[6..1];

dy[19..8] = f[19..8];

dy8 = f8;

dy7 = gnd;

y1 = qy1;

y2 = qy2;

y3 = qy3;

y4 = qy4;

y5 = qy5;

y6 = qy6;

y8 = qy8;

y9 = qy9;

y10= qy10;

y11= qy11;

y12= qy12;

y13= qy13;

y14= qy14;

y15= qy15;

y16= qy16;

y17= qy17;

y18= qy18;

y19= qy19;

end;

8.3. О повышении технического уровня отечественных разработок.

В настоящее время остро ощущается разрыв поколений разработчиков, резко снизился технический уровень НИОКР. Это результат целенаправленного уничтожения морали, культуры, образования, науки, экономики, политики и обороноспособности России, осуществляемого «пятой колонной» по указанию так называемого Всемирного правительства (США). Бороться с этой предательской политикой фактически оккупационного правительства необходимо на всех фронтах, в том числе и на научно-техническом. Задачей старшего поколения инженеров и учёных является передача накопленных знаний молодому поколению патриотов, строителей новой России.

Автор более 30 лет занимался разработками цифровых систем управления, длительное время возглавлял отдел в ЦННИИ «Циклон» (головной институт Минэлектронпрома СССР), внедрял микропроцессоры и вычислительную технику в народное хозяйство, поэтому о советских разработках знает не понаслышке. Если даже в СССР технический уровень проектов был недостаточно высоким, то теперь он опустился до радиолюбительства. Задача старшего поколения проектировщиков заключается в повышении уровня современных разработок и передаче накопленного опыта молодой генерации конструкторов.

В НИИ Дальней Радиосвязи (НИИДАР) сложилась группа разработчиков-профессионалов, имеющих 30 – 40-летний опыт создания систем управления оборонного назначения. Возглавляет группу зам.руководителя НПП «Полигонные системы ПВО» Кашин Ф.А. На его счету разработки систем управления радиовзрывателями (РВ) для ракет (изделия 83В6, 88В6, 98В6, 3В46, 9ЖБ920 – изделие «Крым» и т.п.), а также систем спутниковой навигации и систем полигонных испытаний для головок самонаведения и РВ при работе по движущейся цели. При создании этих систем использовалась как отечественная, так и современная зарубежная элементная база (ПЛИС, микроконтроллеры, синтезаторы частоты и т.п.). В группе обобщён опыт проведения работ НИИРТА (НПО «Импульс», Минсредмаш СССР), ЦНИИ «Циклон» (Минэлектронпром СССР), НПП «Полигонные системы», НПП «Редан» (при ГУП НПП «Регион») и НИИДАР. Эта группа в состоянии выявить недостатки проекта в объёме изделия 88В6 и предложить решения по устранению недостатков в течение 5 дней.

Скопившиеся за последнее десятилетие претензии к уровню цифровых разработок изложены в работах автора [26,31,34,37]. В основном это незнание инженерных и формальных методов синтеза микропрограммных автоматов (МПА), неумение построить тестопригодную систему и тем более разработать тест со 100% - полнотой контроля. Элементарным признаком безграмотной разработки является использование «рассыпной» элементной базы вместо разрешённых к применению БМК, ПЛМ и ПМЛ. В случае применения зарубежных ПЛИС по незнанию игнорируются вопросы стыковки ПЛИС с входными и выходными сигналами. Не решаются вопросы повышения надёжности при спецвоздействиях хотя бы на таком уровне как это сделано в изделии 5Е50.

Многолетний стаж разработок цифровых систем управления в Минсредмаше, разработка и внедрение в народное хозяйство микропроцессорных систем, а также участие в разработках изделий других ведомств оборонного характера позволили накопить определённый практический и теоретический багаж. Программирование на языках высокого уровня (ЯВУ): Фортран, Алгол, Паскаль, Си, Форт, РАЯ и использование не менее двух десятков ассемблеров привело к выводу, что далеко не всё благополучно в стане программистов. Опыт схемотехнического проектирования и постоянные контакты с разработчиками Советского Союза выявили слабую теоретическую подготовку отечественных разработчиков в области синтеза микропрограммных автоматов (МПА). Непродолжительное, к сожалению, взаимодействие с ведущими специалистами СССР в области диагностики, такими как проф. Дербунович Л.В.(ХПИ, г. Харьков), к.т.н. Мызь А.Н.(ХПИ), тем не менее привело к мысли о низком профессиональном уровне разработчиков цифровых систем управления в области обеспечения контролепригодности своих разработок и их тестировании (автор не является исключением).

Уровень современных разработок и элементная база: ПЛИС, сигнальные процессоры и отечественные аналоги.

Сложность современных задач по цифровой обработке информации достигла такого уровня, что говорить о реализации этих проектов на традиционной «рассыпной» элементной базе не приходится. Одна из плат НИР–овского варианта модуля цифровой обработки сигнала имеет в своём составе 6 сигнальных процессоров типа ADSP2181 и 6 ПЛИС FLEX10K20. Использование указанной элементной базы позволило обеспечить массогабаритные и надёжностные требования к изделию. Однако бортовые системы категорически должны строиться на базе отечественных микросхем. МИД в лице своего министра заявило 26.01.03 о возврате к холодной войне. За прошедшие два года ситуация только обострилась.

Проектирование современных цифровых и аналоговых систем управления напоминает зачастую процесс построения домиков из кубиков в детском саду. В целом такая тенденция прогрессивна. Беда лишь в том, что «кубики» эти зарубежные. Однако требования безопасности России диктуют безусловный переход на отечественную элементную базу. Свежий пример: при создании цифрового телевизионного передатчика были использованы весьма неплохие ИС АЦП AD9244, AD7723 и синтезатор AD9854. А теперь наш ОМТС столкнулся с проблемой эмбарго. В советские времена мы с гордостью говорили: «Только СССР и Америка делают всю номенклатуру электронной техники». Ушли те времена, а проблема обеспечения электронной безопасности осталась. В своих разработках мы столкнулись с тем, что Заказчик (а это люди в погонах, защитники России) справедливо и жёстко потребовал от нас перевода предыдущих разработок на отечественную элементную базу. В цифровой и даже аналоговой электронике такой переход возможен лишь за счёт базовых матричных кристаллов (БМК).

Что может в настоящее время предложить разгромленная электронная промышленность России?

В области сигнальных процессоров разработаны в ГУП НПЦ ЭЛВИС двухпроцессорные (RISC – и DSP – ядро) микросхемы Мультикор-11хх (МС-11хх) на основе 0,54-мкм (3 металла) библиотеки отечественного изготовителя ОАО «Ангстрем». Микросхема МС-11Т имеет интеграцию около 2 млн. вентилей и размеры кристалла 10,1х10,1мм. Функциональные возможности Мультикор-11 на уровне сигнального 32-разрядного процессора TMS320VC5470. Опытные образцы МС-11Т получены в IV квартале 2002г. На их основе созданы платы KIT, с помощью которых проверяется работа САПР отладки программного обеспечения для МС-11Т. Автор присутствовал при демонстрации процесса отладки САПР. В конце 2003г. была создана базовая версия инструментального программного обеспечения MCS для СБИС на базе платформы «Мультикор». Демо-версия MCS была любезно предоставлена автору руководством. Вся стратегия проектирования ГУП НПЦ ЭЛВИС чётко вписывается в требования технологии разработок «система на кристалле» (СнК, или SoC).

В настоящее время серийные образцы «Мультикоров» содержат уже 15 млн. транзисторов. Кристаллы были изготовлены по технологии 0,25 мкм и содержат RISC - и DSP – ядро. Производительность процессоров – порядка 600 Мflops. Напомню, что такую производительность имеет сигнальный процессор SHARC ADSP21160N компании Analog Devices, являющейся флагманом в создании компонентов для построения систем ЦОС. В середине 2004 г. был создан процессор по технологии «Мультикор» с производительностью 2400 Mflops и свыше 14 млрд. оп./с. для байтовых форматов данных, что соответствует характеристикам самого мощного чипа DSP Tiger SHARC (TS201, 0,13-мкм, 3600 Mflops).

Но мало освоить технологию разработки кристаллов – нужно дать проектировщикам инструментарий для создания систем ЦОС на базе «Мультикор». Фирма ЭЛВИС блестяще справилась и с этой задачей. Создан системный «Мультикор-конструктор» на основе набора СБИС, позволяющий разработчику РЭА легко создавать как связанные, так и распределённые системы. В конструктор входят разнообразные средства отладки и моделирования, инструментальные платы и мощное программное обеспечение. Запад не продаёт системы такого интеллектуального уровня (эмбарго). Процессоры «Мультикор» будут продаваться без ограничений. Кроме того, тестовое инструментальное ПО для чипов «Мультикор» передаётся бесплатно.

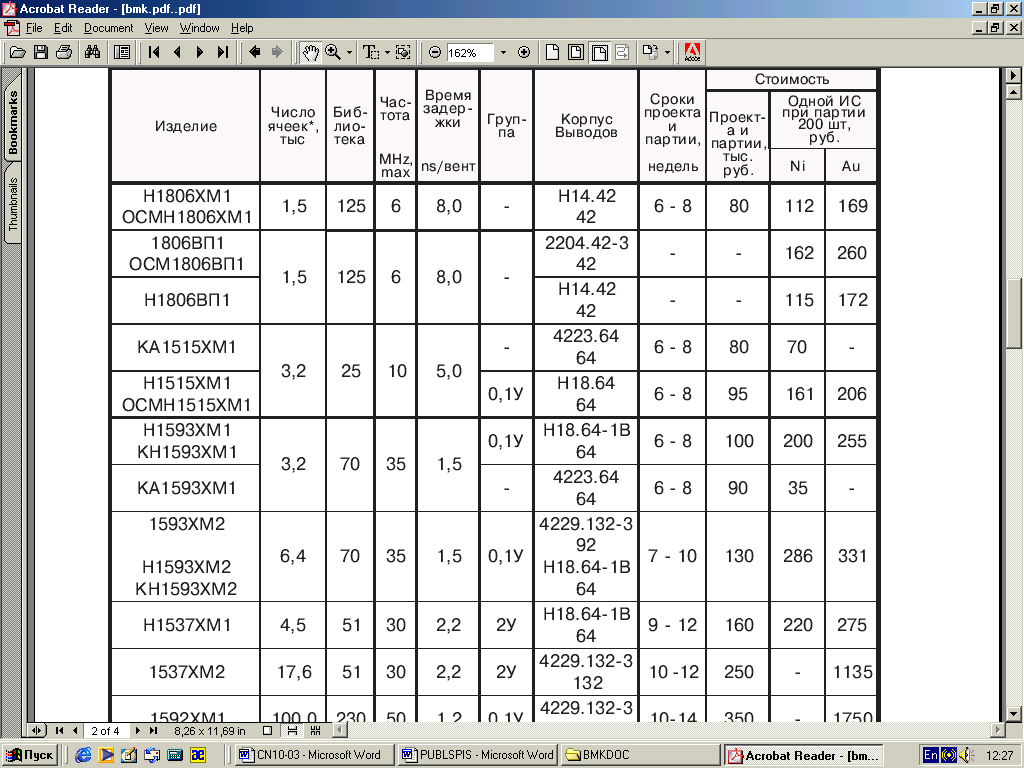

В области БМК достаточно широкая номенклатура от Н1806ХМ1 (1,5 тыс. вентилей) до 1592ХМ1 (100 тыс. вентилей, 50 МГц). Более подробную информацию можно получить на сайте rem.ru. Могу лишь отметить, что отечественные БМК в настоящее время решают все проблемы по замене ПЛИС фирмы “Altera” вплоть до реализации проектов, выполненных на EP1K50 . Перевод одной ПЛИС в настоящее время обходится в 440 тыс.руб. Это относительно дорого, но альтернатива отсутствует: кто не любит свою армию – кормит чужую. Кстати по западным меркам цена чрезвычайно низкая.

Популярная в последнее десятилетие технология проектирования «система на кристалле» (СнК, SoC) поддержана отечественной электроникой выпуском СБИС 1879ВМ3. Эта СБИС содержит два 6-разрядных АЦП и четыре 8-разрядных ЦАП (быстродействие 600 Мвыборок/с.), выпускается в радиационностойком исполнении с пятой Приёмкой Заказчика. Эта же фирма выпускает и сигнальный процессор Л1879ВМ1. Так что «ещё не вечер» для русской электроники, а интеллектом Россия не обижена.

Проблемы проектирования современных цифровых систем управления.

Современное проектирование цифровых устройств и систем предъявляет к разработчику повышенные требования, что вызывает появление ряда проблем. Использование ПЛИС и БМК только обострило эти проблемы. Постараемся рассмотреть их комплексно.

Во-первых, необходимо отметить, что советские инженеры – самые талантливые и образованные в мире. По роду своей предыдущей деятельности мне приходилось общаться почти со всеми разработчиками в СССР и анализировать зарубежные проекты.

Во-вторых, современные разработки предъявляют более жёсткие требования к проектировщикам, поэтому поговорим о наших недостатках.

Формализация ТЗ.

Пять лет назад, выполняя какую-то разработку для фирмы МиГ, я с удивлением обнаружил, что опытные профессионалы, описывая работу МПА, рисуют многочисленные циклограммы. Во-первых, это не гарантирует полного и корректного описания работы МПА, во-вторых, обременительно. Попытался привить им культуру задания МПА с помощью граф-схем алгоритмов (ГСА). Кажется, удалось обратить их в свою веру. Спустя два года, сотрудничая со специалистами «Полигонных систем ПВО», я столкнулся с необходимостью введения некоторого более мощного формального языка описания работы МПА. В качестве такого инструмента может использоваться П-код («Дисциплина программирования» Дзержинского Ф.Я. и Завгороднего Н.В. – М.:1983 г.) или Псевдо-Паскаль. Заманчиво с этой целью использовать просто Паскаль или Си: можно получить вместе с ТЗ и математическую модель проектируемого МПА. Однако, при этом теряется прозрачность ТЗ. Тем не менее решение этой проблемы желательно.

Вот как выглядит частичное описание на Псевдо-Паскале работы МПА для управления БИС динамической памяти на 256 Мбайт.

Program rdram1;

{ Процедура чтения из ОЗУ1: инициируется командой READ от RS232. }

{READ=1 пока не появится EOR=0}

Begin

repeat nop; until (read = 1) and (ready=1) and (write=0);

eosrf: cke := 1; #we := #ras := #cas := 1; #cs := 0;

delay(1);

cke := 1; #we := #ras := #cas := 1; #cs := 1;

delay(2);

i:=0;

repeat

act: A[12..0]:=AdrStr; BA0..BA1:=AdrBank; #we:=cke:= #cas :=1;#ras:=#cs := 0;

delay(1);

reada: A[9..0]:=AdrStb; A10:=1; BA0..BA1:=AdrBank;

#we:=#ras:=cke:=1;#cas:=#cs:=0; dqm:= 0;

delay(1);

cke := 1; #we := #ras := #cas := 1; #cs := 1;

delay(1);

cbr: подать без присвоения AD[10..9]-1;

if i>0 then

begin

#we := 1; #ras := #cas := #cs :=0; cke :=1; dqm := 0;

end;

delay(1);

cke := 1; #we := #ras := #cas := 1; #cs := 1; AD[25..0]:=AD[25..0]+1;

delay(508);

i :=1;

until kr = 1;

delay(3);

slfr: #we := 1; #ras := #cas := #cs := cke := 0;

delay(3);

eor := 0;

delay(1);

eor:=1;

end.

Примерно такие же по объёму алгоритмы подготовки к работе ОЗУ и записи в ОЗУ, поэтому ГСА получается довольно громоздкой. Кстати, традиционная эвристическая реализация такого МПА, выглядит уже неразумной, поскольку очевиден явно программный характер задачи.

Программирование и микропрограммирование.

Уже в 70-е годы прошлого столетия стала проявляться тенденция превращения цифровых схемотехников в программистов. Во-первых, потому, что в разработки был внедрён синтез микропрограммных автоматов , а во-вторых, потому, что каждый инженер обязан владеть программированием (но не обязательно программировать!), поскольку для него это то же самое, что в 19 веке счёты для бухгалтера. В настоящее время синтез цифровых систем выполняется на формальных микро-языках VHDL, AHDL, VERILOG. Схемотехники стали микропрограммистами. А следовательно, и проблемы схемотехников и программистов стали общими. Например, программисты не умеют верифицировать свои программы, схемотехники тоже недолюбливают схемную диагностику.

Простой тест для программистов: из файла триадами поступают целые числа, которые интерпретируются как длины сторон треугольника. Программа определяет тип треугольника. Ни один из программистов не определил все 14 наборов тестов. Ни программисты, ни схемотехники ничего не знают о диагностическом процессоре.

Кроме того, наше программное обеспечение (ПО) построено на западных операционных системах (ОС) и языках программирования, не защищено от взлома, вскрытия, т.е. не соблюдается элементарная информационная безопасность. Выход из тупика в использовании отечественных технологий. Примером такой технологии является ДССП и язык РАЯ (МГУ,Брусенцов Н.П.,tas.ru ). Кстати, язык РАЯ в ДССП позволяет писать в 5 – 7 раз более компактные программы, чем это способен делать ЯВУ Си. Сегодня переход на отечественные программные технологии не реален, но когда-то нужно опомниться. Кстати, в настоящее время в МГУ ведутся работы по реализации ДССП-процессора на ПЛИС EP1K100QC208-1. Автор в свободное от основной работы время участвует в этих работах.

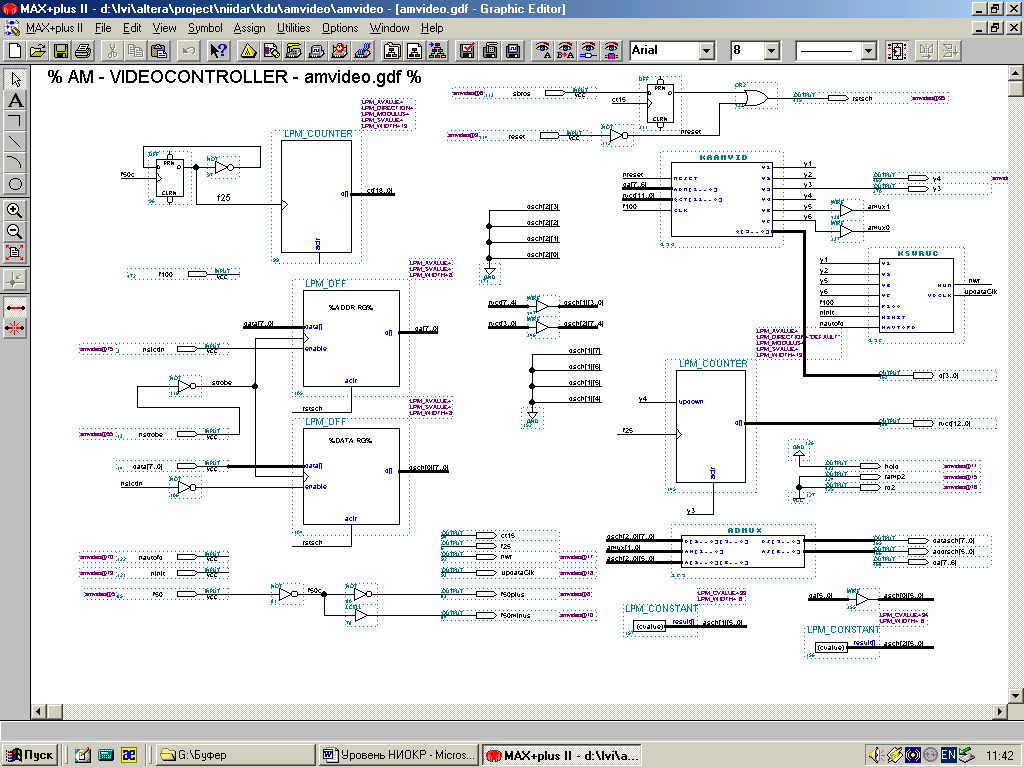

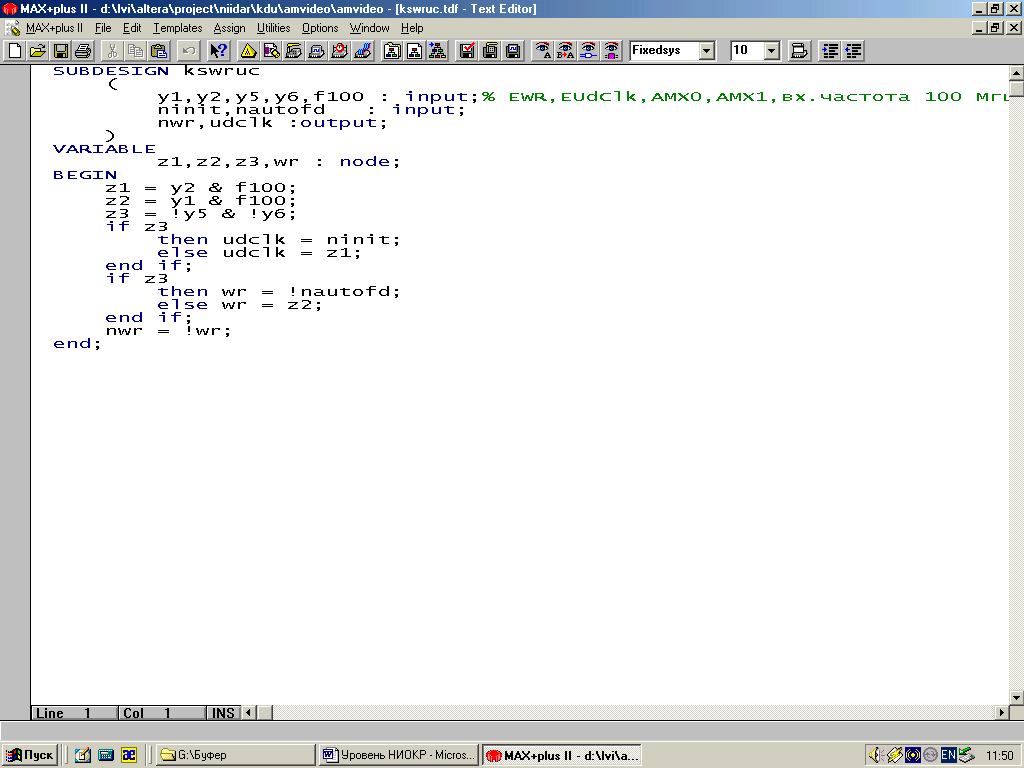

Далее, технология структурированного программирования мало что даёт, если объём ПО превышает 1000 стр. текста на языке Си. Микропрограммисты решают проблему создания относительно прозрачной схемы текстографическим проектированием. Возможно, на этом же пути находится решение проблем дисциплины программирования: лет 30 тому назад существовал графический Паскаль. В качестве примера текстографического проектирования приводится частичное описание видеоконтроллера цифрового телевизионного передатчика (ЦТВП), управляющего синтезатором частоты AD9854. Здесь верхние уровни иерархии представлены в графическом виде, а микропрограммы нижнего уровня создаются в текстовом формате. На рис.1 и 2 представлены схемотехника, микропрограммы и результат симуляции работы видеоконтроллера.

Для отладки видеотракта ЦТВП используется примитивное контрольно-диагностическое устройство (КДУ), состоящее из ПЛИС EP1K100QC208-1, конфигурационного ПЗУ и БИС ОЗУ ёмкостью 2 ТВ-экрана. Габариты платы КДУ составляют 100 х 100 мм. КДУ связано с ПК по интерфейсам USB, LPT, RS-232, RS-485. Программа для управления видеоконтроллером amvideo.pas работает под MS DOS в ПК. Скорость обмена между ПК и КДУ не превышает 200 кбайт в сек.

program amvideo;

{программа амплитудной модуляции для СЧ типа AD9854}

uses printer,dos,crt;

const base = $378;{базовый адрес регистра данных}

strobe = $01;{маска бита STROBE регистра управления}

autofd = $02;{маска бита AUTOFD регистра управления - nWR для СЧ}

init = $04;{маска бита INIT регистра управления - UdClk для СЧ}

slctin = $08;{маска бита SELECTIN регистра управления}

busy = $10;{маска бита BUSY регистра состояния}

type vect=array[0..1023] of real;

massiv=array[0..9] of byte;

var n,nr :longint;

bytemas:massiv;

ni,i,j:longint;

tau:word;

ch :char;

nis,nrs,ns:string;

c1,c2 :array[1..32] of real;

m:array[0..6143] of byte;

c,f,fh,h,ftw,fsys:real;

addr,data:byte;

csys:double;

{addr,data - адрес и данные для СЧ,

f - несущая частота,

h - шаг по частоте,

ftw - код установки частоты для AD9854,

fiint - нач. фаза в дискретах времени,

шина управления(порт $37A) для записи из компьютера:

nSTROBE - запись в регистры адреса и данных КДУ,

nAUTO_FD - сигнал записи для СЧ,

nINIT - сигнал обновления информации(UdClk) для СЧ,

nSLCT_IN - выбор регистра адреса(0) или регистра данных(1) }

{-------------------------------------------------------------}

function intchar(m:integer):char;

var

ch:char;

begin

case m of

0..9: ch:=chr(m+ord('0'));

10..35: ch:=chr(ord('A')+m-10);

else

begin

writeln('Ошибка ввода');

halt;

end;

end{case};

intchar:=ch;

end;

{-------------------------------------------------------------}

function stpn(x,y:real):real;

begin

stpn:=exp(y*ln(x));

end;

{--------------------------------------------------------------}

function int10(a:longint;b:integer):string;

{Пеpевод целого 10-ичного числа в (2..36)-ичные системы}

{a,b - исх. 10-ичн. число и основание сист. счисл. соотв-енно}

var s:string;

m,i,j:integer;

chrarr:array[0..30] of string;

begin

i:=0;

for j:=0 to 30 do chrarr[j]:=' ';

repeat

m:=(a mod b);

chrarr[i]:=intchar(m);

a:=a div b;

i:=i+1;

until (a=0);

s:=chrarr[i];

for j:=i-1 downto 0 do

s:=s + chrarr[j];

int10:=s;

end;

{--------------------------------------------------------------}

procedure int256(f:real;var mass:massiv);

{Разделение целого 10-ичного числа на байты}

{f - исх. 10-ичн. число}

var fi,fri,m:longint;

ff,fr:real;

i:integer;

begin

ff:=f/65536;{масштабирование}

fr:=frac(ff)*65536;

fri:=trunc(fr);

fi:=trunc(ff);

mass[1]:=fri mod 256;

mass[2]:=fri div 256;

i:=3;

repeat

m:=fi mod 256;{m:=a mod 256}

mass[i]:=m;

fi:=fi div 256;{a div 256}

i:=i+1;

until (fi=0);

end;

{---------------------------------------------------------}

procedure ustanow;

begin

port[base]:=0; {0 -> регистр данных LPT1}

port[base+2]:=0; {0 -> регистр управления LPT1}

writeln;

end;

{--------------------------------------------------------------}

procedure ustreg;

{Установка АМ-режима работы СЧ}

var i:integer;

begin

port[base]:=$1f; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=$c6; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=$1f; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=06; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=$1d; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=$10; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=$1e; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=$44; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=$20; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=$40; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

end;

{--------------------------------------------------------------}

procedure ustfreq(var bytemas:massiv);

{Установка частоты}

{bytemas - массив кодов задаваемой частоты}

var i:integer;

begin

port[base]:=04; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=bytemas[5];{посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=05; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=bytemas[4]; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=06; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=bytemas[3]; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=07; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=bytemas[2]; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

port[base]:=08; {посылка в порт 378h байтa адреса}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=bytemas[1]; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

end;

{--------------------------------------------------------------}

procedure lptend;

{Окончание работы с LPT}

var i:integer;

begin

port[base]:=$5f; {посылка в порт 378h признака конца работы с LPT}

port[base+2]:=strobe;

port[base+2]:=0;

port[base]:=$c6; {посылка в порт 378h байта данных для СЧ}

port[base+2]:=strobe xor slctin;

port[base+2]:=slctin;

port[base+2]:=0;

for i:=1 to 10 do

begin

port[base+2]:=autofd;{nWR для СЧ}

port[base+2]:=0;

port[base+2]:=init;{UdClk для СЧ}

port[base+2]:=0;

end;

end;

{=========================================================}

begin

clrscr;

ustanow;

writeln('Подайте напряжение +5 В, затем нажмите ENTER');

readln;

writeln('╔═══════════════════════════════╗');

writeln('║ Амплитудно-частотная модуляция на ║');

writeln('║ основе СЧ с помощью КДУ и ПК ║');

writeln('║ Лобанов В.И. 18-11-2004 ║');

writeln('╚═══════════════════════════════╝');

ustreg;

csys:=stpn(2,40);

writeln('Системная константа csys = 240 = ',csys);

write('Введите системную и несущую частоты диапазона в МГц ');

readln(fsys,f);

ftw:=f/fsys*csys;

writeln('Десятичный код частоты f = ',f:10:6,' равен ftw = ',ftw);

for j:=0 to 9 do bytemas[j]:=0;

writeln;

int256(ftw,bytemas);

writeln('Байты кода = ');

for j:=5 downto 0 do write(bytemas[j]:6);

writeln;

ustfreq(bytemas);

lptend;

writeln('Нажмите ENTER');

readln;

clrscr;

end.

Конечно, эту программку на Паскаль можно сократить в несколько раз, но спешка при отладке аппаратуры не позволила внести изменения.

Рис.1. Структурная схема видеоконтроллера ЦТВП.

Рис.2. Микропрограммы конечных автоматов видеоконтроллера ЦТВП.

Формальный синтез МПА при использовании ПЛИС.

Широкое внедрение ПЛИС фирмы Altera в практику цифровых разработок связано не только с достоинствами этих микросхем, но и не в последнюю очередь с появлением отечественной литературы по данному вопросу. Десять лет тому назад появление САПР ПЛИС Xilinx сопровождалось такими сложностями, что применять эту систему в практических разработках не было ни малейшего желания. В прекрасном практическом курсе Антонова А.П., не только разобран весь процесс проектирования, но ещё и приложен компакт-диск с самой САПР MAX+PLUS II. Эта САПР имеет ряд существенных недостатков, но позволяет даже радиолюбителю решать серьёзные задачи.

Однако, перевод полученного решения на БМК требует знания формальных методов синтеза МПА. Прежде всего это связано с минимизацией булевых функций, поскольку такая операция не только экономит ресурсы, но и минимизирует задержку комбинационной схемы. Аппарат минимизации в САПР реализован из рук вон плохо. Следовательно, цифровику необходимо знать азбуку своей профессии: на калькулятор надейся, а таблицу умножения не забывай. Кто умеет работать с картами Карно на 8-10 переменных? Никто. А ведь это азбука. Не всегда есть под рукой эффективная программа минимизации, да зачастую (в 99% всех случаев) она и не требуется. Кстати, самым эффективным алгоритмом минимизации обладает метод обобщённых кодов. Он был проверен автором в конце 70-х годов прошлого века при минимизации булевых функций от 45 переменных. До сих пор ничего более элегантного не появилось. Этот метод разработан в конце 60-х годов 20-го века на 21-й кафедре Академии им. Дзержинского полковником, д. т. н. Мавренковым Леонидом Трофимовичем. Дальнейшее развитие метода и доведение его до инженерных методик было выполнено сотрудниками этой кафедры к.т.н. Кустенко А.С., к.т.н. Кузнецовым Н.В. и к.т.н. Салтыковым Ю.А.(см. "Вопросы оборонной техники", 1972 г.). В открытой печати этот метод появился в 1977г.[22].

Формальный синтез МПА в САПР также имеет дефекты[25]. Недостатков в САПР слишком много, но это тема для отдельного разговора. Т.е. САПР MAX+PLUS II не удовлетворяет запросы профессиональных разработчиков. При работе с БМК проектировщик всегда должен быть готов к тому, что некоторые элементы и модули ему придётся строить формально. В частности цифровик обязан уметь создавать любую элементную базу на основе И-НЕ (функционально полный элемент ИЛИ-НЕ в OrCAD не позволит создать SR-триггер из-за гонок). Например, при работе на предельных частотах для синтеза асинхронных МПА требуется SR-триггер со сбросом, иначе не удастся провести симуляцию в пакете MAX+PLUS II. Этот элемент памяти необходимо построить чисто формально, причём с предельно высоким быстродействием. Сплошь и рядом приходится синтезировать МПА, работающие по самым причудливым алгоритмам. Применять эвристику для решения подобных задач всё равно, что забивать микроскопом гвозди. Вообще цифровик должен уметь формально строить МПА на любых элементах, в том числе и на лампах, и на реле. Это потребовалось в Чернобыле.

Применение микропроцессоров породило проблему помехоустойчивости. Сбои в работе процессора могли приводить к катастрофическим последствиям. Поэтому появились всевозможные «войч-доги», которые контролировали время выполнения циклических участков программы. Однако этот приём оказался малоэффективным. На смену «сторожевым собачкам» пришёл диагностический процессор (ДП) CERBERUS-16. Но высокая сложность устройства, большой латентный период обнаружения ошибки и сложность подготовки программы ДП не позволили внедрить его в производство. В ХПИ им. В.И. Ленина, на кафедре автоматики и телемеханики в 1985 г. был разработан отечественный ДП, лишённый вышеуказанных недостатков. Работами по созданию и испытаниям ДП руководил проф. Леонид Викторович Дербунович. Кроме самой схемы был разработан транслятор с ассемблера КМ1816ВЕ48 на язык диагностического процессора. ДП успешно прошёл испытания и был рекомендован в 1990 г. к производству в виде специализированной БИС. Отсутствие финансирования и развал Советского Союза похоронили перспективный проект. Автор попытался перевести схему ХПИ на ПЛИС Xilinx, но низкий уровень интеграции позволил сократить объём с 66 корпусов лишь до 12. Такой результат не имеет практической ценности. Появление ПЛИС и БМК высокой интеграции позволяют возродить надежду на реализацию идей харьковчан в виде одной ПЛИС, а возможно и одного отечественного БМК.

Макетирование проектов.

Несмотря на то, что САПР MAX+PLUS II при симуляции выдаёт достаточно корректные результаты, макетирование проектируемой схемы остаётся насущной необходимостью. Поэтому имеет смысл разработки макетной платы, которая содержит одну или несколько различных ПЛИС, несколько АЦП и ЦАП с возможностью коммутации связей. Это позволит проверять работу различных ПЛИС с различными периферийными устройствами. Такая предварительная проверка позволит подготовить проект для реализации его на БМК с минимальным количеством ошибок. В большинстве случаев можно воспользоваться готовыми платами для макетирования, так называемыми KIT.

Кроме того, необходимо аналогичное макетирование для обеспечения входного контроля получаемых БМК. Полагаться на гарантии поставщика было бы неразумно.

Математическая логика и искусственный интеллект.

Как заявил директор ГУП НПЦ «ЭЛВИС» Петричкович Я.Я. Россия не может конкурировать с Китаем в области бытовой электроники: слишком дёшев труд в КНР . А вот в области высоких технологий Россия вне досягаемости Китая, Индии и абсолютного большинства других стран. «ЭЛВИС» уже «наступает на пятки» Америке в создании элементной базы для систем ЦОС. Но в России остался ещё невостребованным потенциал огромной мощности. Все советские инженеры прекрасно владели математикой, а это фундамент искусственного интеллекта.

21 век называют веком искусственного интеллекта (ИИ), но отсутствие математической логики (взамен аристотелевской) препятствует решению фундаментальных проблем ИИ в том числе и для целей обороны. По степени решения проблем ИИ судят о научном потенциале державы. В 21-м веке будут соревноваться не технологии, а интеллекты. Самой высокой технологией станет ИИ.

В России создана Русская логика для решения задач ИИ. Решены проблемы, над которыми трудилось всё человечество (и «физики», и «лирики») 25 веков. Эта истинно математическая логика, созданная в России, прошла проверку на различных конференциях, симпозиумах и конгрессах, в том числе и международных. С 1998 г. не прозвучало ни одного критического замечания в адрес логики России. В свободное от основной работы время автор преподавал Русскую логику в школах, гимназиях, техникумах, колледжах и вузах, а также в обществе «Знание». Эта логика легко осваивалась даже семиклассниками. Основы Русской логики изложены на сайтах ссылка скрыта, ссылка скрыта, ссылка скрыта . И тем не менее преподаваемая в России логика дремуче невежественна и вопиюще безграмотна. Работы автора переведены за рубежом. Есть опасение, что там освоят Русскую логику раньше, чем мы. По докладу автора на «КС» по военной безопасности при Комитете по обороне ГД РФ 13.11.2003 было принято решение «о ликвидации логической необразованности всего российского общества в целом, как в 20-е годы прошлого века была ликвидирована начальная неграмотность в Советской России». Поэтому инженерному корпусу России придётся поголовно осваивать Русскую логику.

Заключение.

У России есть шанс подняться с колен. Нужна лишь политическая воля. Что касается решения чисто инженерных и научных проблем, то имеет смысл изложить некоторые рекомендации. Для Заказчика и руководителей НИИ, ОКБ и НПО предлагается производить прикидочный анализ уровня НИОКР по следующим признакам отсутствия квалификации:

- использование «рассыпной» элементной базы вместо технологии СнК (SoC) или хотя бы использования разрешённых к применению БМК, ПЛМ, ПМЛ и ПЛИС;

- чисто эвристические решения при синтезе всех МПА;

- применение асинхронных МПА на низких частотах;

- «игра» на задержках вместо построения синхронного МПА;

- отсутствие контролепригодности;

- отсутствие самодиагностики;

- отсутствие обоснования полноты тестирования.

Необходимый минимум знаний и умений разработчика-цифровика можно определить следующим перечнем :

- умение работать с картой Карно на большое число переменных (не менее 8);

- владение методом обобщённых кодов Мавренкова для ручной и машинной минимизации булевых функций;

- знание инженерных методов разработки цифровых устройств;

- умение синтезировать счётчики с любыми, в том числе с дробными, коэффициентами деления и распределители импульсов любого вида;

- умение превратить любую циклограмму в ГСА для последующего формального синтеза МПА;

- умение формально построить любой элемент памяти на ИС типа И-НЕ, ИЛИ-НЕ, лампах и реле;

- владение формальными методами синтеза МПА на ИС, лампах и реле;

- знание вопросов диагностики на уровне, обеспечивающем контролепригодность, самодиагностику, контроль и диагностику разрабатываемого прибора;

- знание математической логики, фундамента ИИ.

Экспресс-анализ технического уровня НИОКР может быть также произведён вневедомственной группой профессионалов-электронщиков.

В связи с чрезвычайно низким уровнем разработок современных инженеров России предлагается проведение следующих оргмероприятий:

- Создать вневедомственную группу (подразделение) по контролю технического уровня НИОКР (КТУ) по анализу проекта и выработке предложений по устранению выявленных недостатков в составе не более 10 человек с рабочим циклом на одну НИОКР в 1 – 2 недели. Группа КТУ будет выявлять наиболее характерные ошибки и давать заключение о техническом уровне НИОКР. Естественно, такой анализ целесообразнее проводить на этапе НИР.

- Проведение технического обучения ведущих специалистов разрабатывающих организаций и подразделений Приёмки Заказчика (не более 40 часов);

- Издание технического руководства по разработке цифровых устройств.

- Аттестация инженеров-цифровиков в объёме «АРЦУ» [37].

- Перестройка преподавания гуманитарной и математической логики в средних и высших учебных заведениях России.