Методы оптимизации энергопотребления в микроэлектронных системах

| Вид материала | Автореферат |

СодержаниеОсновные результаты работы |

- Решение задач глобальной оптимизации большой размерности на многопроцессорных комплексах, 143.77kb.

- Календарный план учебных занятий по дисциплине Компьютерный дизайн оптических наноструктур,, 39.38kb.

- Конспект лекций по Методам оптимизации для студентов, обучающихся по специальности, 41.05kb.

- Концепция системного подхода при проектировании сапр. Последовательный метод компоновки, 29.25kb.

- Учебной дисциплины «Методы оптимизации» для направления 010400. 62 «Прикладная математика, 40.12kb.

- Рабочая учебная программа по дисциплине «Методы оптимизации» Направление №230100 «Информатика, 129.28kb.

- Методы оптимизации запросов в реляционных системах, 453.81kb.

- Рабочая программа учебной дисциплины (модуля) методы оптимизации, 164.09kb.

- Алтайский Государственный Технический Университет им. И. И. Ползунова памятка, 129.3kb.

- Программа дисциплины " методы оптимизации " Направление, 59.57kb.

Перенос принципов классической КМОП-схемотехники цифровых устройств на устройства с QCA невозможен, поскольку в их основах лежат разные концепции. В ранних работах предлагались подходы к решению проблем, возникающих при архитектурном проектировании вычислительных устройств с QCA. Однако существует ряд до конца нерешенных задач, таких как задачи сокращения количества числа ячеек в одной временной зоне, унификация топологии временных зон, уменьшение потерь полезной площади, построение обратных информационных связей и др.

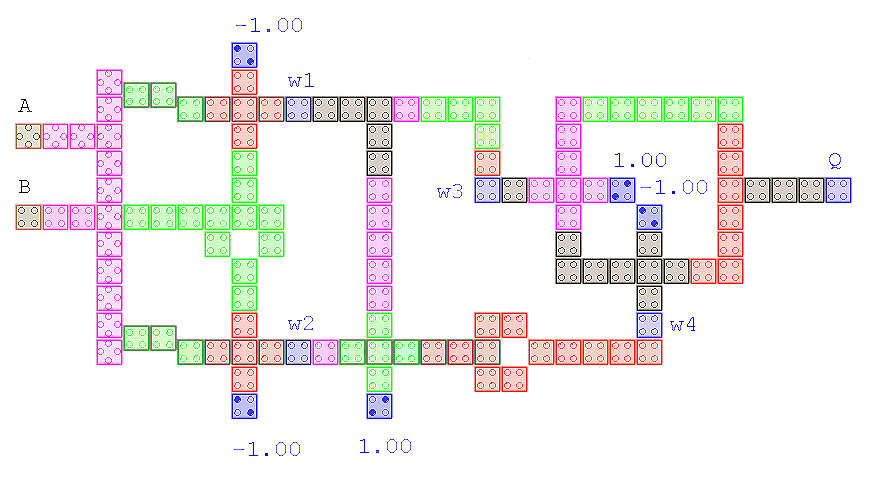

Разработан метод построения схем QCA функций четырех переменных. Схемы состоят из двух рангов: в первом ранге – три мажоритарных элемента, во втором – один, объединяющий выходы элементов первого ранга (Рис. 11).

Рис. 11. Обобщенная схема, состоящая из мажоритарных элементов

Целью процедур метода является определение наборов имен входов (множеств S) трех мажоритарных элементов, расположенных в первом ранге схемы. Каждый такой набор (множество) составляется из имен входных сигналов из алфавита Z = {a, b, c, d,a,b,c,d, 0, 1}, мощность которого |Z| = 10. Множество имен входов состоит из трех элементов S = {i1,i2,i3}, где i1 Z, i2 Z, i3 Z.

Другими словами, решается задача поиска решения из всех возможных сочетаний имен (элементов множества Z): M{S Z}.

Разработанный метод состоит из следующих этапов:

- установка начальных ограничений;

- определение возможных вариантов;

- определение дополнительных ограничений второго элемента для каждого варианта первого элемента;

- определение дополнительных ограничений третьего элемента для каждого варианта первого и второго элементов;

- выбор окончательного варианта.

На первом этапе выбираются любые две позиции, имеющие значения 0 и 1 в целевой карте Карно (функции четырех переменных). Учитывая особенности принятой схемы можно сделать вывод о том, что в обеих выбранных позициях будут те же самые значения хотя бы в одной из карт элементов первого ранга. Дополнительно в одной (только одной) из позиций другой карты можно закрепить ее исходное значение. Подобное закрепление значений в позициях одной из карт является ограничением рассматриваемых вариантов (сужением диапазона сочетаний).

На втором этапе на основе поставленных ограничений определяется диапазон возможных вариантов решения. Для этого составляется система из двух булевых уравнений:

,

,где P1 и P2 – значения всех сигналов из множества Z для двух заданных позиций в картах Карно.

На основе полученных уравнений строятся графы условных связей между именами в наборах S. Для каждого уравнения получают два графа – один для разрешенных сочетаний, другой – для запрещенных.

На третьем этапе определяются дополнительные ограничения для каждого варианта. Если начальные ограничения устанавливались для одного из элементов, то данные ограничения устанавливаются для другого (второго) элемента первого ранга.

Для полученных ограничений, как и на втором этапе, строится система булевых уравнений подобно приведенной системе уравнений, но количество уравнений будет зависеть от количества позиций с новыми ограничениями. Как правило, количество таких позиций находиться в диапазоне от 2 до 8.

На следующем этапе определяются ограничения для третьего элемента при заданных картах первых двух элементов. Для получения ограничений карты третьего элемента анализируются значения в позициях целевой карты и карт упомянутых элементов. В среднем количество позиций с ограничениями в карте третьего элемента лежит в диапазоне от 6 до 12.

На последнем этапе производится сравнение карт выбранных вариантов и целевой карты.

Эффективность предложенного метода проектирования функциональных блоков на основе квантовых клеточных автоматов доказана результатами сравнительного анализа с существующими методами проектирования на основе мажоритарных элементов. Сокращение числа элементов в среднем достигает 3 раз. Снижение времени проектирования до 14 раз.

Разработаны и исследованы схема и конструкция NCL-элемента 2-из-2 с логическим гистерезисом, позволяющим реализовать принципы асинхронной логики при синтезе функциональных блоков QCA. Предложенная схема обеспечивает функционирование элемента с гистерезисом (Рис. 12). Круговая стрелка показывает петлю памяти, по которой циклически перемещаются данные. Топология, реализующая предложенную схему NCL-элемента показана на Рис. 13.

|

| Рис. 12. Схема NCL-элемента 2-из-2 с логическим гистерезисом для технологии QCA |

Рис. 13. Топология NCL-элемента 2-из-2 (яркость заливки соответствует определенной тактирующей зоне)

Для функциональной верификации работы разработанного элемента был использован метод бистабильного моделирования, а также САПР QCADesigner, распространяемая по открытой лицензии.

В методе бистабильного моделирования принимается во внимание то, что каждая ячейка это простая система с двумя состояниями. Поскольку экспериментальные данные о временах переключения ячеек отсутствуют, то моделирование не включает в себя временную информацию. С использованием функции отклика вычисляется состояние каждой ячейки относительно других ячеек, попадающих в эффективный радиус. Данное вычисление производится итеративно до тех пор, пока описание всей системы не сойдется к заданной допустимой погрешности.

Хотя данный подход достаточен для функциональной верификации проектов, он не может быть использован для достоверного динамического моделирования. Но он из-за принятых упрощений может быть полезен для относительно быстрого моделирования больших схем.

В пятой главе предлагается методология проектирования асинхронных схем, основой которой являются разработанные автором методы, алгоритмы и программные средства, интегрированные в сквозной маршрут прямой конвертации синхронных проектов, полученных на основе традиционных инструментов, таких как VHDL и С++, в их асинхронный функциональный аналог. Преимущества данного подхода в том, что все функции тестирования и отладки могут быть произведены на оригинальной синхронной версии проекта и прямая трансляция требует от разработчика минимального вмешательства в процесс построения асинхронного проекта.

Традиционный подход к выполнению подобной конвертации состоит в так называемой десинхронизации, когда все синхронные элементы и структуры заменяются их асинхронными аналогами. Далее проводится оптимизация по различным параметрам (быстродействие, занимаемая площадь, энергопотребление). В частности, в ранних работах описан маршрут с применением коммерческих САПР, однако он ориентирован только на методологию NCL-проектирования и может быть применен для реализации разработанных автором методов и программных средств.

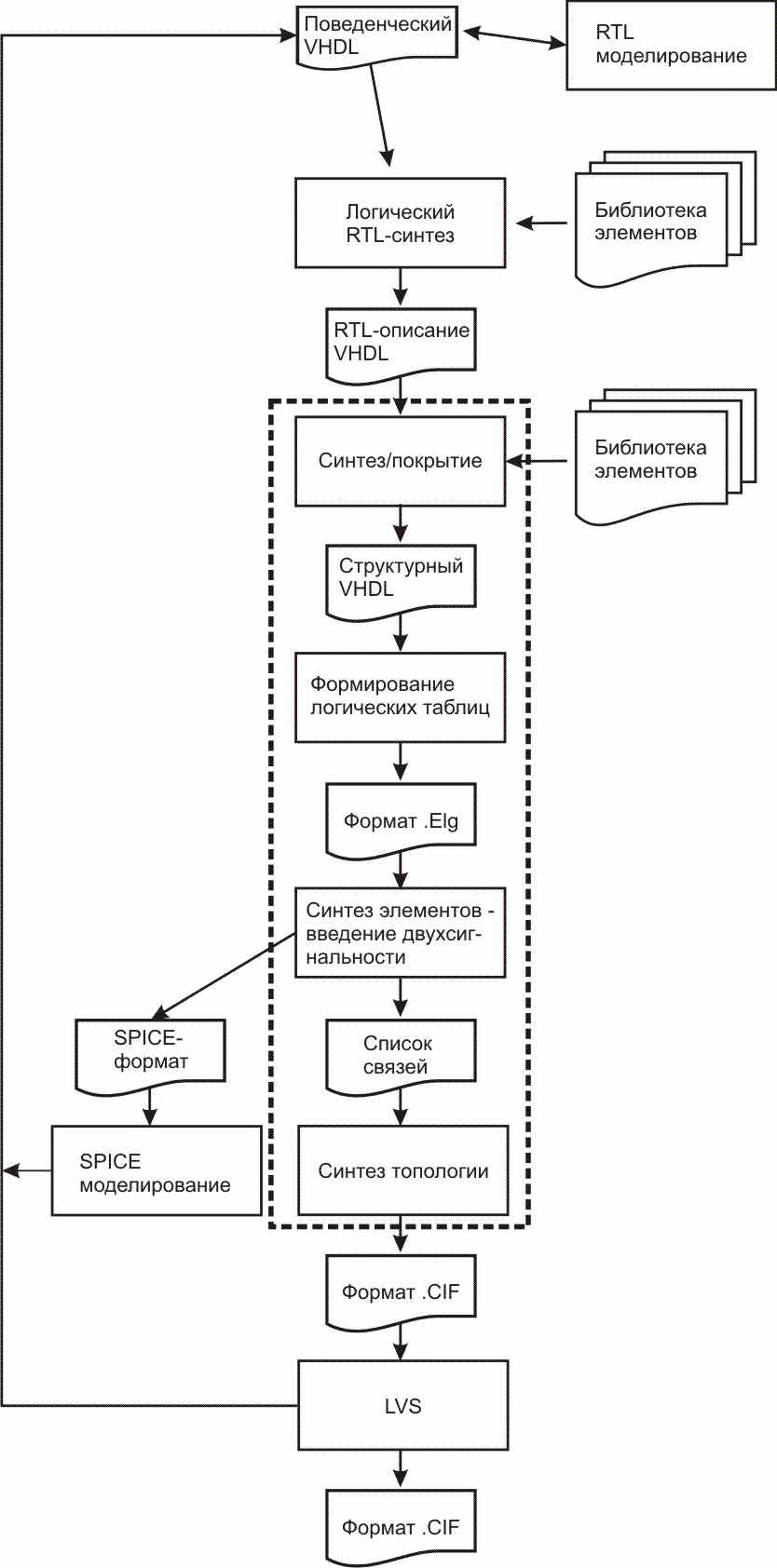

Для повышения эффективности разработки асинхронных СБИС, за счет использования лучших достижений «синхроники» и новых методологий построения асинхронных схем, предлагается маршрут сквозного проектирования, этапы реализации которого базируются на разработанных автором методах, алгоритмах и программных средствах, а также существующих (синхронных) коммерческих подсистемах САПР (Рис. 14). Этапы, заключенные в пунктирную область, содержат разработанные на основе предложенных автором методов алгоритмы и программные средства.

В маршруте присутствуют следующие этапы:

- Определение требований для проекта.

- Разработка функциональных описаний на языке программирования высокого уровня С++ или SystemC.

- Формирование HDL-описания (HDL – Hardware Description Language) цифрового устройства путем трансляции из функциональных описаний на языке С++ (SystemC) или самостоятельного создания HDL-кода.

- Моделирование и отладка HDL-описания.

Рис. 14. Маршрут проектирования асинхронных схем

- Логический синтез с использованием коммерческих компиляторов. Получение RTL-описания (RTL – Register Transfer Level) проекта.

- Оптимизация RTL-описания и повторный синтез в базис универсальных n-входовых элементов (n = 1, 2, 3, 4).

- Формальная верификация на логическом уровне.

- Создание логических таблиц для всех универсальных элементов, входящих в синтезированную схему.

- Схемотехнический (на транзисторном уровне) синтез каждого универсального элемента.

- Сборка схемы на транзисторном уровне.

- Верификация общей транзисторной схемы с использованием SPICE-симулятора.

- Топологический синтез каждого универсального элемента.

- Общий топологический синтез схемы из универсальных элементов.

- Экстракция схемы из топологии.

- Формальная верификация схемы.

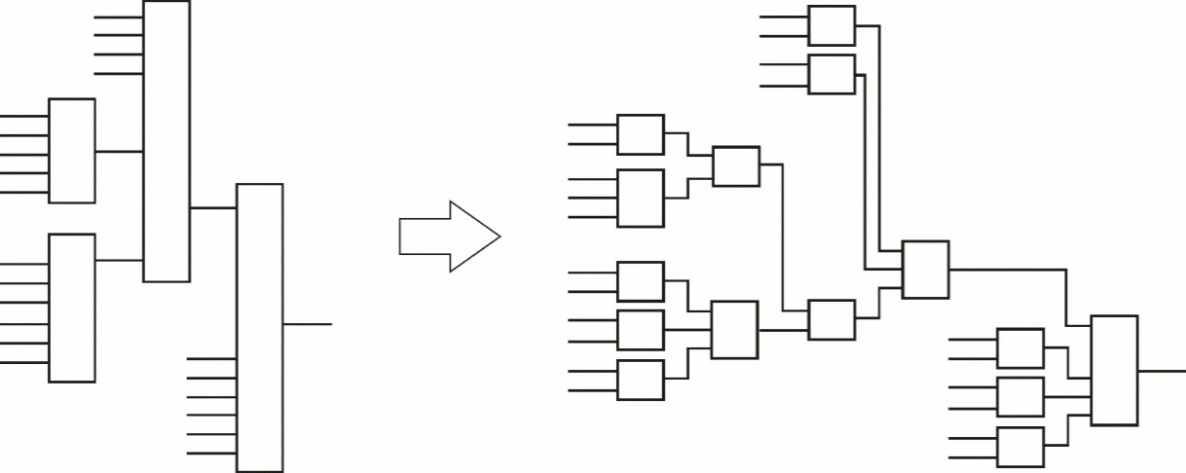

С этапа оптимизации и повторного синтеза в базис универсальных (1-4)-входовых элементов начинается использование разработанных автором (частично или полностью) методов и процедур, относящихся к асихронике. Первой из таких процедур является автоматическая конвертация синхронных схем в базис, удобный для синтеза функциональных блоков асинхронных схем. На данном этапе проводится декомпозиция комбинационной части синхронной схемы в сеть из универсальных n-входовых элементов (Рис. 15), причем n может принимать значения от 1 до 4. Ограничение сверху на число n входов универсального элемента обусловлено особенностями схемотехники асинхронных элементов с логическим гистерезисом.

Рис. 15. Декомпозиция на универсальные элементы

На этапе создания логических таблиц для каждого универсального (1-4)-входового элемента схемы строится промежуточная таблица истинности, предназначенная для выполнения схемотехнического синтеза на следующем этапе.

На этапе схемотехнического (на транзисторном уровне) проектирования универсального элемента формируются нечувствительные к задержкам элементы, ориентированные на работу с двухпроводными сигналами по 4-фазному протоколу. Данный этап выполняется с помощью специализированного программного модуля, который воспринимает файлы формата .Elg и выводит результат, как во внутреннем формате, так и в SPICE-формате для цифро-аналогового моделирования.

После схемного синтеза элементов производится их общая сборка в единую схему, включающую в себя все двухсигнальные цепи и сигналы подтверждения.

Для асинхронных схем более важно логическое, нежели схемотехническое моделирование, которое может быть проведено на упрощенном уровне. Это становится возможным благодаря тому, что корректность функционирования асинхронных схем гораздо менее подвержена технологическим разбросам и слабо зависит от условий эксплуатации СБИС. В этом одно из их достоинств.

Конечно, полностью исключить схемотехническое моделирование асинхронных схем нельзя, из-за необходимости оценивать их динамические параметры. В зависимости от сложности проекта циклы схемотехнического моделирования и проектирования топологии могут выполняться на разных уровнях иерархии проекта, чередуясь с этапами верификации топологии и коррекции электрической схемы.

При топологическом синтезе универсальных элементов многократно выполняется процедура формирования рисунков слоев для каждого универсального элемента. Для этой цели используется разработанная автором специализированная подсистема САПР, которая синтезирует топологию с применением оптимизации по различным параметрам.

При формировании топологии применяется разработанный метод на основе стандартных ячеек. Каждая ячейка представляет собой топологический рисунок (1-4)-входового стандартного элемента фиксированной высоты. Ширина ячейки определяется, во-первых, технологическими нормами, во-вторых, количеством входов и, в-третьих, параметризацией конкретного элемента.

Этап общего топологического синтеза схемы на основе блоков универсальных элементов подразумевает сборку общей топологии СБИС с использование рисунков элементов, полученных на предыдущем этапе. Данный этап может проводиться как специализированной, разработанной автором, подсистемой, так и коммерческими САПР, поскольку необходимые процедуры являются традиционными и оперируют с заранее подготовленной по правилам метода библиотекой элементов.

Новизна предлагаемого маршрута проектирования состоит в использовании уникальных методов, алгоритмов, процедур и программных средств на различных его этапах.

С целью реализации данного маршрута проектирования разработаны алгоритмы и программные средства, выполняющие ряд описанных выше процедур. В частности, были разработаны подсистемы САПР для схемотехнического и топологического синтеза асинхронных функциональных блоков.

Для выполнения начального (подготовительного) этапа предложенного маршрута проектирования – получения поведенческого описания на VHDL, разработан метод полностью автоматического формирования VHDL-описаний на основе С++-кода.

Разработка и отладка исходного кода алгоритма, как правило, значительно упрощаются, когда они выполняются с помощью высокоуровнего языка традиционного программирования (C/C++, Паскаль и т.п.), поскольку одни и те же спецификации могут быть использованы как при моделировании, так и при схемном синтезе в общем маршруте проектирования.

Большинство программистов и разработчиков алгоритмов привыкли описывать процедуры для последовательной вычислительной машины. Для того, чтобы создавать эффективные алгоритмы для аппаратной реализации необходимы знания и опыт в области схемотехники (концепции параллельности вычислений, конвейеризации, учета задержек и др.).

Автоматическая трансляция алгоритмов, описанных на C++ в синтезируемое описание на языке VHDL позволит решить подобные проблемы. Однако во многих случаях прямая трансляция не может быть произведена, поскольку возникают трудности учета параллелизма, конвейеризации и обеспечения синтезируемости окончательного описания.

Разработан метод трансляции алгоритмов с языка C++ в синтезируемое подмножество языка VHDL, который позволяет учесть вышеописанные особенности аппаратной реализации алгоритмов асинхронной логики. Получаемый VHDL-код далее используется для синтеза асинхронных схем.

В рамках метода задаются правила написания программ на С++:

– специально определяются функции для трансляции;

– функции, неподлежащие трансляции не должны возвращать никакого значения, т.е. в ней отсутствует оператор return, а тип возвращаемого значения – void;

– функции, подлежащие трансляции не должны вызывать библиотечных функций, которые не имеют исходного кода или потенциально несинтезируемые (например, printf и др.). Если есть необходимость в вызове другой функции, то она должна иметь исходное описание;

– входные данные – обычные аргументы функции, а возвращаемые – ссылочные переменные;

– все переменные в транслируемой функции должны быть статическими;

– каждый вызов (во время моделирования) транслируемой функции с фиксированным набором аргументов, соответствует одному такту рабочей частоты аппаратной реализации.

Также предлагаются принципы построения VHDL-описаний асинхронных блоков на основе языка SystemC, который фактически является библиотекой классов, учитывающей особенности аппаратной реализации функций проекта (сигналы, параллельность выполнения и др.).

Эффективность предложенного метода трансляции функциональных описаний на языке С++ в VHDL-описания с учетом особенностей асинхронной логики доказана результатами сравнительного анализа с существующими методами проектирования систем-на-кристалле, которые либо не предназначены для разработки асинхронных систем, либо не позволяют прямую трансляцию с исполнимых спецификаций. Сокращение времени проектирования достигает в среднем 50%.

Эффективность предложенного маршрута сквозного проектирования асинхронных систем, интегрирующего в себе разработанные и известные методы была показана апробацией на примере проектов микроконтроллера, турбодекодера, криптопроцессора и др. Сокращение времени проектирования асинхронных систем достигает в среднем 90%.

В приложении представлены документы о внедрении результатов диссертационной работы.

ОСНОВНЫЕ РЕЗУЛЬТАТЫ РАБОТЫ

В рамках диссертационной работы предложены и исследованы методы повышения энергоэффективности вычислительных систем, реализующихся по технологии КМОП и на основе квантовых клеточных автоматов. В частности разработаны:

- методология построения цифровых асинхронных компонентов систем-на-кристалле, включая схемотехнические основы создания асинхронных функциональных блоков. Данная методология позволяет сократить число транзисторов в асинхронных блоках и повысить их энергоэффективность;

- аналитические модели для оценки энергопотребления и задержек сигналов асинхронными элементами и функциональными блоками, позволяющие на основе введенного интегрального критерия относительно быстро и с приемлемой точностью (до 8%) оценить энергоэффективность проектируемых элементов без применения ресурсозатратного моделирования. Модели предназначены для использования в САПР СБИС асинхронной логики;

- методика нахождения оптимальных ширин каналов транзисторов для максимизации энергоэффективности;

- метод повышения энергоэффективности на архитектурном уровне. Анализ и апробация данного метода на примере разработки архитектуры турбодекодера показали, что получаемые решения отличаются от аналогов меньшими, минимум в 2 раза, энергопотреблением и площадью. Предложенные идеи архитектурного преобразования функциональных блоков использованы при проектировании новых систем микроэлектронной техники.

- метод оптимизации межблочных транзакций и распределения задач в системах-на-кристалле для повышения их энергоэффективности;

- метод проектирования вычислительных устройств с малым энергопотреблением на основе квантовых клеточных автоматов;

- конструкции элементов асинхронной логики на основе квантовых клеточных автоматов;

- методология автоматизированного проектирования асинхронных микроэлектронных систем-на-кристалле. Данная методология проектирования в виде маршрута реализуется с помощью существующих средств САПР и разработанных программных средств,

- метод проектирования асинхронных функциональных блоков с использованием языка C++, который позволил сократить время проектирования микроэлектронных систем;

- метод построения VHDL-описаний малопотребляющих функциональных блоков для повторного использования на основе описаний на языке SystemC. Данный метод использован в общем маршруте проектирования для сокращения временных затрат на разработку микроэлектронных систем;

- маршрут проектирования СБИС на основе библиотеки элементов AMS-0,8 мкм для САПР Leonardo Spectrum;

- маршрут проектирования заказных СБИС от уровня поведенческого представления на языке VHDL до структурного описания в формате EDIF;

- проект БИС арбитра шин многопроцессорной вычислительной системы, выполненный на библиотеке элементов HP-0,5 мкм;

- БИС арбитра шин для многопроцессорной вычислительной системы на основе БМК серии 5503ХМ2;

- проект БИС арбитра шин для многопроцессорной вычислительной системы на основе ПЛИС;

- проект БИС декодера сверточных турбокодов для спутниковой телекоммуникационной системы INMARSAT;

- проект статического ОЗУ для технологической линейки кремний-на-изоляторе;

- подсистема САПР для синтеза топологии статического ОЗУ для систем-на-кристалле.

Публикации по диссертации в изданиях из Перечня ВАК.

- Ковалев А.В. Асинхронный MAP-декодер с пониженным энергопотреблением// Вестник компьютерных и информационных технологий. № 7, 2009. – с. 49-55.

- Ковалев А.В., Коноплев Б.Г., Бибило П.Н. Маршрут проектирования с автоматической конвертацией проектов синхронных СБИС в асинхронные // Известия вузов. Электроника. № 3(77), 2009. – с. 18-25.

- Ковалев А.В. Метод проектирования быстродействующих асинхронных цифровых устройств с малым энергопотреблением // Известия вузов. Электроника. № 1, 2009. – с. 48-53.

- Konoplev B.G., Kovalev A.V., Kalskov V.V. New Method for Improving Quantum-Algorithm Reliability // Russian Microelectronics ISSN 1063-7397, 2007, Vol. 36, No. 2, pp. 135–138. © Pleiades Publishing, Ltd., 2007.

- Коноплев Б.Г., Ковалев А.В., Кальсков В.В. Метод повышения надежности работы квантовых алгоритмов // Микроэлектроника, 2007. №2. - с. 15 – 21.

- Ковалев А.В. Метод проектирования цифровых асинхронных устройств с малым энергопотреблением // Известия ТРТУ. Таганрог: Изд-во ТРТУ, 2005. № 9(53). – с. 123.

- Ковалев А.В. Метод проектирования систем-на-кристалле на основе сетевых алгоритмов // Известия вузов. Электроника. № 2, 2005. – с. 49-53.

- Ковалев А.В. Методика и программные средства автоматического синтеза библиотечных элементов для модулей статических ОЗУ // Известия ТРТУ. Таганрог: Изд-во ТРТУ, 2004. № 1(36). – с. 116-120.

- Ковалев А.В., Коноплев Б.Г., Рындин Е.А. Генератор топологии статических ОЗУ // Известия ТРТУ. Таганрог: Изд-во ТРТУ, 2003. № 1(30). – с. 113-114.

- Ковалев А.В. Четырехсторонние логические элементы заказных СБИС // Известия ТРТУ. Таганрог: Изд-во ТРТУ, 2001. №1(19). с. 95.

- Ковалев А.В. Логические элементы для деформируемых субблоков заказных БИС // Известия ТРТУ. Таганрог: ТРТУ, 2000. №3(17). с. 155-159.

- Ковалев А.В., Коноплев Б.Г. Метод мозаичного синтеза топологии заказных СБИС // Известия вузов. Электроника. № 4, 1999. – с.23-29.