Федеральное агентство по образованию бийский технологический институт (филиал)

| Вид материала | Документы |

| 4.6Обмен данными по шине IС 4.6.2Пример обмена данными по шине IC |

- Федеральное агентство по образованию бийский технологический институт (филиал), 981.77kb.

- Федеральное агентство по образованию Бийский технологический институт (филиал), 2694.55kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 2134.54kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 1660.78kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 1946.38kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 3460.44kb.

- Решением Ученого совета, 125.93kb.

- Федеральная целевая программа "Развитие электронной компонентной базы и радиоэлектроники", 3538.74kb.

- Бийский технологический институт (филиал), 2586.35kb.

- Министерство образования и науки федеральное агентство по образованию майкопский государственный, 102.13kb.

4.6Обмен данными по шине I2С

4.6.1Общие положения и введение в логику работы шины I2С

Разработанная фирмой Philips шина I2С (Inter-Integrated Circuit) – это двунаправленная асинхронная шина с последовательной передачей данных и возможностью адресации до 128 устройств. Физически шина содержит две сигнальные линии, одна из которых (SCL) предназначена для передачи тактового сигнала, вторая (SDA) для обмена данными. Для управления линиями применяются выходные каскады с открытым коллектором, поэтому линии шины должны быть подключены к источнику питания +5 В через резисторы сопротивлением 1–10 кОм, в зависимости от физической длины линий и скорости передачи данных. Длина соединительных линий в стандартном режиме может достигать 2 метров, скорость передачи – до 100 кбит/с.

Все абоненты шины делятся на два класса – «Master» и «Slave». Устройство «Master» генерирует тактовый сигнал (SCL) и, как следствие, является ведущим. Оно может самостоятельно выходить на шину и адресовать любое «Slave»-устройство с целью передачи или приёма информации. Все «Slave»-устройства «слушают» шину на предмет обнаружения собственного адреса и, распознав его, выполняют предписываемую операцию.

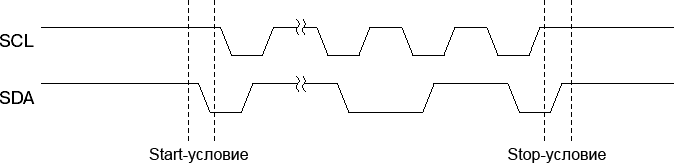

В начальный момент времени – в режиме ожидания – обе линии SCL и SDA находятся в состоянии логической единицы. В режиме передачи (рисунок 4.26) бит данных SDA стробируется положительным импульсом SCL. Смена информации на линии SDA производится при нулевом состоянии линии SCL. «Slave»-устройство может «придерживать» линию SCL в нулевом состоянии, например, на время обработки очередного принятого байта, при этом «Master»-устройство обязано дождаться освобождения линии SCL, прежде чем продолжить передачу информации.

Рисунок 4.26 – Диаграмма процесса передачи данных по шине I2C |

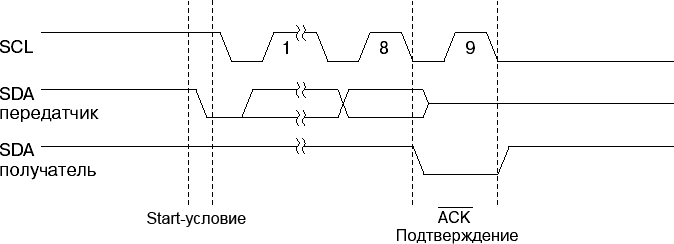

Для синхронизации пакетов шины I2C различают два условия – «Start» и «Stop», ограничивающие начало и конец информационного пакета (рисунок 4.27).

Рисунок 4.27 – Диаграмма «Start»/«Stop» условия шины I2C |

Для кодирования этих условий используется изменение состояния линии SDA при единичном состоянии линии SCL, что недопустимо при передаче данных. «Start»-условие образуется при отрицательном перепаде линии SDA, когда линия SCL находится в единичном состоянии, и наоборот, «Stop»-условие образуется при положительном перепаде линии SDA при единичном состоянии линии SCL.

Передача данных начинается по первому положительному импульсу на линии SCL (рисунок 4.28), которым стробируется старший бит первого информационного байта. Каждый информационный байт (8 битов) содержит 9 тактовых периодов линии SCL.

Рисунок 4.28 – Диаграмма подтверждения приёма байта по шине I2C |

В девятом такте устройство-получатель выдаёт подтверждение (

) – отрицательный импульс, свидетельствующий о «взаимопонимании» передатчика и получателя. Любой абонент шины, как «Master», так и «Slave», может в разные моменты времени быть как передатчиком, так и получателем и в соответствии с режимом обязан либо принимать, либо выдавать сигнал

) – отрицательный импульс, свидетельствующий о «взаимопонимании» передатчика и получателя. Любой абонент шины, как «Master», так и «Slave», может в разные моменты времени быть как передатчиком, так и получателем и в соответствии с режимом обязан либо принимать, либо выдавать сигнал  , отсутствие которого интерпретируется как ошибка.

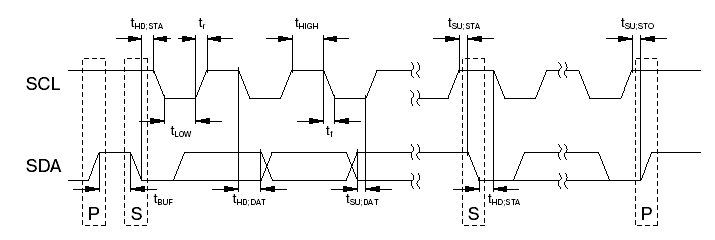

, отсутствие которого интерпретируется как ошибка.Временная диаграмма сигналов SCL и SDA шины I2С приведена на рисунке 4.29. Здесь S обозначает «Start»-условие, Р – «Stop»-условие.

Рисунок 4.29 – Временная диаграмма работы шины I2C |

4.6.2Пример обмена данными по шине I2C

Рассмотрим обмен данными по протоколу I2C на конкретном примере – между микроконтроллером и микросхемой памяти с электрическим стиранием 24С16 ёмкостью 2048 B. Схема включения приведена на рисунке 4.30.

Рисунок 4.30 – Схема подключения микросхемы 24С16

к микроконтроллеру

Назначение входов SCL и SDA приведено выше. Вход WP – вход защиты от записи. Информация может быть записана в микросхему только при логическом 0 на этом входе.

На рисунке 4.31 приведена диаграмма записи байта в память.

Рисунок 4.31 – Диаграмма записи байта в память

DEVICE ADDRES (адрес устройства) – это 8-битное слово, имеющее следующий формат:

| 1 | 0 | 1 | 0 | A10 | A9 | A8 |  |

где А8–А10 – старшая часть адреса, по которому будет записан байт данных (DATA);

– бит, определяющий тип операции (0 – запись, 1 – чтение).

– бит, определяющий тип операции (0 – запись, 1 – чтение).После того как микросхеме передаётся «Stop»-условие, она выполняет внутренний цикл записи принятых данных по указанному адресу. При этом она не реагирует на внешние сигналы. Поэтому необходимо дождаться завершения этого процесса. Для этого выполняется попытка записи в микросхему адреса устройства. Приход сигнала подтверждения свидетельствует о завершении внутреннего цикла записи.

На рисунке 4.32 приведена диаграмма чтения байта из памяти.

Рисунок 4.32 – Диаграмма чтения байта из памяти

Листинг 4.41 содержит текст программы, реализующей тестирование микросхемы. В микросхему записывается тестовая информация. После этого выполняется её чтение и проверка правильности. Один байт тестовой информации – это адрес тестируемой ячейки, увеличенный на 2.

Листинг 4.41 – Программа тестирования микросхемы 24С16

| SDA: | .REG P1.0 | ; Линия SDA |

| SCL: | .REG P1.5 | ; Линия SCL |

| WP: | .REG P1.4 | ; Линия «Защита от записи» |

| | | |

| | .ORG 0000H | ; Адрес начала программы |

| | | |

| | CLR WP SETB SDA CLR SCL | ; Разрешение записи |

| | MOV DPTR, #0000H | ; В DPTR заносится адрес, ; по которому будут ; записаны данные |

| NEXTW: | | |

| | MOV A, DPL | ; В аккумулятор заносится ; младшая часть адреса |

| | INC A | ; Увеличение содержимого ; аккумулятора на 2 |

| | INC A | |

| | CALL WRITE | ; Вызов подпрограммы ; записи в память ; по протоколу I2C |

| | INC DPTR | ; Увеличение адреса |

| | MOV A, DPH | ; Проверка предела заполнения ; памяти и переход на начало ; цикла записи, если память ; заполнена не полностью |

| | CJNE A, #08H, NEXTW | |

| | | |

| | MOV DPTR, #0000H | ; В DPTR заносится адрес, ; из которого будут ; считаны данные |

| NEXTR: | | |

| | CALL READ | ; Вызов подпрограммы ; чтения из памяти ; по протоколу I2C |

| | DEC A | ; Уменьшение считанного ; значения на 2 |

| | DEC A | |

| | CJNE A, DPL, ERROR | ; Проверка правильности ; записанных данных ; Переход на подпрограмму ; ERROR, если данные ; записаны неправильно |

| | INC DPTR | ; Увеличение адреса |

| | MOV A, DPH | ; Проверка предела чтения ; памяти и переход на начало ; цикла чтения, если память ; считана не полностью |

| | CJNE A, #08H, NEXTR | |

| | MOV A, #55H | ; В аккумулятор заносится ; 55H, если тест памяти ; пройден |

| | JMP BEGIN | ; Переход к основной ; программе |

| | | |

| ERROR: | | |

| | MOV A, #AAH | ; В аккумулятор заносится ; ААh, если обнаружена ошибка |

| BEGIN: | | ; Основная программа |

| | … | |

| ; Подпрограмма записи байта информации в память по протоколу I2C | ||

| WRITE: | | |

| | MOV 10H, A | ; В ячейке 10H сохраняются ; записываемые данные |

| ; Формирование адреса устройства (режим записи) | ||

| | MOV A, DPH | ; В аккумулятор заносится ; старшая часть адреса |

| | RL A | ; Выполняется сдвиг влево |

| | ANL A, #0EH | ; Обнуление битов 0, 4, 5, 6 и 7 |

| | ORL A, #A0H | ; Установка битов 5 и 7 |

| | MOV 11H, A | ; Сохранение адреса ; устройства в ячейке 11H |

| | ||

| | LCALL START | ; Вызов процедуры, ; генерирующей «Start»- ; условие |

| | MOV A,11H | ; Запись адреса устройства |

| | LCALL BYTE | |

| | MOV A,DPL | ; Запись младшего байта ; адреса |

| | LCALL BYTE | |

| | MOV A,10H | ; Запись байта информации |

| | LCALL BYTE | |

| | LCALL STOP | ; Вызов процедуры, ; генерирующей «Start»- ; условие |

| | | |

| | MOV 1DH,#00H | ; Цикл ожидания ; подтверждения ; В цикле 256 раз выполняется ; подача «Start»-условия, ; запись адреса устройства, ; проверка подтверждения ; (логический 0 ; на линии SDA) и подача ; «Stop»-условия ; Как только приходит ; подтверждение, в ; аккумулятор ; помещается байт ; информации ; и выполняется выход из ; подпрограммы ; Если подтверждение не ; формируется, в аккумулятор ; помещается инверсное ; значение байта информации ; и выполняется выход из ; подпрограммы |

| W3: | | |

| | DJNZ 1DH,W1 | |

| | LJMP W2 | |

| W1: | | |

| | LCALL START | |

| | MOV A,11H | |

| | | |

| | LCALL BYTE | |

| | JC W3 | |

| | | |

| | LCALL STOP | |

| | MOV A,10H | |

| | RET | |

| W2: | | |

| | LCALL STOP | |

| | MOV A,10H | |

| | CPL A | |

| | RET | |

| ; Подпрограмма, генерирующая «Start»-условие | ||

| START: | | |

| | SETB SCL | |

| | CLR SDA | |

| | CLR SCL SETB SDA | |

| | RET | |

| | | |

| ; Подпрограмма выдачи байта в последовательной форме ; (Передаётся содержимое аккумулятора) | ||

| BYTE: | | |

| | MOV 1CH, #08H | ; В ячейку 1CH помещается ; количество передаваемых ; бит |

| WBIT: | | |

| | RLC A | ; Сдвиг содержимого ; аккумулятора влево ; (Старший бит ; помещается во ; флаг переноса) |

| | MOV SDA,C | ; Выдача «выдвинутого» бита ; в линию SDA |

| | SETB SCL | ; Формирование тактового ; импульса на линии SCL |

| | CLR SCL | |

| | DJNZ 1CH, WBIT | ; Проверка условия выхода из ; цикла |

| | SETB SDA | ; Установка логической 1 на ; линии SDA |

| | SETB SCL | ; Установка логической 1 на ; линии SCL |

| | MOV C, SDA | ; Считывание сигнала ; подтверждения |

| | CLR SCL | ; Установка логического 0 на ; линии SCL |

| | RET | ; Выход из подпрограммы |

| ; Подпрограмма, генерирующая «Stop»-условие | ||

| STOP: | | |

| | CLR SDA | |

| | SETB SCL | |

| | SETB SDA CLR SCL | |

| | RET | |

| | | |

| ; Подпрограмма чтения байта информации из памяти по протоколу I2C | ||

| READ: | | |

| ; Формирование адреса устройства (режим записи) | ||

| | MOV A, DPH | |

| | RL A | |

| | ANL A, #0EH | |

| | ORL A, #A0H | |

| | MOV 11H, A | |

| | | |

| | LCALL START | ; Вызов процедуры ; генерирующей «Start»- ; условие |

| | | |

| | MOV A, 11H | ; Запись адреса устройства |

| | LCALL BYTE | |

| | MOV A, DPL | ; Запись младшего байта ; адреса |

| | LCALL BYTE | |

| | | |

| | LCALL START | ; Вызов процедуры ; генерирующей «Start»- ; условие |

| | ||

| ; Формирование адреса устройства (режим чтения) | ||

| | MOV A, 11H | |

| | SETB ACC.0 | |

| | LCALL BYTE | ; Запись адреса устройства |

| ; Подпрограмма приёма байта в последовательной форме ; (Результат сохраняется в аккумуляторе) | ||

| | MOV R0, #08H | ; В регистр R0 помещается ; количество принимаемых ; бит |

| RBIT: | | |

| | SETB SCL | ; Установка логической 1 на ; линии SCL |

| | MOV C, SDA | ; Сохранение состояния ; линии SDA (бит информации) |

| | RLC A | ; Сдвиг содержимого ; аккумулятора влево ; («вдвигается» принятый бит) |

| | CLR SCL | ; Установка логического 0 на ; линии SCL |

| | DJNZ R0, RBIT | ; Проверка условия выхода из ; цикла |

| | SETB SDA | ; Установка логической 1 на ; линии SDA |

| | | |

| | SETB SCL | ; Установка логической 1 на ; линии SCL |

| | CLR SCL | ; Установка логического 0 на ; линии SCL |

| | CALL STOP | ; Вызов процедуры ; генерирующей «Stop»- ; условие |

| | RET | ; Выход из подпрограммы |

Контрольные вопросы

- Что такое шина I2C?

Чем отличается «Master» от «Slave» устройства?

Каковы этапы приема байта информации от «Slave» устройства по шине I2C?

Какое устройство на шине I2C выдает сигнал ACK и в каком случае?

Для чего нужны «Start»- и «Stop»-условия?