Федеральное агентство по образованию бийский технологический институт (филиал)

| Вид материала | Документы |

- Федеральное агентство по образованию бийский технологический институт (филиал), 981.77kb.

- Федеральное агентство по образованию Бийский технологический институт (филиал), 2694.55kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 2134.54kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 1660.78kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 1946.38kb.

- Федеральное агентство по образованию бийский технологический институт (филиал), 3460.44kb.

- Решением Ученого совета, 125.93kb.

- Федеральная целевая программа "Развитие электронной компонентной базы и радиоэлектроники", 3538.74kb.

- Бийский технологический институт (филиал), 2586.35kb.

- Министерство образования и науки федеральное агентство по образованию майкопский государственный, 102.13kb.

4.4Преобразование кодов

В задачах управления может возникнуть необходимость преобразования информации из одной формы представления в другую. Это связано с тем, что обработка данных в МК осуществляется в параллельном двоичном коде, а поступать в МК и выводиться из него информация может в иной форме представления.

Наиболее распространены в задачах логического управления следующие преобразования:

– из унитарного кода в двоичный (при вводе информации с клавиатуры или от оцифрованных переключателей);

– из двоичного в унитарный;

– из одной системы счисления в другую (при работе со специальными клавиатурами);

– специальные преобразования (для организации индикации и при выводе информации на периферийные устройства);

– из последовательного кода в параллельный (при вводе) и из параллельного в последовательный (при выводе);

– из аналоговой формы представления в цифровую, и наоборот (для связи с аналоговыми датчиками и исполнительными механизмами).

4.4.1Преобразование унитарного кода в двоичный позиционный

Двоичный эквивалент унитарного кода равен номеру бита, в котором находится единственная единица или ноль. Данное преобразование осуществляется путем сдвига исходного унитарного кода в сторону младших бит с одновременным подсчетом числа сдвигов. При «выдвигании» из младшего бита значения 1 (или 0) сдвиги прекращаются, а в счетчике сдвигов будет содержаться двоичный эквивалент унитарного кода (листинг 4.27).

Листинг 4.27 – Программа преобразования унитарного кода

в двоичный позиционный

; Активным сигналом для бита является логическая 1.

| | .ORG 0000h | ; Адрес начала программы |

| NEXT: EXIT: | MOV P1, #FFh MOV A, P1 MOV R0, #FFh JZ EXIT INC R0 CLR C RRC A JMP NEXT … | ; Настройка порта P1 на ввод ; Считывание данных из порта P1 ; Обнуление счётчика циклов ; Выход из процедуры, если считанное ; значение 0 ; Увеличение счетчика циклов ; Сброс флага переноса ; Сдвиг вправо считанного значения с ; учётом переноса ; Переход на начало цикла |

4.4.2Преобразование двоичного позиционного кода в унитарный

Необходимость такого преобразования возникает при выборе одного из исполнительных устройств, подключенных к параллельному порту контроллера, по номеру этого устройства.

Алгоритм преобразования включает следующие шаги:

– в регистр сдвига (R) загружается число 00000001b;

– если преобразуемый двоичный код (B) не равен нулю, то выполняется сдвиг содержимого регистра R влево В раз, иначе программа преобразования завершается.

Листинг 4.28 демонстрирует преобразование трехбитного двоичного кода, хранящегося в аккумуляторе, в 8-битный унитарный.

Листинг 4.28 – Программа преобразования 3-битного двоичного кода, хранящегося в аккумуляторе, в 8-битный унитарный

| | .ORG 0000h | ; Адрес начала программы |

| GO: NEXT: EXIT: | … ANL A, #07H MOV R0, A MOV A, #01H CJNE R0, #00H, GO JMP EXIT CLR C RLC A DJNZ R0, NEXT … | ; Обнуление незначащих бит ; Сохранение двоичного кода в ; регистре R0 ; Загрузка регистра сдвига ; Сравнение преобразуемого ; двоичного кода с нулём ; Выход из подпрограммы, если ; преобразуемый код 000b ; Сброс флага переноса ; Сдвиг влево содержимого ; аккумулятора ; Проверка условия выхода из ; цикла ; Выход из подпрограммы |

После выхода из подпрограммы результат хранится в аккумуляторе.

4.4.3Преобразование кодов из одной системы счисления в другую

Преобразование кода из одной позиционной системы счисления в другую осуществляется делением исходного числа на основание новой системы счисления. При этом деление должно выполняться по правилам исходной системы счисления. Например, для преобразования двоичного числа в двоично-десятичное исходное двоичное число должно быть поделено на 10. Деление должно осуществляться по правилам двоичной арифметики.

Пусть требуется выполнить преобразования 8-битного двоичного числа в двоично-десятичное. Исходный двоичный код хранится в аккумуляторе. Результат преобразования состоит из 12 бит: младшие

4 бита – единицы, представляют собой остаток от деления исходного числа на 10; следующее 4 бита – десятки, представляют собой остаток от деления на 10 полученного частного; старшие 4 бита – сотни, являются частным от второго деления. Листинг 4.29 содержит программу преобразования однобайтового двоичного кода в двоично-десятичный.

Листинг 4.29 – Программа преобразования однобайтового двоичного кода в двоично-десятичный

| | .ORG 0000h | ; Адрес начала программы |

| | MOV A, #255 MOV B, #10 DIV AB MOV DPL, B MOV B, #10 DIV AB MOV DPH, A MOV A, B SWAP A ORL A, DPL MOV DPL, A ... | ; Загрузка в аккумулятор ; преобразуемого числа (255) ; Загрузка в регистр B ; делителя ; Деление A на B ; Сохранение остатка от ; деления (единиц) в регистре ; DPL. Регистр A содержит ; частное от первого деления ; Загрузка в регистр B ; делителя ; Деление A на B ; Сохранение частного от ; второго деления в DPH ; Сохранение остатка от ; второго деления в старшей ; тетраде регистра DPL |

Результат выполнения программы сохраняется в регистре DPTR. Формат результата приведен на рисунке 4.19.

| DPTR | |||||||||||||||

| DPH | DPL | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Незначащие | Сотни | Десятки | Единицы | ||||||||||||

Рисунок 4.19 – Формат результата преобразования

Обратное преобразование (из двоично-десятичного кода в двоичный) заключается в расчёте суммы:

«единицы» + «десятки» × 10 + «сотни» × 100…

Программа преобразования двухзначного двоично-десятичного кода в двоичный приведена в листинге 4.30.

В приведённой программе исходное значение хранится в младших двенадцати битах регистра DPTR. Результат сохраняется в аккумулятор.

Листинг 4.30 – Программа преобразования двухзначного

двоично-десятичного кода в двоичный

| | .ORG 0000H | ; Адрес начала программы |

| | … MOV A, DPL SWAP A ANL A, #0FH MOV B, #10 MUL AB PUSH A MOV A, DPL ANL A, #0FH MOV DPL, A POP A ADD A, DPL MOV DPL, A MOV A, DPH ANL A, #0FH MOV B, #100 MUL AB ADD A, DPL … | ; Выделение десятков ; Умножение десятков на 10 ; Сохранение в стек ; результата умножения ; Выделение единиц ; Восстановление из стека ; Сложение единиц и ; результата умножения ; Выделение сотен ; Умножение сотен на 100 ; Сложение результата умножения ; с числом «единицы»+«десятки»×10 |

Кроме рассмотренного способа преобразования чисел из одной системы счисления в другую, можно воспользоваться более медленным, но зато и более простым способом «двух счетчиков». При этом способе из исходного кода вычитается, а к новому коду прибавляется по единице до обнуления исходного кода, причем вычитание осуществляется «в старой», а прибавление – в «новой» системе счисления. Пример программы преобразования двоичного числа в двоично-десятичное методом двух счетчиков приводится ниже (листинг 4.31).

В приведенной программе исходный двоичный код должен находиться в аккумуляторе, двоично-десятичный код – в регистре DPTR.

Листинг 4.31 – Программа преобразования двоичного числа

в двоично-десятичное методом двух счетчиков

| | .ORG 0000h | ; Адрес начала программы |

| NEXT: EXIT: | MOV A, #200 MOV DPTR, #0000H JZ EXIT MOV R0, A MOV A, DPL ADD A, #01H DA A MOV DPL, A MOV A, DPH ADDC A, #00H DA A MOV DPH, A DJNZ R0, NEXT … | ; в A преобразуемое число ; Обнуление регистра DPTR ; Выход из подпрограммы ; преобразования, если ; преобразуемое число 0 ; В регистр-счётчик (R0) ; преобразуемое число ; Увеличение регистра DPL ; на единицу и его ; двоично-десятичная ; коррекция ; Увеличение регистра DPH ; на единицу, если возник ; перенос при увеличении ; регистра DPL и ; двоично-десятичная коррекция ; результата ; Уменьшение счетчика циклов ; (R0) и переход на начало цикла, ; если R0 не равно 0 |

4.4.4Преобразование данных из параллельного кода

в последовательный и обратно

Наиболее распространенным применением процедур преобразования параллельной формы в последовательную и обратно является связь с удаленными датчиками, исполнительными механизмами и другими МК по однопроводным и двухпроводным линиям передачи информации.

Для этих целей удобно использовать аппаратные средства микроконтроллера – последовательный порт (см. п. 1.3.4). Порт может работать в двух режимах: в режиме сдвигающего регистра и режиме универсального асинхронного приёмопередатчика.

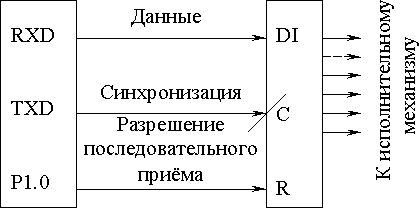

Работа последовательного порта в режиме сдвигающего регистра предполагает синхронную выдачу и приём битов информации (рисунок 4.20).

Внешнее устройство, принимающее информацию, должно «защёлкивать» биты по переднему фронту сигнала на выходе TXD, выдающее – устанавливать данные по заднему фронту.

Выдача информации в этом режиме может быть реализована следующим образом (листинг 4.32).

|  |

| Рисунок 4.20 – Организация последовательного синхронного обмена между микроконтроллером и периферийным устройством | |

Листинг 4.32 – Программа выдачи информации микроконтроллером

| | ORG 0000H | ; Адрес начала программы |

| NEXT: | MOV IE, #00H MOV SCON, #00H MOV P0, #FFH MOV A, P0 SETB P1.0 MOV SBUF, A JNB TI, $ CLR P1.0 CLR TI JMP NEXT | ; Запрет всех прерываний ; Настройка последовательного ; порта контроллера на режим ; синхронной передачи ; Настройка порта P0 на ввод ; Чтение данных из порта P0 ; Разрешение внешнему ; устройству приёма данных ; Запись данных в регистр SBUF ; (при этом автоматически ; начинается выдача данных) ; Ожидание завершения передачи ; Запрет внешнему устройству ; приёма данных ; Сброс флага конца передачи ; Переход на начало цикла |

Процедура приёма данных аналогична процедуре выдачи (листинг 4.33).

Листинг 4.33 – Программа приёма информации микроконтроллером

| | ORG 0000H | ; Адрес начала программы |

| NEXT: | MOV IE, #00H MOV SCON, #10H SETB P1.0 JNB RI, $ MOV A, SBUF MOV P0, A CLR P1.0 CLR RI JMP NEXT … | ; Запрет всех прерываний ; Настройка последовательного ; порта контроллера на режим ; синхронного приёма ; Разрешение внешнему ; устройству на передачу данных ; Ожидание завершения приёма ; Чтение данных из регистра SBUF ; и их выдача в P0 ; Запрет внешнему устройству ; передачи данных ; Сброс флага конца приёма ; Переход на начало цикла |

Режим универсального приёмопередатчика удобно использовать для асинхронной выдачи и асинхронного приёма информации по последовательному каналу связи (например, по интерфейсу RS-232). Описание работы последовательного порта в режиме универсального приёмопередатчика приведено в п. 1.3.4.

Программа, реализующая прием байта данных, его инвертирование и выдачу обратно (подобная процедура часто используется для тестирования физических линий связи), реализована следующим образом (листинг 4.34).

Листинг 4.34 – Программа, демонстрирующая асинхронный обмен

информации через последовательный порт

| FOSC: BR: COUNT: | .EQU 18432000 .EQU 9600 .EQU 256-(FOSC/(BR*192)) | ; Частота кварцевого ; резонатора ; Скорость обмена (бод) ; Число, загружаемое в ; таймер-счетчик T/C2 |

| | .ORG 0000H | ; Адрес начала программы |

| CICLE: | MOV TMOD, #20H MOV SCON, #50H ORL PCON, #80H MOV TH1, #COUNT MOV TL1, TH1 CLR TI CALL READ CPL A CALL SEND JMP CICLE | ; Настройка T/C2 в режим ; с автоперезагрузкой ; Настройка ; последовательного порта ; Установка бита 7 ; регистра PCON (бит ; влияет на скорость ; передачи) ; Загрузка регистров T/C2 ; Сброс флага готовности ; передатчика ; Сброс флага готовности ; приёмника ; Вызов процедуры приёма ; Инвертирование ; полученного байта ; Вызов процедуры выдачи ; Переход на начало цикла |

| ; ПОДПРОГРАММЫ | ||

| ; Подпрограмма асинхронного приёма | ||

| READ: | JNB RI, $ MOV A, SBUF CLR RI RET | ; Ожидание установки ; флага готовности ; приёмника ; (устанавливается при ; получении символа) ; Считывание в ; аккумулятор принятого ; байта ; Сброс флага готовности ; приёмника ; Выход из подпрограммы |

| ; Подпрограмма асинхронной выдачи | ||

| SEND: | MOV SBUF, A JNB TI, $ CLR TI RET | ; Загрузка в регистр ; SBUF Отправляемого ; значения ; Ожидание установки ; флага готовности ; передатчика ; Сброс флага готовности ; передатчика ; Выход из подпрограммы |

4.4.5Цифро-аналоговое преобразование

Преобразование информации из цифровой формы в аналоговую осуществляется путем подключения ЦАП к одному из портов МК. Выдача аналогового управляющего воздействия в этом случае сводится к команде пересылки двоичного кода в порт. При этом на выходе ЦАП появится напряжение (ток), пропорциональное двоичному коду, загруженному в порт.

Некоторые объекты управления могут требовать непрерывного воздействия изменяющегося сигнала. Простейшим случаем является формирование линейно изменяющегося сигнала (рисунок 4.21, листинг 4.35).

Рисунок 4.21 – Принцип формирования линейно изменяющегося сигнала с помощью ЦАП |

Листинг 4.35 – Программа формирования линейно изменяющегося сигнала

| | . ORG 0000H | ; Адрес начала программы |

| NEXT: | MOV A, #00H MOV P1, A CALL DELAY INC A JMP NEXT | ; Обнуление аккумулятора ; Пересылка содержимого ; аккумулятора в порт P1 ; Вызов подпрограммы, ; реализующей задержку ; Инкремент аккумулятора ; Переход на начало цикла |

Программа формирования аналогового сигнала, заданного таблично, приведена в листинге 4.36.

Листинг 4.36 – Программа формирования аналогового сигнала,

заданного таблично

| | . ORG 8000H | ; Адрес начала программы |

| CYCLE: NEXT: | MOV DPTR, #TABLE MOV A, #00H MOVC A, @A+DPTR MOV P1, A CALL DELAY INC DPTR MOV A, DPH CJNE A, # MOV A, DPL CJNE A, #>END, NEXT JMP CYCLE | ; Загрузка в DPTR базового ; адреса таблицы ; Загрузка в аккумулятор ; смещения относительно ; базового адреса (00) ; Чтение байта из таблицы ; Пересылка считанного ; байта в порт ; Вызов подпрограммы, ; реализующей задержку ; Увеличение адреса ; обращения к таблице ; Проверка вхождения в ; пределы таблицы ; Переход на начало ; программы, если считано ; последнее значение из ; таблицы |

| TABLE: | | |

| | .DB 00, 01, 02, 02, 02, 03 .DB 03… | ; Таблица значений ; реализуемой функции |

| END: | | |

4.4.6Аналого-цифровое преобразование

Преобразование аналогового сигнала от датчика в цифровой код, принимаемый и обрабатываемый в МК, можно осуществить несколькими способами:

– аппаратным на основе микросхемы АЦП, подключаемой к порту МК. В этом случае МК только инициирует АЦП и через заданные периоды преобразования считывает из него цифровой код. Данный способ характеризуется самым высоким быстродействием, но требует использования АЦП, что далеко не во всех применениях МК является оправданным с экономической точки зрения;

– программно-аппаратным на основе ЦАП и программы взвешивания битов (методом последовательного приближения). Данный способ характеризуется меньшим быстродействием, но требует использования относительно простых и дешевых микросхем ЦАП и операционного усилителя;

– программно-аппаратным способом на основе метода двойного интегрирования. Это самый дешевый, но и наиболее медленный способ. Данный способ может обеспечить достижение очень высокой точности преобразования;

– программно-аппаратным на основе использования преобразователя напряжение–частота и программы измерения периода сигнала.

Наибольший практический интерес представляют последние 3 способа, так как их использование обеспечивает получение высоких технико-экономических характеристик микропроцессорной системы относительно простыми средствами.

4.4.6.1Метод последовательного приближения

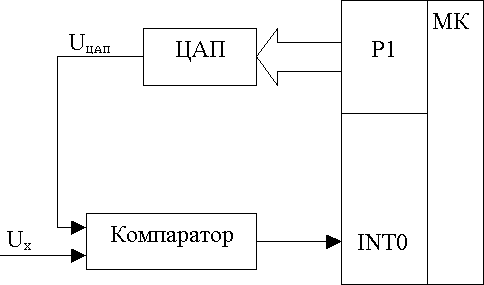

При использовании данного способа преобразования аналогового сигнала в код, из дополнительной аппаратуры в микроконтроллерном устройстве используются ЦАП и сравнивающий компаратор. Схема включения приведена на рисунке 4.22.

Рисунок 4.22 – Структурная схема аналого-цифрового преобразования по методу последовательного приближения

Микроконтроллер через порт Р1, работающий в режиме вывода, передает двоичные коды в ЦАП, выход которого соединяется с одним из входов компаратора. На второй вход компаратора подаётся преобразуемое напряжение. Сигнал с выхода компаратора подаётся на вход микроконтроллера.

На выходе компаратора формируется логический 0, если напряжение на выходе ЦАП (Uцап) меньше преобразуемого напряжения (Ux). Если Uцап>Ux, на выходе компаратора формируется логическая единица.

Программа аналого-цифрового преобразования (листинг 4.37) работает следующим образом: МК выдает через порт P1 байт данных, преобразуемый ЦАП в аналоговый сигнал Uцап и сравниваемый с входным аналоговым сигналом Ux, а затем анализирует результат сравнения. В зависимости от значения сигнала на входе INT0 МК или оставляет старший бит выводимого байта в 1, если Uцап

Листинг 4.37 – Программа аналого-цифрового преобразования

методом последовательного приближения

| NEXT: ENOUGH: | .ORG 0000H MOV R0,#08H MOV R1, #01H MOV R2, #00H MOV A, R1 RR A MOV R1, A ORL A, R2 MOV P1, A JB INT0, ENOUGH MOV R2, A DJNZ R0, NEXT | ; Адрес начала программы ; Инициализация счётчика битов ; Инициализация регистра сдвига ; Инициализация регистра ; результата ; Ротация регистра сдвига ; Логическое сложение регистра ; сдвига и регистра результата ; (Результат сохраняется в ; аккумуляторе) ; Выдача в порт результата ; сложения ; Проверка результата сравнения ; Если на выходе компаратора 1, ; то регистр результата не ; изменяется (переход), ; иначе результат логического ; сложения сохраняется в R2 ; Переход на начало цикла |

4.4.6.2Метод двойного интегрирования

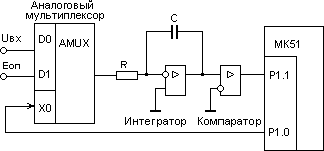

Схема подключения к МК дополнительной аппаратуры показана на рисунке 4.23, временные диаграммы, поясняющие принцип метода двойного интегрирования, приведены на рисунке 4.24.

Рисунок 4.23 – Структурная схема аналого-цифрового преобразования по методу двойного интегрирования

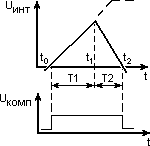

Рисунок 4.24 – Временные диаграммы, поясняющие принцип метода двойного интегрирования

Первоначально на вход интегратора подается отрицательное напряжение Eоп. При этом на выходе интегратора через некоторое время установится отрицательный уровень, а на выходе компаратора будет сформирован сигнал логического 0.

Процесс преобразования состоит из двух этапов. Сначала производится интегрирование входного аналогового сигнала в течение строго определенного времени Т1. Отсчет интервала Т1 производится от момента t0 перехода напряжения на выходе интегратора через нуль. Входной преобразуемый сигнал (для данной схемы) должен быть положительным. Затем в момент времени t1 на вход интегратора подается опорное отрицательное напряжение Eоп и измеряется время интегрирования Т2, которое и будет пропорционально входному напряжению (Uвх).

Время Т1 выбирается так, чтобы при максимальном входном напряжении интегратор не вошел в насыщение.

Листинг 4.38 содержит программу аналого-цифрового преобразования методом двойного интегрирования. После выполнения программы результат сохраняется в регистрах TH0:TL0.

Листинг 4.38 – Программа аналого-цифрового преобразования

методом двойного интегрирования

| TIME: | .EQU #7FFFH | ; Время интегрирования |

| | | |

| | .ORG 0000H | ; Адрес начала программы |

| | CLR EA | ; Запрет всех прерываний |

| | MOV TMOD,#01H | ; Настройка таймер-счётчика Т/С0 |

| | MOV TL0, # MOV TH0, #>TIME | ; Загрузка Т/С0 |

| | SETB P1.1 | ; Настройка Р1.1 на ввод |

| | SETB P1.0 | ; Подача Еоп на вход интегратора |

| | JB P1.1, $ | ; Ожидание появления на выходе ; интегратора отрицательного ; уровня |

| | CLR P1.0 JNB P1.1, $ SETB TR0 JNB TF0,$ | ; Подача Uвх на вход интегратора ; ожидание момента Т0 ; Запуск Т/С0 ; Ожидание момента Т1 |

| ; НАЧАЛО ОБРАТНОГО ИНТЕГРИРОВАНИЯ | ||

| | SETB P1.0 | ; Подача Еоп на вход интегратора |

| | MOV TL0, #00H MOV TH0, #00H JNB P1.1, $ CLR TR0 … | ; Загрузка Т/С0 ; Ожидание появления на выходе ; интегратора отрицательного ; уровня ; Остановка счётчика Т/С0 |

Контрольные вопросы

- Для чего необходимо преобразование кодов в микроконтроллерных устройствах?

Преобразование каких кодов наиболее часто выполняется микроконтроллером?

Для чего необходим двоично-десятичный код?

Как организуется преобразование из двоичного кода в двоично-десятичный и обратно?

Для чего необходимо преобразование последовательного кода в параллельный и обратно?

Что такое цифро-аналоговое преобразование и для чего оно нужно?

Опишите методы аналого-цифрового преобразования, применяемые в микроконтроллерных устройствах.