Ылым министрлігі қазақ инженерлік теникалық академиясы

| Вид материала | Документы |

- Ылым министрлігі ы. Алтынсарин атындағЫ Ұлттық білім беру академиясы, 651.63kb.

- Ылым министрлігі әЛ–фараби атындағЫ Қазақ Ұлттық университеті, 577.59kb.

- Ылым министрлігі л. Н. Гумилев атындағы еуразия ұлттық университеті заң факультеті, 1996.9kb.

- Ылым министрлігі с. Аманжолов атындағы шығыс қазақстан мемлекеттік университеті, 983.92kb.

- Ылым министрлігі «ТҰран» университеті, 5763.02kb.

- Қазақстан Республикасының Білім және ғылым министрлігі, 787.91kb.

- Ылым министрлігі министерство науки и образования республики казахстан л. Н. Гумилев, 255.46kb.

- Қазақстан Республикасы білім және ғылым министрлігі, 686kb.

- Ылым министрлігі ministry of education and science of republic of kazakhstan, 2153.05kb.

- Қазақстан Республикасының Білім және ғылым министрлігі, 122.27kb.

^ 5. Студенттердің білімін бағалау жүйесі

- Жұмыс нәтижесін бағалау үшін аяқталған және ұсынылған әр тәжірибелік сабақ студентпен алынған Аралық бақылау нәтижесі балл негізінде бағаланады.

- Ағымды бақылау апта сайын форумда жүргізілетін «сұрақ-жауап» түрінде жүргізіледі. Мақсаты-теориялық оқу материалдарын түсінуді және меңгеруді, тәжірибелік тапсырмаларды шешу кезінде теориялық тапсырмаларды қолдануды білуді жүйелі тексеру.

- ^ Аралық бақылау сессия кезінде 2 рет жүргізіледі. Мақсаты-оқу материалдардың анықталған бөлігін меңгеру деңгейін тексеру.

- Аралық бақылау нәтижесі форумда белсенді қатысқаны үшін алынған бағаланатын шаралар және баллдар тапсырған кезде студентпен алынған балл негізінде бағаланады.

- Бағаланатын шаралар бойынша баллдарды бөлу тең жүзеге асырылады.

Қортынды бақылау емтихан формасында жүргізіледі және 40% студенттердің білімінің қортынды бағасын құрайды.

- Оқу жетістіктерінің бағалау критерилері. Несие технологияларының талаптарына сәйкес қортынды бағаны анықтау кезінде:

60%- студенттің білімін ағымды рейтенг үшін

40%-қортынды емтихан үшін

- Семестр үшін студенттің білімін бақылау кезінде ең жоғары жинауы мүмкін:

100 балл-100%

Ағымды рейтенг-60 балл

Қортынды емтихан-40 балл

- Осы жүйеде қортынды баға 1 формула бойынша анықталады:

ИО=РК+ИЭ, кайда

ИО-қортынды баға

РК-аралық бақылау

ИЭ-қортынды емтихан

Осы жүйедегі студенттің білімін аралық бақылау 2 формула бойынша анықталады:

РК=(У+А)+ОМ кайда

У-форумдарға қатысу

А-чаттардағы белсенділік

ОМ-бағаланатын шаралар

(У) форумдарға қатысу –12 балл

(ОМ) бағаланатын шаралар-36 балл

- Студенттердің оқу жетістіктері онбалдық әріптік жүйе бойынша бағаланады.

| Әріптік баға | Баллдар | %-мазмұны | Дәстүрлі баға |

| А | 4,00 | 95-100 | Өте жақсы |

| А- | 3,67 | 90-94 | |

| В+ | 3,33 | 85-89 | Жақсы |

| В | 3,00 | 80-84 | |

| В- | 2,67 | 75-79 | |

| С+ | 2,33 | 70-74 | қанағаттанарлық |

| С | 2,00 | 65-69 | |

| С- | 1,67 | 60-64 | |

| D+ | 1,33 | 55-59 | |

| D | 1,00 | 50-54 | |

| F | 0,67 | 0-49 | қанағаттанарлықсыз |

6. Ұсынылатын әдебиеттер тізімі

^ 6.1.Негізгі әдебиеттер

- М. Гук Современные микропроцессоры Pentium, Pentium II, Pentium III

Издательство "Питер" 2000г.

- М. Гук Аппаратные средства IBM PC Издательство «ПитерКом» П. 1999г.

- 3. Жаров А. Железо IBM 2000 или все о современном компьютере. – М.: Микроарт.

- Олссон Г., Пиани Д. Цифровые системы автоматизации и управления. -

Спб.: Невский диалект, 2001.-557с,

- Цифровая обработка сигналов./Сергиенко А.Б. -Спб.: Питер, 2002.-608с.

- Шалыто А.А. Логическое управление. Методы аппаратной и

программной реализации алгоритмов. - Спб.: Наука, 2000. - 780с.

- Степоненко О. С. Компьютер внутри. – Киев: Логос, 1998. -128.

- Микропроцессоры и микропроцессорные комплекты интегральных

микросхем: Справочник. В 2-х т./В.Б. Абрайтис, Н. Н. Аверьянов и др.

Под ред. В.А. Шахнова. - М.: Радио и связь, 1988.

^ 6.2. Қосымша әдебиеттер

- Аристова П.И., Корнеева А.А. Промышленные программно-аппаратные

средства на отечественном рынке АСУ ТП. - М.: Научтехиздат, 2001.-

400с.

- Смит Дж. Сопряжение компьютеров с внешними устройствами. Уроки

реализации: пер. с англ.-М.: 2000.- 266с.

- Мячев А. А. Интерфейсы средств вычислительной техники. Справочник.

М.: Радио и связь. 1997. - 352.

- Щербо В. К., Киреечев В. М., Самойленко С. Н. Стандарты по локальным

вычислительным сетям. Справочник. М: Радио и связь. 1990. - 304.

- Хоникатт Дж. Использование Internet. 2-е изд.: Пер. с англ. - Киев:

Диалектика, 1997. - 304 с.

- Микропроцессорные системы./ М.С. Куприянов, Р.И. Грушвицкий, О.Е.

Мартынов и др. Под. ред Д.В.Пузанкова Учебное пособие для вузов. -

СПб, Политехника, 2002, 936 с.

- Щелкунов Н.П., Дианов А.П. Микропроцессорные средства и системы. -

М.: Радио и связь, 1989. - 288 с.

- Фрир Дж. Построение вычислительных систем на базе перспективных

микропроцессоров: Пер. с англ. - М.: Мир, 1990. -413 с. ил.

Лекциялар конспектілері

1 Лекция Микропроцессорлық жүйелердің жалпы құрылымы

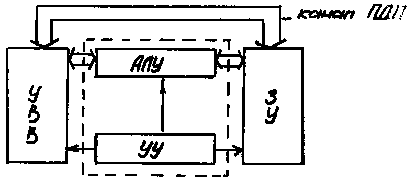

Микропроцессор-кез-келген микропроцессорлық жүйелердің орталық бөлігі (МПС) – командалық циклді тарататын АЛУ және ЦУУ енеді. МП тек МПС құрамында МП басқа зерде, енгізу/қортынды құрылым, қосалқы схемалар (такталық генератор, ПДП және тоқтату бақылаушылары, шиналық қалыптастырушы, защелктер-тіркеуші және т.б.)

Кез-келген МПС төмендегі негізгі бөлікті атап айтуға болады:

- процессорлық модуль

- зерде

- ішкі құрылым (ЗУ ішкі+енгізу/қортынды құрылым)

- бөлу жүйесі

- зердеге тіке қол жеткізу жүйесі

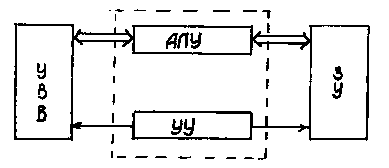

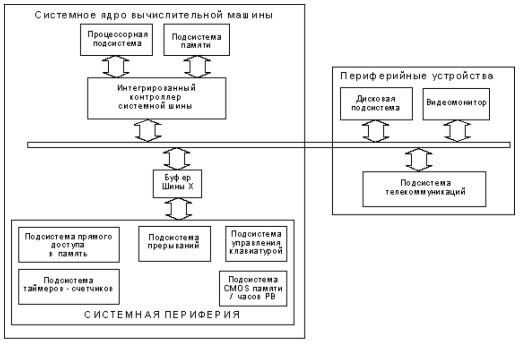

МПС процессорымен басқа құрылымдарымен байланысы радиальды байланыс принциптерімен, жалпы шинамен және құрама тәсілдерімен жүзеге асырылады. МПС біртекті әсіресе 8 және 16 разрядты процессорларында «Жалпы шина» байланыс принциптерін алды яғни барлық құрылымдар бір образбен интерфейске қосылады. (1.1. сурет)

- Сурет «Жалпы шина» интерфейспен МПС құрылымы

Интерфейстің барлық сигналдары негізгі үш топқа бөлінеді-негіздер, адрестер және басқару.

Белгілі болғандай процессор компьютердің негізгі есептеуіш блогы және көп деңгейде оның күшін анықтауыш болып табылады. Процессор – программист ойлаған және бағдарламалық кодтың модулі ретінде ресімделген бағдарламаны орындаушы болып табылады. Процессор не істейтінін түсіну үшін біріккен компьютерді ІВМ РС жүйе компоненттерінің аясында қараймыз, Осы компьютерлік архитектурамен әрине процессорларды қолдану сферасы шектелмейді.

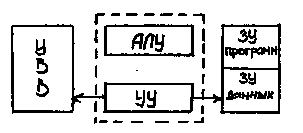

Бәріне танымал ІВМ РС – біріккен компьютер есептеуіш машиналардың фон-неймандық архитектурасын таратуды ұсынады. Бұл архитектура Джон фон-Нейман 1945 жылы ұсынылған және төмендегі негізгі признактары бар. Машина басқару блогынан, арифметикалық-логикалық құралдан (АЛУ) , зердеден және енгізу/қортынды блогынан тұрады. Одан сақтаушы бағдарлама концепциясы таратылады: негіздер және бағдарламалар бір зердеде сақталады.

- Сурет Фон-Нейман архитектурасы

1.2.Сурет Гарвардтық архитектура

Егер зердені бағдарлама зердесіне және негіздер зердесіне бөлсек онда Гарвардалық архитектураны аламыз.

Фон-найманды архитектура – ЭВМ құрудың бір варианты ғана емес басқа да көрсетілген принциптеріне сәйкес қазіргі заманғы компютерлердің көбісі осы принципте негізделген, қоса айтқанда фон-неймандық машиналарды қосқанда көп процессорлық кешендер.

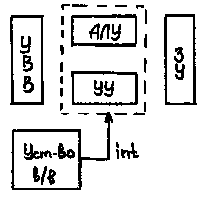

Тоқтату –Фон-нейман машиналарынан қазіргі заманғы архитектураның бірінші ерекшелігі. Тоқтату жұмысы тоқтату сигналы түскеннен кейін процессор ағымды бағдарламаның орындалуын тоқтату керектігімен және тоқтату процедурасына дайындығын бастаумен шектеледі.

1^ .3. Сурет Тоқтатумен фон-нейман архитектурасы

1^ .3. Сурет Тоқтатумен фон-нейман архитектурасы ЗТҚ (Зердеге тікелей қол жеткізу) – фон-Нейман машинасынан қазіргі заманғы архитектураның ерекшілігі екінші ерекшілік. ЗТҚ ақпартқа единица жіберу шығындарын қысқартады.

1.4. Сурет ЗТҚ каналымен фон-Нейман архитектурасы

^ 2. Лекция Микропроцессорлар архитектурасы

ІВМ РС шиналық ұйым

ІВМ РС архитектурасы негізіне оның ерекше бөлігі болып табылатын ашық принциптері орналасқан. Персоналды машиналар аясындағы ІВМ негізгі бақталастығы бұған бірнеше жылдардан соң осы айтылған принцип ІВМ фирмасының персоналды компьютерлеріне компьютерлік рынокты басып алуға жол берген кезде келді.

Ашық принциптер біріншіден, ІВМ РС төтенше дамыған яғни қолданушының «қосу» бағдарламасының барлық ресурстарға кез-келген деңгейде тоқтату жүйесіне екіншіден,ақпараттық ағымды ұйымдастыратын шина жүйесінде яғни қолданушының өзінің аппаратттық құралдарын процессорға қосуға ғана емес сонымен қатар ақпараттық ағымдарды ұйымдастыру кезінде принциптік өзгертулерсіз немесе қосымша жүргізулер есебінен архитектураның өзіне жетілдіруге мүмкіндік береді.

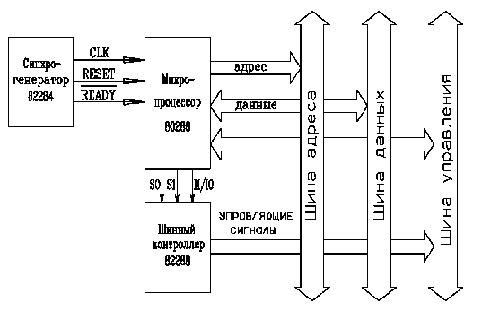

Микрокомпьютер шинасын сигналдарды ақпарттық мекн-жайлармен беру, сигналдарды басқару топ жүйелері жүзеге асырады. Оны нақты түрде үшке бөлуге болады: адрестік шина, негіздер шинасы және басқару шинасы. Осы сигналдар деңгейін әр мезетте есептеуіш жүйелердің жағдайын анықтайды. 2.1 Суретте мысалы і82284 синхрогенератор, і80286 микропроцессор, және і80287 сопроцессор, сонымен қатар і82288 шина бақылаушылар енетін гипотекалық есептеуіш жүйенің ядросы суреттелген.

2.1. Сурет Компьютер шинасы

Одан басқа үш шина көрсетілген: адрестер, негіздер және сигналдарды басқару. Синхрогенератор CLK такталық сигнал процессордың және басқа да микросхемалардың ішкі жұмыс істеуін синхронизациялау үшін әрекет етеді. RESET сигналы бас кезіндегі жағдайда процессорды лақтыуды жүзеге асырады. READY сигналы сонымен қатар синхрогенератор көмегімен қалыптасады, жай периферилік құралдардың жұмысы кезінде шиналар циклдерін жоюға арналған. 24 жолдан тұратын адрестік шинағанегіздер шинасынан процессор немесе одан берілетін і80286 микропроцессоры байт және сөз адресін шығарады. Сонымен қатар адрес шинасы негіздермен алмасу жүргізілетін периферилік порттардың адрестерін көрсету үшін микропроцессорлармен қолданылады.

Негіздер шинасы жеке байттар және сонымен қатар екі байттық сөзді беруге мүмкіндік беретін 16 жолдан тұрады, Байтты беру кезінде үлкен 8 , сонымен қатар төмен жүйе бойынша беруге болады. Негіздер шинасы екі бағытты байтты және сөздерді беру микропроцессор ретінде жүргізіледі. Басқару шинасы сигналдармен қалыптасады, біріншіден микропроцессордан тікелей түскен , екіншіден жүйелік бақылаумен құрылған, үшіншіден- микропроцессорға басқа микросхемалардан және периферилік адаптерлерден келетін сигналдардан тұарды. Микропроцессор шина бойынша қосылу тәртібін анықтайтын басқару сигналдарын қалыптастыру үшін жүйелік бақылауды қолданады. Ол шинан циклының типін, (тоқтатуды бекіту, енгізу/қортынды портын оқу, енгізу/қортынды портына жазу, зердені оқу, зердеге жазу) SO,S1,М/IO үш сигналды ұсынады. Осы сигналдардың мағынас негізінде жүйе бақылаушысы басқарушы сигналдарды, шина циклының типтерінің процесстерінің жалғасын қалыптастырады,

Шиналар жұмысының динамикасын түсіну үшін процессор оперативті зердеден сөзді оқуды қалай жүзеге асыратынын анықтайық. Бұл үш такта ішінде немесе процессордың ішкі жағдайы ішінде орындалады. (нақты айтқанда процессордың әр жағдайы синхросигналдың 2 тактасын созылады.)

^ РС/АТ компьютеріндегі L ,S, X және M шина жүйелерін ұйымдастыру

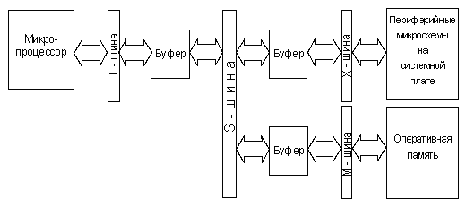

Жоғарыда айтылған жүйе үш секцияға бөлінген, шиналар бұрынғы ЭВМ ІВМ РС ХТ кластарында ғана қолданылған. «Жалпы шина» деп аталатын ол әр уақытта процессор басқа құралдар зердесімен немесе преиферилік құралдардың бақылаушыларымен қосуға мүмкіндік алып компьютерді толық қамтыған. Атап айтқанда біздің компьютерде бір емес, бірнеше шиналар бар. (2.2 суретте қарау).

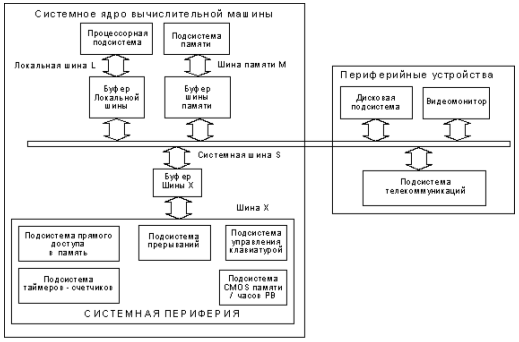

Негізгі шиналар төртеу және олар L – шина, S-шина, M-шина, X-шина болып айтылады. Біз жаңа ғана бізбен тікелей микропроцессормен байланысты адрес және негіздер жүйесі L – шина (немесе локальды шина) қарастырылды. Соншалықты шина көп буфер бөлсе, соған байланысты процессордан көп бөлінеді. Сонда L – шина процессорға жақын болып саналады.

2.2. Сурет ІВМ РС АТ шиналық ұйым

Негізгі шина компьютермен барлығын байланыстыратын S-шинасы немесе жүйелік шина болып табылады. Яғни ол 8 арнайы қосқыш слоттарға шығарылған.

L – шинасының S-шинасына ауысуы процессор сигналы аранйы трансформацияны ұстау қажет. Микропроцессор жүйесінің ең жоғарғы жүктемелі мүмкіндігі бір ТТ L шинасымен S көтерілмейді, яғни осы жүйелердің шығатын тогы 1 ма көтерілмеуі тиіс. Сондықтан L шинасымен S шинасы жүйелері арасында кем дегенде жүз рет енгізудің күштілігін арттыратын буферлі элементтер орналасуы қажет. Одан басқа микропроцессорлардың шиналары біз алдағы уақытта көретіндей ЭВМ басқа да бөліктерімен әрқашан байланыста болмауы керек. Процессордан тыс деп аталатын алмасуды орындау кезінде микропроцессор компьютердің басқа схемаларынан өшірілуі қажет.

Басу (бұл инженерлер-электронщиктер арасында таратылған термин регистрде ақпартты сақтауды білдіреді) төмендегі себептер бойынша қажет адрестердің коды. Шиналарда негіздерінде микропроцессор дан немесе одан алмасуға жататын ақпараттар пайда болғанда бұл ақпараттың көзден қосылушыға берілуге дайындығы болуы қажет. Белгілі болғандай микросхема қортындыларын жоғарғы импедандық жағдайдан жұмыс жағдайына қайта қосу, сонымен қатар ақпараттардың берілу бағыттарын қайта қосу арнайы уақытты талап етеді. Сонымен қатар уақыт осы алмасуға қатысатын элементтерді дешифирациялауға жұмсалады. Адрестік ақпарат қарастырылатын алмасудың циклінде, машиналық циклдің соңында шинаға шығарылуы тиіс және регистрде сақталуы қажет. . Сонымен қатар Жылдамдықты арттыру мүмкіндігін күшейту үшін адрестік ақпартты периферийлік микросхеманы дешифрациялауға қажет, жалпы айтқанда ортадан бастап алмасуға қатысады және бекітеді. Адрестің жүйелерде пайда болатын LA (17) - LA (23) және басқа циклдің алмасу адресіне сәйкес бұл варианты адрестің басқа жүйелерінде жүйе шинасында әлі ақпарат болғанда ғана өзгереді.

^ Шина архитектурасының эволюциясы

Қарастырылған шина архитектурасымен микропроцессор орындаған кезде мысалы, зердеден оқу командасы, локальды L шинасымен жүйелік S шинасына, ал содан кейін M шина зердесіне түседі. Осыдан кейін зердеден оқылған негіздер сол секілді жүйелік шинаға одан локальды шинаға түседі. Белгілі болғандай әр ақпаратты сол немесе басқа буферлік элемент арқылы беру анықталған кешіріктірулер жөнелтіледі. Бір кешіктіру көп болмағанымен олардың жинақталуы өте көп, сонымен қатар ол ең төменгі такталық бөлікті анықтайды.

^ 2.3.Сурет ІВМ РС АТ286 Классикалық архитектура

ІВМ РС АТ286 соңғы модельдерде жоғалтуларды жою үшін негізгі оперативті зерде негізгі жүйеге ерекшеленеді және оған қол жеткізу жүйелік шина арқылы емес, паралелльді жүйелік шинаға қол жеткізу арқылы жүзеге асырылады. Ережеге сәйкес бұл негіздер шинасының интегрирлі бақылаушылардың қолда барына сәйкес. Негіздердің берілуі мұндай жағдайда 20нс, ал такаталық жиілігі 25 Мгц дейін көтеріледі.

2.4. Сурет ІВМ РС АТ286 кеш модельдерінің архитектурасы

2.4. Сурет ІВМ РС АТ286 кеш модельдерінің архитектурасы Бұл бағытта жүйелерді алдағы уақытта жетідіру негіздер шинасынан LD локальды шинадан MD шинасының зердесіне көшу шектеуге дейін жетеді. Бұл жағдайда негіздер шинасының бақылаушысының функцияларын жай шина қалыптастырушысы орындайды. Былай қарағанда онда қажеттілік жоқ және тек LD және MD шиналарын біріктіреді.

2.5. Сурет. Жүйелік шиналар конверторымен ІВМ РС АТ286 архитектура

Процессордың өндірістілігін арттыру мүмкіндігі РС АТ архитектура аясында шешім іздеулерімен байланысты. Кэш-зердені жүргізу негізгі оперативті зердеге қол жеткізу уақыты бойынша талаптарды әлсіреуге жол берді.

Қалған архитектуралық өзгертулер 32 разрядты негіз шиналары бар процессорлардан 64 разрядты шиналары бар процессорларға нақты айтқанда Pentium, Pentium Pro, Pentium II процессорларға ауысуымен байланысты.

2.6. Сурет Кэш-зердемен ІВМ РС АТ286 архитектура

- Лекция зерде жүйесін ұйымдастыру

Тізбектілік алмасуды ұйымдастыру кезінде екі мәселе саналады:

- берушінің және қабылдаушының биттерін синхронизациялау

- беру сеансының басын фиксациялау

МПС ақпартты берудің үш тәсілі бар:

- асинхронды

- синхронды

- аралас

Асинхронды тәсіл сигналдар беталды аралық уақытымен берілетінімен сипатталады.

Синхронды тәсіл сигналдар қатаң кезеңді берілетімен сипатталады.

Аралас тәсіл байттар асинхронды , ал биттер байт ішінде синхронды берілетімен сипатталды.

^ Асинхронды тәсіл

Асинхронды тәсіл ақпаратты жеке жүйе бойынша берілуді қамтамсыз етеді. Асинхронды режимде алмасуды синхронизациялау үшін

- беруші және қабылдаушы жұмысқа бір жиелікпен беруді дайындайды

- сілтеменің басын және соңын ерекшелейтін беруші старттық және стоптық байтты қалыптастырады.

- берілу қысқа сілтемелермен, ал берілу жиелігі салыстырғанда төмен жүргізіледі.

^ Синхронды тәсіл

Синхронды тәсілде ақпаратты беру изохронды тәсілді ерекшелейді.

-ішкі

-сыртқы

Ішкі синхронизациялау

Қадір-қасиеті:

-жеткілікті екі жүйе: сигнал және жер

-жоғарғы жиелік

-байланыстың жоғарғы сенімділігі

пакеттің ұзындығы берушімен және қабылдаушының қарым-қатынасты синхронизациясынан анықталады.

Ішкі синхронизациялауды ұйымдастыру кезінде сигнал алғашында BD беру берушімен генерланады және қабылдаушыға арнайы жүйе бойынша беріледі. Ішкі синхронизация жүйелерінде BD жүйесі болмайды, ал негіздер жүйесіне 1-2 байт ұзындығымен «синхронизация символы» арнайы коды генераланады. Әр қабылдаушыға шамамен арнайы синхросимволдар анықталады, осыған байланысты бір жүйеде жұмыс жасайтын бірнеше нақты абоненттердің адресациясын жүзеге асыруға болады. Әр қабылдаушы әрқашан R хD битін қабылдайды, символдарды қалыптастырады және жеке синхросимволдармен салыстырады. Синхросимволдар сәйкес келген жағдайда келесі биттер негіздер қабылдау каналына түседі.

^ Асинхронно-синхронды тәсіл

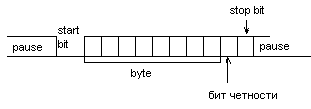

Біз әр байтты единица және нөл ағымына , яғни байланыс ортасы арқылы беріле алатын биттерді өзгерте аламыз дейік. (мысалы телефон жүйесін) . Шындығында біз төменде көретіндей әмбебап асихронды қабылдаушы осындай нақты функцияны орындайды. Жүйе күту режимінде болған кезде жүйеде бари жақсы деп демонстрациялау үшін олар арқылы единица беріліп жүйе бос екенін білдіреді. Бір жағынан жүйе логикалық нөл болған жағдайда ол интервалдардың ұстау режимінде тұруын айтады. Осыған байланысты логикалық единица жәнее нөл MARK және SPACE сәйкес қарастырылады.

Асинхронды байланыста MARK және SPACE жүйелерінің жағдайының өзгеруі символдың басталуын сипаттайды. (3.1. сурет) . Бұл старттық бит деп аталады. Старттық биттерден символ, содан кейін бақылау биті ұсынылатын биттің комбинациялануы болады. Ақырында жүйе MARKкүту жағдайына ауысады, және ағымды симводың соңын көрсетеді. Символды ұсыну үшін қолданылатын биттер саны жетіге және сегізге тең болады. Бақылау биті қателерді тексеруді орындау үшін қолданылады.

^ Сурет Ақпаратты берудің асинхронды-синхронды тәсілі

^ Сурет Ақпаратты берудің асинхронды-синхронды тәсілі

Әр биттің ұзақтығы қабылдау және беруші такталық импульс генераторларымен анықталады. Атап кететін жайт қабылдаушыда және берушіде генераторлар бір жиелікте болуы қажет., бірақ олар синхронды болуы талап етілмейді. Генраторлар жиелігін таңдау әр секундта жүйе жағдайының өзгеруіннің санын сипаттайтын бодта беру жылдамдылығына тәуелді. такталық жиелік «бодта 16 беру жылдамдығы» старттық бит үшін тану үшін жүйе тексеріледі.

Қарастырылған асинхрондық принциптерге байланысты ақпаратты беру үшін таратылған, олардың ішінде RS -232 ең танымал болып табылады.

Бұл тізбектілік байланыс принциптері БИС түрінде таратылған, олардың ішінде ең танымал : 6850, Intel 18251 ( КР 580ВВ51А) Z80- S ІО , 8250, 16450, 16550, 16550А.