Микросхемотехника

| Вид материала | Документы |

- Пояснительная записка к курсовой работе по дисциплине: «Электроника и микросхемотехника», 171.54kb.

- Электронные цепи и микросхемотехника, 24.42kb.

- Расписание Расписание, 43.04kb.

- Учебно-методический комплекс дисциплины «Микросхемотехника» Образовательной профессиональной, 266.28kb.

Федеральное агентство РФ по высшему образованию

Санкт-Петербургский государственный электротехнический университет (ЛЭТИ)

О.А. ИЗУМРУДОВ

МИКРОСХЕМОТЕХНИКА

Санкт-Петербург - 2005

ББК З 844.15я7

И 39 УДК 621.38

Изумрудов О.А. Микросхемотехника: Конспект лекций /ГЭТУ. -СПб., 1996.-56 с.

Содержит наиболее часто встречающиеся понятия и определения, используемые при изучении элементной базы, параметров и характеристик основных серий отечественных цифровых интегральных схем. Рассматриваются схемотехнические решения базовых функциональных элементов, направления развития элементной базы БИС и СБИС.

Предназначен для студентов, обучающихся в области электронной техники и микроэлектроники.

Рецензенты: кафедра конструирования и производства радиоэ- лектронной аппаратуры СЗПИ; начальник сектора канд.техн.наук А.А.Соловов (Российский институт радионавигации и времени)

Утверждено

редакционно-издательским советом университета

в качестве конспекта лекций

ISBN 5-7629-0095-9 С.-Пб. ГЭТУ, 1996

\

Введение.

Понятия и определения, приведенные ниже, соответствуют действующим в полупроводниковой электронике стандартам и отражают содержательную часть конспекта лекций по цифровой схемотехнике для студентов специальностей 200100 и 200200.

Микроэлектроника - область электроники, охватывающая проблемы исследования, конструирования, изготовления и применения электронных устройств с высокой степенью миниатюризаации.

Микросхемотехника - раздел микроэлектроники, охватывающий исследования и разработку схемотехнических решений (электрических структурных схем), используемых в интегральных микросхемах и радиоэлектронной аппаратуре на их основе.

Интегральная микросхема - микроэлектронное изделие, выполняющее определенную функцию преобразования, обработки сигнала и (или) накапливания информации и имеющее высокую плотность упаковки электрически соединенных элементов, которое с точки зрения требований к испытаниям, приемке, поставке и эксплуатации рассматривается как единое целое.

Элемент интегральной микросхемы - часть интегральной микросхемы, реализующая функцию какого-либо электрорадиоэлемента, которая выполнена нераздельно от кристалла или подложки и не может быть выделена как самостоятельное изделие с точки зрения требований к испытаниям, приемке, поставке и эксплуатации.

Компонент интегральной микросхемы - часть интегральной микросхемы, реализующая функции какого-либо электрорадиоэлемента, которая может быть выделена как самостоятельное изделие с точки зрения требований к испытаниям, приемке, поставке и эксплуатации.

Полупроводниковая интегральная микросхема – интегральная микросхема, все элементы и межэлементные соединения которой выполнены в объеме и на поверхности полупроводника.

Плёночная интегральная микросхема – интегральная микросхема, все элементы и межэлементные соединения которой выполнены в виде плёнок.

Гибридная интегральная микросхема – интегральная микросхема, содержащая, кроме элементов, компоненты и (или) кристаллы.

Аналоговая интегральная микросхема – интегральная микросхема, предназначенная для преобразования и обработки сигналов, изменяющихся по закону непрерывной функции.

Цифровая интегральная микросхема – интегральная микросхема, предназначенная для преобразования и обработки сигналов, изменяющихся по закону дискретной функции.

Степень упаковки интегральной микросхемы – отношение числа компонентов и элементов интегральной микросхемы, в том числе содержащихся в составе компонентов, к объёму интегральной микросхемы без учёта объёма выводов.

Степень интеграции интегральной микросхемы – показатель степени сложности микросхемы, характеризуемый числом содержащихся в ней элементов и компонентов.

Серия интегральных микросхем - совокупность типов интегральных микросхем, которые могут выполнять различные функции, имеют единое конструктивно-технологическое исполнение и предназначены для совместного применения.

Большая интегральная микросхема - интегральная микросхема, содержащая 500 и более элементов, изготовленных по биполярной технологии, или 1000 и более элементов, изготовленных по МДП-технологии.

Микропроцессор - программно управляемое устройство, осуществляющее процесс обработки цифровой информации и управление, им построенное на основе одной или нескольких больших интегральных микросхем.

Микроконтроллер –

Логический элемент (ЛЭ) – устройство, реализующее заданную переключательную функцию.

Потенциальные ЛЭ - ЛЭ, в которых значение двоичной переменной задается уровнем постоянного напряжения.

Положительная (прямая) логика - значению лог.I соответствует высокий уровень напряжения.

Отрицательная (инверсная) логика - значению лог.1 соответствует низкий уровень напряжения.

Включенное состояние ЛЭ - состояние, при котором на выходе ЛЭ устанавливается лог.О..

Выключенное состояние ЛЭ - состояние, при котором на выходе ЛЭ устанавливается лог.1.

Нагрузочная способность ЛЭ - характеристика, определяемая коэффициентом объединения по входу и коэффициентом разветвления по выходу.

Коэффициент объединения по входу (Коб) - число входов ИМС, по которым реализуется логическая функция.

Коэффициент разветвления по выходу (Краз) - число единичных нагрузок (ЛЭ), которое можно одновременно подключить к выходу ИМС.

Передаточная (амплитудная) характеристика ЛЭ – зависимость выходного напряжения от медленно меняющегося входного напряжения.

Примечание. Фундаментальным свойством ЛЭ является формирование логических уровней напряжений на выходе ЛЭ с таким же значением, как и на входе ЛЭ (свойство восстановления логических уровней 0 и 1).

Дизъюнктор - ЛЭ, выполняющий операцию логического сложения (ИЛИ).

Конъюнктор – ЛЭ, выполняющий операцию логического умножения (И).

Инвертор – ЛЭ, выполняющий операцию логического отрицания (НЕ).

Формы представления логической функции: словесное, табличное, алгебраическое, геометрическое (кубическое).

Таблица переключений (таблица переходов, таблица истинности) - форма представления логической функции в виде таблицы, которая содержит все возможные наборы значений логических переменных и соответствующие этим наборам значения функции.

Минтерм - конъюнкция логических переменных в наборе, которые берутся в прямом виде, если значение логической переменной в наборе равно 1, или в инверсном виде, если значение логической переменной равно 0.

Макстерм - дизъюнкция логических переменных в наборе, которые берутся в прямом виде, если значение логической переменной в наборе равно 0, или в инверсном виде, если значение логической переменной равно 1.

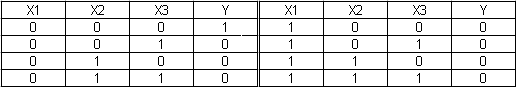

Совершенная дизъюнктивная нормальная форма (СДНФ) - дизъюнкция минтермов, соответствующих наборам входных переменных, для которых функция равна 1. Алгебраическое представление логической функции:

q-1

F = ∑ fi*mi,

i=0

где fi, mi - значение функции (0 или 1) и минтерм, соответствующий i-му набору переменных; q = 2K - число минтермов (макстермов) для функции k переменных.

Совершенная конъюнктивная нормальная форма (СКНФ) - конъюнкция макстермов, соответствующих входным наборам, для которых функция равна 0. Алгебраическое представление логической функции:

q-1

F = ∏ (fi+Mi),

i=0

где fi, Mi - значение функции и макстерм i-го набора переменных.

Карта Карно (карта минтермов) – табличная форма представления логической функции в виде набора q = 2K клеток, каждой их которых соответствует один из q минтермов.

Примечание. Если функция задается в виде СДНФ, то в клетках ооответствующих минтермов ставится 1. Остальные клетки остаются незаполненными. Таким образом, устанавливается однозначное соответствие между табличным и алгебраическим представлениями логической функции.

Полностью определённая функция – логическая функция, имеющая определённые значения 0 или 1 для всех входных наборов переменных.

Частично определённая функция – логическая функция, значения которой определены не для всех входных наборов переменных.

Рабочие наборы - входные наборы переменных, для которых логическая функция полностью определена.

Безразличные наборы - входные наборы, для которых логическая функция не определена.

Элементарная конъюнкция (дизьюнкция) - это логическая функция нескольких переменных и (или) их отрицаний, в которой символ переменной встречается один раз.

Соседние элементарные конъюнкции (дизъюнкции) - две логические функции с одинаковым числом одних и тех же переменных, отличающиеся только знаком отрицания одной переменной.

Импликанта - произведение переменных, значения которых совпадают у всех объединенных ячеек, входящих в какое-либо покрытие карты Карно.

Ранг элементарной конъюнкции (дизъюнкции) – число переменных, входящих в элементарную конъюнкцию (дизъюнкцию).

Уровни функциональной сложности ИС: 1 – компонент; 2 – функциональный элемент (ФЭ); 3 – функциональная ячейка (ФЯ); 4 – функциональный узел (ФУ); 5 – функциональный блок (ФБ); 6 – БИС.

Комбинационные цифровые устройства – устройства, логическое состояние которых зависит только от текущих значений входных переменных (логические элементы, преобразователи кодов, дешифраторы, шифраторы, компараторы, сумматоры и т.д.).

Последовательностные цифровые устройства – устройства, обладающие памятью, логическое состояние которых зависит не только от текущих значений входных переменных, но и от логического состояния цепи к моменту изменения входного набора переменных (триггеры, регистры, счётчики, ОЗУ и т.д.).

Функциональные компоненты цифровых ИС: источники тока (ИТ, транзисторные ключи (ТК), разветвители тока (РТ), объединители тока (ОТ), фиксаторы потенциала (ФП).

1. СХЕМОТЕХНИКА ЦИФРОВЫХ ИС.

Основные требования, предъявляемые к интегральным микросхемам - функциональная и техническая полнота, обеспечивающая реализацию изделий микроэлектроники при ограниченной номенклатуре ИС; единство конструктивного оформления, унификация сигналов и напряжений питания; технологичность изготовления.

В настоящее время основу цифровых ИС составляют потенциальные схемы. Они представлены в виде серий микросхем различной степени интеграции и конструктивно-технологического исполнения.

Для схемотехнической реализации ИС потенциального типа используется ряд базовых схемотехнических решений выполнения функции Шеффера и Пирса (И - НЕ, ИЛИ - НЕ), а также трехступенчатых функций И - ИЛИ - НЕ, ИЛИ - И - НЕ.

Потенциальные схемы представлены наиболее массовыми сериями ИС (133, 155, 555, 530, 564, 500, 1500, 100 и др.), выполненными по планарно-эпитаксиальной технологии в едином кристалле кремния.

Микросхемы в сериях ИС отличаются числом входов, выполняемыми логическими функциями, количеством базовых элементов, нагрузочной способностью, временем задержки, потребляемой мощностью и т.д.

К настоящему времени создано много схемотехнических вариантов цифровых потенциальных ИС, поэтому целесообразно дать анализ их структуры с общих позиций.

В цифровой ИС можно выделить части или ступени, выполняющие логические функции, а также отдельные цепи, осуществляющие связи между логическими ступенями при реализации функциональных устройств. При организации связей часто используются отдельные схемы для усиления и формирования сигналов.

Связи в схемах, а также между схемами могут быть пассивными и активными. К пассивным связям относятся:

1. Непосредственная связь (НС) - гальваническое соединение между элементами и схемами. Для быстродействующих схем длина НС оказывает влияние на их быстродействие, так как электрический сигнал проходит за 1 нс 8...10 см (свет за 1 нс проходит 30 см).

2. Резисторная связь (РС) - ограничивает ток, снижает быстродействие, но увеличивает помехоустойчивость схемы.

3. Резисторно-конденсаторная связь (РКС) - увеличивает быстродействие схемы за счет того, что параллельно, резистору включается конденсатор.

4. Диодная связь (ДС) - увеличивает пороговые напряжения и помехоустойчивость схемы путём использования нелинейной вольт-амперной характеристики диодов и одновременно обеспечивает развязку электрических цепей.

Активная связь между схемами реализуется использованием либо эмиттерных повторителей, либо парафазных усилителей на выходах. Эмиттерные повторители обеспечивают усиление сигнала по мощности и повышают быстродействие, а также позволяют объединять выходы нескольких схем, реализуя монтажные соединения ИЛИ / И. Парафазные усилительные каскады на выходах микросхем обеспечивают усиление сигналов обеих полярностей и быстрый перезаряд емкостей нагрузки. Такая выходная связь используется очень широко, так как увеличивает коэффициент разветвления по выходу, быстродействие схем и позволяет снизить требования к параметрам транзисторов.

- Базовые схемы транзисторной логики.

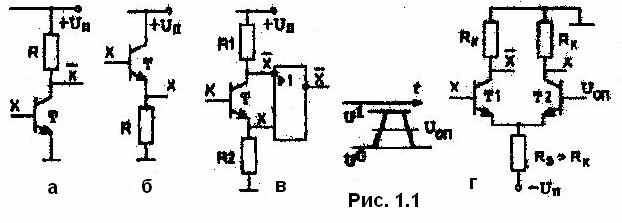

Отдельный транзистор, работающий на нагрузку в цепи коллектора, подключённую к источнику питания UП , является инвертором (рис.1.1, а). Если транзистор работает на нагрузку в

цепи эмиттера, подсоединённую к общей шине, то такая цепь повторяет входной сигнал (рис.1.1, б). При нагрузке, подсоединённой одновременно к коллектору и эмиттеру, транзистор инвертирует сигнал на коллекторе и повторяет его на эмиттере. Такое включение транзистора представляет парафазный усилитель и используется в сложных инверторах для управления выходным каскадом (рис.1.1, в). Простые или сложные инверторы составляют основу схемотехники обширного класса схем транзисторно-транзисторной логики (ТТЛ), диодно-транзисторной логики (ДТЛ), интегральной инжекционной логики ИИЛ (И2Л), логики на МОП-транзисторах и ряда других транзисторных логик.

В семействе цифровых ИС эмиттерно-связанной транзисторной логики (ЭСЛ) в качестве основы используется дифференциальный усилитель или переключатель тока (рис.1.1, г).

Отличительные особенности переключателя тока:

1) использование транзисторов в ненасыщенном режиме, обеспечивающем высокое быстродействие схемы;

2) наличие двух выходов (прямого и инверсного);

3) постоянный ток, отбираемый от источника питания независимо от режима работы схемы;

4) пониженная по сравнению с инверторами амплитуда выходных сигналов.

Сигнал на входе схемы, изменяясь относительно опорного напряжения (Uоп), открывает при значении U1 или закрывает при U0 транзистор Т1. Соответственно, благодаря эмиттерной связи закрывается или открывается транзистор Т2, т.е. в каждом из состояний схемы ток проходит или по левой, или по правой коллекторной цепи переключателя тока.

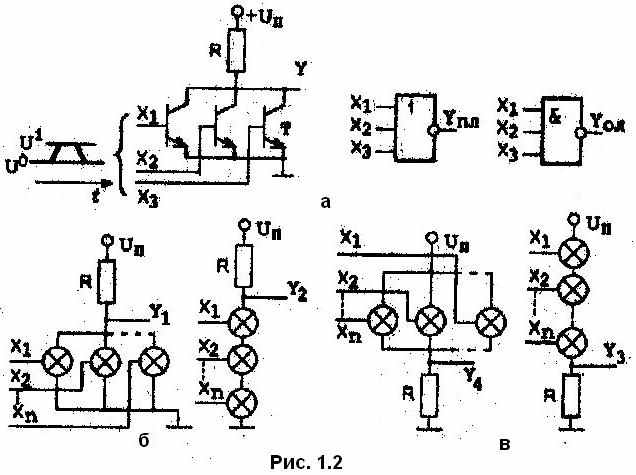

1.2. Транзисторные схемы с общей нагрузкой.

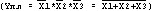

При гальваническом соединении выходов нескольких логических элементов получаемая функция называется монтажной. На рис.1.2,а показана трёхвходовая схема транзисторной логики на основе трёх инверторов, подсоединённых к общей коллекторной нагрузке. Работа схемы описывается таблицей состояний. Если закодировать верхний уровень 1, а нижний - 0 (положительная логика (ПЛ)), схема реализует функцию И для инверсных сигналов, появляющихся на коллекторах транзисторов, или функцию ИЛИ - НЕ для входных аргументов X1...Х3

.

.

П

ри обратной кодировке уровней логических переменных, когда верхний уровень кодируется 0, а нижний - 1 (отрицательная логика (ОЛ)), схема реализует функцию И - НЕ для аргументов Х1...Х3, или функцию ИЛИ для инверсных сигналов на выходах транзисторов

ри обратной кодировке уровней логических переменных, когда верхний уровень кодируется 0, а нижний - 1 (отрицательная логика (ОЛ)), схема реализует функцию И - НЕ для аргументов Х1...Х3, или функцию ИЛИ для инверсных сигналов на выходах транзисторов  . Следовательно, каждая транзисторная схема в зависимости от кодировки уровней может выполнять два набора функций. При смене типа логики в логической функции операторы И меняются на операторы ИЛИ и наоборот. Инверсии остаются без изменения. Каждая логическая схема в зависимости от принятой логики работы может иметь два условных графических обозначения (рис.1.2,а). На рис.1.2,б показаны два варианта реализации логических функций для обобщённых транзисторных схем, работающих на общую нагрузку, подсоединенную к источнику питания Uп. Тип транзистора и полярность источника питания не имеют значения.

. Следовательно, каждая транзисторная схема в зависимости от кодировки уровней может выполнять два набора функций. При смене типа логики в логической функции операторы И меняются на операторы ИЛИ и наоборот. Инверсии остаются без изменения. Каждая логическая схема в зависимости от принятой логики работы может иметь два условных графических обозначения (рис.1.2,а). На рис.1.2,б показаны два варианта реализации логических функций для обобщённых транзисторных схем, работающих на общую нагрузку, подсоединенную к источнику питания Uп. Тип транзистора и полярность источника питания не имеют значения.На рис.1.2,в показаны два варианта реализации логических функций, когда транзисторные параллельные и последовательные сборки работают на нагрузку, подсоединенную к общей точке.

Логические функции схем:

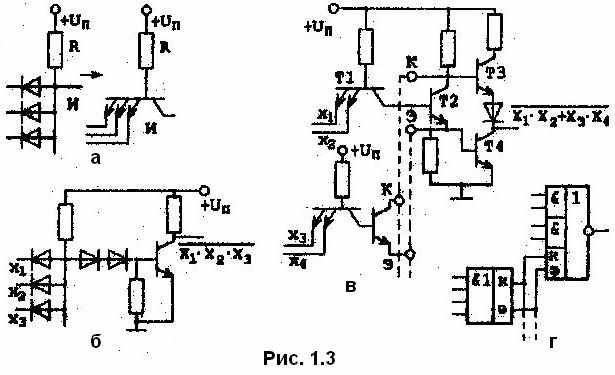

Входная логика может быть выполнена на диодных логических схемах или многоэмиттерных транзисторах (рис.1.3, а). Если построить таблицу уровней для диодной схемы, учитывая, что выходное сопротивление схемы много больше внутреннего сопротивления источников входных сигналов, то, закодировав таблицу уровней единицами и нулями, получим на выходе диодной схемы функция И/ИЛИ. Точно такие же функции в зависимости от положительной или отрицательной логики выполняются на коллекторном выходе многоэмиттерного транзистора, у которого переходы баэа - эмиттер выполняют функцию диодов.

П

рименение многоэмиттерного транзистора (МЭТ) вместо диодной оборки повышает быстродействие схемы, так как МЭТ работает при высоких уровнях на всех входах в режиме инверсного включения, а при появлении низких уровней на входах в режиме нормального включении обеспечивает быстрый перезаряд емкостей нагрузки.

рименение многоэмиттерного транзистора (МЭТ) вместо диодной оборки повышает быстродействие схемы, так как МЭТ работает при высоких уровнях на всех входах в режиме инверсного включения, а при появлении низких уровней на входах в режиме нормального включении обеспечивает быстрый перезаряд емкостей нагрузки.Использование входной логики на диодной схеме или МЭТ расширяет логические возможности транзисторной логики.

Диодная схема И/ИЛИ на входе, подсоединенная к инвертору через цепочку из двух последовательных диодов (рис.1.3, 6), обеспечивает выполнение функций И - НЕ / ИЛИ - НЕ (для положительной/отрицательной логики) при наличии одного транзистора - инвертора в схеме. Эта схема (рис.1.3, б) является базовым элементом диодно-транзисторной логики (ДТЛ), применяемой в цифровых устройствах, где требуется повышенная помехоустойчивость. Она обеспечивается диодами в цепи входной связи и за счёт выбора ВАХ диодов может быть повышена до нескольких вольт, что и сделано в серии микросхем ДТЛ для специальных применений, например для цифровой аппаратуры, обслуживающей станки с числовым программным управлением и работающей в условиях повышенных помех. Использование в качестве входной логики схемы И/ИЛИ на МЭТ, подсоединённой к сложному инвертору (рис.1.3, в), послужило началом обширного семейства схем ТТЛ.

Схемы ТТЛ удачно сочетают простоту, высокое быстродействие, экономичность с широкими логическими возможностями, которые обеспечиваются подсоединением нескольких инверторов к общей нагрузке. На рис.1.3, в показано, как подсоединением к точкам К, Э схемы 2И - НЕ дополнительной схемы 2И получается схема 2 – 2И - 2ИЛИ - НЕ (для положительной логики). У некоторых микросхем точки К, Э подсоединяются к специальным выводам корпуса, образуя микросхемы, расширяемые по ИЛИ. Так, на рис.1.3,г показано условное графическое обозначение схемы 2 - 2И - 2ИЛИ - НЕ с расширением по ИЛИ (К155ЛР1) и пример её подсоединения. К точкам К, Э может быть подсоединено до семи схем И на четыре или восемь входов.

Для расширения логических возможностей, организации схем контроля и системных магистралей, работы в схемах индикации и при сопряжении с внешними устройствами в ТТЛ используются микросхемы с открытым коллекторным выходом (например, ЛА8 – четыре схемы 2И - НЕ в корпусе, ЛА7 - две схемы 4И - НЕ с повышенной нагрузочной способностью).

На рис.1.4 показаны варианты применения схемы с открытым коллектором, которая кроме работы на общую коллекторную нагрузку для нескольких схем (реализация монтажной схемы ИЛИ/И для получения на выходе функции И-ИЛИ-НЕ/ИЛИ-И-НЕ) может работать с обмоткой специального реле либо на электрическую лампочку накаливания, либо на светодиод, либо на импульсный трансформатор.

Перечисленные выше логические схемы являются наиболее распространенными в сериях ТТЛ. Обычно они имеют коэффициент разветвления по выходу Краэ=10, коэффициент объединения по входу Коб ≤ 8. В серии для использования в выходных каскадах цифровых устройств часто включают схему И – НЕ с повышенным коэффициентом разветвления на выходе (30 и более), предназначенную для работы на низкоомную нагрузку со значительными паразитными ёмкостями.

Особенностью схем ТТЛ является работа большинства транзисторов в режиме насыщения (например, транзисторы Т2, Т4 на рис.1.3, в). Поэтому время задержки распространения при переключении схемы по выходу с нижнего уровня на верхний оказывается большим, чем при переключении с верхнего на нижний, во время переходного процесса в короткий момент времени (10 нс) оказываются открытыми оба транзистора Т3, Т4, что приводит к прохождению через схему импульсного тока.

Р