Микросхемотехника

| Вид материала | Документы |

Содержание2. Схемотехника ис на полевьк транзисторах. 3. Схемотехника ис инжекционной логики. 4. Схемотехника транзисторной логики со связанными эмиттерами. 5. Схемотехника триггерных схем. |

- Пояснительная записка к курсовой работе по дисциплине: «Электроника и микросхемотехника», 171.54kb.

- Электронные цепи и микросхемотехника, 24.42kb.

- Расписание Расписание, 43.04kb.

- Учебно-методический комплекс дисциплины «Микросхемотехника» Образовательной профессиональной, 266.28kb.

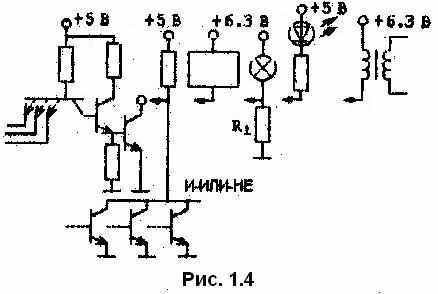

абота переключения схем ТТЛ на обычных биполярных транзисторах составляет Ап = Рпот.ср*tзд.р.ср. = 200…300 пДж; tзд.р.ср. = 15 нс, Рпот.ср = 20 мВт. За счёт прохождения импульсного тока в семах ТТл мощность рассеяния возрастает с увеличением частоты.

абота переключения схем ТТЛ на обычных биполярных транзисторах составляет Ап = Рпот.ср*tзд.р.ср. = 200…300 пДж; tзд.р.ср. = 15 нс, Рпот.ср = 20 мВт. За счёт прохождения импульсного тока в семах ТТл мощность рассеяния возрастает с увеличением частоты.Импульсы тока генерируют помехи по цепи питания, поэтому для схем ТТЛ необходимы цепи с малыми индуктивностями и развязывающие ёмкости (не менее 0,002 мкФ на одну ИС). Вблизи разъёмов печатных плат устанавливаются ёмкости не менее 0,1 мкФ на одну исходную ИС. По этой же причине в схемах ТТЛ (за исключением схем с открытым коллектором) ограничивается (до 15 нс) минимальное время фронта сигналов на входе. Если работа элементов ТТЛ не согласована по логическим функциям, то у них нельзя объединять выходы из-за возрастания выходного тока.

1.3. Быстродействующие схемы ТТЛ на транзисторах Шотки (ТТЛШ).

Д

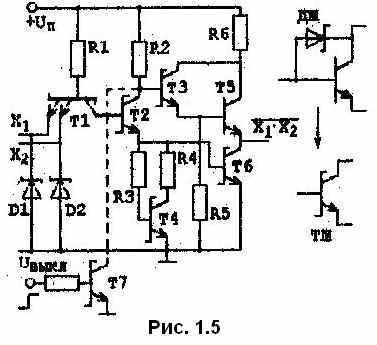

иод Шотки в интегральном исполнении представляет собой контакт металла с высокоомным полупроводником коллекторной области транзистора. Напряжение на диоде Шотки в открытом состоянии 0,4 В, поэтому его включение параллельно переходу база - коллектор исключает насыщение транзистора. В интегральном исполнении транзистор и диод составляют единую структуру, называемую транзистором Шотки (рис. 1.5). Базовый элемент 2И - НЕ на транзисторах Шотки покаэан на рис.1.5.

иод Шотки в интегральном исполнении представляет собой контакт металла с высокоомным полупроводником коллекторной области транзистора. Напряжение на диоде Шотки в открытом состоянии 0,4 В, поэтому его включение параллельно переходу база - коллектор исключает насыщение транзистора. В интегральном исполнении транзистор и диод составляют единую структуру, называемую транзистором Шотки (рис. 1.5). Базовый элемент 2И - НЕ на транзисторах Шотки покаэан на рис.1.5.Диоды Шотки используются на входах схемы для гашения колебаний и защиты от отрицательных помех на входе элемента. Такое включение диодов применяется и в схемах на обычных транзисторах.

Примечание. Наиболее распространенными сериями ТТЛШ с диодами Шотки, позволившими увеличить в несколько раз быстродействие схем или значительно снизить мощность рассеяния, являются серии 530, К531, 533, серия пониженной мощности К555, серии К1531, К1533.

1.4. Схемы с тремя состояниями.

Элементы типа ТТЛ допускают режим работы с тремя состояниями (1, 0 и выключено), когда кроме состояния с верхним или нижним уровнем на выходе в схеме возможно выключение (режим отсечки) обоих выходных транзисторов ТЗ, Т4 (см. рис.1.3, в) или транзисторов Т5, Т6 (рис. 1.5). Для этого достаточно к коллекторной нагрузке подсоединить транзистор Т7 так, как показано на рис.1.5. Положительный потенциал на его базе выключает схему позволяя использовать ее для построения системных шин, объединяющих выходы ряда устройств. В каждый момент времени на шину идут сигналы с одного из устройств, остальные устройства в это время выключены.

Микромощные серии ТТЛШ нашли применение в ряде отечественных микропроцессорных БИС, например сериях К589, КР1802, КМ1804 и др.

2. СХЕМОТЕХНИКА ИС НА ПОЛЕВЬК ТРАНЗИСТОРАХ.

Наряду с рассмотренными схемами на биполярных транзисторах в микроэлектронике активно используются схемы на полевых (униполярных, с одним типом носителей заряда) транзисторах. В настоящее время полевые транзисторы являются лучшими активными элементами для БИС.

МДП-транзисторам присущи следующие достоинства:

1) высокое входное сопротивление (до 1014 Ом);

2) малые размеры и высокая технологичность (площадь МДП-транзистора, как правило, меньше площади биполярного транзистора, при изготовлении МДП-транзистора требуется меньше технологических операций);

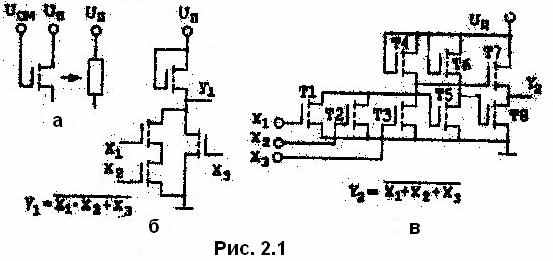

3) МДП-транзисторы возможно использовать в качестве нагрузки, что обеспечивает высокую однородность ИС (рис.2.1, а);

4) высокая помехоустойчивость (2...6 В по сравнению с 0,6 В для биполярных транзисторов);

5) малая мощность рассеяния в статике, особенно при использовании в схеме транзисторов с взаимно дополнительным типом проводимости;

6) один источник питания, обеспечивающий простоту схем;

7) способность пропускать ток в обоих направлениях;

8) устойчивость к нейтронной составляющей радиационного воздействия.

Недостатком МДП-транзисторов является их относительно невысокое быстродействие и малая крутизна, что снижает нагрузочную способность элементов по току и ухудшает показатёль, определяемый отношением скорости переключения к мощности рассеяния.

Наибольшее распространение получили полевые транзисторы со структурой металл - оксид - полупроводник. Поскольку оксид играет роль диэлектрика, их также называют МДП - транзисторами. Наиболее часто используются транзисторы с индуцированным каналом. Отличительная особенность МДП-транзисторов – возможность использования их в качестве резисторов нагрузки, когда транзистор открывается напряжением смещения на затворе. Это обусловлено линейной зависимостью тока стока от напряжения на стоке при определённых напряжениях на затворе. Включение МДП-транзистора для использования в режиме резистора показано на рис.2.1, б, где изображена логическая схема, из анализа работы которой очевидно, что последовательное соединение МДП-транзисторов образует конъюнктор.

Л

огика работы этой схемы не зависит от типа МДП-транзисторов (от этого будет зависеть только полярность питания и сигналов в схеме), поэтому на схеме тип транзистора не указывается. Высокая однородность логических схем, содержащих одни МДП-транзисторы, особенно удобна для построения БИС.

огика работы этой схемы не зависит от типа МДП-транзисторов (от этого будет зависеть только полярность питания и сигналов в схеме), поэтому на схеме тип транзистора не указывается. Высокая однородность логических схем, содержащих одни МДП-транзисторы, особенно удобна для построения БИС.2.1. Схемотехника ИС на МДП-транзисторах с одним типом проводимости.

Наибольшее распространение получили схемы на МДП-транзисторах со связанными истоками. На рис.2.1,в показана схема ИЛИ – НЕ (И - НЕ). Транзисторы Т1 – Т3 являются инверторами входных сигналов X1 – Х3, их стоки объединены и подсоединены к транзистору Т4, выполняющему роль нагрузки (полная аналогия со схемой, изображённой на рис.1.2, а). Выходной сигнал с транзистора Т4 поступает непосредственно на транзистор Т7, а также предварительно инвертируется на транзисторе Т5 и с его нагрузки, выполненной на транзисторе Т6, поступает на выходной транзистор Т8. Таким образом, транзисторы Т5 – Т8 представляют собой выходной парафазный усилитель, не выполняющий логических преобразований и необходимый только для увеличения коэффициента разветвления элемента во выходу и быстрого перезаряда емкостей в цепи нагрузки.

Технологичность и невысокая стоимость схем на МДП-транзисторах делают их особенно перспективными в случае изготовления устройств в виде БИС.

Схемы на транзисторах р-типа очень дёшевы и более технологичны, чем схемы на транзисторах n-типа, но уступают последним по быстродействию в 8...10 раз.

Схемы на МДП-транзисторах n-типа по быстродействии не уступают ТТЛ-схемам: они обеспечивают меньшую мощность рассеяния и более высокую плотность размещения компонентов, чем схемы ТТЛ. Использование метода ионной имплантации и применение в цепях нагрузок транзисторов с обедняемыми каналами, а не обогащаемыми, позволило снизить напряжение питания до 5 В, что обеспечило совместимость этих схем по электрическим уровням с микросхемами ТТЛ.

Примечание. Отечественные серии микропроцессоров К1801, КР1810, К580, К581 используют схемотехнику и технологию n-МДП.

2.2. Схемотехника ИС на комплементарных МДП-транзисторах(КМДП).

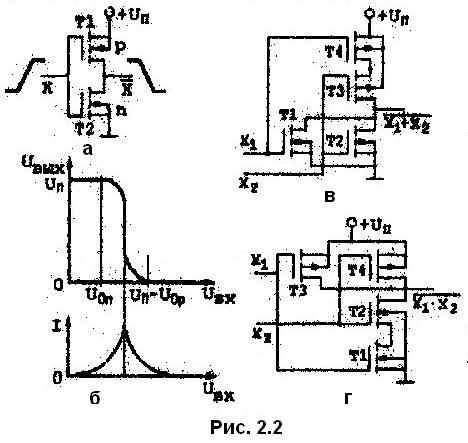

Использование взаимодополняюцих (комплементарных) КМДП - транзисторов в схемотехнике ИС открывает новые возможности улучшения их параметров. Если объединить затворы и стоки двух транзисторов n- и р-типа, как показано на рис.2.2, а, то получится инверторный каскад, который в статическом состоянии не рассеивает мощность. Это объясняется тем, что постоянный ток через него проходить не может (исключение составляют токи утечки через закрытый транзистор). Действительно, при любом значении логического уровня потенциала на входе схемы один из транзисторов последовательной цепи остается закрытым.

Динамическая мощность рассеяния этих схем на порядок ниже схем на транзисторах с одним типом проводимости, и определяется током, проходящим через схему во время её переключения (рис.2.2, б). Она зависит от емкостной нагрузки Сн, частоты работы схемы f и напряжения питания Uп:

Рдин = Uп2*Сн*f

С

войства КМДП-схем становятся понятны при анализе передаточной характеристики инвертора (рис.2.2, б):

войства КМДП-схем становятся понятны при анализе передаточной характеристики инвертора (рис.2.2, б):1. Логические уровни у схемы равны соответственно: нижний - нулю, верхний - Uп. Полезный сигнал на выходе равен напряжению питания. (Никакая другая схемотехника не обеспечивает этих возможностей).

8. Помехозащищённость по 0 (для положительной логики) определяется напряжением отпирания Uпор нижнего транзистора, помехоустойчивость по 1 определяется напряжением отпирания Uпор верхнего транзистора.

3. Работоспособность, схемы не зависит от напряжения питания, начиная со значений Uп ≥ Uоn + Uор, т. е. схема может работать при весьма больших разбросах по питанию, если начальный его уровень выбран с соответствующим запасом.

Базовым принципом схемотехники логических элементов на КМДП-транзисторах является организация схем, обеспечивающая отсутствие постоянного тока через схему при любой комбинации входных сигналов. Это достигается последовательным включением дополняющих транзисторов так, как показано на рис.2.2, в, г. Из рисунка видно, что переход от схемы ИЛИ – НЕ к схеме И – НЕ может быть произведён как сменой логики, так и соответствующей коммутацией каскадов. Любая n-входовая схема схема И – НЕ/ИЛИ – НЕ требует 2n-транзисторов.

Типовая задержка в современных КМДП-схемах tзд.р.ср составляет 50 нс. Мощность рассеяния пропорциональна частоте работы и увеличивается в среднем на 1 мВт при возрастании частоты на 1 МГц. Уменьшение мощности рассеяния в динамическом режиме достигается снижением ёмкости нагрузки.

Минимальное напряжение питания схемы на КМДП-транзисторах определяется пороговым напряжением p-канального транзистора, которое обычно превышает пороговое напряжение n-канального транзистора.

Недостаток КМДП ИС связан с относительной сложностью технологии их изготовления и с меньшей степенью интеграции, чем у схем на однотипных МДП-транзисторах.

Из отечественных серий КМДП ИС наиболее развиты серии К561, К564, КР1561, 1564. Микросхемы указанных серий сохраняют работоспособность при напряжениях питания от 3 до 15 В. На основе схемотехники КМДП изготавливается несколько семейств микропроцессоров, например К587, К588 и др.

3. СХЕМОТЕХНИКА ИС ИНЖЕКЦИОННОЙ ЛОГИКИ.

Схемы интегральной инжекционной логики (ИИЛ), или И2Л – схемы являются развитием схем с непосредственными связями.

Отличительной особенностью И2Л–схем является отсутствие токозадающих резисторов в цепях управления транзисторами.

Работоспособность такой схемы зависит от выбора нагрузки, задающей ток в базовой цепи выходного транзистора.

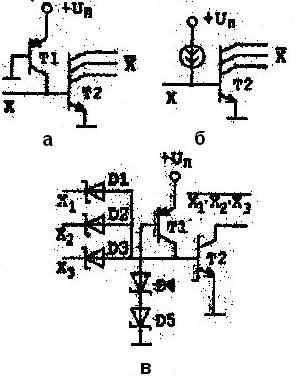

Основу схемотехники И2Л составляет инвертор (рисунок а), работающий в насыщенном режиме и выполненный на многоколлекторном транзисторе (МКТ) Т2, обеспечивающем развязку выходов для исключения их взаимного влияния. Нагрузка для предыдущего каскада, принадлежащая к его базовой цепи, выполнена на p-n-p – транзисторе Т1, который играет тока (рисунок, б) и обеспечивает питание базовой цепи Т2. По этой причине схемы И2Л называют ещё схемами с инжекционным питанием.

С

хема базового элемента И2Л очень технологична и занимает минимальную площадь на кристалле. Область n принадлежит как базе p-n-p-транзистора, так и эмиттеру ключевого транзистора-инвертора (его база p является коллектором инжектора).

хема базового элемента И2Л очень технологична и занимает минимальную площадь на кристалле. Область n принадлежит как базе p-n-p-транзистора, так и эмиттеру ключевого транзистора-инвертора (его база p является коллектором инжектора).Напряжение питания И2Л-схем составляет 1,5 В, амплитуда логического сигнала 0,7 В. Благодаря низким значениям рабочих токов, не превышающих нескольких десятков микроампер, достигается уменьшение степени насыщения ключевого транзистора и обеспечивается высокое быстродействие схемы.

Мощность рассеяния схемы может быть снижена до 20 мкВт. При задержке инвертора tзд.р = 50 нс это обеспечивает И2Л-схеме работу переключения Ап = 0,02*50 = 1 пДж (в 100 раз меньше, чем у ТТЛ-схем). Плотность элементов на кристалле И2Л-схем в 50 раз выше, чем в ТТЛ-схемах. Все это делает схемотехнику И2Л весьма перспективной для БИС.

При использовании диодов Шотки в качестве диодной логики и развязки цепей на входе, а транзисторов Шотки - в качестве инверторов (рисунок, в) показатели И2Л-схем могут превзойти комплексные показатели любых схем на основе кремния. Так, теоретический предел И2Л-схем по добротности равен 0,001 пДж. Однако по быстродействию эти схемы уступают ТТЛШ- и ЭСЛ-схемам. И2Л-схемы весьма перспективны для построения СБИС.

Примечание. Схемотехника И2Л не используется для производства серии ИС, так как она более эффективна в ИС высоких степеней интеграции. Отечественные семейства микропроцессоров К583, К584 и др. выполнены на базе схемотехники И2Л.

4. СХЕМОТЕХНИКА ТРАНЗИСТОРНОЙ ЛОГИКИ СО СВЯЗАННЫМИ ЭМИТТЕРАМИ.

Серии цифровых интегральных схем эмиттерно-связанной транзисторной логики (ЭСТЛ, или просто ЭСЛ) представляют в настоящее время самые быстродействующие серии схем потенциального типа на кремниевых биполярных транзисторах.

ИС ЭСЛ составляют серьёзную конкуренцию семейству ТТЛ-схем из-за ряда положительных качеств, обеспечивающих их оптимальное применение в цифровой аппаратуре широкого класса.

Достоинства ЭСЛ-схем обусловлены их схемотехникой, которая использует в качестве основного элемента транзисторной логики дифференциальный усилитель (переключатель тока) с транзисторами, работающими в ненасыщенном режиме (см. рис.1.1, г).

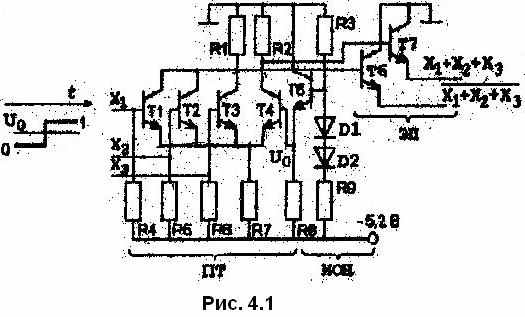

Базовый логический элемент ИЛИ – НЕ, ИЛИ (для положительной логики) наиболее распространённых отечественных серий ЭСЛ-схем 100, К500, 700, К1500 показан на рис.4.1. В нём можно выделить следующие цепи: переключатель тока Пт, встроенный источник опорного напряжения ИОН и выходные усилители мощности в виде эмиттерных повторителей ЭП.

Переключатель тока ПТ предназначен для выполнения логических функций и образует первую логическую ступень с прямыми и инверсными выходами. Источник опорного напряжения ИОН содержит температурно-компенсированный делитель (R3, D1, D2, R9) и эмиттерный повторитель (T5, R8) и задаёт уровень напряжения, равный среднему напряжению между уровнями 0 и 1 на входе схемы.

Эмиттерные повторители ЭП (Т6, Т7) предназначены для усиления сигнала по мощности, работы на согласованные линии связи, смещения выходных сигналов по напряжению с целью обеспечения совместной работы с другими аналогичными элементами.

К

роме того, ЭП является второй ступенью логики, так как позволяют реализовывать монтажные функции ИЛИ, получаемые путём объединения нескольких элементов и подсоединением их к общей нагрузке.

роме того, ЭП является второй ступенью логики, так как позволяют реализовывать монтажные функции ИЛИ, получаемые путём объединения нескольких элементов и подсоединением их к общей нагрузке.Расширение логических возможностей ЭСЛ-схем производится объединением выходов нескольких ПТ на одном коллекторном резисторе с образованием монтажной функции И.

Другим эффективным приёмом расширения логических возможностями ЭСЛ является использование двух- и трёхуровневых ПТ, когда в качестве эмиттерного тока ПТ верхнего уровня служит коллекторный ток ПТ нижнего уровня переключения. Оба переключателя тока (верхний и нижний) управляются различными логическими сигналами (рис.4.2), т.е. в одноступенчатой схеме ток может разветвляться в две цепи, в двухступенчатой схеме он может коммутироваться на втором уровне в четыре цепи, в трёхступенчатой схеме на последнем уровне коммутация тока возможна в восемь цепей.

Таким образом, использование дифференциального усилителя в качестве основы схемотехники семейства ЭСЛ-схем и эмиттерных повторителей обеспечивает:

1) самое высокое быстродействие среди полупроводниковых схем на основе кремния;

2) расширенные логические возможности, обусловленные наличием двух выходов с прямым и инверсным значениями функции, возможностями монтажных функций и многоуровневых схем;

3) постоянство тока потребления от источников основного питания и отсутствие бросков тока при переключении схемы;

4) большую нагрузочную способность и способность схем работать на низкоомные согласованные линии связи и нагрузку;

5) высокую стабильность динамических параметров в диапазоне рабочих температур и при изменении питающих напряжений;

6) постоянную мощность потребления при повышении частоты переключения.

К недостаткам схем ЭСЛ-схем определяются спецификой их схемотехники.

Схем ЭСЛ подключается к источнику питания - 5,2 В, коллекторные цепи заземляются. Такое включение обеспечивает меньшую зависимость выходного напряжения от наводок по цепи питания, лучшую помехоустойчивость и сохранность схем при случайном соединении выходов с общей точкой.

Особенностью большинства ЭСЛ-схем различных серий является подключение всех видов к шине питания через высокоомные резисторы, что исключает необходимость ориентации неиспользованных входов на специальный потенциал. У выходных эмиттерных повторителей отсутствуют нагрузочные резисторы. Они присоединяются к выходам ЭСЛ-схем и к специальной отдельной шине питания – 2 В. Номинал резисторов определяется параметрами используемых линий связи. Верхний уровень сигналов ЭСЛ-схем указанных серий -0,9 В, нижний – 1,65 В, т.е. логический перепад (составляет 0,75 В, а значит, для сопряжения уровней ЭСЛ-схем и ТТЛ-схем требуются специальные схемы трансляторов уровней (они есть в номенклатуре ИС ЭСЛ).

Каждая ЭСЛ-схема (рис.4.1) имеет два вывода для подсоединения к общей точке (выводы питания, подсоединяемые к положительному полюсу источника). Это необходимо, чтобы отделить цепь питания выходных транзисторов, где возможны помехи из-за больших токов нагрузки, от цепи питания логической схемы. Раздельные цепи питания гарантируют минимальную связь между различными схемами внутри корпуса при максимальной нагрузке на выходе схем.

Большим преимуществом ЭСЛ-схем перед ТТЛ-схемами является возможность работы на длинные (до 15 м) линии в виде кабеля. Волновое сопротивление при этом подключается к источнику - 2 В, что позволяет снизить токи нагрузки.

Нагрузочная способность ЭСЛ-схем высока (Краз > 15). Запас помехоустойчивости составляет -0,125 В, Средняя задержка 2 нс при мощности рассеяния 25 мВт обеспечивает показатель Ап=50 пДж.

Связь между ЭСЛ-схемами осуществляется только согласованными линиями (полосковые линии на печатных платах или коаксиальный кабель, например с волновым сопротивлением 50 Ом).

В БИС наряду с рассмотренными ЭСЛ используются также малосигнальные ЭСЛ (МЭСЛ), питаемые от источника 3 В, с уменьшенным логическим перепадом 0,3 В. Их особенностью является работа в схемах внутренней логики без эмиттерных повторителей.

На ЭСЛ-схемах выпускается самая быстродействующая серия микропроцессорных БИС К1800 с тактовой частотой до 36 МГц и матричные БИС.

5. СХЕМОТЕХНИКА ТРИГГЕРНЫХ СХЕМ.

В процессе обработки информации возникает необходимость в ее промежуточном хранении. Для этих целей используются триггеры - элементы с двумя устойчивыми состояниями, имеющие соответствующие входы для сигналов управления.

О

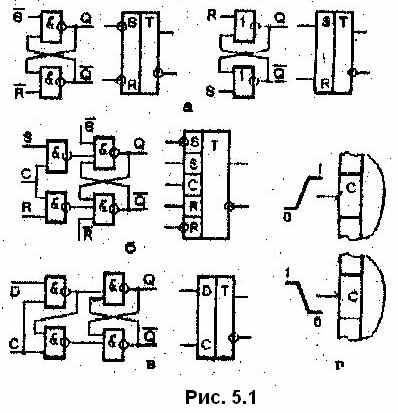

снову триггеров составляют простейшие запоминающие ячейки, получаемые соединением двух потенциальных элементов И – НЕ (ИЛИ - НЕ) так, как показано на рис. 5.1, а. Триггер может находиться в двух устойчивых состояниях: 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 – аналогичный сигнал на выходе

снову триггеров составляют простейшие запоминающие ячейки, получаемые соединением двух потенциальных элементов И – НЕ (ИЛИ - НЕ) так, как показано на рис. 5.1, а. Триггер может находиться в двух устойчивых состояниях: 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 – аналогичный сигнал на выходе  .

.Информация может сниматься с запоминающей ячейки (триггера) одновременно в прямом и инверсном видах.

Появление нулевых сигналов на обоих входах триггера, выполненного в базисе И - НЕ, или единичных сигналов на входах схемы в базисе ИЛИ - НЕ является запрещённой комбинацией, так как состояние триггера при этом оказывается неопределённым.

Нетрудно проследить, что состояние триггеров сохраняется неизменным только при наличии единичных уровней на своих входах схемы, выполненной в базисе И - НЕ, и нулевых уровней для схемы, реализованной в базисе ИЛИ - НЕ.

Для установки триггеров в заданное состояние используются соответственно нулевые уровни на одном из входов для базиса И - НЕ и единичные уровни для базиса ИЛИ - НЕ. Вход, по которому триггер устанавливается в состояние 1, обозначается буквой S, а в состояние О - буквой R. Анализ работы триггеров (рис. 6.1, а) показывает, что если ячейка из элементов, выполняющих функцию ИЛИ-НЕ, управляется сигналами R, S, то ячейка из элементов И-НЕ управляется инверсными сигналами

. В таком простейшем виде запоминающие ячейки входят в состав более сложных схем.

. В таком простейшем виде запоминающие ячейки входят в состав более сложных схем.В общем случае триггер имеет несколько входов, на которые могут поступать и подвергаться логическому преобразованию управляющие сигналы с различных схем, а также сигналы с собственных выходов триггера. Поэтому в потенциальной системе, которая не содержит каких-либо элементов временной задержки, особое, внимание уделяется согласованию работы логических схем и триггеров во времени. В связи с этим в потенциальной системе, как правило, на входах запоминающих ячеек используются специальные логические схемы, управляемые синхронизирующими сигналами, определяющими момент приема триггером входной информации. В таком триггере могут быть входы, зависимые от сигнала С, и установочные входы, не зависимые от сигнала С (рис, 5.1, б). Такое построение входных цепей триггера и соответственно сам триггер называется синхронным триггером (триггер, тактируемый импульсом).

Триггер с одним логическим входом для записи информации обычно обозначается буквой D. Такие триггеры, получившие название D-триггеры или триггеры - защёлки, используются только в синхронном варианте (рис. 5.1, в).

Наряду с триггерами, тактируемыми импульсом (рис. 5.1, б, в), применяются триггеры, тактируемые фронтом (триггеры с динамическим управлением). В синхронных триггерах информация принимается все время, пока значение синхронизирующего импульса равно 1 (0, если вход С - инверсный). В триггерах с динамическим управлением прием информации происходит в момент смены уровней сигнала на синхронизирующем входе. Следовательно, возможен случай прямого управления, когда происходит смена уровней с 0 на 1, или инверсного управления при смене с 1 на О.

Примечание. Для синхронизирующих входов (либо логических входов) с динамическим управлением используется специальное изображение, показывающее смену уровней управляющих сигналов, при которой происходит изменение состояния триггера (рис.5.1, г).

Синхронизирующие входы с динамическим управлением часто используются в ИС высоких степеней интеграции.

Т