Микросхемотехника

| Вид материала | Документы |

Содержание9. Общие принципы проектирования ис. 10. Особенности развития интегральных схем высоких степеней интеграции. 4. Схемотехника транзисторной логики со связанными |

- Пояснительная записка к курсовой работе по дисциплине: «Электроника и микросхемотехника», 171.54kb.

- Электронные цепи и микросхемотехника, 24.42kb.

- Расписание Расписание, 43.04kb.

- Учебно-методический комплекс дисциплины «Микросхемотехника» Образовательной профессиональной, 266.28kb.

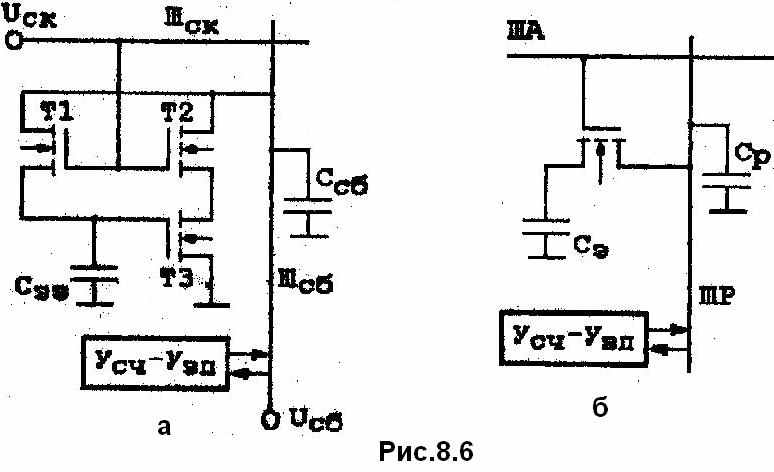

ля снижения мощности потребления запоминающим элементом в режимах считывания регенерации производится перезапись инверсной информации, т.е. если считывается 1, то в такте перезаписи (регенерации) производится запись 0, и наоборот. В этом случае положительный заряд с ёмкости Сзэ стекает в Шсб через открытый транзистор Т1, поскольку эта шина имеет нулевой потенциал. Если же ёмкость Сзэ была разряжена (при этом Т3 закрыт), то её заряд до положительного потенциала Uсб происходит через открытый транзистор Т1. До полного заряда ёмкости Сзэ последовательная цепь транзисторов Т2, Т3 находится в непроводящем состоянии, что существенно снижает нагрузку формирователя записи.

ля снижения мощности потребления запоминающим элементом в режимах считывания регенерации производится перезапись инверсной информации, т.е. если считывается 1, то в такте перезаписи (регенерации) производится запись 0, и наоборот. В этом случае положительный заряд с ёмкости Сзэ стекает в Шсб через открытый транзистор Т1, поскольку эта шина имеет нулевой потенциал. Если же ёмкость Сзэ была разряжена (при этом Т3 закрыт), то её заряд до положительного потенциала Uсб происходит через открытый транзистор Т1. До полного заряда ёмкости Сзэ последовательная цепь транзисторов Т2, Т3 находится в непроводящем состоянии, что существенно снижает нагрузку формирователя записи.Следует отметить, что подобная организация работы ЗЭ приводит к необходимости после каждого обращения в режимах считывания и регенерации, которые сопровождаются перезаписью, производить инвертирование информации.

Чтобы учесть текущее состояние ячейки, осуществляется контроль чётности инверсий, выполняемый с помощью дополнительной аппаратуры, включающей дополнительный столбец ЗЭ, столбцовый усилитель с двумя логическими схемами <исключающее ИЛИ>, одна из которых относится к цепям ввода, а другая – вывода информации.

В режиме считывания на шине строки Шск устанавливается потенциал около 4 В из-за того, что транзистор Т1 имеет отношение ширины канала к длине в несколько раз меньшее, чем транзистор Т2 (Т2 находится в проводящем состоянии, а Т1 – в состоянии, близком к закрытому). Таким образом, будут ли каскадно включенные транзисторы Т2, ТЗ находиться в проводящем состоянии или нет, зависит от того, заряжена ли ёмкость Сзэ положительным потенциалом (что соответствует записи 1) или же она разряжена до потенциала, близкого к 0 В. В случае, когда ёмкость Сзэ заряжена положительным потенциалом, транзисторы Т2, ТЗ находятся в проводящем состоянии, и ёмкость столбца Ссб будет быстро разряжаться до уровня меньшего, чем уровень срабатывания усилителя считывания. Если же в ячейке был записан О (ёмкость Сзэ разряжена), то потенциал шины столбца Шсб лишь незначительно снизится, не достигнув, однако, уровня срабатывания усилителя считывания.

Из сказанного следует, что срабатывание усилителя считывания, подключенного к шине столбца, будет происходить только в случае, если информационная ёмкость была заряжена, т.е. была записана 1. Существенное упрощение ЗЭ динамического типа достигается в схеме однотранзисторной ячейки хранения. Схема ЗЭ этого типа в настоящее время нашла наиболее широкое применение при проектировании полупроводниковых микросхем памяти, так как они имеют наибольшую информационную ёмкость, достигающую нескольких мегабит.

Схема однотранзисторного ЗЭ представлена на рис. 8.6, б. Как видно из рисунка, управление процессами записи и считывания осуществляется с помощью двух шин: адресной шины ША И разрядной шины ШР, к которой подключены усилитель считывания Усч и усилитель записи Узп.

Запись информации производится при одновременном подключении напряжений к адресной и разрядной шинам. Напряжение на ША открывает транзистор, и конденсатор Сэ либо заряжается, если на ШР высокое напряжение (код 1), либо разряжается, если на ШР напряжение низкого уровня (код 0).

При считывании напряжение подается только на ША. При этом напряжение на конденсаторе Сэ передаётся на Усч. С учётом собственной ёмкости разрядной шины Ср напряжение на входе Усч при считывании кода 1 определяется выражением Uсч=Uсэ*Сэ/(Ср+Сэ). В современных ЗЭ Сэ = 0,05 пФ, Ср = 0,5 пФ, U1сэ = 2...5 В.

8.2. Схемотехника запоминающих элементов ПЗУ.

Основным признаком классификации ПЗУ является характер программирования, которое может быть однократным (МПЗУ, ППЗУ) или допускать возможность перезаписи информации (РПЗУ).

При однократном программировании используются элементы с односторонней проводимостью, обеспечивающие электрическую развязку ША и ШР (диоды, транзисторы). В ЗУ, допускающих перезапись информации, применяются элементы, обладающие способностью к длительному хранению электрического заряда, который поддерживает включенное (проводящее) состояние коммутирующего элемента. Классификация ПЗУ по типу ЗЭ, виду элемента программирования, способу стирания и др. д

ана в таблице.

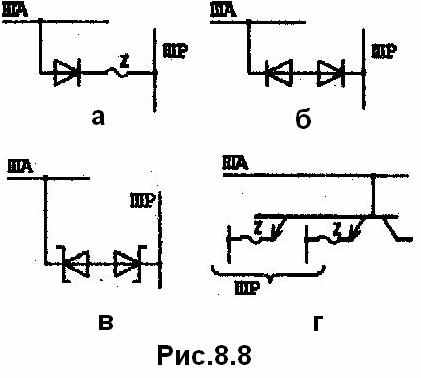

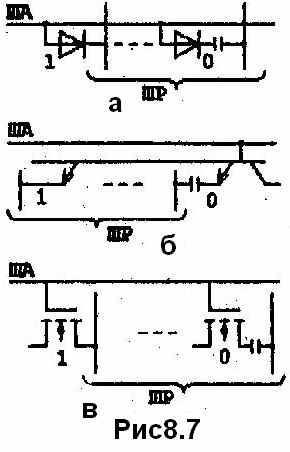

ана в таблице.В МПЗУ запоминающие элементы располагаются в узлах матрицы, образованной адресными (словарными) и разрядными шинами. Коду 1 соответствует соединение ЗЭ, коду 0 - отсутствие соединения (рис.8.7, а-в).

В ППЗУ запоминающие ячейки образованы диодами или многоэмиттерными транзисторами (рис.8.8), и программирование осуществляется пережиганием плавких перемычек Z (рис.8.8, а, г) либо электрическим пробоем р-n-перехода или барьера Шотки (рис.8.8,б,в). Перемычки формируются в технологическом процессе изготовления ИС на основе тонких плёнок нихрома или поликремния. При пропускании через них тока 50...100 мА они необратимо разрушаются. После программирования ППЗУ подвергаются электротермотренировке для исключения потенциально ненадежных ПЗУ.

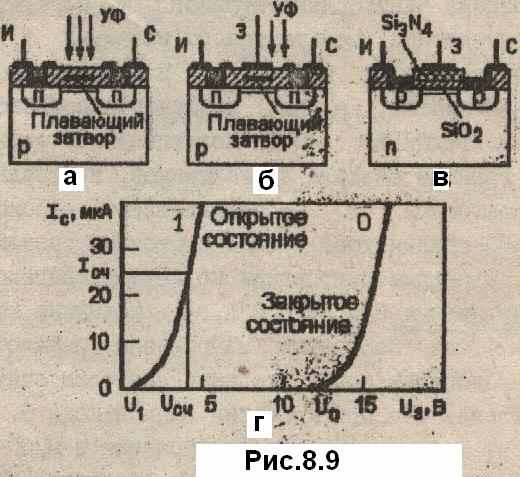

В ЗЭ перепрограммируемых ПЗУ используется зависимость порогового напряжения МДП-транзистора от вводимого в подзатворный диэлектрик электрического заряда. Этот заряд может сохраняться в ЗЭ на протяжении нескольких лет независимо от напряжения питания. Перезапись информации происходит после стирания накопленного заряда, которое производится ультрафиолетовым (УФ) излучением или электрическим полем.

С

труктура МДП-транзистора с УФ-стиранием информации (рис.8.9, а) содержит плавающий затвор, размещённый в толще диоксида кремния на расстоянии 0,1 мкм от поверхности полупроводника. В режиме записи между стоком и подложкой прикладывается высокое обратное напряжение, при котором происходит лавинный пробой перехода сток-подложка. Дырки, возникающие в поле перехода, достигают затвора и накапливаются на нём. Положительный заряд дырок вызывает образование n-канала и переход транзистора в открытое состояние (код 1). Для стирания записанной информации структура облучается УФ-лучами через прозрачную кварцевую крышку корпуса БИС. При этом в оксиде образуются электронно-дырочные пары. Электроны, двигаясь в поле затвора, нейтрализуют положительный заряд на затворе, и транзистор переходит в закрытое состояние (код 0).

труктура МДП-транзистора с УФ-стиранием информации (рис.8.9, а) содержит плавающий затвор, размещённый в толще диоксида кремния на расстоянии 0,1 мкм от поверхности полупроводника. В режиме записи между стоком и подложкой прикладывается высокое обратное напряжение, при котором происходит лавинный пробой перехода сток-подложка. Дырки, возникающие в поле перехода, достигают затвора и накапливаются на нём. Положительный заряд дырок вызывает образование n-канала и переход транзистора в открытое состояние (код 1). Для стирания записанной информации структура облучается УФ-лучами через прозрачную кварцевую крышку корпуса БИС. При этом в оксиде образуются электронно-дырочные пары. Электроны, двигаясь в поле затвора, нейтрализуют положительный заряд на затворе, и транзистор переходит в закрытое состояние (код 0).Считывание хранимой информации сводится к определению проводимости транзистора. Записанная информация во время считывания сохраняется.

При использовании МДП-транзистора с дополнительным затвором (рис.8.9, б) заряд на плавающем затворе образуется в результате инжекции «горячих» электронов из околостоковой области под действием положительного напряжения на управляющем затворе.

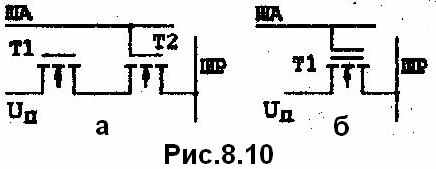

Если на стоке низкое напряжение (0 В), то ЗЭ программируется, если высокое (15 В) – не программируется. В запрограммированном состоянии пороговое напряжение транзистора по управляющему затвору возрастает (рис.8.9, г). Считывание производится при подаче на управляющий затвор считывающего напряжения Uсч. Стирание осуществляется путём облучения кристалла УФ излучением. Включение МДП-транзисторов с накоплением заряда в ячейки матриц ЗУ показано на рис.8.10, а, б. Транзистор с одним плавающим затвором Т1 подключается к координатным шинам с помощью дополнительного ключевого транзистора Т2 (рис.8.10, а).

Е

ще одним элементом памяти РПЗУ является МНОП-транзистор (металл- нитрид- оксид- полупроводник) с р-каналом (рис.8.9, в). Затвор транзистора отделен от подложки слоями диоксида кремния (2...4 нм) и нитрида кремния (80...100 нм). Пороговое напряжение транзистора в исходном состоянии высокое - 10...15 В.

ще одним элементом памяти РПЗУ является МНОП-транзистор (металл- нитрид- оксид- полупроводник) с р-каналом (рис.8.9, в). Затвор транзистора отделен от подложки слоями диоксида кремния (2...4 нм) и нитрида кремния (80...100 нм). Пороговое напряжение транзистора в исходном состоянии высокое - 10...15 В.В режиме записи на затвор транзистора подается импульс напряжения положительной полярности. Электроны из подложки туннелируют через тонкий слой оксида и накапливаются на границе раздела двух диэлектриков. В результате пороговое напряжение транзистора уменьшается до значений 1...2 В (рис.8.9, г), что соответствует записи 1. В режиме стирания эатвор транзистора заземляется, а на подложку подается импульс напряжения амплитудой 30...40 В. Положительные заряды из подложки поступают к границе раздела диэлектриков, нейтрализуют отрицательный заряд электронов и восстанавливают высокое пороговое напряжение МНОП-транзистора. Такое состояние транзистора соответствует коду 0. В режиме считывания на затвор транзистора подается напряжение считывания Uсч (рис.8.9, г), величина которого лежит в пределах значений пороговых напряжений транзистора. Если в транзисторе был записан код 1, то значение тока считывания будет значительно больше, чем при хранении записи кода 0.

Так как стирание информации в МНОП-транзисторах происходит под воздействием электрического поля, РПЗУ на МНОП-транзисторах относят к классу электрически управляемых. Отключение напряжения питания не изменяет записанную информацию, поэтому РПЗУ на МДП-транзисторах являются энергонезависимыми.

В репрограммируемых ЗУ используются МНОП-транзисторы с n- и р- каналами. Микросхемы РПЗУ на р-канальных транзисторах КР558РР1, КР1601РРЗ и др. имеют относительно невысокое быстродействие, высокое напряжение программирования (30...40 В) и нуждаются в двух источниках питания.

Микросхем РПЗУ на n-канальных МНОП-транзисторах имеют более высокое быстродействие (в три раза), меньшее напряжение программирования (22 В) и работают с одним источником питания.

Электрически управляемые РПЗУ позволяют производить 103…104 циклов программирования, а РПЗУ с УФ-стиранием – лишь 10...100 циклов, что объясняется быстрым старением диэлектрика в МДП-транзисторах под воздействием УФ-излучения.

9. ОБЩИЕ ПРИНЦИПЫ ПРОЕКТИРОВАНИЯ ИС.

Для реализации ИС с высокой степенью интеграции необходимо уменьшать площадь интегральных элементов, снижать мощность рассеяния при их переключении, а для обеспечения высокого быстродействия использовать схемы с малыми временами задержки.

Комплексным критерием качества схем является работа переключения Ап = Рпот.ср*tзд.р.ср, характеризующая каждую конкретную схемотехнику. Оставаясь в рамках определенной технологии и размеров схем уменьшать один из сомножителей за счет другого.

Уменьшение размеров схемы улучшает показатель Ап в целом (рисунок, а).

Мощность рассеяния отдельной схемы с учетом плотности N схем на кристалле определяет мощность рассеяния кристалла (рисунок, б). Условия охлаждения микросхем определяют расстояния между кристаллами или микросхемами (рисунок, в).

Расстояния между кристаллами обусловливают задержку распространения сигналов в устройствах и в конечном счете их быстродействие (рисунок, г). В зависимости от требований к аппаратуре выбирается последовательность анализа указанных зависимостей, которые могут быть представлены как графически, так и аналитически. Приведённые зависимости показывают отправные условия при проектировании современной схемотехники.

9.1. Система морфологических показателей.

Данная система оценок позволяет выбрать рациональный вариант схемотехнического решения в соответствии с заданными требованиями. Она включает в себя общие показатели, оценивающие пригодность схемотехники к интеграции и не связанные с характеристиками технологического процесса, а также специальные показатели, определяющие надёжностные и технологические аспекты интеграции изделий микроэлектроники.

Наиболее распространенный общий показатель схемотехнического решения - работа переключения Ап. Она является своеобразной константой, характеризующей определённую схемотехнику. Учитывая особую важность повышения плотности компоновки схем на кристалле и степени интеграции микросхем, желательно дополнить этот показатель ещё одним сомножителем.

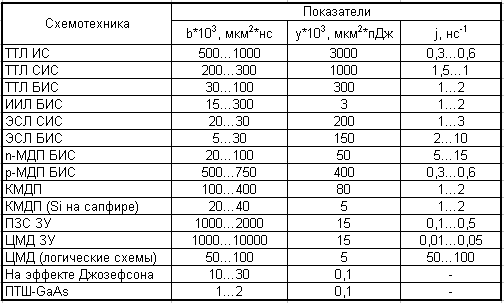

Таким образом, новый общий показатель будет содержать три сомножителя, т.е. у = Рпот.ср*tзд.р.ср*Sэ, где Sэ – площадь элементарной схемы, для которой определены Рпот.ср и tзд.р.ср. Меньшее значение показателя у указывает на лучшую схемотехнику.

Наряду с Ап для выбора схемотехники представляет интерес частный показатель b=Sэ* tзд.р.ср, причём параметры схемы выбираются для получения максимальной плотности компановки и предельного быстродействия.

Широкое распространение имеют обобщённые показатели в виде дроби, где в числитель ставят числовые значения критериальных свойств, увеличение которых улучшает показатель, а в знаменатель - критериальные свойства, числовые значения которых желательно уменьшить. Определяющим показателем интегральных элементных структур, увеличение которого улучшает их качество, следует считать показатель функционального разбиения Ав, определяемый числом функциональных элементов Nфэ, отнесённым к числу n выводов микросхем Ав = Nфэ/n.

Важнейшим параметром ИС, который желательно уменьшать, является время выполнения операции ИС tо (для ИС малых степеней интеграции - это просто задержка распространения сигнала). Отсюда обобщённый морфологический показатель для схемных структур, реализованных в виде ИС с высокой степенью интеграции, определяется отношением Ав к времени выполнения операции конкретной ИС:

j = Ав/tо,

т.е. показатели b и у характеризуют схемотехнику, а показатель j - принципы организации интегральных схем на основе конкретной схемотехники. -

В качестве примера в табл.9.1 приведены усреднённые значения показателя у и диапазон значений показателей j и b для действующих и перспективных схемотехник.

Таблица 9.1.

Анализ данных, приведённых в таблице, показывает, что наиболее эффективны схемные структуры на основе ЭСЛ СИС и БИС. Это объясняется как высоким быстродействием схемотехники ЭСЛ, так и большими значениями Ав у матричных БИС и субсистем памяти. По показателю у выделяются схемы И2Л, что обусловлено их достаточно высоким быстродействием, малыми линейными размерами базового элемента, особенно в структурах с вертикальной инжекцией и диодами Шотки.

Хорошие показатели у n-МДП БИС, которые обусловлены малой площадью и хорошим быстродействием n-МДП-транзисторов, а также высокой степенью совершенства схемо- и системотехнических решений динамических ЗУ с произвольной выборкой и ПЗУ. Следует подчеркнуть, что наивысшие показатели j из всех существующих схем имеют субсистемы памяти.

Среди перспективных интегральных схем по показателю у выделяются ИС, использующие вместо кремния арсенид галлия, имеющий более высокую подвижность носителей, и схемы на эффекте Джозефсона. На основе арсенида галлия, например, изготовляются полевые транзисторы, работающие в режиме обеднения, с затворами, образованными контактами Шотки (ПТШ). Транзисторные схемы ИЛИ - НЕ на таких приборах работают на частоте 3 ГГц, обеспечивая время задержки 0,1 нс. Такую же задержку при срабатывании имеют криотронные элементы на аффекте Джозефсона, однако они работают при температуре жидкого гелия, в отличие от арсенидгаллиевых схем, функционирующих в том же температурном диапазоне, что и обычные полупроводниковые схемы. Параметры отечественных микросхем различных серий приведены в табл.9.2.

Таблица 9.2.

Примечание. Микросхемы серии К65ОО, выполненные по технологии ПТШ-GаАs, являются наиболее быстродействующими из выпускаемых в настоящее время серий и применяются в измерительных системах, системах цифровой связи, блоках уплотнения информации в ЭВМ.

10. ОСОБЕННОСТИ РАЗВИТИЯ ИНТЕГРАЛЬНЫХ СХЕМ ВЫСОКИХ СТЕПЕНЕЙ ИНТЕГРАЦИИ.

С

увеличением функциональной сложности ИС время и себестоимость их проектирования возрастает по экспоненциальному закону. В результате возникает одно из главных противоречий микроэлектроники: при увеличении степени интеграции число типов ИС возрастает и только при очень больших степенях интеграции, когда, например, вся ЭВМ делается в виде БИС, оно снижается до одного типа. Вынужденная специализация БИС приводит к снижению числа выпускаемых схем, поскольку каждая специализированная БИС имеет относительно узкую область применения.

увеличением функциональной сложности ИС время и себестоимость их проектирования возрастает по экспоненциальному закону. В результате возникает одно из главных противоречий микроэлектроники: при увеличении степени интеграции число типов ИС возрастает и только при очень больших степенях интеграции, когда, например, вся ЭВМ делается в виде БИС, оно снижается до одного типа. Вынужденная специализация БИС приводит к снижению числа выпускаемых схем, поскольку каждая специализированная БИС имеет относительно узкую область применения.Противоречие между уровнем интеграции и числом типов ИС разрешается по двум направлениям:

1) введение специализации на последних этапах технологического процесса изготовления БИС;

2) использование логических методов специализации, когда путём программирования БИС настраивается на выполнение определённых функций.

К направлению 2 относятся два типа БИС: субсистемы с алгоритмической универсальностью (микропроцессорные средства вычислительной техники); субсистемы со структурной универсальностью (программируемые логические матрицы и дискретные вычислительные среды или однородные структуры).

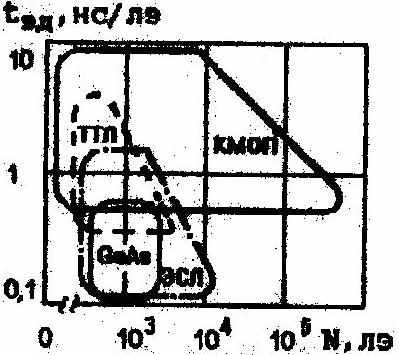

Матричные БИС проектируются на базе различных технологий (см. рисунок), обеспечивающих предельное быстродействие элементов, на основе оптимальной библиотеки функциональных узлов и блоков. Автоматизированные системы выполняют необходимые межсоединения элементов на базовом кристалле в соответствии с назначением специализированной БИС, оставляя часть элементов незадействованными, т.е. платой за универсальность подхода является некоторая избыточность.

Максимально достигнутая степень интеграции БМК составляет 200 тыс. ЛЭ для КМДП-технологии, минимальная задержка -0,1 нс/лэ для ПТШ GаАs технологии БМК.

Примечание. В отечественной практике подучили распространение матричные БИС К1520, К1572 (ЭСЛ); К1527, К1548 (ТТЛШ); К1515, К1806 (КМДП); К6501 (GаАs) и др.

Список литературы:

Алексенко А.Г., Шагурин И.И. Микросхемотехника: Учеб.пособие для вузов.-М.: Радио и связь, 1990.

Фролкин В. Т., Попов Л.Н. Импульсные и цифровые устройства: Учеб.пособие для вузов.-М.: Радио и связь, 1992.

Перспективы развития вычислительной техники: В 11 кн.: Справ.пособие /Под ред. Ю.М.Смирнова.-М.: Высш.шк., 1989.

Микроэлектроника: Учеб.пособие для втузов: В 9 кн. /Под ред. Л.А.Коледова.-М.: Высш.шк., 1987.

Применение интегральных микросхем памяти: Справ. /Под ред. А.Ю.Гордонова, А.А.Дерюгина.-М.: Радио и связь, 1994.

Аваев Н.А., Наумов Ю.Е. Элементы сверхбольших интегральных схем.- М.: Радио и связь, 1986.

Применение интегральных микросхем в электронной вычислительной технике: Справ. /Под ред. Б.Н.Файзулаева, Б.В.Тарабрина.-М.: Радио и связь, 1987.

Горбунов В.Л., Панфилов Д.Н., Преснухин Д.Л. Справ. Пособие по микропроцессорам и микроЭВМ /Под ред. Л.Н.Преснухина.-М.: Высш.шк., 1988.

Цифровые и аналоговые интегральные микросхемы: Справ. /Под ред. С.В.Якубовского.-М.; Радио и связь, 1990.

Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справ.-М.: Радио и связь, 1990.

Шило В.Л. Популярные цифровые микросхемы: Справ.-М.: Радио и связь, 1987.

Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. Микросхемы ЦАП и АЦП: Справ. /Под ред. А.И.Ладика и А.И.Сташкевича.-М.; Радио и связь, 1994.

Базовые матричные кристаллы и матричные БИС /В.Г.Домрачев, П.П.Мальцев, И.В.Новаченко, С.Н.Пономарев.-М.: Энергоатомиздат, 1992.

Схемотехника ЭВМ: Учебник для студентов вузов спец.ЭВМ/ Под ред. Г.Н.Соловьева.- М.: Высш.шк., 1985.

Угрюмов Е.П. Проектирование элементов и узлов ЭВМ: Учеб.пособие для вузов.-М.: Высш.шк., 1987.

Кметь А.Б. Четырёхзначная логика. Реализация операций.-М.: Радио и связь, 1991.

Соломатин Н.М. Логические элементы ЭВМ: Практ. пособие для вузов. 2-е изд., перераб. и доп.- М.: Высш.шк., 1990.

Оглавление

Введение. .................................................. 3

1. СХЕМОТЕХНИКА ЦИФРОВЫХ ИС. ............................... 8

1.1. Базовые схемы транзисторной логики.................... 10

1.2. Транзисторные схемы с общей нагрузкой.................. 11

1.3. Быстродействующие схемы ТТЛ на транзисторах

Шотки (ТТЛШ)........................................... 16

1.4. Схемы с тремя состояниями.............................. 16

2. СХЕМОТЕХНИКА ИС НА ПОЛЕВЫХ ТРАНЗИСТОРАХ.................. 17

2.1. Схемотехника ИС на МДП-транзисторах с одним типом

проводимости........................................... 18

2.2. Схемотехника ИС на комплементарных МДП-транзисторах

(КМДП)................................................. 19

3. СХЕМОТЕХНИКА ИС ИНЖЕКЦИОННОЙ ЛОГИКИ...................... 21

4. СХЕМОТЕХНИКА ТРАНЗИСТОРНОЙ ЛОГИКИ СО СВЯЗАННЫМИ

ЭМИТТЕРАМИ............................................... 23

5. СХЕМОТЕХНИКА ТРИГГЕРНЫХ СХЕМ............................. 26

6. РАЗВИТИЕ СХЕМ ПОТЕНЦИАЛЬНОГО ТИПА.... ................... 32

7. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ....................... 33

8. СХЕМОТЕХНИКА ИНТЕГРАЛЬНЫХ ПОЛУПРОВОДНИКОВЫХ ЗУ........... 36

8.1. Схемотехника запоминающих элементов ОЗУ ............... 37

8.2. Схемотехника запоминающих элементов ПЗУ ............... 45

9. ОБЩИЕ ПРИНЦИПЫ ПРОЕКТИРОВАНИЯ ИС.......................... 49

9.1. Система морфологических показателей.................... 5О

10. ОСОБЕННОСТИ РАЗВИТИЯ ИНТЕГРАЛЬНЫХ СХЕМ

ВЫСОКИХ СТЕПЕНЕЙ ИНТЕГРАЦИИ............................. 53

Список литературы........................................... 54

Изумрудов Олег Алексеевич

МИКРОСХЕМОТЕХНИКА Конспект лекций

Редактор Э.К.Долгатов ИБ N38 Лицензия ЛР N080617 от 10.08.92

Подписано в печать 10.10.96. Формат 60 х 84 1/16. Бумага тип. №2. Печать офсетная. Усл.печ.л.3, 25. Уч.-изд.л. 3,5.

Тираж 105 экз. Заказ 181.

Издательско-полиграфический центр ГЭТУ

197376, С. –Петербург, ул.Проф.Попова, 5