Микросхемотехника

| Вид материала | Документы |

Содержание6. Развитие схем потенциального типа. 7. Программируемые логические матрицы. 8. Схемотехника интегральных полупроводниковых зу. |

- Пояснительная записка к курсовой работе по дисциплине: «Электроника и микросхемотехника», 171.54kb.

- Электронные цепи и микросхемотехника, 24.42kb.

- Расписание Расписание, 43.04kb.

- Учебно-методический комплекс дисциплины «Микросхемотехника» Образовательной профессиональной, 266.28kb.

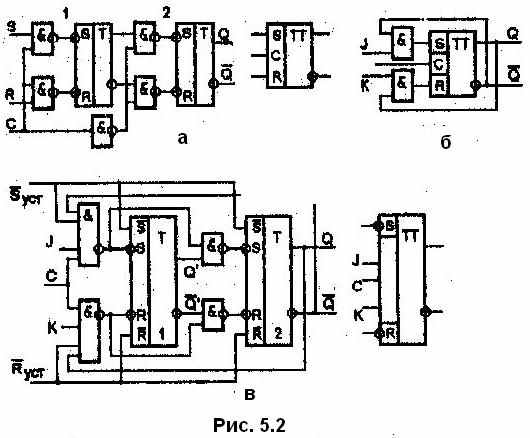

ехническим решением, обеспечивающим сокращение числа тактовых сигналов в цепях управления, является применение двухступенчатых триггеров. Триггер, построенный по двухступенчатой схеме, позволяет в одном и том же такте производить съём информации и запись новой информации. Для хранения одного бита информации в этом случае приходится использовать две элементарные триггерные схемы, информация в которых устанавливается взаимоинверсными тактовыми импульсами (рис.5.2, а). Тем самым удаётся информацию, снимаемую с выхода первой ступени триггера, использовать для управления второй ступенью, что необходимо при построении более сложных схем триггеров. Так как два триггера объединяются в одну схему, второй тактовый импульс получают инвертированием первого. Если на тактовый вход подаётся сигнал С = 1, то входная информация принимается в триггер первой ступени; в это время схемы 2И – НЕ на входе триггера 2-й ступени заблокированы нулевым сигналом.

ехническим решением, обеспечивающим сокращение числа тактовых сигналов в цепях управления, является применение двухступенчатых триггеров. Триггер, построенный по двухступенчатой схеме, позволяет в одном и том же такте производить съём информации и запись новой информации. Для хранения одного бита информации в этом случае приходится использовать две элементарные триггерные схемы, информация в которых устанавливается взаимоинверсными тактовыми импульсами (рис.5.2, а). Тем самым удаётся информацию, снимаемую с выхода первой ступени триггера, использовать для управления второй ступенью, что необходимо при построении более сложных схем триггеров. Так как два триггера объединяются в одну схему, второй тактовый импульс получают инвертированием первого. Если на тактовый вход подаётся сигнал С = 1, то входная информация принимается в триггер первой ступени; в это время схемы 2И – НЕ на входе триггера 2-й ступени заблокированы нулевым сигналом.При подаче на тактовый вход триггера сигнала, равного 0, схемы 2И – НЕ на входе основной запоминающей ячейки закрыты, а на входе вспомогательной запоминающей ячейки – открыты и она принимает информацию из основной ячейки (триггер ступени 2 принимает информацию от триггера ступени 1).

Поскольку триггер, показанный на рис.5.2, а, управляется сигналами R, S и C, это – синхронный двухступенчатый RS-триггер.

Триггер любого типа является простейшим цифровым автоматом.

Его работу можно представить в виде таблицы состояний или полученной на основе её анализа логической формулой, называемой характеристическим уравнением.

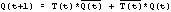

Характеристическое уравнение для асинхронных RS-триггеров имеет вид:

,

,где Q(t+1) - состояние триггера в момент времени t+1.

Уравнение показывает, что триггер в момент времени t устанавливается единичным сигналом S(t) в состояние 1 или сбрасывается единичным сигналом R(t) в состояние 0. Функциональное назначение RS-триггера состоит в реализации задержки на такт или запоминании значения двоичной переменной.

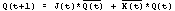

При обработке информации эффективна другая разновидность триггера - триггер со счётным входом, или Т-триггер. Триггер имеет один вход и с приходом очередного сигнала по этому входу переходит в противоположное состояние, т.е. реализует операцию счета по модулю два. Для Т-триггера характеристическое уравнение имеет вид:

,

,где Т(t)- сигнал на входе Т в момент времени t. Функциональное назначение Т-триггера состоит в подсчете числа входных импульсов. Характеристическое уравнение D-триггера:

Q(t+1) = D(t),

т.е. состояние триггера в момент t+1 Q(1+1) определяется лишь сигналом на входе 0 в момент t. Функциональное назначение D-триггера состоит в реализации задержки сигнала на такт.

Универсальные триггеры.

Универсальный триггер можно иcпользовать в качестве RS-, Т- или D-триггера. Существуют две разновидности универсальных триггеров, названные JK- и DV-триггеры.

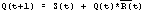

Если на входах R и S RS-триггера поставить схемы 2И, управляемые выходами триггера

и входными сигналами К и J, как показано на рис.5.2, б, в характеристическое уравнение вместо S(t) можно подставить

и входными сигналами К и J, как показано на рис.5.2, б, в характеристическое уравнение вместо S(t) можно подставить  , а вместо R(t) подставить Q(t)K(t). Тогда получим характеристическое уравнение нового триггера:

, а вместо R(t) подставить Q(t)K(t). Тогда получим характеристическое уравнение нового триггера: .

.Т

акой триггер называют JК-триггер. Его особенностью является полная универсальность. Действительно, еcли объединить входы J и К и обозначить их Т, то JK-триггер превращается в T-триггер, что и следует из равенства характеристических уравнений преобразованного триггера и Т-триггера. Другое преобразование характеристического уравнения JК-триггера показывает, что подача на вход J сигнала D, а на вход К - сигнала D превращает JK-триггер в D-триггер:

акой триггер называют JК-триггер. Его особенностью является полная универсальность. Действительно, еcли объединить входы J и К и обозначить их Т, то JK-триггер превращается в T-триггер, что и следует из равенства характеристических уравнений преобразованного триггера и Т-триггера. Другое преобразование характеристического уравнения JК-триггера показывает, что подача на вход J сигнала D, а на вход К - сигнала D превращает JK-триггер в D-триггер: .

.Наиболее распространенная схема двухступенчатого JK-триггера, выполненная на элементах И - НЕ, показана на рис.5.2, в. Из неё очевидно, что для управления логической схемой, отделяющей основную запоминающую ячейку от вспомогательной, не обязательно использовать отдельный инвертор, можно воспользоваться сигналами с логической схемы, управляющей входом основной запоминающей ячейки. Подобные схемы JК-триггеров используются во многих сериях ИС ТТЛ.

Известна другая схема универсального триггера, названная DV-триггером. Характеристическое уравнение DV-триггера имеет вид:

.

.Из этого уравнения очевидно, что соединение входа D с выходом триггера

превращает DV-триггер в Т-триггер;

превращает DV-триггер в Т-триггер; .

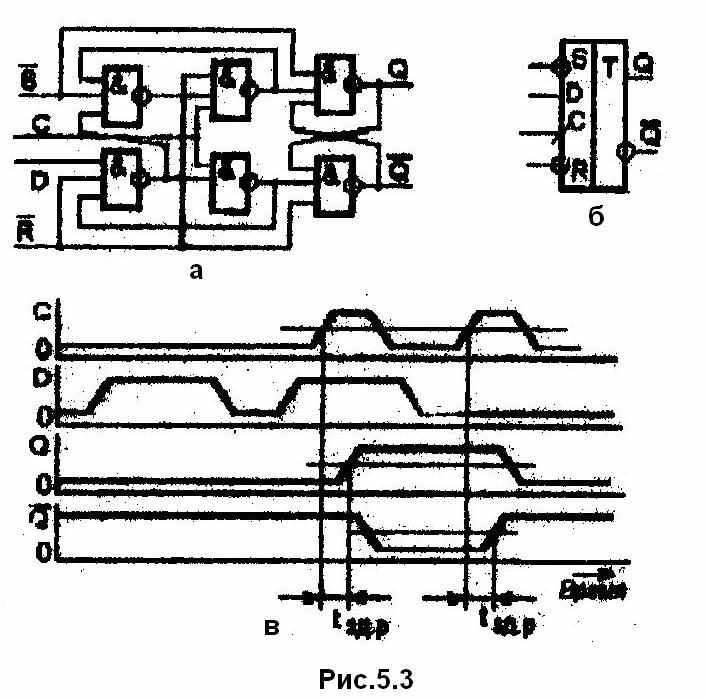

.При этом вход V выполняет роль входа Т. При подаче на вход V сигнала 1 DV-триггер превращается в D-триггер, однако при наличии обратной связи и сигнала С триггер может работать в режиме Т-триггера. Структура D-триггера, построенного на элементах И - НЕ с динамическим управлением записью, приведена на рис.5.3, а. Условное обозначение триггера дано на рис.5.3, б. Временная диаграмма работы D-триггера приведена на рис.5.3, в.

D-триггер широко используется в сериях ИС ТТЛ для реализации задержки, запоминания и счёта импульсов на входе.

6. РАЗВИТИЕ СХЕМ ПОТЕНЦИАЛЬНОГО ТИПА.

Наиболее универсальными и непрерывно совершенствуемыми сериями являются: К155 (ТТЛ); К555, 533 (ТТЛШ) - более 100 типономиналов ИС; 15ЗЗ - более 60 типономиналов ИС; К561, 564 (КМДП) - более 60 типономиналов ИС; К5ОО - более 60 типономиналов ИС.

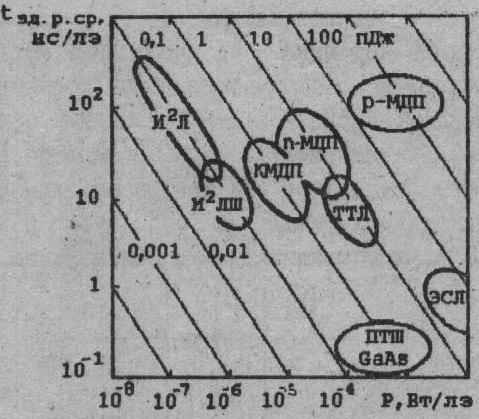

Для указанных серий следует ожидать улучшения показателей по задержке распространения сигналов и мощности рассеяния на простейший логический элемент И - НЕ. Возможности различных схемотехнологических решений определены соответствующими областями на графике (см. рисунок), ограниченном осями "задержка распространения" - "мощность". Диаграмма свидетельствует о перспективности И2Л - схемотехники, особенно с диодами и транзисторами Шотки.

Р

ассмотренные схемотехнические решения используются также в запоминающих устройствах (ЗУ), которые представляют важнейшую часть цифровой техники.

ассмотренные схемотехнические решения используются также в запоминающих устройствах (ЗУ), которые представляют важнейшую часть цифровой техники.Основное направление совершенствования потенциальных схем определяется развитием матричных БИС.

Основу матричных БИС составляет макробиблиотека элементов, триггерных схем, узлов, блоков цифровой техники. По требованию потребителя автоматизированная система межсоединений выполняет необходимые связи на базовом кристалле при условии некоторой избыточности в виде незадействованных элементов. В результате потребитель получает специализированную БИС, наилучшим образом удовлетворяющую её функциональному назначению.

Набор матричных БИС с конкретными фрагментами, ориентированными на потребителя, позволяет проектировать аппаратуру с меньшей стоимостью, большим быстродействием, меньшим временем изготовления и лучшими массогабаритными характеристиками.

7. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ.

В общем случае программируемые логические матрицы (ПЛМ) представляют собой логическую схему для преобразования комбинаций входного двоичного кода в соответствующие комбинации выходного двоичного кода. Правило преобразования кодов задаётся обычно таблицей истинности. Разряд выходного кода Y1Y2 ... Ym могут рассматриваться как система булевых функций от двоичных входных переменных Х1Х2 … Хn. Программируемая логическая матрица реализует систему булевых функций, представленных в минимальной дизъюнктивной нормальной форме.

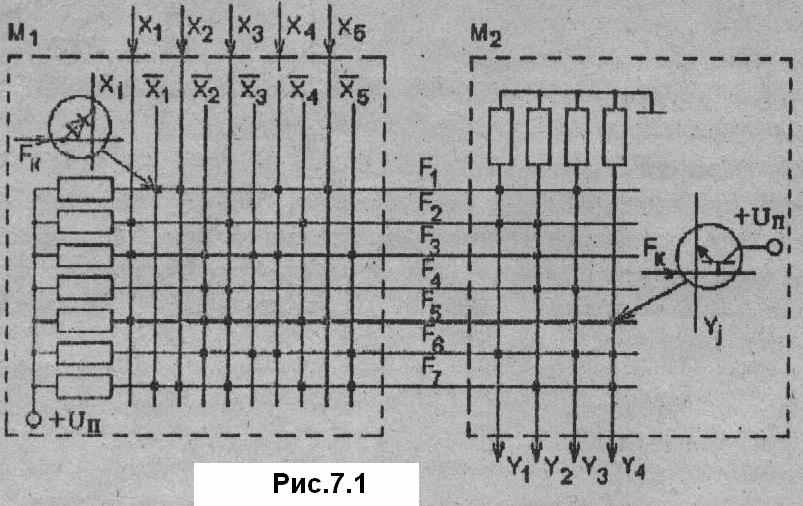

Схема ПЛМ на биполярных элементах показана на рис.7.1. Она представляет собой матрицу И (М1) и матрицу ИЛИ (М2). На матрицу М1 поступают прямые и инверсные значения входных сигналов X1.

На горизонтальных шинах матрицы М1 образуются импликаты входных переменных Fk, поскольку вертикальные шины соединены с соответствующими горизонтальными шинами посредством диодов (на рис.7.1 эти соединения обозначены точками в местах пересечения шин). Если какой-либо вход X (или его инверсия) не имеет соединения с k-ой горизонтальной шиной, то это означает, что данный вход не участвует в образовании конъюнкции Fk (например, конъюнкция F2 безразлична к значениям перемененных Х2 и Х5).

С

игналы Fk являются входными в матрицу М2, реализующую дизъюнкцию импликант, т.е. на выходе матрицы М2 реализуется система выходных функций Y1, Y2, Y3, Y4.

игналы Fk являются входными в матрицу М2, реализующую дизъюнкцию импликант, т.е. на выходе матрицы М2 реализуется система выходных функций Y1, Y2, Y3, Y4. Сигналы переменных Y1...Y4 образуются благодаря соединению посредством транзисторов соответствующих вертикальных и горизонтальных шин в матрице М2 (на рис.7.1 эти соединения обозначены точками в местах пересечений шин; Uп - вывод для подачи питания на ПЛМ).

Разработка ПЛМ осуществляется в несколько этапов с использованием ЭВМ для автоматизации трудоёмких процессов проектирования. С помощью ЭВМ, например, успешно решается задача минимизации логических уравнений, получаемых первоначально из исходных таблиц истинности в СДНФ.

П

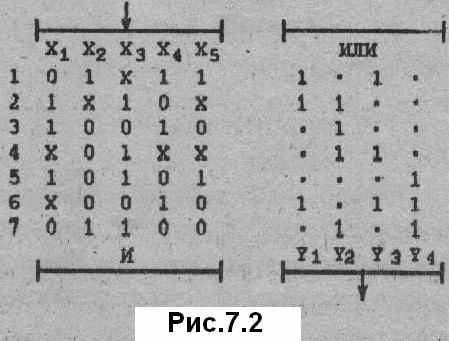

осле минимизации получается табличное изображение матриц М1 и М2, которое затем служит для автоматизированного изготовления фотошаблонов (масок). На рис.7.2 приведено табличное изображение матриц М1 и М2 для ПЛМ, реализующей заданный набор функций. Строки таблицы соответствуют горизонтальным шинам матриц М1 и М2.

осле минимизации получается табличное изображение матриц М1 и М2, которое затем служит для автоматизированного изготовления фотошаблонов (масок). На рис.7.2 приведено табличное изображение матриц М1 и М2 для ПЛМ, реализующей заданный набор функций. Строки таблицы соответствуют горизонтальным шинам матриц М1 и М2.В левой части таблицы (соответствует матрице М1) единицами отмечены переменные Х, которые входят в терм Fk без инверсии; нулями – переменные Х, входящие в терм Fk с инверсией; косыми крестами - переменные Х, не входящие в терм Fk.

В правой части таблицы (соответствующей матрице М2) единицами в каждом столбце отмечены термы Fk, входящие в качестве дизъюнкций в соответствующие функции Yj.

В микропроцессорной технике ПЛМ наиболее широкого используются для реализации микропрограммных УУ.

По способу программирования, т.е. по способу выполнения межсоединений шин в матрицах, различают ПЛМ:

1) программируемые в процессе изготовления;

2) программируемые пользователем.

В ПЛМ первого типа информация заносится в матрицы путём подключения элементов к шинам благодаря металлизации нужных участков схемы, что выполняется с помощью фотошаблона (маски). Никаких изменений в схеме пользователь в этом случае в ходе эксплуатации ПЛМ, сделать не может. Подобным способом изготовляются ПЛМ, встраиваемые в МП БИС, автономные ПЛМ стандартного микропрограммного обеспечения и т.п. ПЛМ второго типа поставляются незапрограммированными, и их функциональная ориентация производится пользователем с помощью специального оборудования, причем существуют ПЛМ с однократной записью информации и репрограммируемые ПЛМ, в которых записанная информация может быть стёрта ультрафиолетовым или рентгеновским лучом.

БИС ПЛМ разрабатываются как на основе биполярной, так и на основе МДП-технологии.

8. СХЕМОТЕХНИКА ИНТЕГРАЛЬНЫХ ПОЛУПРОВОДНИКОВЫХ ЗУ.

Интегральные полупроводниковые ЗУ находят широкое применение во многих областях науки и техники, где возникают проблемы оперативного накопления и длительного хранения информации. Высокое быстродействие и надёжность, компактность и малая мощность потребления, простота согласования с логическими цепями устройств явились теми важнейшими факторами, которые позволили им прочно, занять ведущее место при создании оперативных и сверхоперативных ЗУ, накопителей информации.

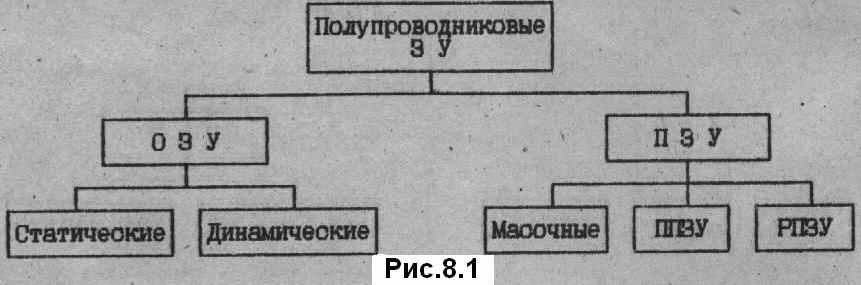

Основные виды полупроводниковых ЗУ представлены на рис.8.1. По конструктивно-технологическому признаку полупроводниковые ЗУ делятся на два больших класса: ЗУ на МДП-структурах и ЗУ на биполярных структурах.

П

о функциональному назначению и областям применения ЗУ подразделяются на оперативные (ОЗУ), позволяющие как записывать, так и считывать информацию с высокой скоростью, и постоянные (ПЗУ), предназначенные в основном только для считывания информации.

о функциональному назначению и областям применения ЗУ подразделяются на оперативные (ОЗУ), позволяющие как записывать, так и считывать информацию с высокой скоростью, и постоянные (ПЗУ), предназначенные в основном только для считывания информации.По схемотехническому принципу запоминающих элементов (ЗЭ) и способу электронного обеспечения различают ОЗУ статического и динамического типов. В статическом ЗУ запоминающим элементом является триггер, выполненный по МДП- или биполярной технологии. В динамических ЗУ информация в виде электрического заряда хранится в ЗЭ, представляющих собой МДП-конденсаторы.

По способу программирования ПЗУ подразделяют на три группы: однократно программируемые изготовителем с помощью фотошаблона-маски (масочные) - МПЗУ; однократно программируемые пользователем путём пережигания соединительных перемычек - ППЗУ; многократно программируемые пользователем (репрограммируемые) - РПЗУ.

8.1. Схемотехника запоминающих элементов ОЗУ.

Успехи полупроводниковой технологии позволили создать современные ЗУ, превосходящие ранее известные по многим параметрам. Полупроводниковое ЗУ представляет собой совокупность запоминающих элементов (ЗЭ) и схем управления их работой, размещённых на одном кристалле.

К ЗЭ полупроводниковых ЗУ предъявляется ряд требований, к важнейшим из которых относят: а) минимальную мощность потребления;

б) простоту схемного решения и минимальное число компонентов;

в) обеспечение устойчивой работы ЗЭ при значительных отклонениях параметров компонентов;

г) минимальную площадь, занимаемую на кристалле и др.

Рассмотрим наиболее часто встречающиеся, схемотехнические решения, использующиеся при построении ЗЭ полупроводниковых ЗУ.

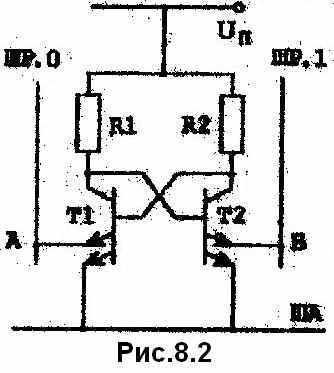

Из биполярных запоминающих элементов наиболее широко применяются компактные схемы элементов хранения на многоэмиттерных транзисторах, которые обеспечивают гибкую организацию цепей управления режимами работы запоминающего элемента. На рис.8.2 приведена схема ЗЭ, представляющая собой триггер, установка которого в одно из устойчивых состояний производится подачей сигналов в точки А и Б схемы. В составе ЗУ запоминающие элементы работают в режимах записи, хранения и считывания.

С

остояние ЗЭ, соответствующее хранению 0 или 1, определяется тем, какой из транзисторов триггера находится в открытом или закрытом состоянии. Примем, что состоянию 0 соответствует следующее: Т2 - закрыт, Т1 - открыт. Тогда для записи 1 необходимо одновременно подать высокие потенциалы на адресную шину ША и на разрядную шину ШР.О и низкий потенциал - на разрядную шину ШР.1.

остояние ЗЭ, соответствующее хранению 0 или 1, определяется тем, какой из транзисторов триггера находится в открытом или закрытом состоянии. Примем, что состоянию 0 соответствует следующее: Т2 - закрыт, Т1 - открыт. Тогда для записи 1 необходимо одновременно подать высокие потенциалы на адресную шину ША и на разрядную шину ШР.О и низкий потенциал - на разрядную шину ШР.1.В этом случае происходит переключение триггера: транзистор Т1 закрывается, а транзистор Т2 - открывается. После снятия сигналов с управляющих шин ЗЭ переходит в режим хранения 1. Режим работы ЗЭ выбирается с учетом требуемой помехозащищённости, которая определяется током и напряжением на коллекторном переходе.

В режиме хранения устойчивость ЗЭ определяется уровнем помех, который не должен превышать порога помехозащищённости.

Считывание информации производится подачей положительного сигнала по адресной шине ША, при этом в транзисторе, находящемся в открытом состоянии, происходит перераспределение тока эмиттеров, причем большая часть его будет проходить в разрядную шину ШР.1 (для рассмотренного выше примера), что приведёт к срабатыванию усилителя считывания, соединенного с ней.

Кроме многоэмиттерного варианта схемы ЗЭ используются и другие схемы на биполярных структурах.

Наиболее широко для построения памяти используются запоминающие элементы на МДП-структурах. По принципу действия они делятся на статические и динамические.

В

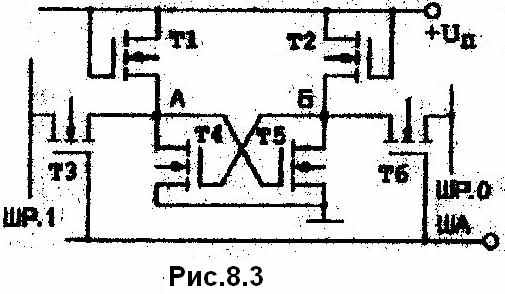

качестве базовой схемы ЗЭ статического типа используется схема триггера, образованного двумя последовательно соединёнными ключевыми схемами с положительной обратной связью. Ключевые схемы выполняются на транзисторах как одного, так и различных типов проводимости.

качестве базовой схемы ЗЭ статического типа используется схема триггера, образованного двумя последовательно соединёнными ключевыми схемами с положительной обратной связью. Ключевые схемы выполняются на транзисторах как одного, так и различных типов проводимости.В схеме ЗЭ (рис.8.3) использованы транзисторы одного типа проводимости, причем нагрузочный транзистор имеет затвор, соединённый со стоком. Режимы работы транзисторов ключевой схемы выбираются такими, чтобы транзистор Т4 в активном состоянии находился в крутой, а нагрузочный транзистор Т1 - в пологой областях переходной характеристики. Управляющие сигналы, с помощью которых осуществляется режим записи и считывания информации, подаются по шинам: адресной ША и разрядным ШР.О и ШР.1.

Рассмотрим один из возможных режимов записи информации, когда сигналы подаются по двум разрядным шинам. Управляющие транзисторы Т3 и Т6 обладают двусторонней проводимостью, поэтому при отпирании их сигналом, подаваемым на затвор, ток в зависимости от состояния триггера может проходить как в направлении плеча триггера, так и в противоположном. Если принять, что нулевому состоянию триггера соответствует открытый транзистор Т4, то запись единичной информации производится подачей положительного сигнала на шину ША, одновременно с которым передаётся отрицательный сигнал на шину ШР.0.

Сигналом на ША открываются оба управляющих транзистора Т3 и Т6, через которые производится перезаряд ёмкостей узлов А и Б схемы. Отрицательным сигналом с шины ШР.О осуществляется разряд ёмкости узла А, и это приводит к тому, что транзистор Т4 будет переходить в закрытое состояние, а транзистор Т5 - в открытое. Если же в исходном состоянии транзистор Т5 был открыт, то аналогичное воздействие не изменит состояния триггера.

Временные параметры переходного процесса переключения ЗЭ определяются параметрами используемых транзисторов, управляющих сигналов и ёмкостью узлов А и Б схемы триггера.

Считывание информации производится подачей сигнала по шине ША, открывающего транзисторы Т3 и Т6, при этом потенциал точки А передается на входную цепь усилителя считывания, который подключен к шине ШР.1. В режиме считывания амплитуда сигнала на шине ША выбирается таким образом, чтобы не произошло переключения триггера.

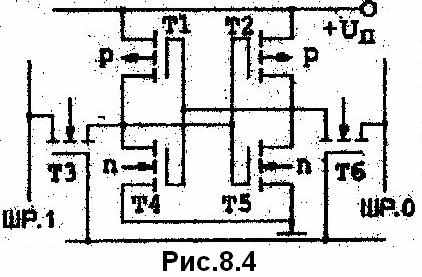

В режиме хранения снижение мощности потребления достигается применением запоминающих элементов на транзисторах с различным типом проводимости. На рис.8.4 приведена схема ячейки хранения на КМДП-структурах, в которой транзисторы Т1, Т2 имеют каналы р-типа, а транзисторы ТЗ – Т6 - каналы n-типа.

Существенное отличие данной схемы от рассмотренной ранее состоит в том, что нагрузочные транзисторы Т1 и Т2 работают в ключевом режиме, и в базовых ключевых схемах Т1, Т4 (Т2, Т5) один из транзисторов всегда закрыт, поэтому мощность потребления определяется только токами утечки n- и р-переходов. Это обстоятельство и объясняет важнейшее достоинство такого ЗЭ - практически полное отсутствие мощности потребления в режиме хранения.

О

днако в процессе записи информации, который производится аналогично процессу записи ранее рассмотренного ЗЭ, на переключение ячейки хранения расходуется значительная мощность.

днако в процессе записи информации, который производится аналогично процессу записи ранее рассмотренного ЗЭ, на переключение ячейки хранения расходуется значительная мощность.Причиной повышенного потребления мощности при переключений ЗЭ является переходное состояние схемы, при котором ток протекает через приоткрытые транзисторы Т1, Т4 и Т2, Т5.

Важным достоинством ЗЭ, построенных на транзисторах с различным типом проводимости, является их существенно меньшая чувствительность к допускам на параметры транзисторов, а также разбросу питающих напряжений, который может достигать 40% от номинальных значений.

Рассматривая схемотехнику ЗЭ статического типа, следует отметить их использование при построении ассоциативных ЗУ (АЗУ). Запоминающие элементы АЗУ кроме обеспечения записи, хранения и считывания информации выполняют и набор логических функций.

Поиск и считывание информации в АЗУ происходят путём параллельного сравнения разрядов всех хранящихся в нём слов с некоторой внешней информацией (признаком опроса). В результате за одно обращение к ЗУ определяются все слова, соответствующие заданному признаку. Сочетание выборки по содержанию с параллельной обработкой информации обеспечивает АЗУ большие преимущества по эффективности использования аппаратных средств и упрощает математическое обеспечение вычислительных устройств.

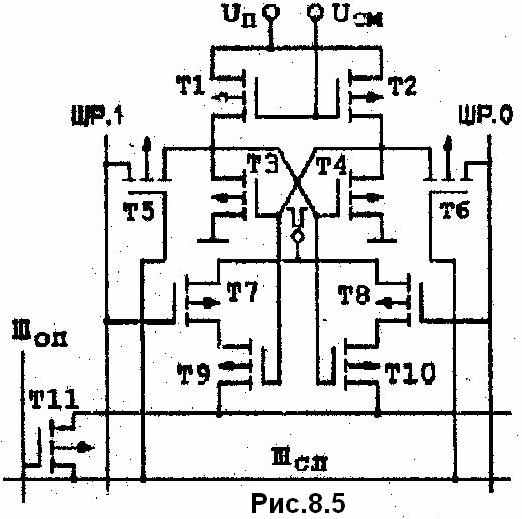

Основу ЗЭ АЗУ составляет статический триггер, дополненный рядом схем, выполняющих логические функции. Схема ячейки хранения АЗУ приведена на рис.8.5. Она обеспечивает хранение информации, проведение режимов записи, считывания, а также логические функции сравнения и маскирования. Запись и считывание информации производятся так же, как и в ЗЭ статического типа, которые были рассмотрены ранее.

При выполнении операции сравнения сравнивается код, записанный в триггере, с кодом, передаваемым по шинам ШР.1 и ШР.О.

К

од, передаваемый на сравнение, представлен сочетанием потенциалов (импульсов), устанавливаемых на разрядных шинах, например единице соответствует низкий уровень на ШР.1 и высокий - на ШР.О, а нулю - противоположные сочетания уровней. Подчеркнём, что информация представляется парафазными сигналами.

од, передаваемый на сравнение, представлен сочетанием потенциалов (импульсов), устанавливаемых на разрядных шинах, например единице соответствует низкий уровень на ШР.1 и высокий - на ШР.О, а нулю - противоположные сочетания уровней. Подчеркнём, что информация представляется парафазными сигналами.Функция сравнения реализуется на двух схемах конъюнкторов для отрицательных сигналов, выполненных на транзисторах Т7, Т9 и Т8, Т10, собранных по каскадной схеме.

Опрос состояния этих схем производится отрицательными сигналами, подаваемыми на шину опроса Шоп. Если хотя бы одна из пар транзисторов Т7, Т9 (Т8, Т10) будет находиться в проводящем состоянии, то ток через транзистор Т11 передаётся в словарную шину Шсл, что указывает на несовпадение сравниваемых кодов. Если шина Шсл объединяет все разряды сравниваемого кода, то только в случае совпадения кодов во всех разрядах ток в словарной шине будет отсутствовать. Из схемы видно, что маскирование операции сравнения в рассматриваемом разряде, выполняемое подачей высокого потенциала по шинам ШР.1 и ШР.О, приводит к тому, что транзисторы Т7 и Т8 закрыты, а это исключает передачу тока в словарную шину, исключая тем самым рассматриваемый разряд из операции сравнения, т.е. маскируя его.

Схемотехника ЗЭ полупроводниковых интегральных ЗУ статического типа требует достаточно большого числа компонентов, вследствие чего площадь, занимаемая на кристалле такими ЗЭ, достаточно велика. Это ограничивает информационную ёмкость микросхемы памяти. Поиски схемотехнических решений реализации ЗЭ с меньшим числом компонентов привели к использованию ячеек динамического типа.

В основе построения ЗЭ динамического типа использована возможность представления информации в виде заряда на ёмкости, который может сохраняться достаточно долгое время. Наиболее широкое практическое применение нашли ЗЭ динамического типа на n-МДП-структурах. Они характеризуются высокими быстродействием и степенью интеграции, малыми токами утечки и, следовательно, большим временем сохранения заряда на ёмкости.

Однако малая ёмкость, а следовательно, и заряд, а также наличие токов утечки приводят к необходимости производить подзаряд ёмкости, т.е. восстанавливать (регенерировать) записанную информацию. Для этого вводится специальный режим работы ЗУ с ячейками динамического типа - режим регенерации. Регенерация выполняется через каждые n-миллисекунд.

Принцип динамического хранения информации позволяет не только построить ЗЭ с меньшим числом компонентов вплоть до применения однотранзисторной ячейки, но и снизить мощность потребления, что облегчает размещение на одном кристалле матрицы с достаточно большим числом ЗЭ и схем электроники управления процессами записи, считывания и регенерации информации.

На рис.8.6,а приведена схема трёхтранзисторного ЗЭ, в котором Т1 - транзистор записи, Т2 - транзистор считывания, ТЗ - информационный транзистор. Запоминающей ёмкостью является Сзэ, а Ссб представляет собой суммарную паразитную ёмкость шины столбца. Управление ЗЭ осуществляется сигналами, подаваемыми на шины столбца Шсб и строки Шск. Режим записи информации производится подачей высокого потенциала +10 В на шину отроки Шск, а на шину столбца Шсб при записи 1 - потенциала +5 В или же потенциала земли при записи 0. В результате записи 1 заряд ёмкости Сзэ должен быть таким, чтобы транзистор Т3 был надёжно открыт, а при записи 0 – надёжно закрыт.

При записи 1 напряжение Uск открывает транзисторы Т1 и Т2 и ёмкость Сзэ заряжается до потенциала Uсб. Если ранее на ней был положительный потенциал (была записана 1), то её подзаряд Сзэ будет производится лишь частью тока, подаваемого с вертикальной шины, поскольку другая его часть (и причём значительная) будет проходить через открытые транзисторы Т2, Т3, вследствие чего мощность потребления ЗЭ будет достаточно большой.

Д