1. Источники питания электронной аппаратуры

| Вид материала | Реферат |

- Модулей, которые предназначены для модернизации электронной аппаратуры путем ее перевода, 24.38kb.

- Оценка влияния технологических факторов на точность автоматической сборки блоков электронной, 66.46kb.

- Хроники объединенного фонда электронных ресурсов «наука и образование», 875.7kb.

- А. Е. Пескин обслуживание и ремонт радиотелевизионной аппаратуры учебное пособие, 2674.23kb.

- Лекция 1, 901.66kb.

- Радиоматериалы и радиокомпоненты» Направление подготовки: 210400 «Радиотехника» Общая, 16.41kb.

- Микроэлектроника, 271.85kb.

- Во избежание поражения электрическим током используйте только источники питания с заземлением!, 26.43kb.

- Практическая работа по курсу «Основы электронной коммерции», 69.84kb.

- Программа обучения рассчитана на специалистов, которые не обладают достаточными знаниями, 3191.48kb.

ТЕМА 16. Флэш-память. Перспективные запоминающие устройства.

16.1 Флэш-память

Флэш-память (Flash-Меmorу) по типу запоминающих элементов и основным принципам работы подобна памяти типа Е2РROМ однако ряд архитектурных и структурных особенностей позволяют выделить ее в отдельный класс. Разработка Флэш-памяти считается кульминацией десятилетнего развития схемотехники памяти с электрическим стиранием информации.

В схемах Флэш-памяти не предусмотрено стирание отдельных слов, стирание информации осуществляется либо для всей памяти одновременно, либо для достаточно больших блоков. Понятно, что это позволяет упростить схемы ЗУ, т. е. способствует достижению высокого уровня интеграции и быстродействия при снижении стоимости. Технологически схемы Флэш-памяти выполняются с высоким качеством и обладают очень хорошими параметрами.

Термин Flash по одной из версий связан с характерной особенностью этого вида памяти — возможностью одновременного стирания всего ее объема Согласно этой версии ещё до появления Флэш-памяти при хранении секретных данных использовались устройства, которые при попытках несанкционированного доступа к ним автоматически стирали хранимую информацию и назывались устройствами типа Flash

(вспышка, мгновение). Это название перешло и к памяти, обладавшей свойством быстрого стирания всего массива данных одним сигналом.

Одновременное стирание всей информации ЗУ реализуется наиболее просто, но имеет тот недостаток, что даже замена одного слова в ЗУ требует стирания и новой записи для всего ЗУ в целом. Для многих применений это неудобно. Поэтому наряду со схемами с одновременным стиранием всего содержимого имеются схемы с блочной структурой, в которых весь массив памяти делится на блоки, стираемые независимо друг от друга. Объем таких блоков сильно разнится: от 256 байт до 128 Кбайт.

Для первого направления в связи с редким обновлением содержимого параметры циклов стирания и записи не столь существенны как информационная емкость и скорость считывания информации. Стирание в этих схемах может быть как одновременным для всей памяти, так и блочным. Среди устройств с блочным стиранием выделяют схемы со специализированными блоками (несимметричные блочные структуры). По имени так называемых Вооt-блоков, в которых информация надежно защищена аппаратными средствами от случайного стирания, эти ЗУ называют Вооt Blосk Flash Метоrу. Вооt блоки хранят программы инициализации системы, позволяющие ввести ее в рабочее состояние после включения питания.

Микросхемы для замены жестких магнитных дисков (Flash-File Метоrу) содержат более развитые средства перезаписи информации и имеют идентичные блоки (симметричные блочные структуры).

Одним из элементов структуры Флэш-памяти является накопитель (матрица запоминающих элементов). В схемотехнике накопителей развиваются два направления: на основе ячеек типа ИЛИ-НЕ (N011) и на основе ячеек типа И-НЕ (№N0).

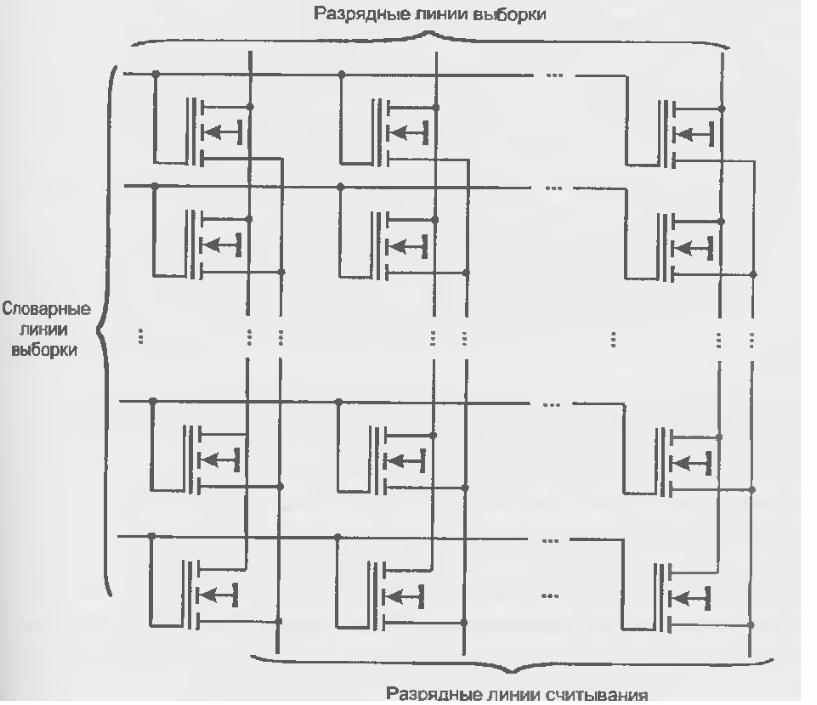

Рисунок 4.8 – Структура матрицы накопителя Флэш-памяти на основе ячеек ИЛИ-НЕ

Накопители на основе ячеек ИЛИ-НЕ (с параллельным включением ЛИЗ-МОП-транзисторов с двойным затвором) обеспечивают быстрый доступ к словам при произвольной выборке. Они приемлемы для разных применений, но наиболее бесспорным считается их применение в памяти для хранении редко обновляемых данных. При этом возникает полезная преемственность с применявшимися ранее КОМ и ЕРКОМ, сохраняются типичные сигналы управления, обеспечивающие чтение с произвольной выборкой. Структура матрицы накопителя показана на рисунке 4.8. Каждый столбец представляет собою совокупность параллельно соединенных транзисторов Разрядные линии выборки находятся под высоким потенциалом. Все транзисторы невыбранных строк заперты. В выбранной строке открываются и передают высокий уровень напряжения на разрядные линии считывания те транзисторы, в плавающих затворах которых отсутствует заряд электронов. и, следовательно, пороговое напряжение транзистора имеет нормальное (не повышенное) значение.

Накопители на основе ячеек ИЛИ-НЕ широко используются фирмой Intel. Имеются мнения о конкурентоспособности этих накопителей и в применениях, связанных с заменой жестких магнитных дисков Флэш-памятью.

Структуры с ячейками И-НЕ более компактны, но не обеспечивают режима произвольного доступа и практически используются только в схемах замены магнитных дисков. В схемах на этих ячейках сам накопитель компактнее, но увеличивается количество логических элементов обрамления накопителя.

Для улучшения технико-экономических характеристик в схемах Флэш-памяти применяются различные средства и приемы:

1. Прерывание процессов записи при обращениях процессора для чтения (Еrase Suspend). Без этого возникали бы длительные простои процессора. т. к. запись занимает достаточно большое время. После прерывания процесс записи возобновляется под управлением внутренних средств Флэш-памяти.

2. Внутренняя очередь команд, управляющих работой Флэш-памяти, которая позволяет организовать конвейеризацию выполняемых операций и ускорить процессы чтения и записи

3. Программирование длины хранимых в ЗУ слов для согласования с различными портами ввода/вывода.

4. Введение режимов пониженной мощности на время, когда к ЗУ нет обращений, в том числе режима глубокого покоя, в котором мощность снижается до крайне малых значений (например, ток потребления снижается до 2 мкА). Эти особенности очень важны для устройств с автономным (батарейным) питанием.

5. Приспособленность к работе при различных питающих напряжениях (5 В; 3,3 В и др.). Сама схема "чувствует" уровень питания и производит необходимые переключения для приспособления к нему.

6. Введение в структуры памяти страничных буферов для быстрого накопления новых данных, подлежащих записи. Два таких буфера могут работать в режиме, называемом "пинг-понг", когда один из них принимает слова, подлежащие записи, а другой в это время обеспечивает запись своего содержимого в память. Когда первый буфер заполнится, второй уже освободится, и они поменяются местами.

7. Различные меры защиты от случайного или несанкционированного доступа.

Флэш-память с адресным доступом, ориентированная на хранение не слишком часто изменяемой информации, может иметь одновременное стирание всей информации (архитектура Вulk Еrаsе) или блочное стирание (архитектура Вооt Blосk Flash Метоrу).

Имея преемственность с ЗУ типов Е2РRОМ и ЕРRОМ, разработанными ранее, схемы Флэш-памяти предпочтительнее Е2РRОМ по информационной емкости и стоимости в применениях, гяе не требуется индивидуальное стирание слов, а в сравнении с ЕРRОМ обладают тем преимуществом, что не требуют специальных условий и аппаратуры для стирания данных, которое к тому же происходит гораздо быстрее.

Память типа Вulk Еrаsе

Память типа Вulk Еrаsе фирмы Intel, наиболее известной среди разработчиков Флэш-памяти, имеет время записи байта около 10 мкс, допускает до 105 циклов стирания, напряжение программирования для нее составляет 12 В ± 5%, ток активного режима около 10 мА, в режиме покоя около 50 мкА. Время доступа при чтении равно приблизительно 100 нс, время стирания и время программирования всего кристалла составляет 0,6...4 с для кристаллов емкостью 256 Кбит...2 Мбит.

В отличие от традиционного управления схемами памяти с помощью адресных и управляющих сигналов. Флэш-память имеет дополнительное управление швами-командами, записываемыми процессором в специальный регистр, функционирующий только при высоком уровне напряжения на выводе микросхемы, обозначаемом UPP (напряжении программирования). При отсутствии такого уровня UPP схема работает только как память для чтения под управлением традиционных сигналов, задающих операции чтения. снижения мощности, управления третьим состоянием и выдачи идентификатора.

16.2 Перспективные запоминающие устройства (FRАМ, РFRАМ, МRАМ, OUM)

Успехи создания ЗУ на основе полупроводниковой технологии не снимают проблемы дальнейшего совершенствования микросхем памяти. Чтобы прибиться к идеалу, желательно к таким свойствам ЗУ, как высокая емкость, быстродействие и малая потребляемая мощность, добавить и энергонезависимость, которой современные ОЗУ не обладают. Если к такому комплексу качеств прибавить и низкую стоимость, то получатся ЗУ, близкие к идеалу. Пути приближения к идеалу включают в себя попытки использования нескольких новых для технологии ЗУ физических явлений - ферроэлектрических, магниторезистивных, связанных с изменением фазовых состояний маралов и др.

16.2.1 ЗУ типа FRАМ (ферроэлектрические)

В ферроэлектрических FRАМ (Ferroelectric RАМ) основой запоминающего элемента служит материал, в кристаллической структуре которого имеется бистабильный атом. Занимая одно из двух возможных пространственных положений ("верхнее" или "нижнее"), этот атом создает в ферроэлектрическом материале внутренние диполи того или иного знака (спонтанная поляризация).

С помощью электрического поля можно придать внутреннему диполю тот или иной знак. Под воздействием внешнего электрического поля и при температуре не выше определенной (связанной с точкой Кюри) материал поляризуется, делали выстраиваются упорядоченное состояние материала может отображать двоичные данные 0 и 1. Зависимость поляризации Р от напряжения U имеет петлю гистерезиса, показанную на рис. 4.9. а Через Uс на рисунке обозначены коэрцитивные напряжения, через PR - остаточные поляризации, до сохраняются после снятия электрических полей.

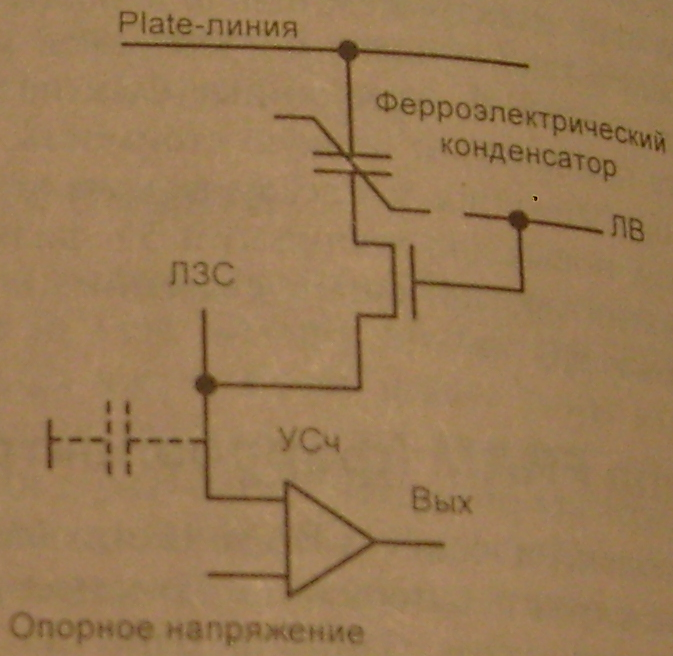

Если бы вместо ферроэлектрического конденсатора был включен обычный, соединенный не с Рlatе-линией, в с обшей точкой схемы (схемной землей), то получился бы запоминающий элемент обычного динамического ЗУ, и подключение конденсатора через ключевой транзистор к линии записи/считывания ЛЗС позволяло бы считывать хранимую элементом информацию (ЛВ – линия выборки), т.к. в зависимости от заряженности или разряженности конденсатора при его подключении по-разному изменялось бы напряжение на линии ЛЗС. Здесь же нужно выявить не наличие или отсутствие заряда конденсатора, а знак поляризации запоминающего элемента. Простым подключением ферроэлектрического конденсатора к линии ЛЗС этого не определить. Поэтому после отпирания транзистора выборки на Plate-линию подается импульс длительностью около 10 нс. Если этот импульс вызовет переполяризацию элемента, то через него пройдет большой ток, который сможет ощутимо изменить напряжение на линии ЛЗС (на ее емкости, изображенной на рисунке 4.9 б штриховыми линиями). Если же знак поляризации был иным и переполяризации элемента не будет, то ток через него будет малым и не сможет заметно повлиять на потенциал линии ЛЗС.

а б

Рисунок 4.9 – Петля гистерезиса ферроэлектрического материала (а) и схема запоминающего элемента FRAM (б)

После пропускания импульса от Plate-линии подается питание на усилитель считывания УСч, логическое состояние которого определяется тем, смогла ли линия ЛЗС зарядиться выше или ниже опорного напряжения, т.е. в конечном счете знаком поляризации запоминающего элемента. При этом выходной сигнал усилителя фиксируется (защелкивается) для обратной подачи на разрядную линию и возвращения фотоэлектрического конденсатора в его первоначальное состояние после проведенной разрушающей операции чтения. Такая обратная перезапись информации занимает время около 10-20 нс и сохраняет считанные данные. Процессы в ЗУ синхронизированы с фронтами управляющих импульсов.

Рассмотренный запоминающий элемент называют элементом типа 1Т/1С, т.к. в его схеме используется один транзистор и один фотоэлектрический конденсатор. Существуют также элементы типа 2Т/2, похожие на сдвоенный элемент 1Т/1С. В таких элементах две ячейки 1Т/1С программируются в противоположных направлениях и в элементе имеются две разрядные линии с взаимоинверсными сигналами. Используется дифференциальный канал для восприятия сигналов, а это повышает помехоустойчивость ЗУ и улучшает также некоторые другие параметры.

Достоинства FRAM: быстрые запись и чтение, практически неограниченное число циклов чтения/записи, малые напряжения питания и потребляемая мощность, компактность запоминающего элемента (площадь его соизмерима с площадью обычного запоминающего элемента DRAM), высока радиационная стойкость, энергонезависимость.

Такой набор достоинств позволяет FRAM выступить в роли конкурента как по отношению к динамическим ОЗУ, не обладающим энергонезависимостью, так и по отношению к EEPROM и Flash, не обеспечивающим быструю запись данных. В настоящее время ЗУ типа FRAM уже выпускаются рядом фирм (Ramtron International, Samsung, NEC и др.)

16.2.2 ЗУ типа PFRAM (полимерно-ферроэлектрические)

ЗУ типа PFRAM (Polimeric Ferroelectric RAM) – разновидность ферроэлектрических ЗУ. Они построены на основе ферроэлектрических материалов – пленок с двумя стабильными состояниями поляризации, полученных около 10 лет назад шведской фирмой Opticom. Над применением таких пленок в схемах ЗУ работает фирма Intel совместно с дочерней компанией указанной шведской фирмы.

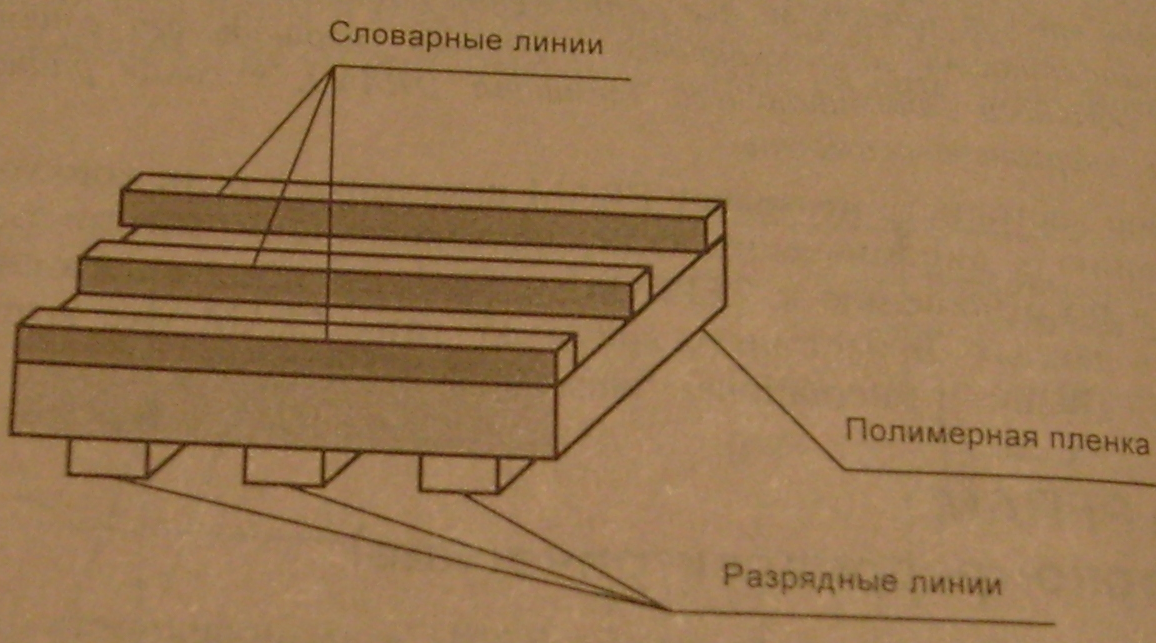

В пленке, толщина которой меньше 0,1 мкм, образуются ориентированные диполи, которые служат запоминающими элементами, хранящими различные двоичные данные при изменении знака поляризации. Расположенные в полимерной пленке запоминающие элементы размещаются между двумя взаимно перпендикулярными металлическими дорожками, на которые подаются определенные напряжения (рис. 16-3). Индивидуальные биты активизируются возбуждением словарной и разрядной линии, на пересечении которых они находятся. Наличие созданных диполей себя проявляет, и набор чувствительных усилителей в разрядных линиях воспринимает значения битов данных.

Рисунок 4.10 – Схематическая конструкция полимерно-ферроэлектрического ЗУ.

ТЕМА 17. Цифроаналоговые преобразователи (ЦАП). Функциональные схемы, принцип работы, основные характеристики. Включение ЦАП для преобразования кодов со знаком. Умножающие ЦАП. Построение генераторов заданной формы на основе ЦАП. Аналогоцифровые преобразователи (АЦП). АЦП последовательного счета, следящие и интегрирующие АЦП: функциональные схемы и принцип работы.

17.1. Цифро-аналоговые преобразователи (ЦАП)

ЦАП служит для преобразования цифровой информации в аналоговую форму, т.е. выходной сигнал ЦАП в общепринятых единицах измерения тока или напряжения (мВ, В, мА) соответствует численному значению входной кодовой комбинации.

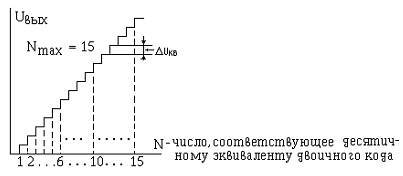

Например, при подаче на вход ЦАП кодовой комбинации (в десятичном эквиваленте) равной 150 на его выходе при этом имеется напряжение 1500 мВ, это значит, что изменение значения входной кодовой комбинации (входного числа) на единицу приводит к изменению выходного напряжения на 10 мВ. В этом случае мы имеем ЦАП с шагом преобразования цифровой информации 10 мВ. Величина напряжения, соответствующая одной единице цифровой информации, называется шагом квантования Duкв. При подаче на вход ЦАП последовательной цифровой комбинации, меняющейся от 0 до N, на его выходе появится ступенчато-нарастающее напряжение (рис. 17.1). Высота каждой ступени соответствует одному шагу квантования Duкв.

Рисунок 4.11 – Диаграмма выходного напряжения ЦАП

Если число входной кодовой комбинации соответствует N, то выходное напряжение Uвых ЦАП = ND´uкв. Таким образом можно вычислить значение выходного напряжения для любой входной кодовой комбинации. Нетрудно убедиться в том, что Duкв является масштабным коэффициентом преобразователя, имеющим размерность тока или напряжения (так как цифровая комбинация на входе ЦАП размерности не имеет). Обычно, значение Duкв выбирают кратным десяти, что облегчает процесс пересчета соответствия преобразованного и исходного сигналов. Так как Duкв определяет минимальное значение выходного напряжения аналогового сигнала Uвых мин. = Duкв, при выборе его значения необходимо учитывать также шумовые факторы, погрешности усиления масштабирующих усилителей и компаратора.

17.1.1 Функциональные схемы, принцип работы, основные характеристики.

Точность преобразования и качество работы ЦАП характеризуют следующие параметры: относительная разрешающая способность, абсолютная разрешающая способность, абсолютная погрешность преобразования, нелинейность преобразования, дифференциальная нелинейность, скорость преобразования (время одного преобразования) и максимальная частота преобразования.

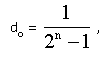

1. Относительная разрешающая способность

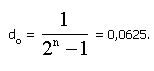

здесь n- количество разрядов двоичного числа, подаваемого на вход АЦП (n - соответствует числу разрядных входов ЦАП). Относительная разрешающая способность - это обратная величина от максимального числа уровней квантования.

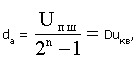

2. Абсолютная разрешающая способность

где Uпш - напряжение полной шкалы, соответствующее опорному напряжению ЦАП. Это напряжение можно считать равным максимальному выходному напряжению; 2n - 1 = N - количество ступеней квантования.

Численно абсолютная разрешающая способность равна шагу квантования Duкв.

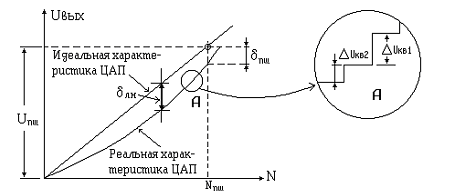

3. Абсолютная погрешность преобразования dпш

показывает максимальное отклонение выходного напряжения Uвых в точке пересечения с идеальной характеристикой (прямой) на уровне напряжения полной шкалы (рис. 4.12). Абсолютная погрешность преобразования оценивается в процентах или же в единицах младшего значащего разряда (МР). При оценке значения абсолютной погрешности преобразования знак напряжения не учитывается.

показывает максимальное отклонение выходного напряжения Uвых в точке пересечения с идеальной характеристикой (прямой) на уровне напряжения полной шкалы (рис. 4.12). Абсолютная погрешность преобразования оценивается в процентах или же в единицах младшего значащего разряда (МР). При оценке значения абсолютной погрешности преобразования знак напряжения не учитывается. 4. Нелинейность преобразования ЦАП dлн определяет максимальное отклонение реальной характеристики от идеальной (рис. 4.12) и оценивается также в процентах или в единицах младшего значащего разряда.

Рисунок 4.12 – Пояснения к определению погрешностей преобразования ЦАП

5 . Дифференциальная нелинейность преобразования ЦАП dдф.лн численно равна максимальной разности двух соседних приращений (шагов квантования)

dдф.лн = Duкв 1 - Duкв2.

Дифференциальная нелинейность оценивается в младших значащих разрядах и обычно не превышает нескольких единиц мр.

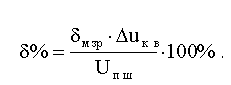

Младший значащий разряд численно определяет минимальное значение выходного напряжения, т.е. квант напряжения. Для оценки дифференциальной нелинейности dдф.лн в процентах можно воспользоваться выражением

Время установления выходного напряжения или тока tуст - интервал времени от подачи входного двоичного входного кода до вхождения выходного сигнала в заданные пределы. Максимальная частота преобразования fпр - наибольшая частота дискретизации, при которой параметры ЦАП соответствуют заданным значениям. Максимальная частота и время установления определяют быстродействие ЦАП.

Виды ЦАП условно можно разделить на две группы: с резисторными матрицами, безматричные ЦАП. В интегральном исполнении применяются только ЦАП с прецизионными резисторными матрицами, формирующими выходные сигналы путем суммирования токов.

ЦАП содержит элементы цифровой и аналоговой схемотехники. В качестве аналоговых элементов используются операционные усилители, аналоговые ключи (коммутаторы), резисторные матрицы и т.д.

Аналоговые элементы, входящие в состав ЦАП, практически полностью определяют его качественные и эксплуатационные параметры, основную роль при этом играют точность подбора номиналов резисторов резисторной матрицы и параметров операционного усилителя (ОУ).

Операционный усилитель представляет собой усилитель постоянного тока, имеющий коэффициент усиления по напряжению более тысячи. Он имеет дифференциальный входной каскад, т.е. имеет два входа: инвертирующий и неинвертирующий.

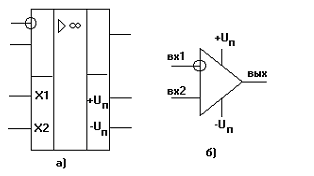

Своему названию ОУ “обязан” аналоговым вычислительным машинам, так как первоначально он был ориентирован на моделирование различных математических операций. Появление ОУ в виде интегральных микросхем привело к быстрому росту популярности ОУ в реализации аналоговой и гибридной электронной схемотехники. Условное обозначение ОУ показано на рис. 4.13.

Рисунок 4.13 – Рисунок 17-3 Условные обозначения операционного усилителя а) стандартное, по ГОСТу; б) для рабочей документации

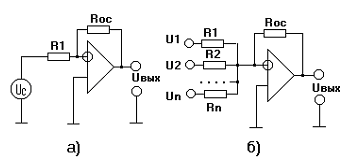

Благодаря большому коэффициенту усиления (современные ОУ имеют коэффициент усиления К=105 ...106) и малым входным токам, усилители, построенные на базе ОУ, обладают уникальными свойствами. В частности, параметры многих устройств определяются только внешними цепями - цепями обратной связи, соединяющими выход ОУ с его входом. Например, коэффициент усиления усилителя, схема которого показана на рис. 4.14 (а), определяется с высокой точностью отношением сопротивлений двух резисторов К=-Rос/R.

Рисунок 4.14 – Схемы усилителей на ОУ а) инвертирующий, б) суммирующий усилитель

Если на инвертирующий вход усилителя на ОУ подать сигнал от нескольких источников (рис. 4.14, б), то выходной сигнал определяется как произведение суммы входных токов на величину сопротивления резистора обратной связи

Uвых = -Rос(Iвх1+Iвх2+. . . . +Iвх.n).

Входной ток от каждого источника определяется как отношение

Iвх=Uвх/Ri,

где Ri - сопротивление резистора в цепи i-того входа.

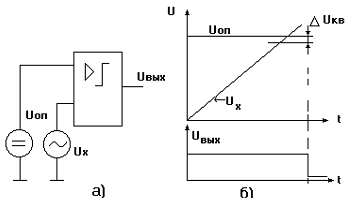

Свойство ОУ суммировать входные токи с последующим преобразованием в напряжение широко используется при построении ЦАП и АЦП. На базе ОУ можно построить компараторы напряжения (сравнивающие устройства). При использовании ОУ в качестве компаратора напряжения на один его вход подается опорное напряжение Uоп, на второй - напряжение обрабатываемого (преобразуемого) сигнала Ux. При соответствующих условиях на выходе компаратора формируется сигнал логической“1”, если (Uоп - Ux) >Duкв, и логического “0”, если (Uоп - Ux)

Рисунок 4.15 –Схемное обозначение (а) и диаграммы напряжений (б) компаратора напряжения

При построении ЦАП и АЦП применяются аналоговые ключи, коммутирующие цепи аналоговых сигналов под воздействием управляющих цифровых сигналов. Токи, коммутируемые электронными аналоговыми ключами, не превышают 10 . . . 50 мА. Относительно высокое сопротивление открытого ключа (50 - 600 Ом) требует наличия высокоомной нагрузки, что обеспечивается высокоомным входным сопротивлением ОУ.

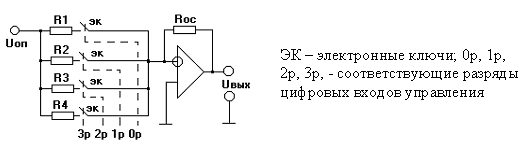

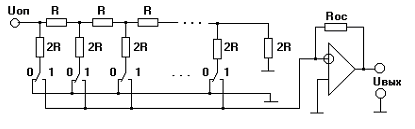

При реализации ЦАП в интегральном исполнении большие трудности вызывает подгонка высокоточных резисторов с сопротивлениями, отличающимися по номиналам друг от друга на несколько порядков. Поэтому, в интегральном исполнении применяются исключительно резистивная матрица R-2R. В качестве примера рассмотрим четырехразрядный ЦАП, использующий схему суммирования токов на ОУ (рис. 4.16).

Рисунок 4.16 –Схема простейшего ЦАП

Относительная разрешающая способность рассматриваемого ЦАП:

Абсолютная разрешающая способность определяется при известном значении опорного напряжения Uоп. Наиболее удобными значениями Uоп являются напряжения, кратные степени двойки, т.е. 10,24 В, 5,12 В, 2,56 В и т.д.

Если принять значение опорного напряжения равным 10,24 В, то абсолютная разрешающая способность (DUкв) определяется как:

DUкв=0,0625 × 10,24 = 0,625В.

Сопротивление резистора в цепи ключа, управляемого старшим разрядом двоичного кода, должно быть в два раза больше сопротивления резистора обратной связи Rос. Сопротивление каждого последующего младшего разряда в два раза больше, чем сопротивление соседнего старшего разряда. Отсюда следует, что с увеличением количества разрядов цифровых входов ЦАП резко увеличивается соотношение сопротивлений резисторов нулевого и самого старшего разрядов (R0=2nRn):

R0/Rn=2n = T.

Если n=8, то это отношение составляет 256. Увеличение Т может привести к чрезмерному увеличению сопротивления резистора младшего разряда или же к сильному уменьшению номинала резистора самого старшего разряда. Поэтому ЦАП с резистивной матрицей R-2nR применяется при небольшом количестве разрядов (при n<8). При больших Т затруднительным становится также изготовление резистивных матриц в интегральном исполнении. Известно, что номиналы резисторов в интегральном исполнении не должны превышать 50...100 кОм. Поэтому, в ЦАП, выполненных по интегральной технологии, в основном применяются резистивные матрицы R-2R. Функциональная схема ЦАП с матрицей R-2R показана на рис. 4. 17.

Рисунок 4.17 –Цап с резистивной матрицей R-2R

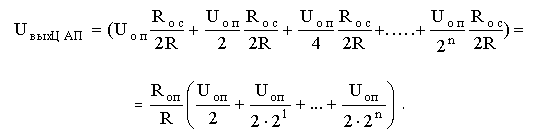

Напряжение на выходе ЦАП (рис. 4.17) определяется как:

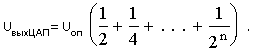

Чтобы выполнить условие формирования выходного напряжения в соответствии с двоичным кодом входного числа, необходимо получить равенство Rос=R, тогда

Дробные члены суммы играют роль весовых коэффициентов, а шаг квантования определяется отношением DUкв=Uоп/2n. На рис. 4.17 символы “0” и “1” перед электронными ключами показывают на состояние ключа при подаче на цифровые входы ЦАП логического “0” или “1”, соответственно.

Рисунок 4.18 –Схема ЦАП на микросхеме КР752ПА1

17.1.2 Преобразование кодов со знаком

Подключение ЦАП для преобразований кодов со знаком:

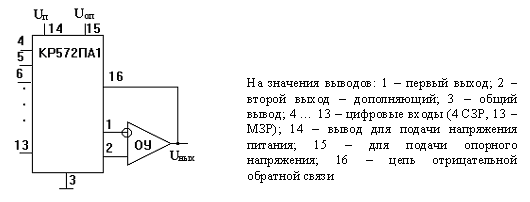

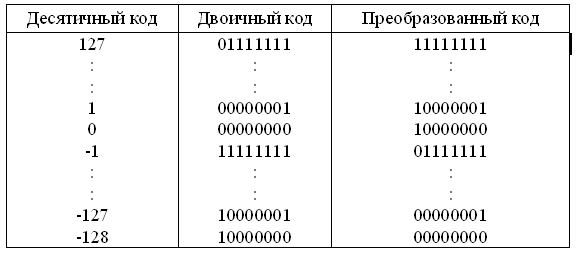

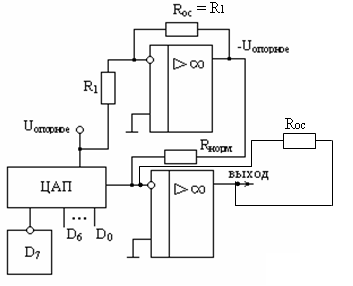

При вводе кода со знаком в ЦАП путем инверсии знакового разряда к этому коду прибавляется код 128-ми (таблица 10). Диапазон входных кодов: -128 127 переходит в диапазон 0 255. После преобразования из полученного тока вычитается ток соответствующий 128-ми (рис.10-3) и тогда знак напряжения на выходе ОУ совпадает со знаком входного кода.

Таблица 17-1 Преобразование кода

Рисунок 4.18 – ЦАП-преобразователь кода со знаком

17.1.3 Умножающие ЦАП

Поскольку выходное напряжение ЦАПа пропорционально и величине Uопорное, и входному коду, значит оно пропорционально их произведению.Поэтому ЦАП производит умножение кода и опорного напряжения.

Умножающие ЦАП можно использовать как усилитель с коэффициентом усиления управляемым с помощью кода.

Промышленностью ЦАП выпускаются в виде интегральных микросхемы и содержат в своем составе резистивную матрицу R-2R, электронные ключи и резистор обратной связи Rос. Для подключения токосуммирующего операционного усилителя имеются специальные выводы. Схема десятиразрядного ЦАП, построенного на базе ИМС К572ПА1, показана на рис. 17.8. ЦАП типа К572ПА1 может управляться кодом, полученным с выходов дискретных интегральных схем типов КМОП и ТТЛ. В последнем случае выходные уровни, соответствующие сигналам уровня логической “1”, должны быть повышены путем соединения выходов ТТЛ инверторов с источником питания 5 В через резисторы сопротивлением 2 - 10 кОм. Непосредственное согласование входных управляющих уровней ЦАП с параметрами сигналов ТТЛ- схем можно достичь путем уменьшения напряжения питания ЦАП до 5 В. Однако при этом возрастает погрешность ЦАП. Основные параметры наиболее широко используемых ЦАП приведены в табл. 5.1. В табл. 17.2 использованы следующие обозначения: n- число разрядов управляющего кода; tуст - время установления выходного напряжения; Iвых - максимальный выходной ток; dлн - нелинейность преобразования ЦАП; Uп - напряжение питания; Uоп - опорное напряжение.