1. Источники питания электронной аппаратуры

| Вид материала | Реферат |

- Модулей, которые предназначены для модернизации электронной аппаратуры путем ее перевода, 24.38kb.

- Оценка влияния технологических факторов на точность автоматической сборки блоков электронной, 66.46kb.

- Хроники объединенного фонда электронных ресурсов «наука и образование», 875.7kb.

- А. Е. Пескин обслуживание и ремонт радиотелевизионной аппаратуры учебное пособие, 2674.23kb.

- Лекция 1, 901.66kb.

- Радиоматериалы и радиокомпоненты» Направление подготовки: 210400 «Радиотехника» Общая, 16.41kb.

- Микроэлектроника, 271.85kb.

- Во избежание поражения электрическим током используйте только источники питания с заземлением!, 26.43kb.

- Практическая работа по курсу «Основы электронной коммерции», 69.84kb.

- Программа обучения рассчитана на специалистов, которые не обладают достаточными знаниями, 3191.48kb.

ТЕМА 9. Шифраторы и дешифраторы. Сумматоры и полусумматоры.

9.1 Шифраторы, дешифраторы и преобразователи кодов

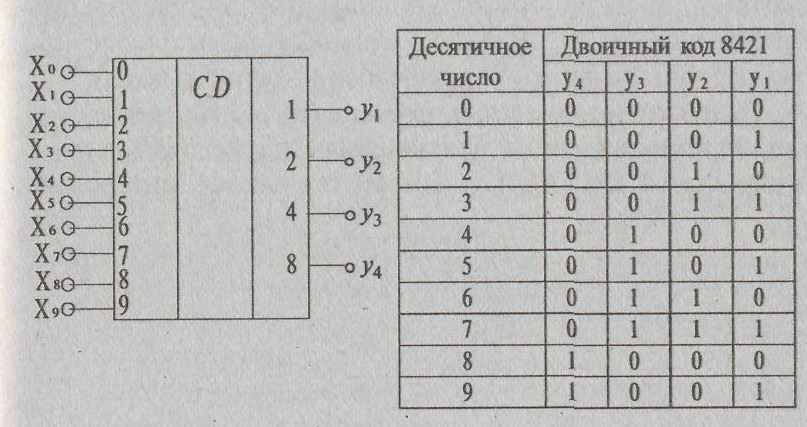

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа. Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением n = 2m, где n — число входов, m — число выходов. Так, для преобразования кода кнопочного пульта в четырехразрядное двоичное число достаточно использовать лишь 10 входов, в то время как полное число возможных входов будет равно 16 (n = 24 = 16), поэтому шифратор 10x4 (из 10 в 4) будет неполным.

Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент времени подается только на один вход. Условное обозначение такого шифратора и таблица соответствия кода приведены на рис. 3.61. Используя данную таблицу соответствия, запишем логические выражения, включая в логическую сумму те входные переменные, которые соответствуют единице некоторой выходной переменной. Так, на выходе у, будет логическая «1»тогда, когда логическая «1» будет или на входе X,, или Х3, или Х5, или Х7, или X,, т. е.

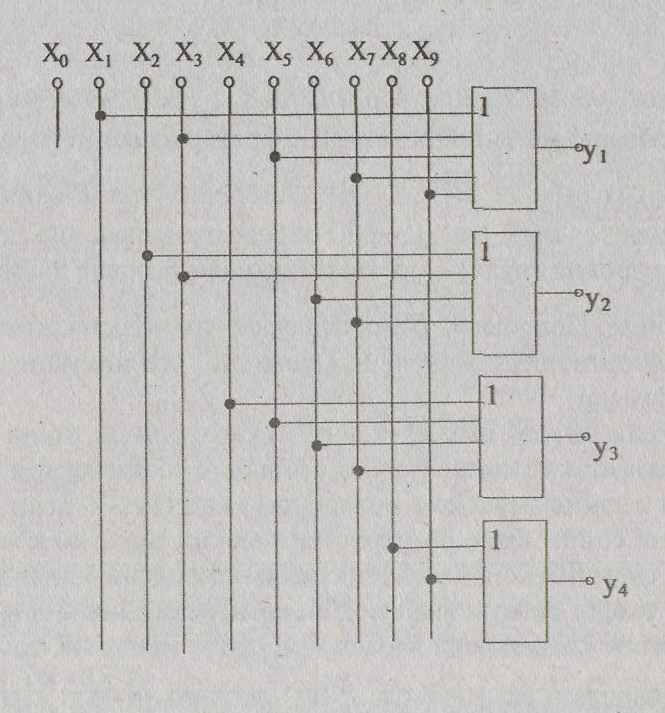

У1 = X1 + Х3 + Х5 + Х7 + X9.

Аналогично получаем

У2 = X2 + X3 + X6 + X7

У3 = X4 + X5 + X6 + Х7, у4 = Х8+ Х9.

Представим на рис. 3.62 схему такого шифратора, используя элементы ИЛИ.

На практике часто используют шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подан сигнал «1», т. е. на приоритетный шифратор допускается подавать сигналы на несколько входов, а он выставляет на выходе код числа, соответствующего старшему входу.

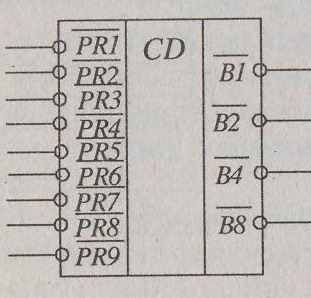

Рассмотрим в качестве примера (рис. 3.63) шифратор с приоритетом (приоритетный шифратор) К555ИВЗ серии микросхем К555 (ТТЛШ). Шифратор имеет 9 инверсных входов, обозначенных через PR1, ... , РР9. Аббревиатура PR обозначает «приоритет». Шифратор имеет четыре инверсных выхода В\, ... , В8. Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа. Например, В8 обозначает, что ноль на этом выходе соответствует числу 8. Очевидно, что это неполный шифратор.

Если на всех входах — логическая единица, то на всех выходах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111). Если хотя бы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номером входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер.

Например, если на входе PR\ — логический ноль, а на всех остальных входах — логическая единица, то на выходах име-ются следующие сигналы: В1 - О, В2 -1, В4 -1, В8 -1, что соответствует числу 1 в инверсном коде (1110).

Если на входе PR9 логический ноль, то независимо от других входных сигналов на выходах имеются следующие

сигналы: В1 — 0, В2-1, В4-\, .88-0, что соответствует числу 9 в инверсном коде (0110).

Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Для получения шифраторов с большим числом входов, т. е. наращивания размерности шифратора, объединяют микросхемы шифраторов с дополнительными выводами.

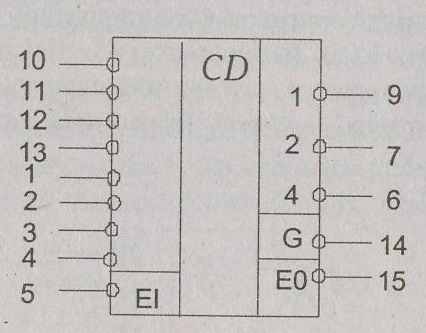

Так микросхема К555ИВ1 (рис. 3.64) представляет собой приоритетный шифратор 8 х 3, т. е. имеет 8 инверсных входов и 3 инверсных выхода. Помимо этого она имеет вход разрешения EI, выход переноса Е0 и выход G, определяющий признак входного информационного сигнала.

Если на всех информационных входах логическая 1, то при подаче на вход EI логического 0, на выходах 1—2—4 и G будут такие логические 1, а на выходе переноса ЕО — логический 0.

Если активизировать один из информационных входов (подать на него логический 0), то на выходах 1—2—4 появится инверсный код, соответствующий номеру активизированного входа, на входе G — логический 0, являющийся признаком подачи входного сигнала, а на выходе ЕО — логическая 1.

Если же микросхема не активизирована, т. е. на вход разрешения Е1 подана логическая 1, то на всех выходах микросхемы также будет логическая 1 независимо от того, что будет подано на информационные входы.

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением

т =

, где п — число входов, а т — число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

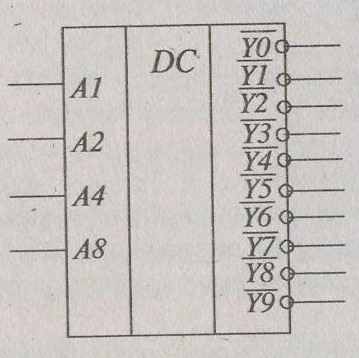

, где п — число входов, а т — число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.Обратимся для примера к дешифратору К555ИД6 серии К555 (рис. 3.65). Дешифратор имеет 4 прямых входа, обозначенных через А\, ..., Л8. Аббревиатура А обозначает «адрес» (от англ. address). Указанные входы называют адресными. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа.

Дешифратор имеет 10 инверсных выходов У0, ... , К9. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный.

Значение активного уровня (нуля) имеет тот выход, номер которого равен десятичному числу, определяемому двоичным числом на входе. Например, если на всех входах — логические нули, то на выходе ко— логический ноль, а на остальных выходах — логическая единица. Если на входе А2 — логическая единица, а на остальных входах — логический ноль, то на выходе Y2 — логический ноль, а на остальных выходах — логическая единица. Если на входе — двоичное число, превышающее 9 (например, на всех входах единицы, что соответствует двоичному числу 1111 и десятичному числу 15), то на всех выходах — логическая единица.

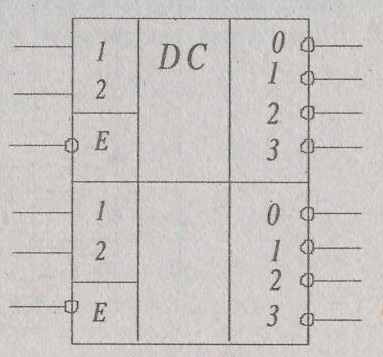

Помимо информационных имеется один или более входов, называемых входами разрешения, или адресными входами. Так, микросхема КР531ИД14 представляет собой два дешифратора 2 х 4, т. е. каждый дешифратор имеет два информационных входа и четыре инверсных выхода, а также инверсный вход разрешения (рис. 3.66).

9.2 Сумматоры и полусумматоры.

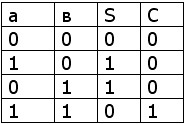

Полусумматор это логическая цепь, которая вырабатывает сигналы суммы (S) и переноса (С) при сложении двух двоичных чисел а и в.

Составим таблицу функционирования.

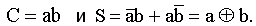

Из таблицы получим:

. – сигнал суммы;

. – сигнал суммы;  - сигнал переноса.

- сигнал переноса. Эти выражения упрощению не поддаются.

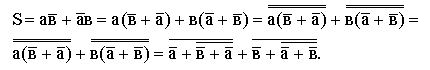

Приведем к виду, удобному для реализации на элементах ИЛИ-НЕ.

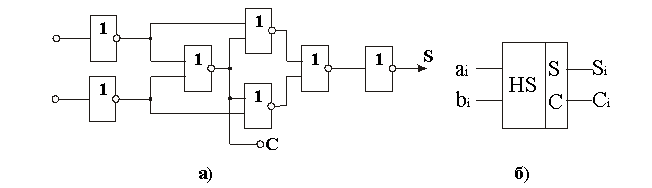

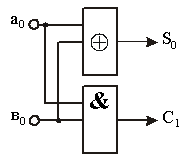

Исходя из полученных формул составим схему полусумматора (рис. 2.31, а):

Рисунок 2.31 – Схема полусумматора

Поскольку полусумматор имеет широкое применение и его выпускают в виде отдельной микросхемы, он имеет собственное обозначение (рис. 2.31 б).

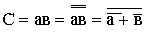

Составляя дизъюнктивную нормальную форму для полусумматора, мы получили следующие булевы функции:

Следовательно, перенос происходит с помощью функции И, а выработка сигнала суммы (функции неравнозначности) производится элементом ИСКЛЮЧАЮЩЕЕ – ИЛИ. На рис.2.32 показана схема полусумматора, составленная из этих элементов.

Рисунок 2.32 – Схема полусумматора.

Сумматор. В отличие от полусумматора должен воспринимать 3 входных сигнала: 2 слагаемых и сигнал переноса с предыдущего разряда.

Сумматором называется операционный узел ЭВМ, выполняющий операцию арифметического сложения двух чисел.

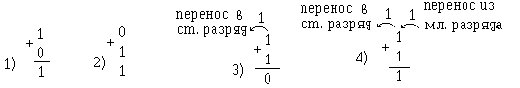

Чтобы понять сущность работы комбинационного сумматора, рассмотрим примеры суммирования двух одноразрядных двоичных чисел:

Из приведенных примеров (1 - 4) видно, что если отсутствует перенос из младшего разряда, то перенос в старший разряд может быть только в одном случае, когда оба числа равны единице. Если же имеется перенос из младшего разряда, то перенос в старший разряд будет всегда, кроме одного случая, когда оба слагаемых равны нулю.

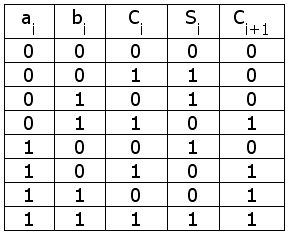

Составим таблицу функционирования:

Таблица 15

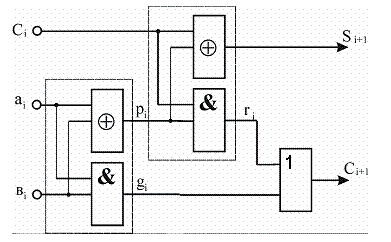

Схема сумматора может быть реализована на двух полусумматорах, соединенных как указано на схеме рис. 2.33. В этой схеме выделим промежуточные сигналы Pi, gi, ri. Введем эти сигналы в новую таблицу функционирования. Соответствие работы этой схемы (рис. 2.33) и таблицы фунционирования можно проверить перебором всех возможных вариантов.

Рисунок 2.33 – Схема полного сумматора

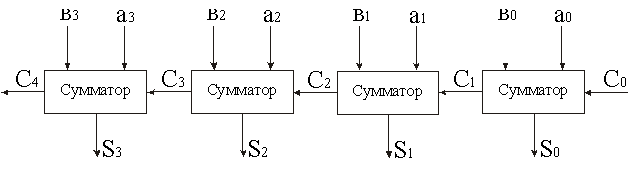

Многоразрядный сумматор с последовательным переносом. Таким образом, в общем случае для каждого разряда необходима логическая схема с тремя входами ai, bi, Ci и двумя выходами Si, Ci+1. Такая схема и есть полный сумматор. Ее можно реализовать с помощью двух полусумматоров.

Таблица 16

Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один полный сумматор. Только в младшем разряде можно обойтись полусумматором. На рис. 2.34 приведена схема, предназначенная для сложения двух четырехразрядных чисел А и В. Эта схема выпускается в интегральном исполнении. В ее младшем разряде также используется полный сумматор, чтобы иметь возможность наращивания разрядности схемы.

Рисунок 2.34 – Сумматор с последовательным переносом

Сумматоры с параллельным переносом. Время выполнения операции в сумматоре с параллельным переносом намного больше времени сложения в одноразрядном сумматоре. Действительно, сигнал переноса С4 только тогда может принять истинное значение, когда будет установлено правильное значение С3. Такой порядок выполнения операций называется последовательным переносом (Ripple Carry).

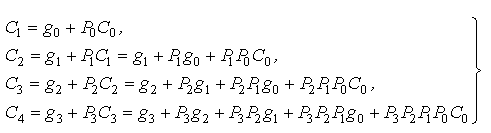

Чтобы уменьшить время операции сложения многоразрядных чисел можно использовать схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значениям входных переменных.

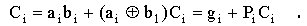

Согласно таблице переключений, в общем случае для сигнала переноса любого i-го разряда справедливо соотношение:

(1)

(1) Величины gi, ri вычисляются в качестве промежуточных результатов и в полном сумматоре. Следовательно, их получение не требует дополнительных затрат. Смысл этих величин объясняется совсем просто. Сигнал gi вырабатывается тогда, когда в данном разряде перенос происходит из-за комбинации входных переменных ai,bi. Поэтому его называют функцией генерации переноса. Сигнал Pi показывает, передается ли полученный в младшем разряде сигнал переноса Ci дальше. Поэтому он называется функцией распространения переноса.

Пользуясь выражением (1), можно вывести следующие формулы для вычисления сигналов переноса:

(2)

(2) Очевидно, что хотя полученные выражения достаточно сложные, время формирования сигнала переноса в любой разрад с помощью вспомогательных функций определяется только времением здержки распространения сигнала на двух элементах. Эти функции реализуются специальным комбинационным устройством – схемой ускоренного переноса.

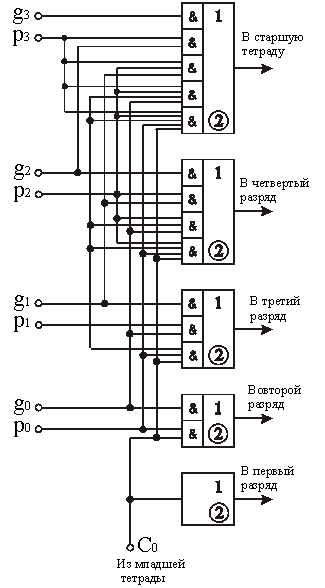

Схема сумматора с параллельным переносом приведена на рис. 2.35, а. На рис. 2.35, б изображена схема устройства параллельного переноса в группе из четырех разрядов. Эта схема реализует систему уравнений (2).

Рисунок 2.35 –Схема сумматора с параллельным переносом

Рисунок 2.36 –Схема ускоренного переноса

Схема выпускается в интегральном исполнении.

Сложение чисел, содержащих более четырех разрядов, можно реализовать подключением нескольких четырехразярадных сумматоров.

ТЕМА 10. Арифметико-логические устройства (АЛУ). Программируемые логические матрицы (ПЛМ). Матричные умножители

10.1 Арифметико-логические устройства и блоки ускоренного переноса

Арифметико-логические устройства АЛУ (ALU, Arithmetic-Logic Unit) выполняют над словами ряд действий. Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛУ и обеспечивающей его перестройку с одной операции на другую.

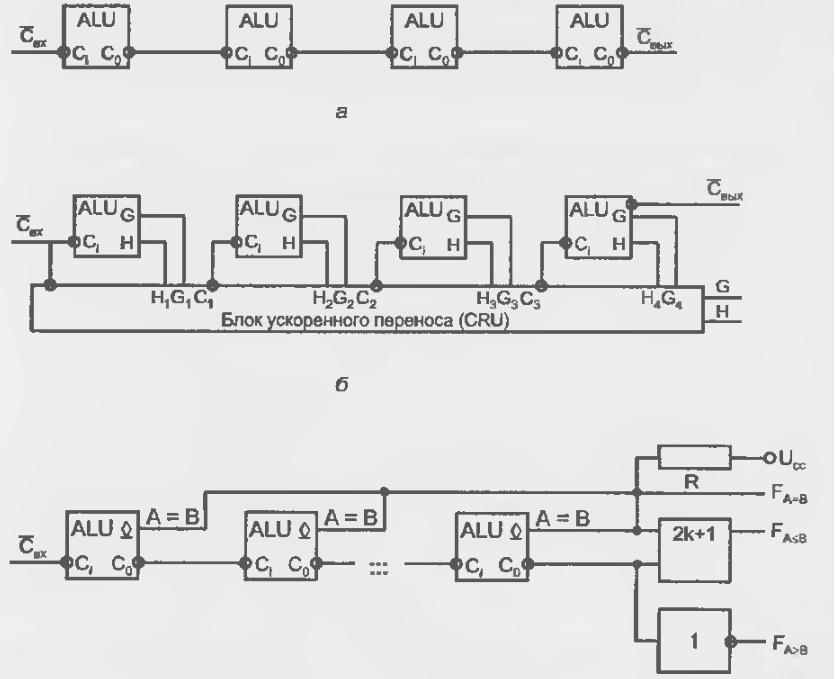

Обычно АЛУ четырехразрядны и для наращивания разрядности объединяются с формированием последовательных или параллельных переносов. Логические возможности АЛУ разных технологий (ТТЛШ, КМОП, ЭСЛ) сходны. В силу самодвойственности выполняемых операций условное обозначение и таблица истинности АЛУ встречаются в двух вариантах, отличающихся взаимно инверсными значениями переменных.

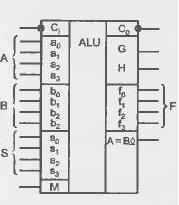

А

ЛУ (рис. 2.35) имеет входы операндов А и В, входы выбора операций S, вход переноса Ci и вход М (Моdе), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со — выходной перенос, а выход А = В есть выход сравнения на равенство с открытым коллектором.

ЛУ (рис. 2.35) имеет входы операндов А и В, входы выбора операций S, вход переноса Ci и вход М (Моdе), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со — выходной перенос, а выход А = В есть выход сравнения на равенство с открытым коллектором.

Рис. 2.35. Условнее обозначение АЛУ

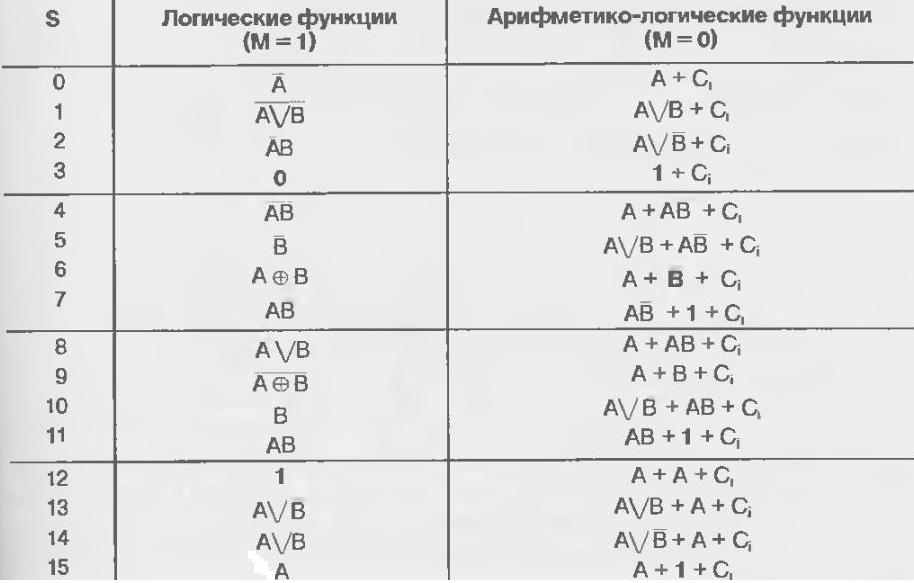

Перечень выполняемых АЛУ операций дан в табл. 2.13. Для краткости двоичные числа s3s2s1s0 представлены их десятичными эквивалентами. Под утолщенными обозначениями 1 и 0 следует понимать наборы 1111 и 0000, входной перенос поступает в младший разряд слова, т. е. равен 000Сi. При арифметических операциях учитываются межразрядные переносы.

Таблица 2.13.

Шестнадцать логических операций позволяют воспроизводить все функции двух переменных. В логико-арифметических операциях встречаются и логические и арифметические операции одновременно.

З

апись типа А\/В + АВ следует понимать так: вначале поразрядно выполняются операции инвертирования (В), логического сложения (А\/В) и умножения (АВ), а затем полученные указанным образом два четырехразрядных числа складываются арифметически.

апись типа А\/В + АВ следует понимать так: вначале поразрядно выполняются операции инвертирования (В), логического сложения (А\/В) и умножения (АВ), а затем полученные указанным образом два четырехразрядных числа складываются арифметически.При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных (рис. 2.36, а) или параллельных (рис. 2.36, б) переносов. В последнем случае совместно с АЛУ применяют микросхемы — блоки ускоренного переноса (СRU, Саrrу Unit), получающие от отдельных АЛУ функции генерации и прозрачности, а также входной перенос и вырабатывающие сигналы переноса

Рис. 2.36. Схемы наращивания АЛУ при последовательном (в) и параллельном (б) переносах и реализация функций компаратора для группы АЛУ (в)

Блок СКГ вырабатывает также функции генерации и прозрачности для всей группы обслуживаемых им АЛУ, что при необходимости позволяет организовать параллельный перенос на следующем уровне (между несколькими группами из четырех АЛУ).

На рис. 2.36, в показаны способы выработки сигналов сравнения слов для группы АЛУ. Выход сравнения на равенство выполняется по схеме монтажной логики для выходов типа ОК. Комбинируя сигнал равенства слов с сигналом переноса на выходе группы при работе АЛУ в режиме вычитания, легко получить функции FA≥B и FA≤B. Если А < В, то при вычитании возникает заем из старшего разряда и FA≤B = 1. Если заем отсутствует (А>В), то подучим FA≥B = 1.

10.2. Матричные умножители

Микросхемы множительных устройств появились в 1980-х годах, когда достигнутый уровень интеграции позволил разместить на одном кристалле достаточно большое количество логических элементов.

Структура матричных умножителей тесно связана со структурой математических выражений, описывающих операцию умножения.

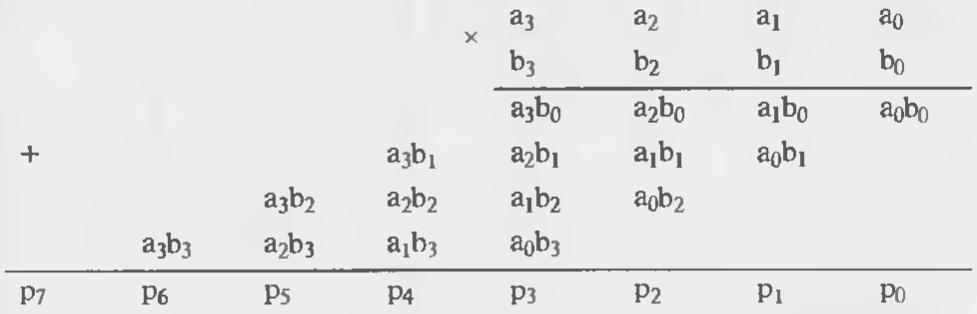

Пусть имеются два целых двоичных числа без знаков Аm = аm-1...ао и Вn = bn-1...bо, Их перемножение выполняется по известной схеме "умножения столбиком". Если числа четырехразрядные, т. е. m = n = 4, то

Произведение выражается числом Рm+n = Рm+n-1 Pm+n-2 … Ро.

Члены вида аibj, где i = 0... (m-1) и j = 0... (n-1) вырабатываются параллельно во времени конъюнкторами. Их сложение в столбцах, которое можно выполнять разными способами, составляет основную операцию для умножителя и определяет почти целиком время перемножения.

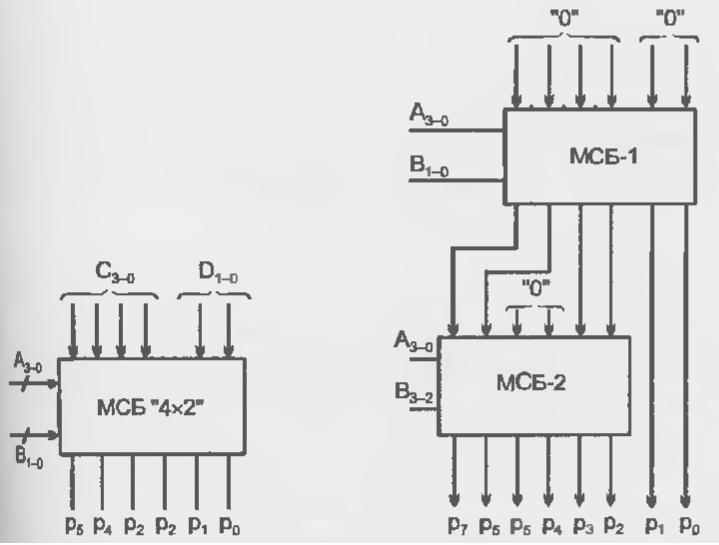

Матричные перемножители могут быть просто множительными блоками (МБ) или множительно-суммирующими (МСБ), последние обеспечивают удобство наращивания размерности умножителя.

МСБ реализует операцию Р = Аm х Вn + Сm + Dn, т. е. добавляет к произведению два слагаемых: одно разрядности m, совпадающей с разрядностью множимого, другое разрядности n, совпадающей с разрядностью множителя.

10.2.1. Множительно-суммирующие блоки

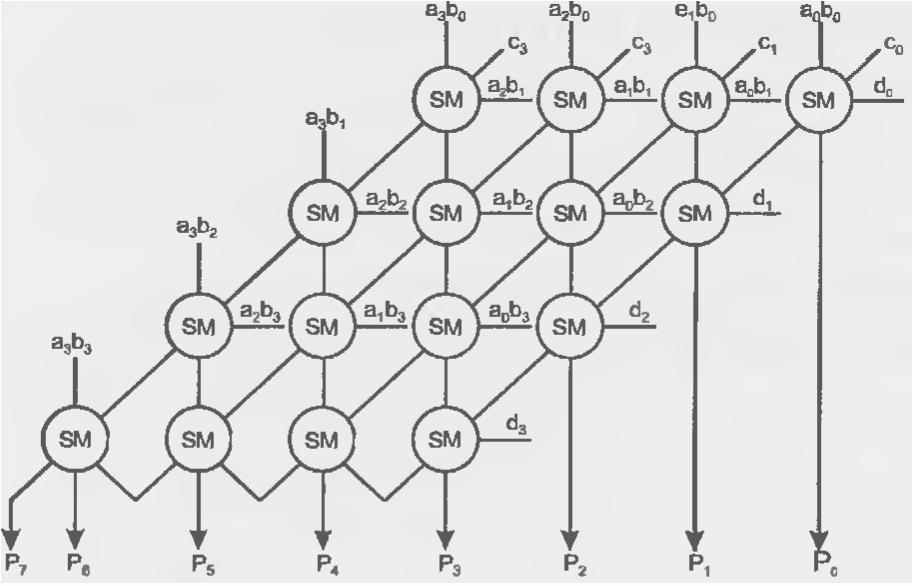

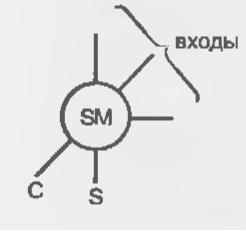

Множительно-суммирующий блок для четырехразрядных операндов без набора конъюнкторов, вырабатывающих члены вида аibj, показан на рис. 2.37, а, где для одноразрядного сумматора принято обозначение (рис. 2.37, б).

Для построения МСБ чисел равной разрядности потребовалось n2 конъюнкторов и n2 одноразрядных сумматоров.

Рис. 2.37. Схема множительно-суммирующего блока для четырехрезрядных сомножителей (а), обозначение одноразрядного сумматоре для данной схемы (б)

Рис. 2.38. К пояснению принципа наращивания размерности множительных устройств (в), условное обозначение множительно-суммирующего блока (б) и схема умножителя 4x4", построенная на множительно-суммирующих блоках "4 х 2" (в)

Максимальная длительность умножения — сумма задержек сигналов в конъюнкторах для выработки членов аibj и задержки в наиболее длинной цепочке передачи сигнала в матрице одноразрядных сумматоров, равной 2n - 1 (m + n - 1 в общем случае). Таким образом, tМРL = tк + (2n - 1)tsм,

Схема множительного блока отличается от схемы МСБ тем, что в ней отсутствуют сумматоры правой диагонали, т. к. при Сm = 0 и Dn = 0 они не требуются.

Построение умножителей большей размерности из умножителей меньшей размерности на основе МБ требует введения дополнительных схем, называемых "деревьями Уоллеса", которые имеются в некоторых зарубежных сериях. При использовании МСБ дополнительные схемы не требуются. Принцип наращивания размерности умножителя иллюстрируется на рис. 2.38, а на примере построения МРЬ "4 х 4" из МСБ "4 х 2". На поле частичных произведений выделены зоны, воспроизведение которых возможно на блоках размерности 4x2 (это две первые строки и две последние).

Перемножение в пределах зон дает частичные произведения р1 = Р51Р41РЗ1Р21Р11Р01 и Р2 = Р52Р42Р32Р22Р12Р02. Для получения конечного значения произведения эти частичные произведения нужно сложить с учетом их взаимного положения (сдвига одного относительно другого).

Схема, реализующая указанный принцип, изображена на рис. 2.38, в. В ней использовано условное обозначение МСБ (рис. 2.38, б). Для общности оба блока размерности 4x2 показаны как МСБ, хотя первый может быть просто множительным блоком, т. к. для него слагаемые С и D имеют нулевое значение.

10.2.2. Схемы ускоренного умножения

Для ускорения умножения разработан ряд алгоритмов, большой вклад в эти разработки внес Э. Бут (Е. Вооt). Рассмотрим процесс умножения по гак называемому модифицированному алгоритму Бута (умножение сразу на два разряда).

Из изложенного выше видно, что основную задержку в процесс выработки произведения вносит суммирование частичных произведений. Уменьшение их числа сократило бы время суммирования. К этому приводит алгоритм, основанный на следующих рассуждениях.

Пусть требуется вычислить произведение

Р = А х В = А х (b n-1 2 n - 1 + b n -2 2 n - 2 +…+b020). (a)

Непосредственное воспроизведение соотношения (а) связано с выработкой частичных произведений вида

(i = 0...n - 1). Число таких произведений равно разрядности множителя n.

(i = 0...n - 1). Число таких произведений равно разрядности множителя n.Выражение (а) можно видоизменить с помощью соотношения

, (б)

, (б)справедливость которого очевидна.

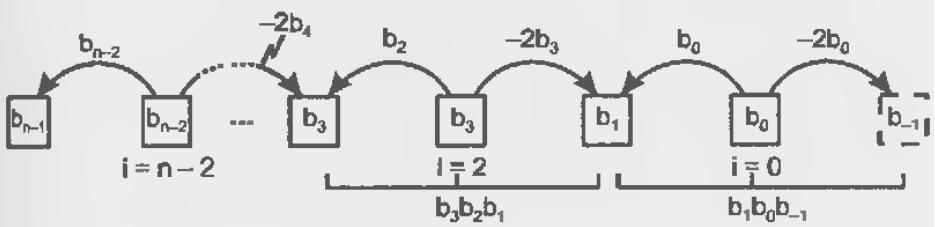

Это соотношение позволяет разреживать последовательность (спектр) степеней в сумме частичных произведений. Можно, например, исключить четные степени, как показано на рис. 2.39, а. Исключение четных (или нечетных) степеней не только изменяет значения оставшихся частичных произведений, но и сокращает их число примерно вдвое, что, в конечном счете, ускоряет выработку произведения. Для того чтобы "разнести по соседям" член со степенью

, расширим разрядную сетку, введя слагаемое

, расширим разрядную сетку, введя слагаемое  (нулевой разряд с номером -1).

(нулевой разряд с номером -1).Оставшиеся частичные произведения имеют вид

.

.Так как число частичных произведений уменьшилось примерно вдвое, при применении этого алгоритма говорят об умножении сразу на два разряда.

Рис- 2.39- К пояснению принципа быстрого умножения "срезу на два разряда" (в) и схема быстрого умножения (б)

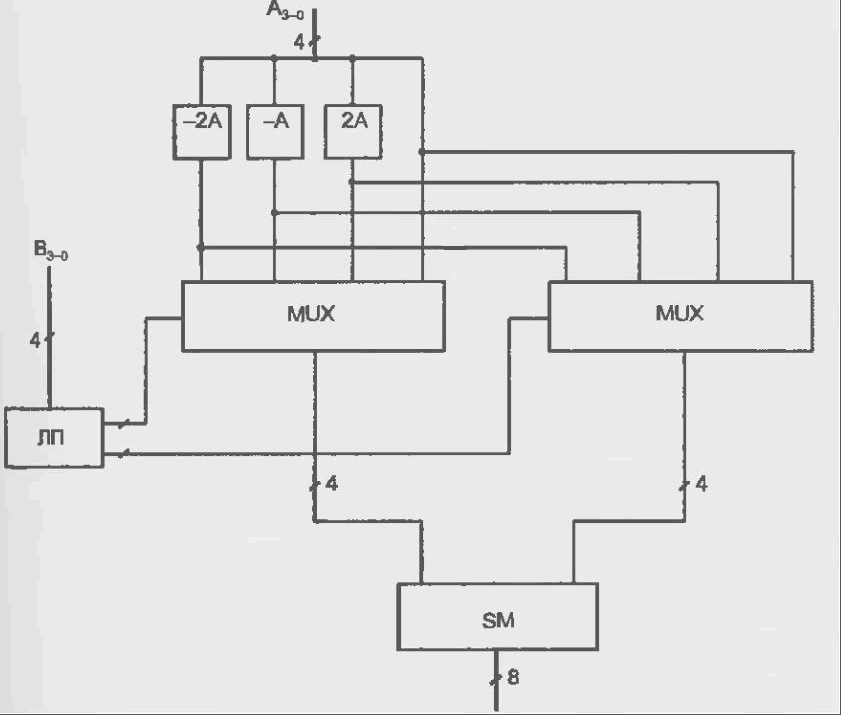

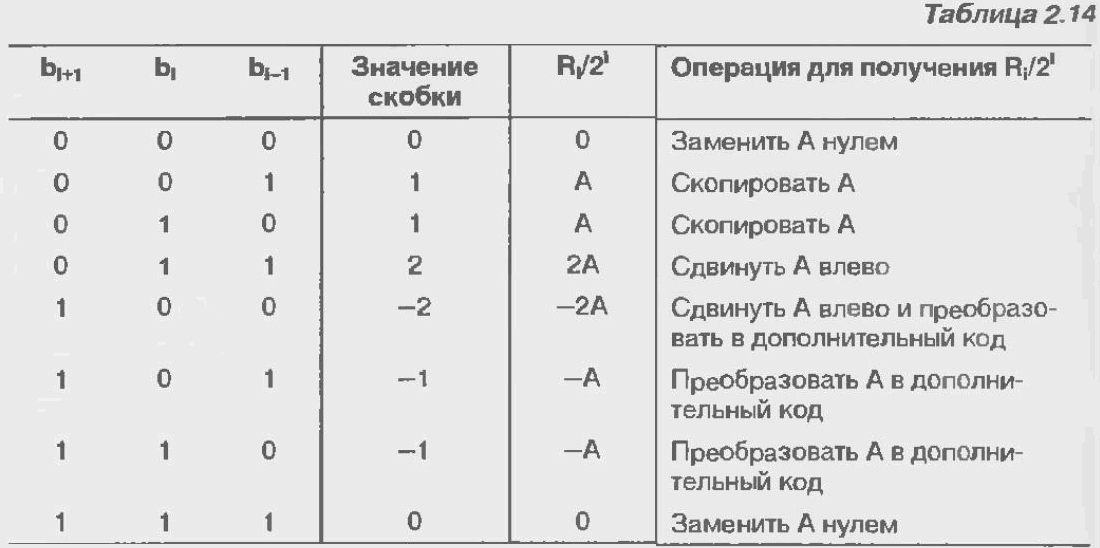

Для всех возможных сочетаний bi+1, bi , bi-1 можно составить таблицу (табл. 2.14) частичных произведений.

Модуль 4. Цифровые запоминающие устройства. Устройства сопряжения аналоговых и цифровых схем.

ТЕМА 14. Основные сведения. Основные структуры ЗУ

14.1 Виды памяти

Память компьютера – совокупность устройств для хранения информации. Вся память компьютера делиться на внутреннюю и внешнюю. Внутренняя делиться на оперативную, постоянную и кэш – память, а внешняя на жёсткие диски, гибкие диски, cd и dvd диски и магнитные ленты.

Основная память предназначена для хранения и оперативного обмена информацией с другими блоками компьютера. Делится на постоянное запоминающее устройство (ПЗУ) и оперативное запоминающее устройство (ОЗУ).

1. ПЗУ (ROM) служит для хранения неизменяемой программной и справочной информации. Постоянная память хранит в себе системные файлы, которые необходимы для загрузки операционной системы, проверки устройств компьютера, а так же файлы BIOS. Такая память называется ROM – (read only memory), Просмотр этой памяти невозможен так как эта память постоянная. Бывает два вида: однократно программируемые и многократно программирумая.

2. ОЗУ (Оперативная память) - это обязательная составная часть компьютера, предназначенная для хранения переменной информации и допускающая изменение своего содержимого в ходе выполнения процессором операций по обработке информации. Вся информация, вводимая в ЭВМ и возникающая в ходе ее работы, хранится в этой памяти. ОП представляет собой совокупность ячеек, разделенных на разряды для хранения в каждом бите информации. В любую ячейку памяти может быть записан некоторый набор нулей и единиц, образующий машинное слово - фиксированную, упорядоченную последовательность битов, рассматриваемую аппаратной частью компьютера как единое целое. Машинное слово может быть различной длины в зависимости от типа ЭВМ и определяет наибольшее число, которое может удерживаться в ячейке памяти. При байтовой архитектуре минимальной единицей измерения информации является байт, а машинное слово (команда процессора) может равняться 2, 4 или 8 байтам. Следовательно, можно говорить об объеме памяти компьютера, измерять его в килобайтах, мегабайтах, гигабайтах в соответствии с количеством байтовых ячеек как дискретных структурных единиц памяти.

Помимо дискретности структуры свойством оперативной памяти является ее адресуемость. Все ячейки памяти пронумерованы, номер ячейки - это ее адрес. Он позволяет отличать ячейки друг от друга, обращаться к любой ячейке, чтобы записать в нее новую информацию вместо старой или воспользоваться уже хранящейся в ячейке, для выполнения каких-то действий с ней. При таком считывании хранящееся в ячейке слово не изменяется. В оперативной памяти в виде последовательности машинных слов хранятся как данные, так и программы. Поскольку в любой момент времени доступ может осуществляться к произвольно выбранной ячейке, то этот вид памяти также называют памятью с произвольной выборкой - RAM (Random Access Memory).

Из микросхем памяти (RAM - Random Access Memory, память с произвольным доступом) используется два основных типа: статическая ( SRAM - Static RAM) и динамическая (DRAM - Dynamic RAM).

В статической памяти элементы (ячейки) построены на различных вариантах триггеров - схем с двумя устойчивыми состояниями. После записи бита в такую ячейку она может пребывать в этом состоянии сколь угодно долго - необходимо только наличие питания. При обращении к микросхеме статической памяти на нее подается полный адрес, который при помощи внутреннего дешифратора преобразуется в сигналы выборки конкретных ячеек. Ячейки статической памяти имеют малое время срабатывания (единицы-десятки наносекунд), однако микросхемы на их основе имеют низкую удельную плотность данных (порядка единиц Мбит на корпус) и высокое энергопотребление. Поэтому статическая память используется в основном в качестве буферной (кэш-память).

В динамической памяти ячейки построены на основе областей с накоплением зарядов, занимающих гораздо меньшую площадь, нежели триггеры, и практически не потребляющих энергии при хранении. При записи бита в такую ячейку в ней формируется электрический заряд, который сохраняется в течение нескольких миллисекунд; для постоянного сохранения заряда ячейки необходимо регенерировать - перезаписывать содержимое для восстановления зарядов. Ячейки микросхем динамической памяти организованы в виде прямоугольной (обычно - квадратной) матрицы; при обращении к микросхеме на ее входы вначале подается адрес строки матрицы, сопровождаемый сигналом RAS (Row Address Strobe - строб адреса строки), затем, через некоторое время - адрес столбца, сопровождаемый сигналом CAS (Column Address Strobe - строб адреса столбца). При каждом обращении к ячейке регенерируют все ячейки выбранной строки, поэтому для полной регенерации матрицы достаточно перебрать адреса строк. Ячейки динамической памяти имеют большее время срабатывания (десятки-сотни наносекунд), но большую удельную плотность (порядка десятков Мбит на корпус) и меньшее энергопотребление. Динамическая память используется в качестве основной.

Обычные виды SRAM и DRAM называют также асинхронными - потому, что установка адреса, подача управляющих сигналов и чтение-запись данных могут выполняться в произвольные моменты времени - необходимо только соблюдение временных соотношений между этими сигналами. В эти временные соотношения включены так называемые охранные интервалы, необходимые для стабилизации сигналов, которые не позволяют достичь теоретически возможного быстродействия памяти. Существуют также синхронные виды памяти, получающие внешний синхросигнал, к импульсам которого жестко привязаны моменты подачи адресов и обмена данными; помимо экономии времени на охранных интервалах, они позволяют более полно использовать внутреннюю конвейеризацию и блочный доступ.

FРM DRAM (Fast Рage Mode DRAM - динамическая память с быстрым страничным доступом) активно используется в последние несколько лет. Память со страничным доступом отличается от обычной динамической памяти тем, что после выбора строки матрицы и удержанием RAS допускает многократную установку адреса столбца, а также быструю регенерацию по схеме «CAS прежде RAS». Первое позволяет ускорить блочные передачи, когда весь блок данных или его часть находятся внутри одной строки матрицы, называемой в этой системе страницей, а второе - снизить накладные расходы на регенерацию памяти.

EDO (Extended Data Out - расширенное время удержания данных на выходе) фактически представляют собой обычные микросхемы FPM, на выходе которых установлены регистры-защелки данных. При страничном обмене такие микросхемы работают в режиме простого конвейера: удерживают на выходах данных содержимое последней выбранной ячейки, в то время как на их входы уже подается адрес следующей выбираемой ячейки. Это позволяет примерно на 15 % по сравнению с FPM ускорить процесс считывания последовательных массивов данных. При случайной адресации такая память ничем не отличается от обычной.

BEDO (Burst EDO - EDO с блочным доступом) - память на основе EDO, работающая не одиночными, а пакетными циклами чтения/записи. Современные процессоры, благодаря внутреннему и внешнему кэшированию команд и данных, обмениваются с основной памятью преимущественно блоками слов максимальной ширины. В случае памяти BEDO отпадает необходимость постоянной подачи последовательных адресов на входы микросхем с соблюдением необходимых временных задержек - достаточно стробировать переход к очередному слову отдельным сигналом.

SDRAM (Synchronous DRAM - синхронная динамическая память) - память с синхронным доступом, работающая быстрее обычной асинхронной (FРM/EDO/BEDO). Помимо синхронного метода доступа, SDRAM использует внутреннее разделение массива памяти на два независимых банка, что позволяет совмещать выборку из одного банка с установкой адреса в другом банке. SDRAM также поддерживает блочный обмен. Основная выгода от использования SDRAM состоит в поддержке последовательного доступа в синхронном режиме, где не требуется дополнительных тактов ожидания. При случайном доступе SDRAM работает практически с той же скоростью, что и FPM/EDO.

РВ SRAM (Pipelined Burst SRAM - статическая память с блочным конвейерным доступом) - разновидность синхронных SRAM с внутренней конвейеризацией, за счет которой примерно вдвое повышается скорость обмена блоками данных.

Алгоритм работы оперативной памяти:

- Включение компьютера загрузка файлов BIOS.

- Загрузка файлов системы

- Обработка программ, которые открывает пользователь

После выключения компьютера оперативная очищается. Является связкой между винчестером и процессором.

Винчестер

Винчестер – это жёсткий диск компьютера. На нём храниться вся информация. Первая модель жёсткого диска имела 30 дорожек по 30 сектаров – это совпало с калибром ружья “Винчестер”. Сейчас используются такие модули подключения: IDE, MiniIDE, SATA I, SATA II.

IDE и MiniIDE подключаются через 40-pi слот, такой же слот используется для CD-rom. Но MiniIDE используется в ноутбуках, и поэтому он намного компактнее и дороже, чем его собрат IDE.

Но сейчас на рынке появились новые винчестеры: SATA I и SATA II. Эти винчестеры стоят в несколько раз дороже, чем IDE.

Но они имеют большую скорость записи, и с помощью пары винчестеров можно создать RAID массив. Массивы бывают разные

1. Raid 0 (striping) объединяет два диска в одну метку тома, тем самым увеличивает скорость записи и объем.

2. Raid 1 (data mirroring) делает точную копию одного винчестера на другом, тем самым увеличивается безопасность сохранения информации

3. Raid 0+1 объединяет в себе Raid 1 и Raid 0, но требует 4 винчестера

4. JBOD позволяет установить операционную систему на SATA диск (ни в одном другом режиме массив RAID не позволяет устанавливать операционную систему на диск SATA).

Примерно такие же массивы существуют в SATA II.

Cache - память

Одним из способов повышения быстродействия МП является использование кэш-памяти (Cache - запас), расположенной между центральным процессором и ОЗУ. Cache - самая быстродействующая часть оперативной памяти, к которой процессор обращается напрямую, а не через системную шину. Она имеет относительно небольшой объем и хранит в себе наиболее часто используемые участки оперативной памяти, а так как время доступа к кэш-памяти в несколько раз меньше чем к оперативной, то среднее время доступа к памяти уменьшается.

Физически Cache представляет собой часть устройства процессора или отдельные микросхемы памяти. В современных компьютерах используются два уровня Cache'а: L1 (самый быстрый, но небольшого размера, первый уровень) внутри процессора, и L2 (второй уровень), который может находиться как внутри (Celeron "А"), так и снаружи (Pentium).

Функционально кэш-память предназначена для согласования скорости работы сравнительно медленных устройств с относительно быстрым МП

Cd и floppy.

Оптические диски – это диски, на поверхности которых информация записана прожигом от лазерного луча. Эти диски, покрыты тонким напылением алюминия. Имеет одну дорожку в форме спирали. На лазерном диске впадины поглащают луч, то это воспринимается как 0, если отражают, то 1

Floppy – гибкий магнитный диск. Весь магнитный диск делится на сектора и дорожки. Поверхность диска покрыта магнитным слоем.

Флэш-память

Следует признать тот факт, что цифровые технологии все шире входят в нашу жизнь. За последние пять лет появилось множество различных МРЗ-плееров, камер, карманных компьютеров и другой цифровой аппаратуры. А все это стало возможным благодаря созданию компактных и мощных процессоров. Однако при покупке какого-либо устройства, помещающегося в кармане, не стоит ориентироваться лишь на процессорную мощность, поскольку в списке приоритетов она стоит далеко не на первом месте.

При выборе портативных устройств самое важное, на мой взгляд - время автономной работы при разумных массе и размерах элемента питания. Во многом это от памяти, которая определяет объем сохраненного материала, и, продолжительность работы без подзарядки аккумуляторов. Возможность хранения информации в карманных устройствах ограничивается скромными энергоресурсами Память, обычно используемая в ОЗУ компьютеров, требует постоянной подачи напряжения. Дисковые накопители могут сохранять информацию и без непрерывной подачи электричества, зато при записи и считывании данных тратят его за троих. Хорошим выходом оказалась флэш-память, не разряжающаяся самопроизвольно. Носители на ее основе называются твердотельными, поскольку не имеют движущихся частей. К сожалению, флэш-память - дорогое удовольствие: средняя стоимость ее мегабайта составляет 2 доллара, что в восемь раз выше, чем у SDRAM, не говоря уж о жестких дисках. А вот отсутствие движущихся частей повышает надежность флэш-памяти: стандартные рабочие перегрузки равняются 15 g, а кратковременные могут достигать 2000 g, т. е. теоретически карта должна превосходно работать при максимально возможных космических перегрузках, и выдержать падения с трёхметровой высоты. Причем в таких условиях гарантируется функционирование карты до 100 лет.

Многие производители вычислительной техники видят память будущего исключительно твердотелой. Следствием этого стало практически одновременное появление на рынке комплектующих нескольких стандартов флэш-памяти.

Compact Flash

Этот стандарт был предложен в 1994 г. компанией SanDisk, а в 1995 г. его стала продвигать ассоциация CFA, созданная такими крупными компаниями, как Hewlett-Packard, Hitachi, IBM, Motorola и др. Сейчас в нее входят уже более 165 фирм.

Модули памяти Compact Flash (CF) представляют собой модификацию PC-карт. Правда, они меньше по объему и имеют всего 50 контактов вместо 68, но их можно подключать в разъемы PCMCIA через пассивный переходник без дополнительного ПО. Устройства CF делятся на два типа, внешне различающихся толщиной. Размеры CF типа I - 36,4x42,8x3,3 мм, a CF типа II имеют ту же площадь, но их толщина больше - 5 мм. Карты типа II несовместимы с разъемами типа I, тогда как для карт типа I подходят порты обоих видов.

Для работы модули CF используют напряжение 3,3 или 5 В и ток до 100 мА. В итоге, по утверждению производителей, они потребляют в 20 раз меньше энергии, нежели стандартные жесткие диски, так что не нужно часто заменять батарейки.

Максимальная емкость карт типа I составляет 256 Мбайт (у компаний PQI и Delkin), а карт типа II - 512 Мбайт (у фирмы SiliconTech).Причём цена экспоненциально зависит от размера модуля. Например, SiliconTech за свою полугигабайтную микросхему типа II требует 1608 долл., а наиболее выгодные по критерию "доллар за мегабайт" 128- и 256-Мбайтные карты стоят от 205 и 420 долл. соответственно. Память типа I дороже, чем типа II, так как у нее то же число микросхем надо вмещать в меньший объем.

Стандарт Compact Flash уже довольно давно представлен на рынке, поэтому при покупке камеры, работающей с картами CF, можно не сомневаться, что удастся найти совместимый по памяти МРЗ-плеер и не придется иметь дело с картами разных видов. Для совмещения карты данного типа с ноутбуком достаточно купить за 10 долл. переходник для разъема PCMCIA.

SmartMedia

Стандарт SmartMedia, или SSFDC был разработан в 1995 г. компанией Toshiba, а его продвижением занимается организация SSFDC Forum, в рядах которой немало известных компаний. SSFDC (Solid State Floppy Disk Card) можно перевести как "твердотельная дискета". Следует отметить, что многие производители делают флэш-карты сразу трех основных типов: Compact Flash, SmartMedia и MultiMediaCard.

В отличие от Compact Flash, карты SmartMedia (SM) не снабжены встроенным контроллером, что, по замыслу создателей, должно снижать их стоимость. Кроме того, SM имеют меньшие размеры (37x45x1,76 мм) и массу (до 2 г). По популярности SM спорят с CF, а вместе с ним оба этих стандарта охватывают более половины рынка флэш-карт.

Рабочие напряжения у SM такие же, как и у CF, но обычно используется 3,3 В. Максимальная емкость карт, объявленная производителями, в частности компаниями ЕМТЕС и Delkin, составляет 128 Мбайт, и стоит около 250 долл.. Из-за отсутствия внутреннего контроллера для работы с этими картами невозможно применить пассивный переходник, а считыватели для них стоят около 50 долл. SM обычно используются в цифровых камерах и МРЗ-плеерах, а вот в КПК - практически никогда.

MultiMediaCard

Этот стандарт предложили в 1997 г. компании Infineon Technologies (подразделение Siemens) и SanDisk, а продвигает его ассоциация ММСА, состоящая из 80 компаний (Infineon, Nokia, Ericsson, Hitachi, SanDisk, Motorola и др.).

Карты ММС еще меньше, чем рассмотренные выше, - 32x24x1,4 мм, да и весят они всего 1,5 г. Поэтому и предназначены в основном для ультрапортативных устройств, особенно актуальны они в КПК, сотовых телефонах и электронных записных книжках.

Эти модули памяти работают при напряжениях 3,3 или 2,7 В и токе до 35 мА, что и обусловливает низкое энергопотребление.

Максимальная емкость ММС, представленных на Российском рынке, составляет 64 Мбайт, и стоит около 130 долл. Этот же объем оказался наиболее выгодным по соотношению "доллар за мегабайт".

Сейчас стандарт ММС уже достаточно популярен, и примером тому может служить его поддержка КПК Cassiopea EM-500

Secure Digital

Компания Matsushita Electronic (известная под торговой маркой Panasonic) вместе с SanDisk и Toshiba разработали стандарт, в котором учли последние веяния времени. Чтобы предотвратить несанкционированное копирование, носители Secure Digital (SD) снабжены средствами защиты от незаконного копирования.

Размеры карт - 32x24x2,1 мм. Разъемы для них совместимы с модулями ММС. Пока стандарт только начал завоевывать рынок, но производители обещают уже в этом году довести емкость карт SD до 256 Мбайт.

Уже анонсирован выпуск в формате SD модемов и других периферийных устройств. А возможность защиты авторских прав позволила продавцам выпустить в продажу книги и песни на этих носителях.

Memory Stick

Некогда Sony заставила компьютерную индустрию выбрать в качестве сменных носителей свои 3,5-дюймовые флоппи-дисководы, а теперь она решила позаботиться о своих позициях и на аудиорынке, для чего разработала новый стандарт флэш-карт Memory Stick

(MS). Эти 10-контактные устройства . размерами 21,5x50x2,8 мм и массой 4 г стали опорой цифровой империи Sony, которая устанавливает их в свои цифровые плееры, фотоаппараты и видеокамеры, также игрушки и другие устройства.

В апреле этого (2001) года была выпущена новая, 128-Мбайт модель MS стоимостью 249 долл. Также существует разновидность MS MagicGate (с защитой от несанкционированного копирования), предназначенная для плееров. В настоящее время стандарт Memory Stick поддерживается почти исключительно устройствами производства концерна Sony. Из-за такой не универсальности они и не получили широкого распространения.

Считыватели

Для быстрого и удобного обмена информацией между флэш-картами и компьютером используются считыватели. Они различаются способом и интерфейсом подключения к ПК, а также скоростными характеристиками.

Внешние считыватели

Эти устройства могут подключаться через USB, LPT, и FireWire(IEEE1394) интерфейсы. Они отличаются друг от друга только скоростными показателями. Скорость самого медленного из них – подключаемого через параллельный порт, может достигать 0,34Мбайт/с – при записи, и 0,62Мбайт/с – при чтение данных. У моделей с универсальным последовательным портом эти показатели составляют 0,46 и 0,77Мбайт/с. А вот FireWire считыватель оставил далеко позади всех своих конкурентов. Устройства с данным интерфейсом способны “запоминать” информацию на скорости до 0,7Мбайт/с, и выдавать её в три раза быстрее - 2,1Мбайт/с. Также большим плюсом является способность некоторых моделей работать ни с одним, а с несколькими стандартами флэш-памяти.

Внутренние считыватели

Подобные устройства вставляются в 3,5-дюймовый отсек системного блока, и подключаются к ATA интерфейсу. К достоинствам считывателей данного класса относятся высокая скорость(0,52 Мбайт/с и 1Мбайт/с) и отсутствие посторонних устройств на столе. А к недостаткам – то он занимает отсек системного блока, и IDE канал.

Считыватели - переходники

Этот класс устройств позволяет подключить флэш-карту к компьютеру через дисковод. При этом используется переходник внешне похожий на 3,5-дюймовую дискету(или PC-карту для ноутбуков). Карта памяти вставляется в адаптер, который впоследствии размещается в дисководе. Использование PCMCIA-адаптеров даёт неплохие результаты, скорость передачи достигает 1Мбайт/с. А при использовании флоппи-дисковода она недотягивает и до отметки 36 Кбайт/с. И это при том что FDD(FlashPath)-адаптер стоит дороже любого другого считывателя.

ТЕМА 15. Постоянные запоминающие устройства (ПЗУ). Структура ПЗУ с прожиганием. Программирование ПЗУ. ПЗУ с УФ стиранием. ПЗУ с электрическим стиранием. Оперативные запоминающие устройства (ОЗУ). Статические ОЗУ. Динамические ОЗУ.

15.1 Постоянные запоминающие устройства (ПЗУ)

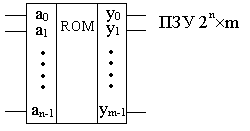

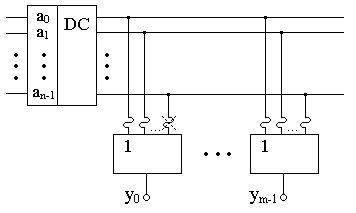

ПЗУ представляет собой чисто комбинационную схему, имеющую n адресных входов и m выходов.

Рисунок 4.1 – Схемное обозначение ПЗУ

ПЗУ организуются по двухъярусной структуре:

2) C помощью схем “или” собираются все нужные конъюнкции.

Рисунок 4.2 – Структура ПЗУ

Работа схемы: если все плавкие перемычки целы, то при выборе любого адреса на входы всех дизъюнкторов будет поступать хотя бы по одной единице, поэтому y0 = y1=···= ym-1=1.

Для занесения в схему какой-либо информации некоторые перемычки пережигаются (ПЗУ с прожиганием), тогда на некоторых дизъюнкторах на все входы поступают “0” и на выход подается “0”.

15.1.1 Структура ПЗУ с прожиганием.

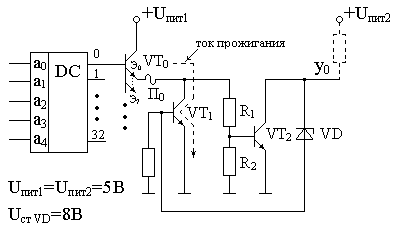

Примером такой ПЗУ является К155РЕ3 .ЕЕ структура 328 (32 слова по 8 битов каждое).

Рисунок 4.3 –ПЗУ К155РЕ3

Если перемычка П0 – цела, то при выборе транзистора VT0 (по адресу 00000 открывается “0” выход дешифратора), тогда ток этого транзистора создает через делитель R1R2 на базе VT2 некоторый потенциал, VT2 открывается, и на выходе y0 появится “0”. VT1 в это время закрыт, т.к. потенциал его базы равен 0. Чтобы на выходе у0 получить “1” необходимо перемычку П0 сжечь. Для этого Uпит2 повышают до уровня 10-11 В; открывается стабилитрон VD, на базе VT1 появляется положительный потенциал, транзистор VT1 открывается и его ток сжигает перемычку. Теперь на базе VT2 не будет положительного потенциала, VT2 – закрыт, следовательно у0 = 1.

Длительность прожигающего импульса выбирается в интервале 520мс.

15.1.2 Программируемые ПЗУ (ППЗУ).

ППЗУ выпускаются заводом-изготовителем в "чистом виде", т.е. по всем адресам записаны"0". Программирование ППЗУ осуществляется пользователем ППЗУ на специальной установке, называемой программатором. В ППЗУ можно записать (его программировать) информацию только один раз. Изменить записанную информацию или исправить ее нельзя. ППЗУ нашли широкое применение в ЭВМ для хранения запускающих программ. Они обладают большим быстродействием, чем репрограммируемые ПЗУ (РПЗУ).

Репрограммируемые ПЗУ позволяют, при необходимости, перепрограммировать ПЗУ, т.е. стереть ранее записанную информацию и записать новую.

По способу стирания ранее записанной информации РПЗУ бывают с ультрафиолетовым (ультрафиолетовыми лучами) и электрическим стиранием. РПЗУ позволяют десятки (некоторые до 1000) раз перепрограммировать и сохранять записанную информацию десятки и сотни тысяч часов. Быстродействие РПЗУ несколько хуже быстродействия ППЗУ.

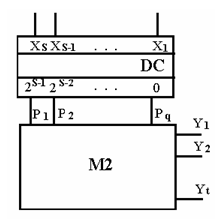

Независимо от типа и способа стирания ПЗУ имеют структуру, приведенную на рис. 2.37.

Рисунок 4.4 –Структурная схема постоянного запоминающего устройства

Структурная схема ПЗУ содержит дешифратор на S входов и 2S -выходов, а также матрицу М2.

Информационная емкость ПЗУ определяется как Sпзу = 2S, где S- количество входов X. В этом определении емкости (объема) памяти не учтено количество выходов Y(t). Обычно число t бывает 4, 8, и 16 (полубайтовая, байтовая и двухбайтовая организация памяти). "Битовая" емкость ПЗУ определяется как

Sпзу (бит) = 2S t (бит).

Промышленностью выпускаются ПЗУ с объемом памяти (информационной емкостью) на 2 кбайт, 4 кбайт,16 кбайт,32 кбайт и т.д., где к=1024; 1байт=8бит.

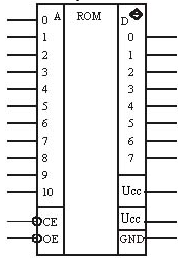

На функциональных и принципиальных схемах РПЗУ с ультрафиолетовым стиранием изображается так, как показано на рис. 2.38.

Рисунок 4.5 –Схемное обозначение РПЗУ К573РФ2, К573РФ5 с ультрафиолетовым стиранием:

А - адресные входы; D – информационные выходы. Uce – вход подачи напряжения записи (в режиме хранения на этот вход подается Ucc); Ucc – вывод для подачи напряжения питания. СЕ и ОЕ –входы управления состоянием выводов, если СЕ=ОЕ=1, входы D имеют высокоимпедансное состояние. При СЕ=ОЕ=0 вывод информации разрешен.

Микросхема РПЗУ К573РФ2 (РФ5) имеет одиннадцатиразрядный дешифратор, выходы которого соединены с восьмиразрядной матрицей М2. В процессе записи выходные элементы РПЗУ находятся в режиме приема информации через выводы D0 . . . D7 (на входе “ОЕ“ уровень “1”). В режиме считывания записанной информации выводы “Uce” и “Ucc” объединяются, и на них подается напряжение питания +5В.

15.1.3 ПЗУ с УФ стиранием

ПЗУ со стиранием информации ультрафиолетовым излучением в настоящее время наиболее широко используются в микропроцессорных системах. В БИС таких ПЗУ каждый бит хранимой информации отображается состоянием соответствующего МОП-транзистора с плавающим затвором (у него нет наружного вывода для подключения). Затворы транзисторов при программировании «1» заряжаются лавинной инжекцией, т.е. обратимым пробоем изолирующего слоя, окружающего затвор под действием электрического импульса напряжением 18 – 26 В. Заряд, накопленный в затворе, может сохраняться очень долго из-за высокого качества изолирующего слоя. Так, например, для ППЗУ серии К573 гарантируется сохранение информации не менее 15 – 25 тысяч часов во включенном состоянии и до 100 тысяч часов (более 10 лет) — в выключенном.

15.1.4 ПЗУ с электрическим стиранием

Они позволяют производить как запись, так и стирание (или перезапись) информации с помощью электрических сигналов. Для построения таких ППЗУ применяются структуры с лавинной инжекцией заряда, аналогичные тем, на которых строятся ППЗУ с УФ стиранием, но с дополнительными управляющими затворами, размещаемыми над плавающими затворами. Подача напряжения на управляющий затвор приводит к рассасыванию заряда за счет туннелирования носителей сквозь изолирующий слой и стиранию информации. По этой технологии изготовляют микросхемы К573РР2.

Достоинства ППЗУ с электрическим стиранием: высокая скорость перезаписи информации и значительное допустимое число циклов перезаписи — не менее 10000.

15.2 ОЗУ

15.2.1 Статические ОЗУ

Рассматриваемые типы запоминающих устройств (ЗУ) применяются в компьютерах для хранения информации, которая изменяется в процессе вычислений, производимых в соответствии с программой, и называются оперативными (ОЗУ). Информация, записанная в них, разрушается при отключении питания.

Главной частью ЗУ является накопитель, состоящий из триггеров

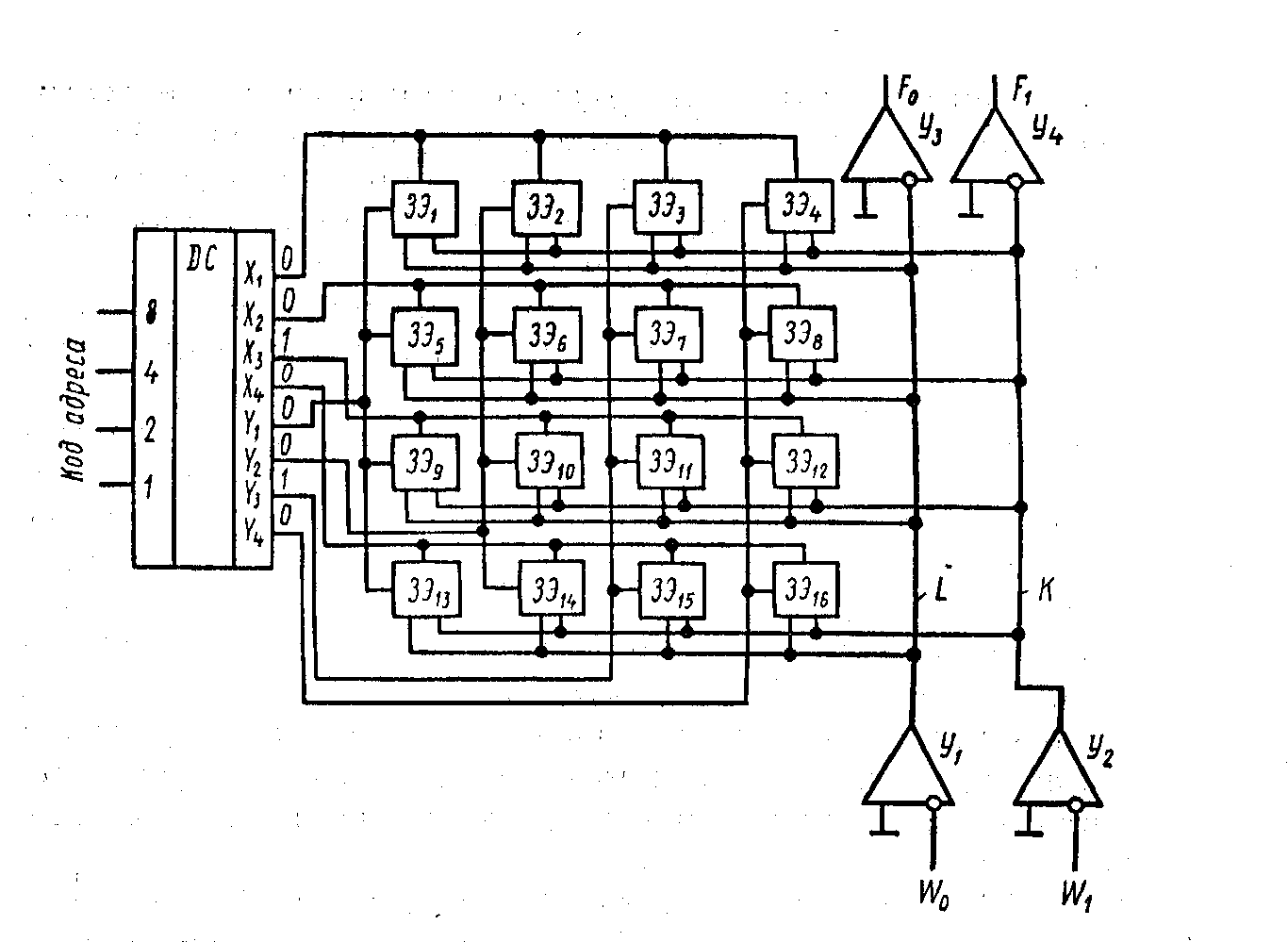

Рисунок 4.6 – Матрица ЗУ

Накопитель двухкоордииатпого ЗУ состоит из нескольких матриц (Рисунок 4.6), количество которых определяется числом разрядов записываемого слова. Запоминающие элементы(ЗЭ) одной матрицы расположены на пересечении адресных шин Х строк и Y столбцов, имеют одну общую для всех элементов разрядную шину. В ЗЭ одной матрицы записываются одноименные разряды всех слов, а каждое слово — в идентично расположенные запоминающие элементы ЗЭi, всех матриц, составляющие ячейку памяти. Таким образом, в двухкоординатное четырехматричное ЗУ, матрицы которого содержат по 16 запоминающих элементов (рис. 4), можно записать 16 четырехразрядных слов.

15.2.2 Динамические ОЗУ

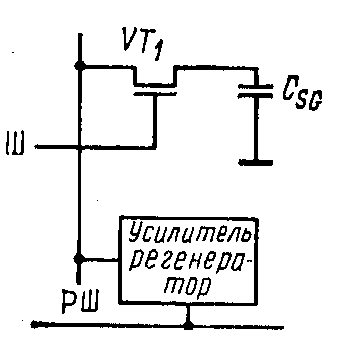

В них запоминающий элемент содержит только один транзисторн. (рис.15-5)

Рисунок 4.7 – Элемент динамической ОЗУ

Информация в таком элементе хранится в виде заряда на запоминающем конденсаторе, обкладками которого являются области стока МОП-транзистора и подложки. Запись и считывание ннформаини производятся путем открывания транзистора по затвору и подключения тем самым заноминаюшей емкости к схеме усилителя-регенератора. Последний, по существу является триггерным элементом ,который В зависимости от предварительной подготовки или принимает (считывает) цнформацию из емкоетной запоминающец ячейки, устаиавливаясь при этом в состояние 0 пли 1,или, наоборот, в режиме записи соотвегствующим образом заряжает ячейку, будучи иредварительно установленным в 0 нли 1

В режиме чтения триггер усилителя — регенератора в иачале специальным управляющим сигналом устанавливается в неустойчивое равновесное состояние, из которого при подключении к нему запоминающей емкости

он переключается в 0 или I. При этом в начале он потребляет часть заряда, а затем при установке в усгойчивое состояние , возвращает его ячейке осуществляя таким образом регенерацию ее состояния. В режиме хранения информации необходимо периодически производить регенерацию для компенсации естественных утечек заряда.максимальный период цикла регенерации для каждой из ячеек обычно составляет 1 — 2 мс.