1. Основные определения

| Вид материала | Задача |

- Тема: Основные понятия и определения, 164.71kb.

- Надежность в технике основные понятия. Термины и определения гост 27. 002-89 государственный, 583.36kb.

- Гост 60-2003 издания. Основные виды. Термины и определения, 62.99kb.

- Расторгуев С. П. Информационная война, 5412.32kb.

- Сибид. Библиографическая деятельность. Основные термины и определения сибид. Библиографическое, 76.18kb.

- Контрольные вопросы по курсу бжд для групп рк основные определения: биосфера, окружающая, 181.53kb.

- Тема: Основные понятия и определения, 121.92kb.

- 1. Функции нескольких переменных. Основные понятия. Область определения, 13.11kb.

- Федеральный закон, 690.72kb.

- Основные термины и определения 02 техническая подготовка производства (тпп), 31.83kb.

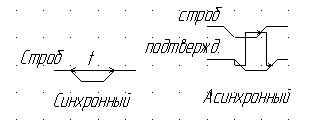

8. Типы обмена информацией – синхронный, асинхронный, асинхронно-синхронный (достоинства и недостатки)

Большое значение имеет то, как процессор заканчивает обмен в пределах цикла, и в какой момент он снимает строб обмена. Возможны 2 варианта: - при асинхронном обмене процессор заканчивает обмен только тогда, когда устройство- исполнитель подтверждает выполнение операции специальным сигналом – handshake (режим "рукопожатия"); - при синхронном обмене процессор заканчивает обмен данными самостоятельно через установленный временной интервал без учета интересов устройства-исполнителя.

Достоинства синхронного обмена: простой протокол обмена, малое количество управляемых сигналов.

Недостатки синхронного обмена: отсутствие гарантии, что исполнитель выполнит требуемую операцию и высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена: надежная пересылка данных, возможность работы с исполнителями разного быстродействия.

Недостаток асинхронного обмена: необходимость сигнала подтверждения.

9. Методы инициации обмена

1. Право инициировать обмен представляется только одному модулю системы (чаще микропроцессору), который ведет периодический опрос всех остальных модулей системы, ища готового к обмену – поллинг.

Метод не эффективен для многомодульных систем. Используется, когда вероятность готовности модуля к обмену высока.

Достоинства: простота технической реализации.

2. Право инициировать обмен предоставляется нескольким модулям системы. Эффективность работы резко возрастает, однако микропроцессор должен иметь средства восприятия запроса от нескольких модулей, т.е. обладать средствами прерывания.

Средства, реализующие обмен по прерыванию, называют подсистемами прерываний. Обычно они распределены в нескольких модулях системы.

3. При обслуживании любого запроса на прерывании основным звеном системы является микропроцессор, управляющий шиной адреса и шиной данных и вырабатывающий управляющие сигналы для периферийных микросхем. Однако в некоторых случаях, когда необходимо пересылать между внешними устройствами и памятью большие блоки информации, использование процессора становится неэффективным, и используют метод прямого доступа к памяти. При прямом доступе к памяти управление системой передается специальному модулю. Все сигналы на выводах микропроцессора, за исключением некоторых управляющих выводов, переводится в 3-тье состояние, говорят, что процессор переходит в состояние захвата HOLD. Обменом управляет специализированный контроллер прямого доступа к памяти, и информация подается к внешнему устройству, минуя микропроцессор. Средства прямого доступа к памяти комплектуются отдельными модулями памяти.

Достоинство прямого доступа к памяти: высокая скорость обмена

Недостаток прямого доступа к памяти: система теряет управляемость, т.к. процессор отключается.

4. Метод, при котором процессор отключается полностью, называется методом полного занятия цикла. Альтернативой является метод частичного занятия цикла. Прямой доступ к памяти реализуется в те моменты, когда процессор занят внутренними вычислительными операциями.

Достоинство: полная управляемость системы

Недостаток: малая, по сравнению с полным циклом, скорость.

10. Средства, реализующие обмен по прерыванию. Прерывания – внутренние, программные, внешние.

Средства, реализующие обмен по прерыванию, называют подсистемами прерываний. Обычно они распределены в нескольких модулях системы.

Различают средства прерывания:

1. внутренние прерывания – происходит в результате событий, локализованных внутри модулей системы. Например, прерывание таймера.

Функции внутренних прерываний: распознавание события, сохранение текущего процесса, загрузка счетчика команд начальным адресом прерывания.

2. программные прерывания – инициируются специальными командами внутри программы. После этого в специальной области памяти (стек) сохраняется состояние процесса, обеспечивается загрузка счетчика команд новым содержимым (например, команда CALL ADR).

Восстановление прерванного процесса может быть с помощью специальных команд, так и автоматически.

3. Функции средств, обслуживающих внешние прерывания: 1)фиксация запросов от внешних устройств 2)определение запроса, принадлежащего к обслуживанию 3)идентификация источника, который послал запрос в случае запросов от внешних источников 4)анализ текущего процесса на предмет прерывания 5)запоминание состояния текущего процесса 6)передача управления подпрограмме обслуживания данного запроса 7)возврат, т.е. восстановление состояния прерванного процесса и передача ему управления.

11. Классификация прерываний по обслуживанию (маскируемые, приоритетные, уровневые, векторные)

В зависимости от способа реализации каждой из перечисленных функций подсистемы прерываний могут классифицироваться:

А) с маскированием входов запроса и без маскирования. Под маскированием понимается запрет какого-то запроса на прерывание.

Б) приоритетные и безприоритетные. Приоритетные – прерывание с меньшим приоритетом может быть реализовано запросом с большим приоритетом. Безприоритетные – обслуживаются в порядке очереди.

В) одноуровневые и многоуровневые. Многоуровневый запрос может быть прерван более высокоуровневым запросом (вложенность прерываний)

Г) динамически маскируемые системы. Имеется возможность динамически запрещать применять приоритеты по результатам обслуживания. Имеется возможность прерывать обслуживание запроса от какого-либо источника запросом с меньшим приоритетом.

Д) безвекторные и векторные прерывания. Безвекторные прерывания – передача управления происходит на 1 фиксированный адрес не зависимо от того, кто послал запрос. В таких системах используются обзорные прерывания, т.е. после фиксации процесса процессор должен определить, кто послал запрос. Векторные прерывания – запрос от любого источника обслуживается своей подпрограммой прерывания с конкретным адресом (вектором).

12. Контроллер прерываний К580ВН59 – описание функционирования.

- Контроллер прерываний преобразует аппаратные прерывания системной магистрали в аппаратные прерывания процессора и задает адреса векторов прерывания. Все режимы функционирования контроллера прерываний задаются программно процессором перед началом работы.

Контроллеры радиальных прерываний в первых компьютерах выполнялись на микросхемах i8259, каждая из которых имела 8 входов запроса прерываний. В IBM PC AT применялось две таких микросхемы, в результате чего количество входов запросов прерываний увеличилось до 15. Режимы работы контроллеров прерываний определяются процессором путем записи соответствующих управляющих кодов по адресам в пространстве устройств ввода/вывода.

При поступлении запроса прерывания на один из входов IRQ и удовлетворении этого запроса контроллер прерываний вырабатывает выходной сигнал запроса прерывания, поступающий на процессор. В ответ на это процессор запрашивает контроллер о том, прерывание с каким адресом вектора необходимо обслужить. Всего прерываний может быть 256 (от 00 до FF). Номер прерывания, полученный от контроллера, процессор умножает на 4 и получает, таким образом, адрес памяти, где хранится адрес начала программы обработки прерываний (вектор прерывания). Присваивание каждому из каналов IRQ своего номера процессор осуществляет на этапе инициализации контроллера.

Контроллер прерываний может выполнять следующий набор операций:

- маскирование запросов на прерывание, то есть временное запрещение реакции на них;

- установка приоритетов запросов по различным входам, то есть разрешение конфликтов при одновременном приходе нескольких запросов на прерывание;

- работа в качестве основного контролера (Master) или подчиненного (Slave).

Для маскирования прерываний используется внутренний регистр контроллера, программно доступный процессору как по записи, так и по чтению. Замаскирован может быть каждый запрос (по каждой из линий IRQ), путем установки соответствующего бита маскирования в записываемом в контроллер управляющем байте.

Схема приоритетов прерываний может быть задана процессором программным путем. В базовом варианте все приоритеты фиксированы (то есть IRQ0 имеет высший приоритет, а IRQ7 — низший). Но в принципе высший уровень приоритета задается для любого из входов запросов, можно также установить циклическое переключение приоритетов (последний обслуженный запрос получает низший приоритет), обеспечивая тем самым всем запросам равные приоритеты. Если во время обработки прерывания с меньшим уровнем приоритета приходит более приоритетный запрос, то процессор переходит на программу обработки более приоритетного запроса, а после ее выполнения возвращается к программе обработки менее приоритетного запроса. Отметим, что немаскируемое прерывание NMI имеет приоритет выше любого другого аппаратного прерывания.

Завершив выполнение программы обработки прерывания, процессору необходимо с помощью специальной команды сообщить об этом контроллеру прерываний, чтобы разрешить ему дальнейшую работу, в частности, вновь обрабатывать тот же самый запрос.

Все операции начальной настройки контроллеров прерываний выполняет BIOS, и пользователю нужно прибегать к программированию этих контроллеров только при необходимости смены режимов обслуживания прерываний или при написании собственной программы обработки аппаратных прерываний.

В микропроцессорном комплекте 580 серии имеется контроллер прерываний КР580ВН59, который позволяет создать систему прерываний: с маскированием, любые приоритетные, многоуровневые (до 64 уровней), многовекторные (до 64 векторов), динамически маскированные.

13. Обмен информацией МПС в режиме прямого доступа к памяти.

При обслуживании любого запроса на прерывании основным звеном системы является микропроцессор, управляющий шиной адреса и шиной данных и вырабатывающий управляющие сигналы для периферийных микросхем. Однако в некоторых случаях, когда необходимо пересылать между внешними устройствами и памятью большие блоки информации, использование процессора становится неэффективным, и используют метод прямого доступа к памяти. При прямом доступе к памяти управление системой передается специальному модулю. Все сигналы на выводах микропроцессора, за исключением некоторых управляющих выводов, переводится в 3-тье состояние, говорят, что процессор переходит в состояние захвата HOLD. Обменом управляет специализированный контроллер прямого доступа к памяти, и информация подается к внешнему устройству, минуя микропроцессор. Средства прямого доступа к памяти комплектуются отдельными модулями памяти.

Достоинство прямого доступа к памяти: высокая скорость обмена

Недостаток прямого доступа к памяти: система теряет управляемость, т.к. процессор отключается.

Прямой доступ к памяти (ПДП, DMA) — это режим, принципиально отличающийся от обмена по прерываниям и программного обмена информацией тем, что обмен по системной шине идет без участия процессора. Внешнее устройство, требующее обслуживания, сигнализирует процессору, что режим ПДП необходим, в ответ на это процессор заканчивает выполнение текущей команды и отключается от всех шин, сигнализируя запросившему устройству, что обмен в режиме ПДП можно начинать.

Операция ПДП сводится к пересылке информации из устройства ввода/вывода в память или же из памяти в устройство ввода/вывода. Когда пересылка информации будет закончена, процессор вновь возвращается к прерванной программе, продолжая ее с той точки, где его прервали. Это похоже на режим обслуживания прерываний, но в данном случае процессор не участвует в обмене. Как и в случае прерываний, реакция на внешнее событие при ПДП существенно медленнее, чем при программном режиме.

Понятно, что в этом случае требуется введение в систему дополнительного устройства (контроллера ПДП), которое будет осуществлять полноценный обмен по системной магистрали без всякого участия процессора. Причем процессор предварительно должен сообщить этому контроллеру ПДП, откуда ему следует брать информацию и/или куда ее следует помещать. Контроллер ПДП может считаться специализированным процессором, который отличается тем, что сам не участвует в обмене, не принимает в себя информацию и не выдает ее

В принципе контроллер ПДП может входить в состав устройства ввода/вывода, которому необходим режим ПДП или даже в состав нескольких устройств ввода/вывода. Теоретически обмен с помощью прямого доступа к памяти может обеспечить более высокую скорость передачи информации, чем программный обмен, так как процессор передает данные медленнее, чем специализированный контроллер ПДП. Однако на практике это преимущество реализуется далеко не всегда. Скорость обмена в режиме ПДП обычно ограничена возможностями магистрали. К тому же необходимость программного задания режимов контроллера ПДП может свести на нет выигрыш от более высокой скорости пересылки данных в режиме ПДП. Поэтому режим ПДП применяется редко.

Если в системе уже имеется самостоятельный контроллер ПДП, то это может в ряде случаев существенно упростить аппаратуру устройств ввода/вывода, работающих в режиме ПДП. В этом, пожалуй, состоит единственное бесспорное преимущество режима ПДП.

14. Организация обмена с памятью и внешними устройствами.

Из-за различия в быстродействии между памятью и внешними устройствами различают средства обмена между процессором и памятью (подсистема управления памятью) и средства обмена с внешними устройствами (подсистема ввода/вывода). Обычно эти средства распределяют между процессором и специализированными БИС. При организации обмена различают 2 подхода: 1)управление памятью и внешними устройствами с разделенным адресным пространством (карта памяти). 2)разделенное управление памятью и внешними устройствами.

В первом методе каждое внешнее устройство представляется как ячейка памяти. Для работы с памятью используются 2 управляющих устройства: MEMR (memory read), MEMW (memory write).

При втором методе все адресное пространство отводится под память, под внешнее устройство отводится специальная область и обращение проводится специальными сигналами: IOR (input output read), IOW (input output write).

Перечисленные сигналы никогда не появляются одновременно.

Достоинства при 1-ом методе: можно использовать полностью набор команд микропроцессора при обращении к внешнему устройству.

Недостаток при 1-ом методе: ограничение объема памяти.

Достоинства при 2-ом методе: полностью используется адресное пространство

Недостаток при 2-ом методе: - для обмена с внешними устройствами используются только 2 команды: IN ADR (для чтения), OUT ADR (для ввода). – малое количество внешних устройств.

15. Виды адресации

Для любого микропроцессора существует уникальный набор команд для работы с памятью и внешними устройствами. От разнообразия способов адресации зависит производительность микропроцессорной системы. Наиболее часто используются следующие виды:

- неявная – адресация, при которой местонахождение команды или операнда фиксировано.

- непосредственная – операнд непосредственно включен в команду

- прямая – операнды извлекаются из памяти или регистров по адресу указанному в команде. Если в команде адрес не символьный, а абсолютный, то ее называют абсолютной прямой адресацией.

- прямая регистровая – в коде команды хранится имя регистра, в котором находится или будет помещен операнд.

Достоинство всех 4-х видов: простота

Недостаток всех 4-х видов: негибкость

При необходимости разместить в памяти нескольких программ или модифицировать одну программу, такие виды адресации не эффективны, поэтому как привязаны к конкретным адресам, данным и регистрам.

- косвенная – операнд извлекается или помещается из одной ячейки памяти в другую ячейку памяти. В коде команды указан адрес ячейки памяти, в которой находится адрес операнда.

- косвенная регистровая – в коде команды указано имя регистра, в котором находится адрес операнда.

- индексная – используется при работе с массивами данных. С ее помощью адрес операнда вычисляется суммированием адреса одного элемента массива (адрес в коде команды) и некоторого целого смещения, называемого индексом, для хранения которого отводится специальный смежный регистр. Смещение может быть только положительное.

- базовая – адрес операнда вычисляется суммированием содержимого некоторого регистра, называемого базовым, и смещения, которое хранится в формате команды (здесь же задается адрес или имя базового регистра)

- относительная – позволяет обеспечить переместимость программ, содержащих команды переходов (условных и безусловных), а также возвратов. Адрес операнда вычисляется суммированием положительного или отрицательного смещения с содержимым счетчика команд.

- автоувеличение/уменьшение (автоинкриментирование и автодикриментирование) – разновидность косвенной регистровой, индексной адресации, при которой после или перед выполнением команды содержимое регистра с адресом операнда автоматически увеличивается или уменьшается на единицу. Используется при организации циклов и операций со строковыми переменными.

- стековая (косвенная регистровая с автоувеличением/уменьшением) – регистр с указанием адреса операнда задается неявно. Ячейка памяти, на который указывает этот регистр, называют верхушкой стека, а сам регистр – указателем стека.

- страничная и сегментная – из-за того, что ограничено число разрядов в формате команды, в процессорах, работающих с большим адресным пространством, используют деление памяти на страницы и/или сегменты. При этом производится 2-3 измерения при обращении к ячейке памяти. Применяют 2 способа получения физического адреса: 1)адрес ячейки содержится в коде команды и состоит из 2 частей (номер сегмента или страницы и адрес внутри) 2) физический адрес определяется суммированием исполнительного адреса и содержимого специального регистра, называемого сегментным или страничным.

Иногда в отдельный вид адресации выделяют адресацию к нулевой странице и к текущей странице.

- виртуальная – развита из страничной и сегментной адресации. В ее основе лежит динамическое перераспределение страниц памяти между основной памятью системы (АЗУ) и внешней памятью. Каждому модулю памяти система создает таблицу соответствия виртуальных и физических страниц, т.е. таблицу соответствия между логическими адресами страниц и физическими адресами страниц. Логический адрес при этом разделяется на 2 поля: младшие разряды указывают на слово внутри страницы, а старшие – на номер страницы.

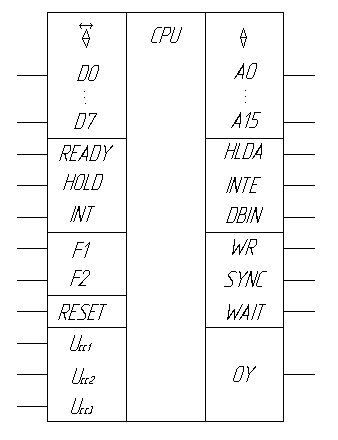

16. Микропроцессор КР580ВМ80 i8080

Этот микропроцессор является восьмиразрядным параллельным процессором, т.е. программируемые универсальные БИС способны: 1. считывать информацию из внешних устройств и памяти 2. производить арифметические и логические операции 3. анализировать результаты вычислений 4. записывать данные в память и внешние устройства.

Примечание: архитектура является базовой для семейства Х86.

Краткие технические характеристики: технология n-МОП; количество транзисторов – 4500; производительность – 0,5 миллиона операций в секунду; тактовая частота – не более 2,5МГц; потребляемая мощность – 1,25Вт; напряжение питания - ±5В,±12В; нагрузочная способность – 1 ТТЛ вход; рабочий диапазон температур – от -10 до +70˚С.

Рис 16а КР580ВМ80 i8080

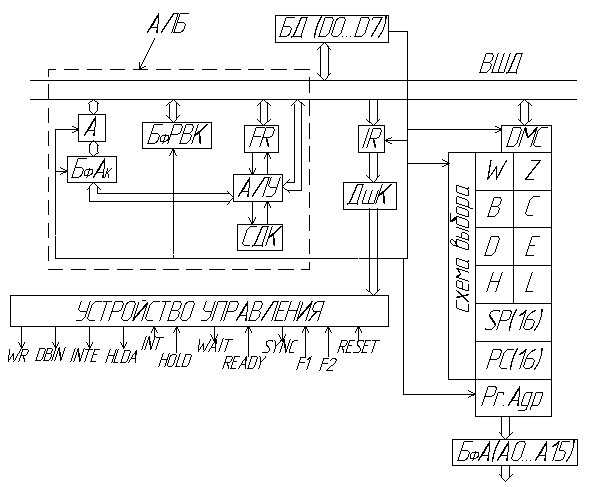

Рис 16б Функциональный микропроцессор

Функциональный микропроцессор состоит из следующих блоков:

-арифметико-логический блок (АЛБ)

-блок регистров и цепей их выбора

-регистр команд и устройство управления

-буфера данных и буфера адреса

-ВШД – внутренняя шина данных

В АЛБ входит восьмиразрядное арифметико-логическое устройство, также схема десятичной коррекции на базе постоянного запоминающего устройства.

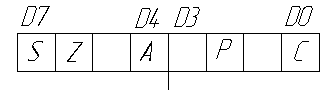

FR – регистр флагов – восьмиразрядный, но используется только 5 разрядов.

Флаг – разряд, который может установиться либо в 0, либо в 1.

S – Знаковый разряд, равный единице, если результат операции меньше нуля.

Z – Флаг нуля, равен единице, если результат операции равен нулю.

А (АС) – флаг дополнительного переноса, устанавливается в единицу, если во время выполнения или после операции произошел перенос из разряда D3 в D4.

Р – флаг четности равен единице, если число единиц в результате четно.

С – флаг переноса устанавливается в единицу, если был перенос из старшего разряда или в старший разряд (D7)

Блок регистров включает в себя 6 шестнадцатиразрядных регистров, четыре из которых образованы парами восьмиразрядных регистров. Регистры W и Z используются для хранения промежуточных результатов процессором и программно недоступны. Регистры SP и PC – специальные регистры, полностью шестнадцатиразрядные. SP (Stack Pointer) – хранит адрес верхушки стека, его значения модифицируются при операциях со стеком. PC (Program Counter) – хранит адрес следующей команды, которая будет выполняться. Его значение автоматически увеличивается на единицу, либо изменяется при выполнении команд перехода и вызова подпрограмм.

IR (Instruction Register) – регистр команд и дешифратор команд ДшК используются для извлечения и дешифрации кода команды. Выполнение каждой команды производится в строго определенной последовательности, в соответствии с кодом, и синхронизируется сигналами тактового генератора F1 и F2. Период этих сигналов называется машинным тактом.

Назначение выводов процессора.

А0-А15 – шина адреса – обеспечивает прямую адресацию к 216 ячейкам памяти.

Магистраль однонаправленная с возможностью третьего состояния.

D0-D7 – двунаправленная магистраль данных с возможностью третьего состояния для обмена информацией с памятью и внешними устройствами.

F1, F2 – входы для подачи тактовых импульсов (сигналы одной частоты, но не пересекающиеся во времени)

Reset (сброс) – вход начальной установки, по сигналу на этом входе сбрасывается в ноль программный счетчик, запрещаются прерывания и снимается состояние захвата (если таковое было)

SYNC – выход синхронизации – существует в течении одного такта и формируется вначале каждого машинного цикла

READY – вход-"готовность" – используется для организации обмена данными с внешними устройствами, быстродействие которых ниже быстродействия процессора. Высокий уровень на этом входе обеспечивает нормальное функционирование процессора.

WAIT – выход ожидания. Высокий уровень соответствует низкому уровню на входе READY.

HOLD – высокий уровень на этом входе переводит микропроцессор в состояние "захват". Это состояние возникает не сразу. Сначала завершается выполнение текущей команды, затем переводится в третье состояние шина адреса и данных, все остальные сигналы остаются без изменений.

На выходе HLDA появляется сигнал высокого уровня – "подтверждение захвата". Используется при организации прямого доступа к памяти.

INT – вход запроса на прерывание. Сигнал на этот вход поступает от внешнего устройства и обеспечивает выполнение цикла перехода к обработке прерывания. Воспринимается только при установке внутреннего триггера INTE в состояние единицы.

Состояние триггера отображается на выходе INTE

DBIN – вход шины данных – высокий уровень на этом входе говорит о приеме микропроцессором байта с шины данных.

WR (Write) – сигнал записи – сообщает о выдаче процессором байта информации на шину данных (обычно используется как строб записи)

17. Машинный такт, машинный цикл. Машинные циклы К580ВМ80

Важнейшими понятиями, характеризующими работу процессора, являются частота задающего генератора данного ПК и зависящий от неё такт работы процессора, называемый так же машинным тактом. В течение машинного такта выполняется одна или несколько микроопераций процессора, в зависимости от разрядности процессора и шины данных. Чем больше разрядность, тем больше операций выполняется за один такт. Чем короче машинный такт, тем выше производительность процессора, которая выражается количеством выполняемых операций в единицу времени. Определённая периодичность, с которой процессор обрабатывает очередную порцию информации, называется тактовой частотой и измеряется в мегагерцах (МГц).

Машинный цикл – время, требующееся для извлечения одного байта из памяти или выполнение команды, определяемое одним машинным словом. Для 80-го процессора машинное слово составляет 1 байт. Машинный цикл может содержать от 3 до 5 машинных тактов. Время выполнения команды включает время получения декодирования и непосредственного выполнения команды (для 80-го процессора от 1 до 5 машинных циклов)

Машинные циклы процессора 580ВМ80

Существует 10 машинных циклов. Все начинаются с буквы М и разбиты на 3 группы:

- цикл чтения – М1, М2, М4, М6, М8, М10

- цикл записи – М3, М5, М7

- цикл остановки – М9

М1 – цикл извлечения кода команды. С этого цикла начинается любая команда.

М2 – чтение данных из памяти по адресу, расположенному в паре регистров или счетчике команд

М3 – цикл записи в память по адресу, расположенному в одной из пар регистров

М4 – чтение из стека, т.е. чтение из ячейки памяти, на которую указывает SP.

М5 – цикл записи в стек

М6 – цикл чтения данных из внешнего устройства в аккумулятор

М7 – запись из аккумулятора во внешнее устройство

М8 – цикл обслуживания прерывания

М9 – цикл остановки

М10 – цикл обслуживания прерываний в режиме остановки.

Пример цикла чтения.

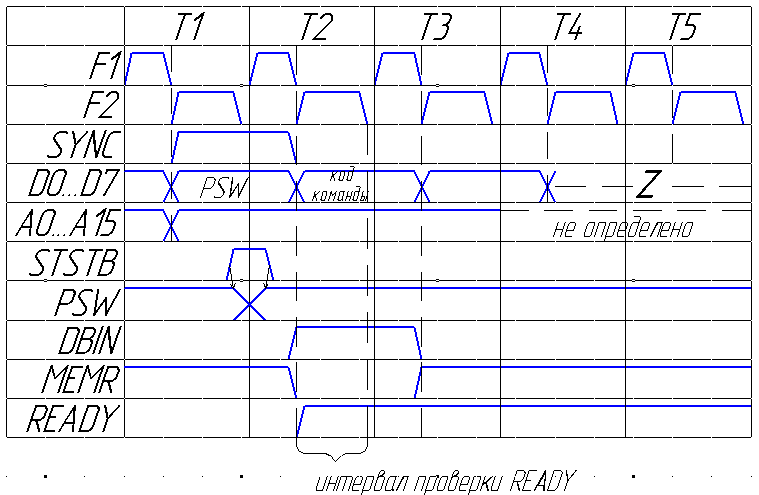

Рис 17. Пример цикла чтения

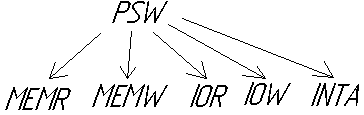

В начале каждого машинного цикла по переднему фронту сигнала F2 на выходе процессора SYNC формируется импульс высокого уровня. Он инициирует начало машинного цикла для внешних устройств. Одновременно на шине данных появляется код слова состояния (PSW), который содержит информацию о типе выполняемого процессором машинного цикла. Длительность синхронизации и словосостояния один такт, но словосостояние необходимо сохранять, т.к. оно используется для формирования всех управляющих сигналов.

Для сохранения словосостояния могут использоваться внешние регистры (серия 589) или системные контроллеры (КР58028, КР58038). Для записи словосостояния формируется сигнал STSTB. В этом же такте Т1 на магистрали адреса формируется шестнадцатиразрядный адрес, из которого будет извлекаться код команды или данные в зависимости от типа цикла. Адрес на шине сохраняется до четвертого такта, затем он переходит в неопределенное состояние. После записи словосостояния на шину данных появляется код команды, извлекаемой из памяти. В это же время в такте Т2 формируется сигнал DBIN, который сообщает, что шина данных находится в режиме чтения. По этому сигналу происходит запись кода команды в микропроцессор и его дальнейшая дешифрация. Для формирования управляющих сигналов чтения памяти используется сигнал DBIN и один из разрядов словосочетания. Таким образом, к началу третьего такта завершена запись кода команды в микропроцессор. К началу третьего такта в такте Т2 микропроцессор проверяет состояние READY и состояние HOLD, а также состояние внутреннего триггера останова HLTA, который устанавливается в единицу после выполнения команды останова HALT. В зависимости от сигналов на этих выводах процессор переходит либо в состояние ожидания, либо в состояние "захвата", либо в состояние останова.

В состояние ожидания процессор переходит в следующем такте (Т4). В этом состоянии сигналы на всех выводах процессора остаются постоянными, за исключением вывода WAIT, и в каждом такте происходит проверка сигнала на входе READY (по заднему фронту сигнала F2). И при появлении высокого уровня процессор переходит к выполнению такта Т3.

При переходе в состояние "захват" процессор завершает текущий цикл чтения, после чего переводит шину адреса и шину данных в третье состояние. Это происходит после такта Т3. Все остальные сигналы на входах остаются неизменными. В такте Т4 код команды поступает на регистр IR (регистр команд), дешифрируется, т.е. определяется сколько тактов и циклов требуется для выполнения команды, и в такте Т5 может произойти выполнение команды (если она занимает 1 цикл). Если для выполнения команды требуется большее число циклов, то после М1 выполняется цикл чтения или записи. Цикл записи занимает ровно 3 такта и отличается тем, что сигнал DBIN не формируется. Вместо него в третьем такте формируется сигнал WRITE, из которого совместно со словосостоянием системой управления формируется сигнал MEMW. Цикл чтения (М2, М4, М6, М8, М10) отличается от цикла М1 только тем, что вместо кода команды извлекаются операнды, т.е. данные. Циклы чтения и записи для внешних устройств отличаются от циклов работы с памятью тем, что вместо сигналов MEMW и MEMR формируются сигналы IOW и IOR. Для формирования сигналов управления используется сигнал словосостояния PSW и сигналы WRITE и READ.

18. Начальная установка и особое состояние 580 процессора.

Функции начальной установки микропроцессора – внешний сигнал начальной установки микропроцессора Reset формируется при включении питания или нажатия на кнопку Reset. При появлении этого сигнала устройство управления обеспечивает загрузку нулевого значения в указатель команд (нулевое значение для большинства микропроцессоров, но не для всех, например, Motorola).

Нулевое значение указателя команд инициирует выборку команды с нулевым адресом. В конце выборки содержимое указателя команд увеличивается на единицу и выбирается байт команд со следующим адресом.

Функции синхронизации: в соответствии с внешними управляющими командами и сигналами синхронизации устройство управления синхронизирует работу всех блоков микропроцессорной системы.

Функции прерываний: с поступлением сигнала прерывания устройство управления инициирует выполнение предпрограммы обработки соответствующего прерывания. Потребность в реализации прерываний возникает тогда, когда во время выполнения основной программы процессор надо перевести на выполнение другой задачи, например, обработку ситуации или работу с УВВ.

Функции согласования быстродействия модулей микропроцессорной системы: во время обслуживания памяти и устройств ввода-вывода, быстродействие которых меньше, чем у микропроцессора, согласование реализуется генерацией тактов ожидания микропроцессора. Во время обслуживания устройств с большим быстродействием, чем у микропроцессора, используется режим прямого доступа к памяти.

Арифметико-логическое устройство представляет собой комбинационную схему на основе сумматора, который сигналами с выходов устройства управления настраивается на выполнение арифметических или логических операций. АЛУ выполняет операции над операндами, которые пересылаются из памяти и/или регистров микропроцессора.

Операнд – это объект в виде значения данных содержимого регистров или ячейки памяти, с которым работает команда. Регистры предназначены для хранения n-разрядного двоичного числа. Они представляют собой n триггеров со схемами управления и чтением записи сборки. Регистры создают внутреннюю память микропроцессора и используются для хранения промежуточных результатов вычисления.

Аккумулятор – это регистр, в котором хранится один из операндов. После выполнения команды вместо операнда в аккумуляторе помещается результат операции. В 8-ми разрядных процессорах аккумулятор принимает участие во всех операциях АЛУ. В 16-ти разрядных микропроцессорах большинство команд выполняется без участия аккумулятора, однако в некоторых типах команд (ввод-вывод, умножение и деление) аккумулятор действует также как 8-ми разрядный процессор.

Указатель команд или программный счетчик предназначен для хранения ячейки памяти, которая содержит код следующей команды.

Программа действия микропроцессора записана в памяти в виде последовательности кодов. Для перехода к следующей команде содержимое счетчика увеличивают на единицу в момент выборки команды из памяти. Таким образом, в конце выполнения команды в счетчике команд хранятся адреса следующей команды.

Указатель стека – это регистр, который хранит адрес последней занятой ячейки стека.

Стеком называется область памяти, которая организована по принципу "последний пришел - первый вышел" (LIFO)

Стек предназначен для хранения данных и сохранения состояния текущего процесса при вызове подпрограмм.

Регистр команд хранит код команды на протяжении всего времени выполнения команды. Регистр адреса и регистры данных предназначены для хранения адресов и данных, используемых во время выполнения текущей команды. Регистр состояния (регистр флагов, признаков) предназначен для хранения информации о результате операции в АЛУ и представляет собой несколько триггеров, входы которых находятся в "1" или "0" состояниях.

При включении питания процессора и поступлении на входы F1, F2 тактовых импульсов, все регистры и флаги устанавливаются в произвольное состояние, поэтому необходимо произвести сброс, который осуществляется по входу RESET. Для этого необходимо сформировать сигнал высокого уровня длительностью не менее трех тактов, после чего сбрасывается в 0 программный счетчик РС и сбрасывается триггер разрешения прерывания INTE, сбрасывается триггер подтверждения "захвата" HLDA и процессор начинает осуществлять выборку команд начиная с нулевого адреса (поэтому у 80-го процессора область ПЗУ начинается с адреса 0000). К особым состояниям относятся 4 состояния:

- ожидание

- "захват"

- останов

- прерывание

События, в результате которых происходят эти состояния:

- если в такте Т2 любого из циклов, кроме 8-10 на выходе READY подается сигнал низкого уровня, то процессор переходит в состояние ожидания.

- если на вход HOLD подать сигнал высокого уровня, процессор переходит в состояние "захват", причем переход происходит по-разному в зависимости от типа цикла:

- в цикле записи: в такте, следующем за Т3, появляется подтверждение "захвата", т.е. после завершения выполнения команды.

-в циклах чтения: подтверждение "захвата" происходит в Т4 и процессор завершает команду чтения уже с отключенными выводами.

- состояние останов похоже на состояние ожидания, но процессор входит в это состояние программы после выполнения команды HLT и выйти из этого состояния может только после выключения или сброса, однако процессор реагирует на прерывание и запрос на "захват".

19. Структура блока центрального процессора на основе КР580ВМ80.

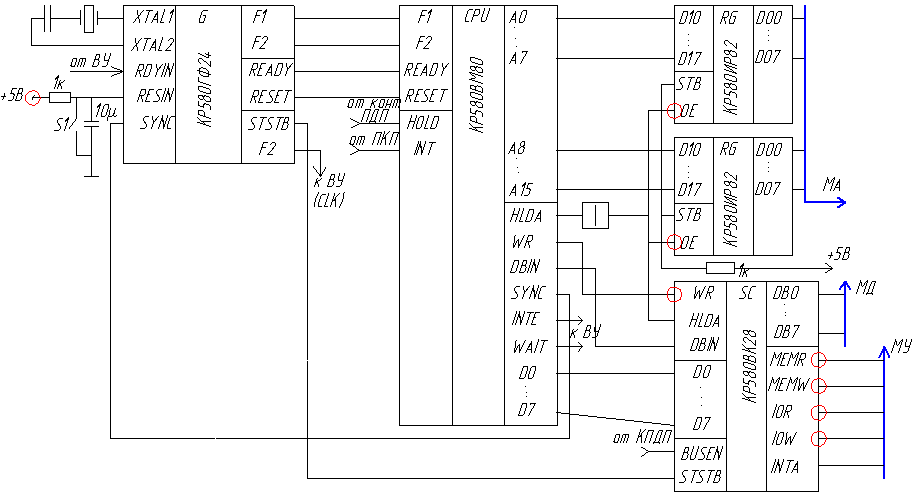

Рис 19. Структура блока центрального процессора

от конт. ПДП – от контроллера ПДП – сигнал HOLD сигнал INT поступает от программируемого контроллера прерываний (ПКП) к ВУ (внешнее устройство) идут сигналы INTE и WAIT .

CLK – сигнал тактовой частоты для внешних устройств.

Переключатель S1 формирует сигнал сброса. На вход генератора RDINT поступает сигнал, который переводит процессор в состояние ожидания. Частота работы процессора в данной схеме 2МГц.

ША формируется с помощью двух буферных регистров (КР580ИР82), которые предназначены для увеличения нагрузочной способности магистрали адреса. ША стробируется сигналом HLDA. ШД и ШУ формирует системный контроллер.

20. Программируемый интерфейс К580ВВ55, структура и назначение выводов

Программный параллельный интерфейс КР580ВВ55 предназначен для организации обмена как синхронного, так и асинхронного по прерыванию между процессором и внешним устройством.

Краткие технические данные.

Технология…………………………………….. n-МОП

Напряжение питания…………………………… +5В

Максимальная тактовая частота ……………….2МГц

Нагрузочная способность…………………… 1 ТТЛ-вход

Все сигналы ТТЛ уровня

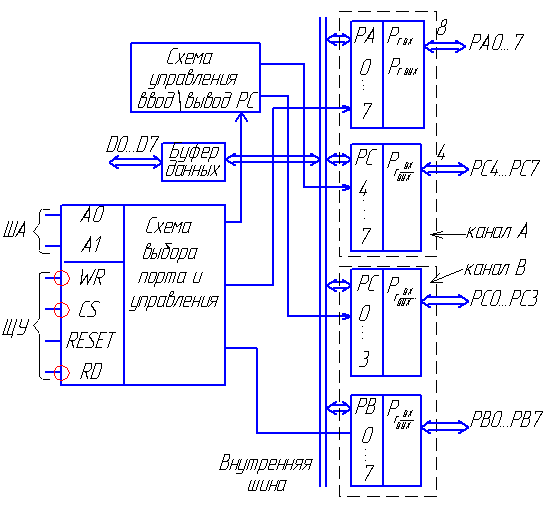

Рис 20. Программируемый интерфейс К580ВВ55

В структуру входит схема управления вводом-выводом двунаправленный вывод данных и 3 восьмиразрядных порта – А, В и С. При этом порт А содержит 2 восьмиразрядных регистра и двунаправленный шинный формирователь. Порт С содержит по 2 четырехразрядных регистра входа и выхода и 2 шинных формирователя, а также отдельную схему управления портом С. Порт В содержит 1 восьмиразрядный регистр, работающий либо на вход, либо на выход и шинный формирователь. Порт А и старшие разряды порта С (4-7) образуют канал А. Порт В и младшие разряды порта С образуют канал В. Канал А может работать в трех режимах:

режим 0 – основной режим, однонаправленный синхронный обмен, порт работает либо только на вход, либо только на выход. Дополнительных сигналов управления не требуется, можно использовать все 3 порта

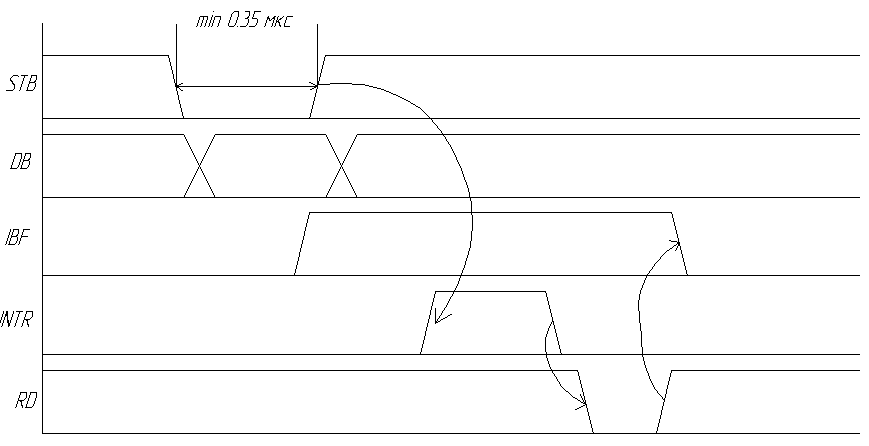

режим 1 (стробированный ввод-вывод) – однонаправленный асинхронный обмен по прерыванию. Информация передается по портам А и В. Порт С используется для передачи управляющих сигналов, при этом каждый сигнал может быть настроен на ввод или вывод.

режим 2 (режим двунаправленной шины) – используются порты А и С. Порт А – данные, порт С – управляющие сигналы. Порт В не используется.

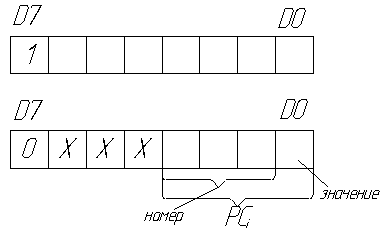

21. Настройка микросхем на режим

Настройка осуществляется загрузкой управляющих слов, которые записываются в регистр управляющего слова (Control Word Register CWR). Используются 2 управляющих слова, которые отличаются наличием "1" в старшем разряде. Второе управляющее слово, у которого разряд D7 равен 0 предназначено для установки отдельных разрядов порта С в "0" или "1".

0ххх0010 02h – пример

Загрузка управляющего слова производится по старшему из адресов, присвоенному микросхеме

РА 50

РВ 51

РС 52

CWR 53

Переключение портов микросхемы на чтение или запись сопровождается управляющими сигналами.

Режим 0 – адрес порта задается комбинацией сигналов А0 А1, чтение-запись производится за счет сигналов READ-WRITE, необходимо учитывать, что при записи в порт данные фиксируются в выходных регистрах, а при чтении (вводе в микропроцессор) данные должны оставаться на входах порта до тех пор пока их не прочитает процессор.

Режим 1 – выводы порта С имеют строго фиксированное значение.

| | Ввод | Вывод |

| С0 | INTR B | INTR B |

| С1 | IBF B | OBF B |

| С2 | STB B | ACK B |

| С3 | INTR A | INTR A |

| С4 | STB A | - |

| С5 | IBF A | - |

| С6 | - | ACK A |

| С7 | - | OBF A |

Interrupt Request

Input (Output) Buffer Full

STB – Strobe

ACK (Acknowledge)

Рис 21 Настройка микросхем на режим

Чтобы организовать запись из внешнего устройства в порт с последующим чтением информации процессором, внешнее устройство формирует сигнал строб STB, выставляет данные на вход порта, которые записываются в буфер порта, после чего формируется сигнал IBF. По окончании импульса STB и сигналов IBF, STB и INTE формируется сигнал запроса на прерывание для процессора. Сигнал подается либо на процессор, либо на один из входов контроллера прерываний. В результате вызывается подпрограмма обработки прерываний, и микропроцессор командой IN читает соответствующий порт, при этом на шине управления присутствует сигнал RD низкого уровня. По нему сбрасывается сигнал запроса на прерывание и сигнал IBF.

0ХХХ1001

0ХХХ0101

22. Семейства PIC контроллеров PIC-16XXX

Основным назначением микроконтроллеров семейств PIC16 и PIC17, как следует из аббревиатуры PIC (Peripheral Interface Controller), является выполнение интерфейсных функций. Этим объясняются особенности их архитектуры:

- RISC-система команд, характеризующаяся малым набором одноадресных инструкций (33, 35 или 58), каждая из которых имеет длину в одно слово (12, 14 или 16 бит) и большинство выполняется за один машинный цикл. В системе команд отсутствуют сложные арифметические команды (умножение, деление), предельно сокращен набор условных переходов;

- высокая скорость выполнения команд: при тактовой частоте 20 МГц время машинного цикла составляет 200 нс (быстродействие равно 5 млн. операций/сек);

- наличие мощных драйверов (до 25 мА) на линиях портов ввода/вывода, что позволяет подключать непосредственно к ним довольно мощную нагрузку, например, светодиоды.

- низкая потребляемая мощность;

- ориентация на ценовую нишу предельно низкой стоимости, определяющая использование дешевых корпусов с малым количеством выводов (8, 14, 18, 28), отказ от внешних шин адреса и данных (кроме PIC17C4X), использование упрощенного механизма прерываний и аппаратного (программно недоступного) стека.