Инженерная логика против классической

| Вид материала | Книга |

| Глава четвёртая РЕГИСТРЫ И СЧЁТЧИКИ 4.1 Регистры памяти. 4..2. Регистры сдвига. 4..3. Двоичные счётчики. 4.4 . Десятичные счётчики. 4.5. Элементная база для построения счётчиков. |

- Программа курса и темы практических занятий; Логика в таблицах и схемах. Логика как, 1722.34kb.

- Логика в образовании, 153.37kb.

- Математическая логика, 1012.22kb.

- Курс: 1 семестр 2 дисциплина: Инженерная графика задания для самостоятельной работы, 459.93kb.

- Логика богочеловечества, 213.06kb.

- Гуманитарное образование в технических вузах России в 19 20 веках, 261.32kb.

- Активизирующий опросник "За и против", 392.33kb.

- Отчет о выполнении 1 этапа проекта кафедры «Инженерная графика и дизайн», 95.62kb.

- «Инженерная экономика и маркетинг», 412.65kb.

- Н. В. Папуловская Математическая логика Методическое пособие, 786.38kb.

Глава четвёртая

РЕГИСТРЫ И СЧЁТЧИКИ

Наиболее часто в схемах с памятью используются такие функциональные узлы , как регистры и счётчики. Регистры разделяются на два типа: параллельные (регистры памяти) и последовательные (регистры сдвига). Регистры могут быть реализованы на любых триггерах.

4.1 Регистры памяти.

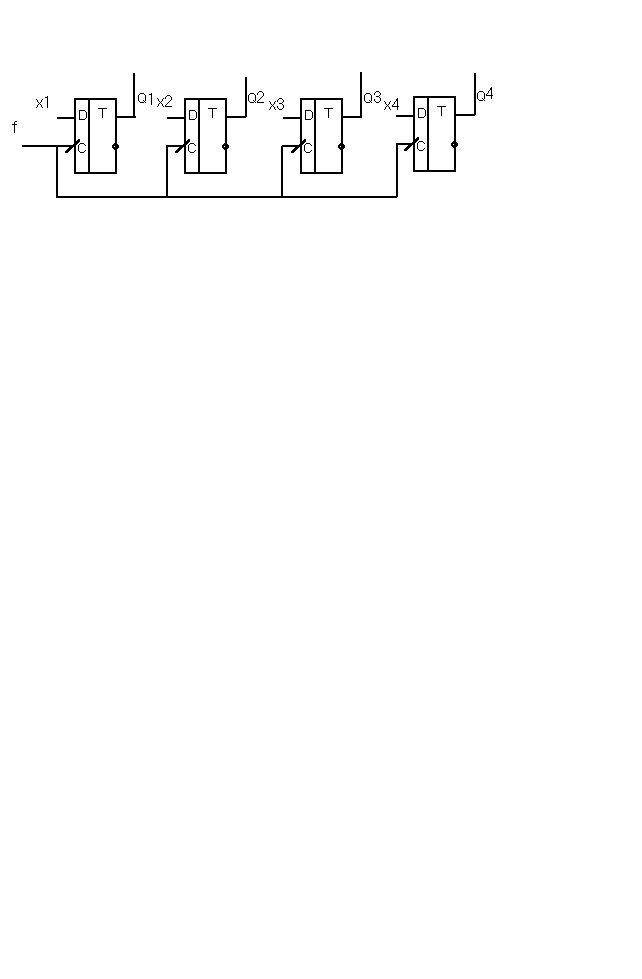

Эти регистры предназначены для хранения информации, представленной в виде двоичного кода. Регистры памяти осуществляют параллельную запись всего кода с приходом тактового импульса. Записанная информация хранится до прихода следующего тактового импульса. На рисунке представлен один из вариантов регистра памяти, реализованного на D- триггерах, тактируемых передним фронтом. Этот регистр предназначен для записи и хранения 4-разрядного кода X.

С приходом переднего фронта тактовой частоты fт регистр запишет код X и будет хранить его до тех пор , пока код X не изменит своей величины. Но это изменение кода X пройдёт на выход регистра только с приходом переднего фронта fт.

Схема параллельного регистра.

4..2. Регистры сдвига.

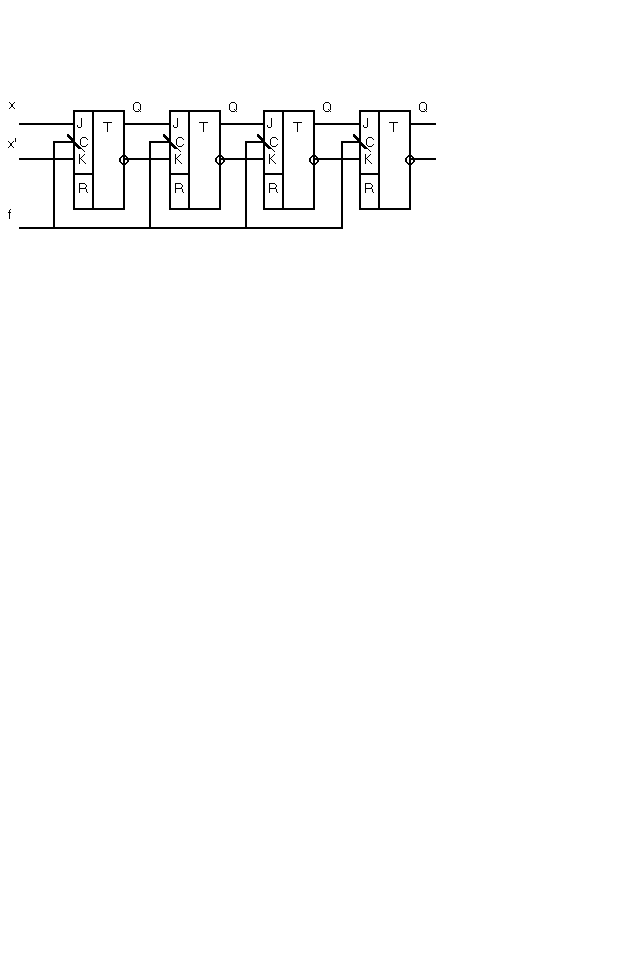

Сдвиговые регистры широко используются в цифровой технике, в частности для преобразования последовательного двоичного кода в параллельный или наоборот. На рисунке изображён сдвиговый регистр , реализованный на JK- триггерах.

Схема регистра сдвига.

Благодаря последовательной схеме соединения разрядов регистра каждый задний фронт fт устанавливает последующий триггер в состояние, в котором до этого находился предыдущий, осуществляя сдвиг информации на разряд вправо.

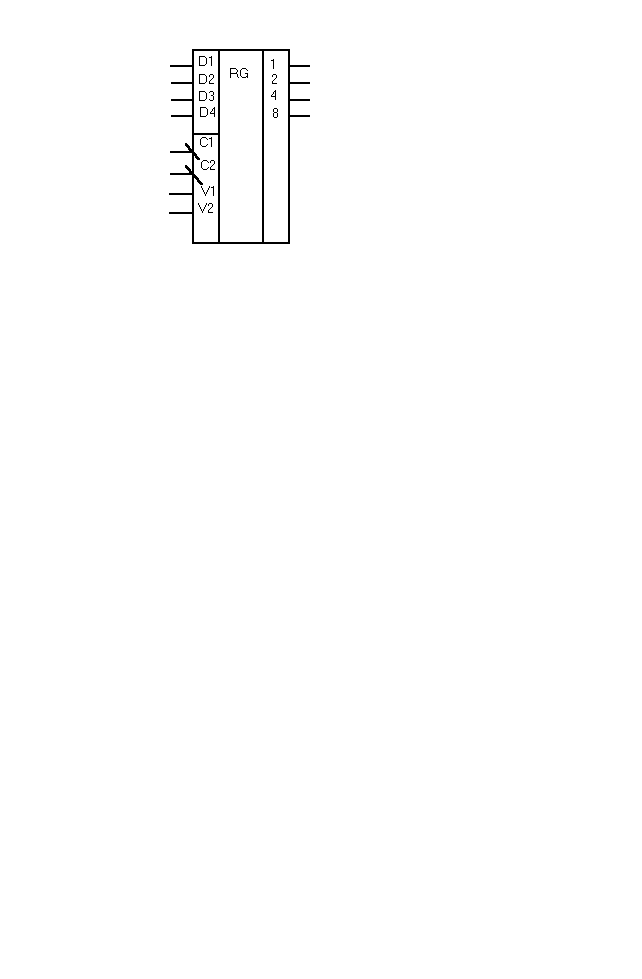

На следующем рисунке представлена ИС типа 533ИР1, которая реализует функции как 4-х разрядного регистра памяти, так и функции регистра сдвига в зависимости от значения сигнала на входе выбора режима V2:

при V2=0 - режим сдвига,

при V2=1 - режим параллельной записи.

На рисунке :

C1- тактовый вход продвижения информации , поступающей по входу V1.

C2- тактовый вход параллельной записи.

Если смена режима для 533ИР1 происходит в процессе работы, то для обеспечения безошибочной работы регистра необходимо выполнить условие C1’C2’=1.

Условное обозначение универсального регистра.

4..3. Двоичные счётчики.

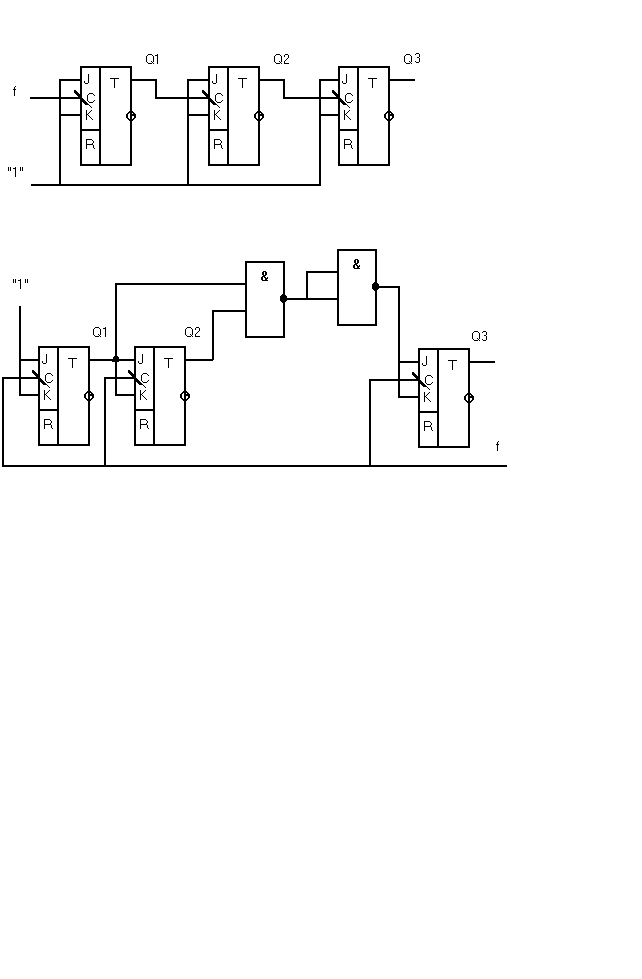

Двоичные счётчики могут быть синхронными и асинхронными . Двоичный асинхронный счётчик может быть построен последовательным соединением счётных триггеров, или JK- триггеров , у которых J=K=1.

Асинхронный и синхронный двоичные счётчики.

Недостатком асинхронных счётчиков является задержка в установлении соответствующего кода после прихода счётного импульса. Эта задержка, в частности, может приводить к появлению ложных кодов на выходе счётчика и сбою дешифратора. Например, после кода 011 на выходе счётчика должен появиться код 100 (коды записаны в порядке Q3Q2Q1). В асинхронном счётчике при последовательном срабатывании триггеров код будет меняться следующим образом 011-010-000-100, т.е. во время переходного процесса появляются два ложных кода 010 и 000.

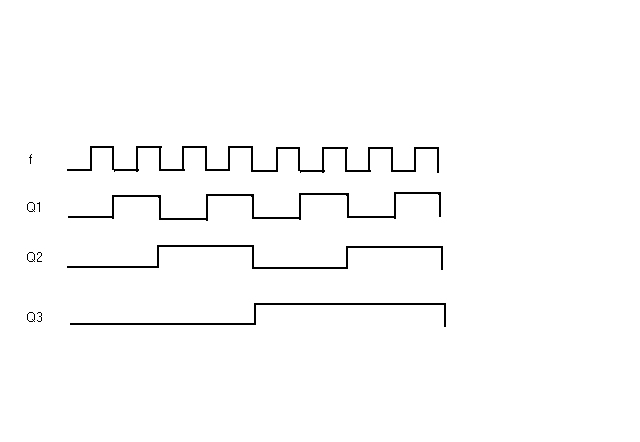

В двоичных синхронных счёичиках срабатывание триггеров происходит одновременно или почти одновременно , так как все тактовые входы триггеров запараллелены . Временная диаграмма двоичного счётчика представлена на рисунке.

Диаграммы работы двоичного счётчика.

Для построения синхронных счётчиков с коэффициентом деления K=2n используется n JK- триггеров, функции возбуждения которых определяются соотношением

m-1

Jm=Km=& Qi ,

i=1

где Jm, Km - соответствующие входы JK- триггера, на котором реализован m-ый разряд счётчика.

4.4 . Десятичные счётчики.

Десятичные счётчики строят на основе четырёхразрядных двоичных. Для понижения коэффициента пересчёта четырёразрядного счётчика с 16 до 10 вводят различные логические связи. В зависимости от вида логической связи одним и тем же десятичным числам в различных счётчиках могут соответствовать различные четырёхразрядные двоичные коды. В этом случае говорят, что счётчики работают в различных двоично-десятичных кодах.

Наиболее часто в счётчиках используется взвешенное кодирование. Если любое десятичное число А может быть выражено в виде суммы

n

А = aiQi ,

i=0

где Qi - двоичные числа (0 или 1) в соответствующих разрядах кода,

аi - некоторые постоянные числа (веса разрядов),

то кодирование, построенное на данном соотношении, называется взвешенным.

Чаще других употребляется двоично-десятичный код 8-4-2-1.Здесь и далее цифры 8, 4, 2, 1 обозначают веса разрядов двоично-десятичного кода. Преимущество кода в его одназначности. Другие же коды неодназначны. Например, в коде 4-2-2-1 десятичное число 4 можно представить как 1000 или 0110, поэтому существуют таблицы, однозначно закрепляющие за каждым кодом соответствующее десятичное число [5].

В таблице приводятся наиболее употребительные двоично-десятичные коды. Код с избытком 3 является самодополняющимся. Для этих кодов характерно то, что при их поразрядном инвертировании получается код числа, дополняющее данное до девяти. Это свойство кода удобно при построении цифровых приборов, измеряющих знакопеременные величины.

| Q4Q3Q2Q1 | код 8-4-2-1 | Невзвешенный код | Код с избытком 3 |

| 0 0 0 0 | 0 | 0 | - |

| 0 0 0 1 | 1 | 1 | - |

| 0 0 1 0 | 2 | 2 | - |

| 0 0 1 1 | 3 | 3 | 0 |

| 0 1 0 0 | 4 | - | 1 |

| 0 1 0 1 | 5 | - | 2 |

| 0 1 1 0 | 6 | 4 | 3 |

| 0 1 1 1 | 7 | 5 | 4 |

| 1 0 0 0 | 8 | - | 5 |

| 1 0 0 1 | 9 | - | 6 |

| 1 0 1 0 | - | - | 7 |

| 1 0 1 1 | - | - | 8 |

| 1 1 0 0 | - | 8 | 9 |

| 1 1 0 1 | - | 9 | - |

| 1 1 1 0 | - | 6 | - |

| 1 1 1 1 | - | 7 | - |

4.5. Элементная база для построения счётчиков.

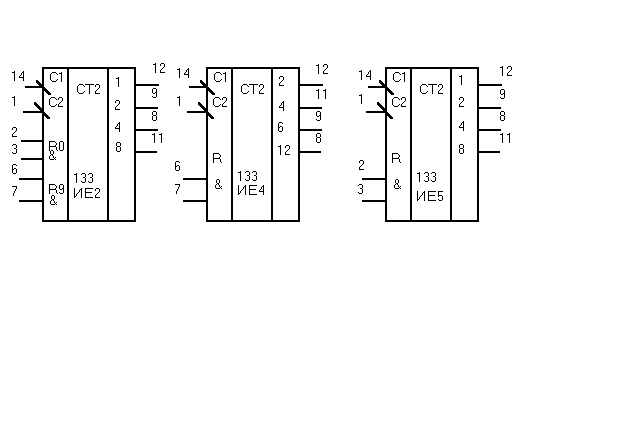

В настоящее время промышленность выпускает ИС, реализующие асинхронные двоично-десятичные счётчики (533ИЕ2), счётчики-делители на 12 (533ИЕ4) и делитель на 16 (533ИЕ5). 533ИЕ2 имеет коэффициент деления К = 2 х 5, для 533ИЕ4 К = 2 х 6, для 533ИЕ5 К = 2 х 8.

На рисунке в поле изображения микросхемы использованы следующие обозначения:

С1, С2 - тактовые входы соответственно для 1-го и 2-го разрядов;

R0 - вход обнуления;

R9 - вход установки счётчика в состояние 1001.

Для 533ИЕ4 выходы с весами 2, 4, 6, 12 обозначают выходы соответственно 1-го, 2-го, 3-го и 4-го разрядов, для счётчиков 533ИЕ2 и 533ИЕ5 выходы с весами 1, 2, 4, 8 обозначают выходы соответственно 1го, 2-го, 3-го и 4-го разрядов. Двоичный и десятичный счётчики изменяют свои состояния в соответствии с натуральной последовательностью кодов. Счётчик 533ИЕ4(133ИЕ4) изменяет своё состояние в соответствии со следующей последовательностью десятичных кодов: 0-1-2-3-4-5-8-9-10-11-12-13.Это связано с тем, что счётчик построен по схеме соединения делителей с коэффициентами деления 2 x 3 x 2 вместо 2 x 2 x 3 . Такую архитектуру можно объяснить лишь безграмотностью разработчиков.

Условные обозначения ИС асинхронных счётчиков 133 серии.