Методические указания по дисциплине 5 3 Задания для контрольной работы 8

| Вид материала | Методические указания |

- Методические указания и задания контрольной работы по дисциплине «Маркетинг» составлены, 814.73kb.

- Методические указания и задания к выполнению контрольной работы по дисциплине, 246.08kb.

- Рабочая программа, методические указания по выполнению курсовой работы, темы курсовых, 1694.43kb.

- Методические указания по выполнению контрольной работы по учебной дисциплине «валютные, 450.92kb.

- Методические указания и задания для контрольной работы студентам идо, 594.75kb.

- Методические указания и задания по контрольной работе по дисциплине «Деньги, кредит,, 260.6kb.

- Рабочая программа, методические указания, задания на контрольную работу и темы курсовых, 623.25kb.

- Методические указания и контрольные задания по дисциплине: «Электротехника и электроника», 414.34kb.

- Методические указания по выполнению контрольной работы по курсу, 260.49kb.

- Методические указания к выполнению контрольной работы по дисциплине «Материаловедение», 319.29kb.

Содержание

Содержание 2

Предисловие 3

1 Содержание учебного материала 4

1.1 Содержание дисциплины (90 часов) 4

1.2 Содержание лекционного материала (12 часов) 5

1.3 Содержание лабораторных работ (10 часов) 5

2 Методические указания по дисциплине 5

3 Задания для контрольной работы 8

3.1 Задача 1 8

3.2 Задача 2 10

3.3 Задача 3 12

3.4 Задача 4 12

3.5 Задача 5 14

Список литературы 16

Предисловие

В настоящее время в эксплуатации находится большое количество электромеханических приборов (ваттметры, счетчики, реле защиты), характеризующиеся большими габаритами, наличием контактов и значительным потреблением мощности. Защиты не обладают достаточной чувствительностью и быстродействием.

Использование в технике контроля и релейной защиты полупроводниковых элементов неинтегрального исполнения происходило путем компоновки измерительных систем и защит из типовых логических и функциональных элементов, например, комплекс защит и автоматики для КРУ 6-10 кВ. Это позволило снизить напряжение срабатывания, например, реле направления мощности, реле сопротивления, повысить их быстродействие и несколько уменьшить потребление от измерительных трансформаторов. Однако в этих защитах и в автоматике сохранилась зависимость между информационными и энергетическими характеристиками устройств, а уменьшение потребления мощности от трансформаторов тока и напряжения оказалось недостаточным. В ряде случаев они стали сложнее в эксплуатации.

Применение интегральной микроэлектроники позволило решать задачу комплексного улучшения основных показателей систем контроля, защит и автоматики: точность, быстродействие, надежность, потребление мощности.

Современные устройства защиты и автоматики выполняются в виде совокупности унифицированных функциональных узлов и элементов, позволяющих получать измерительные сигналы с высокой степенью избирательности, передавать их на значительные расстояния, обрабатывать по определенным программам, хранить и воспроизводить по требованию пользователя.

Материал данной дисциплины базируется на знании физики, теоретических основ электротехники, информатики. Знания, полученные в результате освоения данной дисциплины, потребуются при выполнении курсового и дипломного проектирования по разделам: аппараты и реле защиты и автоматика.

Бюджет времени студентов по данной дисциплине, обучающихся по дистанционной форме обучения, составляет 2 кредита, т.е. 90 часов; из них аудиторные - 22 часа; в том числе, из них лекции – 12 часов; лабораторные занятия – 10 часов; 68 часов отводится для самостоятельной работы. Предусмотрено выполнение одной контрольной работы.

Основной упор при изучении данной дисциплины делается на самостоятельную работу с учебной литературой.

К экзамену по курсу студенты допускаются только после выполнения лабораторных работ, контрольной работы и их защиты.

^

1 Содержание учебного материала

1.1 Содержание дисциплины (90 часов)

1.1.1 Виды интегральных микросхем (ИМС) (30 часов). ИМС: полупроводниковые (монолитные), гибридные (пленочные); логические (цифровые), аналоговые (линейно-импульсные).

Общие свойства и технические характеристики операционных усилителей (ОУ): структурная схема и параметры ОУ, базовые схемы включения ОУ (инвертирующая, неинвертирующая, дифференциальная). Усилители: звуковых частот, широкополосные, избирательные.

Линейные безинерционные активные преобразователи (инверторы, повторители, сумматоры, интеграторы, дифференциаторы, формирователи модулей (выпрямители)).

Коммутаторы и компараторы (ограничители, детекторы ненулевого и нулевого уровней).

Цифроаналоговые и аналого-цифровые преобразователи.

1.1.2 Микропроцессоры (МП) и микроконтроллеры (34 часа). Типовая структура аппаратного оборудования МП. Основные логические операции. Реализация логических операции на элементах. Базовые логические элементы на основе КМОП – технологии.

Реализация основных арифметических операций. Аппаратные устройства их реализации. Схема полу- и полного сумматора. JK-триггер.

Регистры. Способы их загрузки и разгрузки. Память. Элемент памяти. Ячейка биполярного программируемого ПЗУ на МОП – транзисторах.

Шифраторы и дешифраторы команд и адресов.

1.1.3 Оптоэлектроника (12 часов). Источники света: инжекционные светодиоды и лазеры.

Источники приема света: фоторезисторы, фотодиоды, фототиристоры, фотосимисторы.

Каналы оптической связи: воздушное пространство, световолоконные кабели.

Оптоэлектронные микросхемы в цепях управления, коммутации и согласования. Схемы оптоэлектронных ключей, переключателей, реле.

1.1.4 Микросхемы вторичных источников питания (6 часов). ИМС – стабилизаторы параметрического, компенсационного и импульсного типов.

ИМС с выпрямителем и стабилизатором.

Принципы устройства однополярных и двухполярных источников питания с постоянным и регулируемым выходным напряжением. Импульсные безтрансформаторные источники питания.

1.1.5 Средства отображения информации при контроле, управлении и коммутации (8 часов). Газоразрядные индикаторы, панели и кнопки переменного тока. Вакуумные люминесцентные индикаторы, табло и панели различного цвета. Светодиодные сигнальные ячейки и панели. Жидкокристаллические алфавитно-знаковые экраны, табло и панели.

Комплексные плоские индикаторные панели.

^

1.2 Содержание лекционного материала (12 часов)

1.2.1 Полупроводниковые и гибридные ИМС (2 часа).

1.2.2 Схемотехника и параметры операционного усилителя (2 часа).

1.2.3 Логические функции и логические элементы (2 часа).

1.2.4 Программируемые логические контроллеры в автоматических системах (2 часа).

1.2.5 Оптоэлектронные устройства контроля, автоматики и управления (2 часа).

1.2.6 Источники вторичного электропитания (2 часа).

^

1.3 Содержание лабораторных работ (10 часов)

1.3.1 Исследования схем на логических элементах и триггерах (4 часа).

1.3.2 Исследование функциональных возможностях операционного усилителя (4 часа).

1.3.3 Ознакомление и работа с МП серии i8080 (8085) (2 часа).

^

2 Методические указания по дисциплине

К разделу 1.1.1. Интегральные микросхемы (ИМС) [1, 2] делятся по конструктивно-технологическому признаку (монолитные и гибридные) и по функциональному назначению (цифровые и аналоговые). Все они делятся по степени интеграции на четыре группы. В настоящее время в электроэнергетике пока используется ИМС первый и второй групп. ИМС третьей и четвертой групп используются в аппаратах иностранных фирм (Сименс, Моторолла, АББ и др.).

К числу основных компонентов, используемых в качестве основы для большого числа узлов автоматических устройств различного функционального назначения, относятся операционные усилители (ОУ) [1, 2, 6]. Интегральный ОУ - высококачественный усилитель постоянного тока с большим коэффициентом усиления, высоким входным и низким выходным сопротивлениями, малыми входными токами. Их параметры приводятся в справочных таблицах [1, 2, 6, 7]. ОУ включаются на двухполярное питание или по специальным схемам - на однополярное. Каждый ОУ имеет свою типовую схему включения [6], которая предусматривает наравне с информационными входами (неинвертирующий и инвертирующий) и одним выходом подключение цепей частотный коррекции и стабилизации нулевой точки. При наличии отрицательной обратной связи (по напряжению, по току) ОУ применяется в схемах входных и решающих усилителей, в преобразователях - напряжение в ток, ток в напряжение, [1] а при больших входных токах - как самостоятельный элемент в фильтрах низкой и высокой частоты, в заградительных (режекторных) фильтрах.

Аналоговый коммутатор выполняет функцию по коммутации непрерывно меняющихся сигналов. В ИМС они реализуются посредством ОУ и полевого транзистора, выполняющего функцию управляемого резистора. Этот принцип изложен в [1, 2]. Компаратор – разновидность аналогового коммутатора. Как правило, это ОУ без обратный связи [2]. Он осуществляет сравнение напряжение аналогового сигнала с эталонным (заданным).

К разделу 1.1.2. Микропроцессор (МП) - единый электронный компонент, управляемый программным способом, осуществляющий обработку цифровой информации и управление. МП рассматривается как ИМС и как вычислительное устройство [3].

Общепринятая аббревиатура для микропроцессорного устройства MPU обозначает просто микропроцессор МП. В микро- ЭВМ MPU используется в качестве центрального обрабатывающего устройства (СРU). Оно координирует действия и управляет работой отдельных частей микро- ЭВМ, выполняя также все арифметические и логические операции и осуществляя передачу информации от одного устройства к другому.

Для микро- ЭВМ также, как и для МП, требуется постоянные запоминающее устройство ПЗУ (ROM), допускающее только считывание, и оперативное запоминающее устройство ОЗУ (RAM), т.е память для считывания и записи. В микро- ЭВМ требуются специальные вводные и выходные устройства связи (порты) для подсоединение ЦП к внешним устройствам (периферийное оборудование). Данные передаются по 8-разрядной шине передачи данных.

Для передачи команд к различным устройствам необходимы еще управляющие и адресные линии (16 адресных линий - адресная шина). Система линий передачи данных, адресации, управления и питания образует шинную структуру (это шинная система S100 и система Е78).

МП, память, клавиатура, дисплей – все это есть аппаратурное обеспечение. К программному обеспечению относятся программы. Меняя программы, можно заставить аппаратуру выполнять различные функции. Аппаратные средства и связи между ними отображаются в виде структурной схемы МП (архитектура).

Изначально МП были созданы в качестве программно-управляемых устройств для автоматизации промышленных объектов и бытовой техники.

На их основе были созданы программируемые логические контроллеры (ПЛК). Управляющий контроллер-модуль, обеспечивающий логику работы устройства. Физически он представляет блок, имеющий набор выходов и входов для подключения датчиков и исполнительных механизмов. ПЛК - это управляемый дискретный автомат.

МП и ПЛК содержат элементы дискретной и цифровой техники. Используется пять операции: НЕ (NOT), И (AND), ИЛИ (OR), И-НЕ (NAND) и ИЛИ-НЕ (NOR). Каждая из них реализуется на логических элементах (Д-3). Один из путей упрощения разработки электронных логических комбинационных схем состоит в использовании инвертора в качестве основного «строительного» блока. Этот принцип реализуется при использовании КМОП - структур. Два инвертора, соединенные последовательно, образует буфер. На его базе строятся логические элементы И-НЕ, ИЛИ-НЕ. Для этих целей применяются логические элементы, выполненные по КМОП - технологии (К561, К564) [6].

Логические элементы, включенные по определенным схемам, образуют арифметические устройства – полу- и полный сумматор. Если полные сумматоры соединить особым образом, то получим сумматор с последовательным переносом. Логические элементы применяются в схемах мультиплексора, демультиплексора, шифратора, дешифратора.

В МП находят широкое применение последовательностные элементы – триггера. Надо использовать один тип триггера – JK-триггер. На основе этого триггера можно образовать D-триггер, счетный триггер Т. На триггерах строятся двоичные и двоично-десятичные счетчики импульсов. На последовательно соединенных триггерах строятся сдвиговые регистры, которые служат для приема и выдачи данных.

К разделу 1.1.3. Оптоэлектронные устройства [1] начали широко применяться для управления мощными тиристорами и семисторами, для защиты вторичных источников питания, коммутации индикаторов, для согласования схем управления с индикаторным табло, а также для гальванической развязки цепей управления и сигнализации. Для этих целей применяются оптоэлектронные элементарные пары, а также ИМС серий К249, К262, К293, К295, К415 и К490.

К разделу 1.1.4. В настоящее время стремятся улучить характеристики источников вторичного питания (ИВП). Для выпрямителей и стабилизаторов ИВП имеются специализированные ИМС серии К275, К299, К286.

ИМС серии К275 представляют комплект стабилизаторов с фиксированными выходным напряжением от 1 до 24В. ИМС для питания и для работы в импульсных устройствах изложены весьма подробно в [7].

К разделу 1.1.5. В электроэнергетике используются электролюминесцентные кнопки, экраны, панели. Буквенно-цифровая информация отображается при помощи жидкокристаллических экранов, табло матричного типа. Необходимо обратить внимание на способы их присоединения к МП и PCI.

^

3 Задания для контрольной работы

3.1 Задача 1

Рассчитать параметры выбранной инвертирующей (неинвертирующей) схемы усилителя на ИМС ОУ заданного типа (таблица 3.1), которая сможет обеспечить:

- линейные усиление входного сигнала заданной формы (таблица 3.2) с амплитудой А (таблица 3.3) до уровня Um (таблица 3.4);

- произвести интегрирование и дифференцирование этого сигнала (таблица 3.5, 3.6).

Исходные данные

Таблица 3.1 – Тип ОУ

| Вариант. Первая буква фамилии студента | |||||||

| Тип ИМС | А, Б, Ю, Я | В, Г, Щ, Э | Д, Е, Ч, Ш | Ж, З, Х, Ц | И, К, У, Ф | Л, М, С, Т | Н, О, П, Р |

| ОУ | К, КР, 140УД7 | К, КР, 140УД8 | К, КР, 140УД9 | К, КР, 140УД11 | К, КР, 154УД3 | К, КР, 574УД2А | К, КР, 140УД17 |

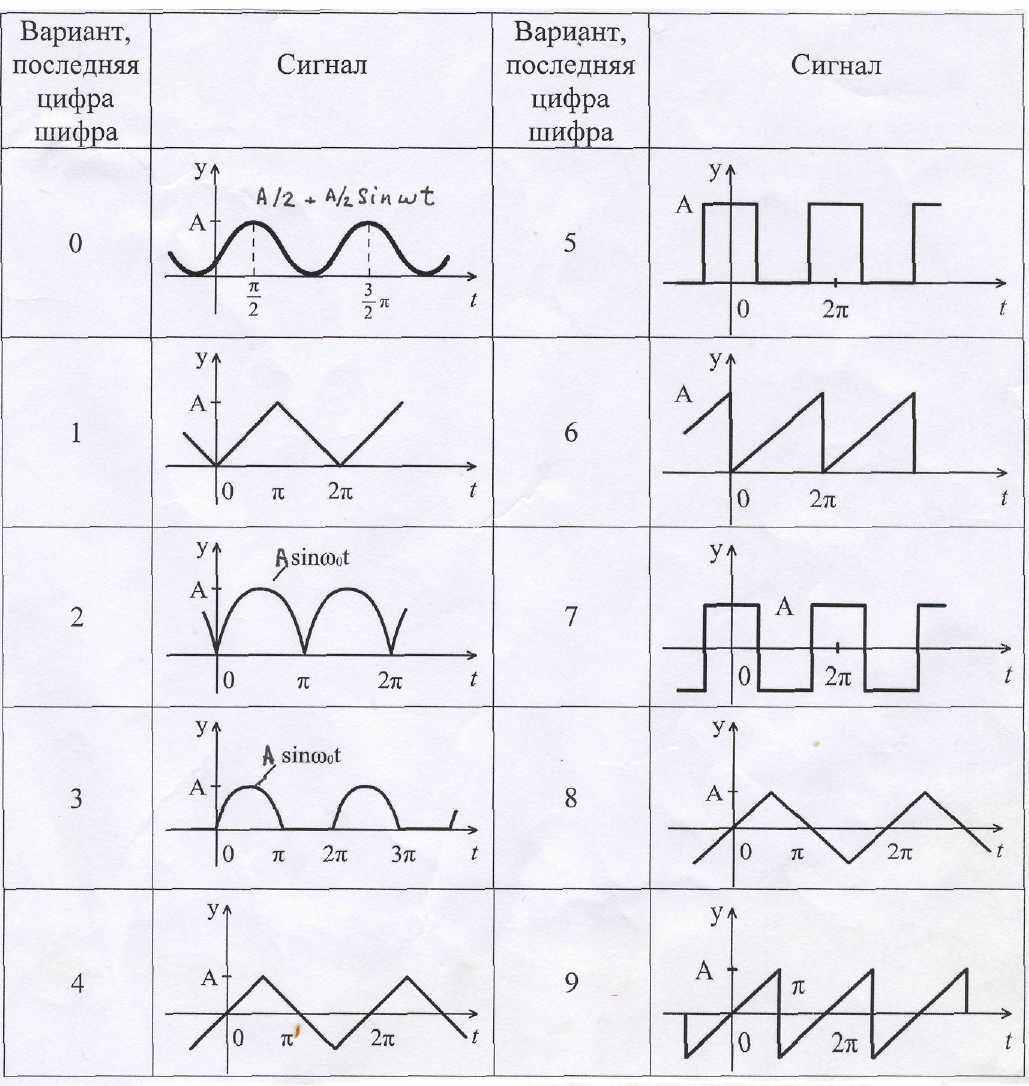

Таблица 3.2 – Входной сигнал

Таблица 3.2 – Входной сигналТаблица 3.3 – Амплитуда входного сигнала

| Амплитуда | Вариант, последняя Кп и предпоследняя Кпр цифра шифра |

| А, мВ | А=401+Кп+Кпр |

Таблица 3.4 – Амплитуда выходного сигнала

| Вариант, предпоследняя цифра шифра | ||||||||||

| Амплитуда | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| Um, В | 3,0 | 3,5 | 4,0 | 4,5 | 5,0 | 5,5 | 6,0 | 6,5 | 7,0 | 7,5 |

| Частота, кГц | 0,05 | 0,1 | 0,5 | 1,0 | 3 | 5 | 0,6 | 4 | 2 | 6 |

Таблица 3.5 – Значение емкости конденсатора

| Вариант, первая буква фамилии | |||||||

| Емкость | А, Ж, О, У | В, И, Р, Ш | Г, Л, Х, Ю | Б, З, П, Э | Д, Т, Ф, Ч | Е, М, С, Ш | К, Н, Ш, Я |

| С, мкФ | 0,01 | 0,05 | 0,1 | 0,15 | 0,2 | 0,25 | 0,3 |

Таблица 3.6 – Значения сопротивления

| Вариант, первая буква имени | |||||||

| Сопротивление | А - Г | Д - З | И - М | Н - Р | С - Ф | Х - Ш | Щ - Я |

| R, кОм | 2 | 3 | 4 | 5 | 7 | 10 | 15 |

^ Руководство к выполнению

Из литературы [1, 2, 6] необходимо выписать параметры и типовую схему включения заданного ОУ. Затем необходимо нарисовать требуемую схему усилителя. Для инвертирующей схемы линейного усилителя коэффициент усиления равен

(3.1)

(3.1)где R1 – входные сопротивление схемы;

R2 – сопротивление цепи обратной связи.

Расчетные значения полученных резисторов следует скорректировать в соответствии с установленными стандартами рядом номинальных величин. Это повлияет на значение Um.

Необходимо нарисовать в установленном масштабе кривые входного и выходного напряжения.

В схеме интегратора и дифференциатора выходные напряжение определяется

(3.2)

(3.2)где U(t) – мгновенные входное напряжение;

- постоянная времени.

- постоянная времени.3.2 Задача 2

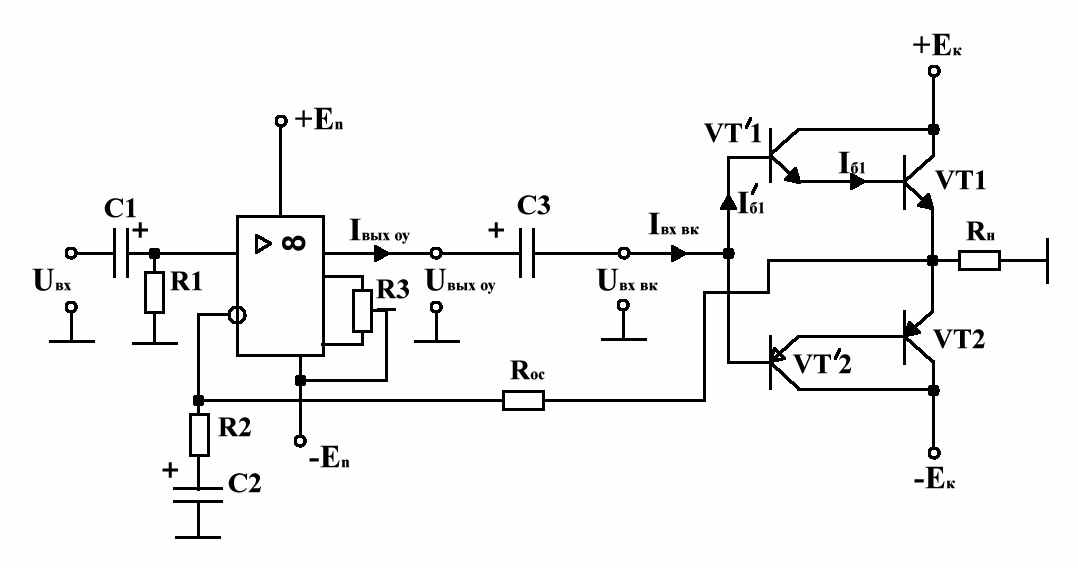

Разработать схему и рассчитать параметры низкочастотного усилителя мощности (УМ), предназначенного для усиления по току входного сигнала (таблицы 3.2, 3.3) с целью выделения полной мощности P (таблица 3.7) на активной нагрузке R (таблица 3.8). В качестве предварительного усилителя применить ОУ (таблица 3.1) и в качестве выходного каскада – бустерный каскад на комплементарных транзисторах.

Исходные данные

Таблица 3.7 – Мощности нагрузки

| Вариант, последняя цифра шифра | ||||||||||

| Мощность | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| P, Вт | 1,0 | 1,5 | 2,0 | 2,5 | 3,0 | 3,5 | 4,0 | 4,5 | 5,0 | 5,5 |

Таблица 3.8 – Сопротивления нагрузки

| Вариант, предпоследняя цифра шифра | ||||||||||

| Нагрузка | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| R, Ом | 4 | 5 | 6 | 7 | 8 | 2 | 3,5 | 4,5 | 6,5 | 9 |

^ Руководство к выполнению

Бестрансформаторные выходные каскады [1, 2] получили преимущественное распространение. Они позволяют осуществить непосредственную связь с нагрузкой, что дает возможность обойтись без громоздких трансформаторов и разделительных конденсаторов; имеют хорошие частотные и амплитудные характеристики; легко могут быть выполнены по интегральной технологии. Кроме того, в связи с отсутствием частотно-зависимых элементов в цепях связи между каскадами можно вводить глубокие общие отрицательные ОС как по переменному, так и по постоянному токам, что существенно улучшает характеристики преобразования всего устройства.

Схема УМ весьма простая (рисунок 3.1) ОУ следует включить в схему неинвертирующего усилителя. Выходной ток ОУ определяется выходным напряжением (порядка 10-12 В) и минимальным сопротивлением нагрузки (2 кОм). Во всех случаях этот ток не превышает 6-10 мА. В качестве выходного каскада используется двухтактная схема на составных комплементарных транзистарах: мощных КТ814 - КТ816 (КТ815 - КТ817) и маломощных КТ503, КТ502 (КТ315, КТ361). Эти транзисторы включается по схеме с общим коллектором ОК (эмиттерные повторители).

Рисунок 3.1 – Схема усилителя мощности

Мощность, выделяемая в нагрузке, определяет амплитудные значения тока и напряжения в выходной цепи

(3.3)

(3.3)Это позволяет найти максимальные значения коллекторного тока и напряжения. С учетом конструктивного коэффициента (1,1 – 1,2) эти токи и напряжения позволяют выбрать параметры выходного транзистора по току, по напряжению и по мощности.

Напряжение источника питания можно из учета коэффициента полезного действия транзисторного каскада в схеме с ОК, который равен 0,785. Для двухтактной схемы на комплементарных транзисторах требуется стандартный двухполярный источник питания. Коэффициент усиления по току, равный отношению тока базы выходного транзистора к выходному току ОУ, определяет общий коэффициент усиления транзисторов по току.

Обратная отрицательная связь, которая обеспечивает стабилизацию напряжения в эмиттерных цепях выходного каскада, обеспечивает условия

(3.4)

(3.4)где R1 – входное сопротивление (50 – 100 кОм);

R2 – сопротивление цепи обратной связи. Необходимо привести принципиальную схему УМ.

3.3 Задача 3

Спроектировать схему 8-разрядного регистра для микропроцессора, позволяющую записывать и считывать данные в последовательной и параллельной форме. Какое число будет находится в регистре после подачи управляющего числа А, если предварительно было установлено число В.

^ Исходные данные

Число А выбирается как сумма 6+ последняя цифра шифра студента.

Число В выбирается как сумма 5+ сумма последних двух цифр шифра студента.

^ Руководство к выполнению

Регистр можно организовать на базе D– или JK– триггеров с включением логических элементов между триггерами. Чтобы организовать различные пути для прохождения данных, можно воспользоваться логической операцией И. Более просто поставленная задача может быть решена, если применить ИМС сдвигающего регистра серий 564 (561).

3.4 Задача 4

Используя команды микропроцессора Intel 8080/8085, составить программу непрерывного вычисления на микро- ЭВМ заданного логического выражения и разместить ее в памяти, начиная с нулевой ячейки.

Переменные X, Y, Z и соответствующие им номера портов, через которые они вводятся в микро- ЭВМ, представлены в виде десятичных чисел, поэтому перед решением задачи их необходимо перевести в шестнадцатеричный вид.

Микро- ЭВМ имеет 2 порта ввода с номерами 07, 08 и один порт вывода с номером 05. Число X вводится в порт 07, число Y вводится в порт 08, а число G выводится из порта 05.

Исходные данные

Таблица 3.9 – Исходный алгоритм

| Вариант последняя цифра шифра | Алгоритм вычисления | X10 | Y10 | Z10 | Начальный адрес программы | Порты ввода | Порт вывода |

| 0 | G = X +Y+Z-1 | 49 | 52 | 88 | 82EB | 10,11,12 | 21 |

| 1 | G = X +Y+Z | 100 | 52 | 116 | 82DF | 25,26,27 | 05 |

| 2 | G = X +Y- Z | 120 | 85 | 50 | 821E | 01,03,05 | 45 |

| 3 | G = X - Y- Z | 255 | 150 | 22 | 80FF | 10,20,30 | 40 |

| 4 | G = X - Y+Z | 168 | 160 | 220 | 82DC | 15,16,17 | 18 |

| 5 | G = X +Y+ 1 | 250 | 38 | - | 808B | 33,22 | 02 |

| 6 | G = X - Y+1 | 125 | 15 | - | 810F | 21,22 | 09 |

| 7 | G = X +Y -1 | 175 | 80 | - | 81EE | 29,30 | 22 |

| 8 | G = X – Z+1 | 200 | 105 | - | 81AD | 77,78 | 87 |

| 9 | G = X -Y-1 | 205 | 25 | - | 81DD | 04,05 | 14 |

Руководство к выполнению

Допустим, по варианту задан вычислительный алгоритм в виде

G = X + Y – 1. (3.5)

Программа начинается с однобайтовых пересылок содержимого ПОРТА 08 в аккумулятор А, а из него в регистр С. Далее в аккумулятор пересылается содержимое ПОРТА 07. Из результата, полученного после команды арифметического сложения А(Х)+C(Y), вычитается 1, и результат выводится в ПОРТ 05. Все вышеперечисленные действия представим в виде блок-схемы алгоритма на рисунке 3.2.

По алгоритму рисунка 3.2 составим листинг программы на символическом языке ассемблера и представим его в виде таблицы 3.9. Данные в этой таблице сгруппированы в три колонки. В левой − перечислены шестнадцатеричные адреса памяти. В средней − мнемонические обозначения команд и операнды, участвующие в вычислениях. В правой колонке даются пояснения, с помощью которых легче разобраться в программе.

Таблица 3.10 - Листинг программы на символическом языке ассемблер

| Адрес | Мнемокод | Комментарий |

| 0000 | IN | AY |

| 0001 | 08 | |

| 0002 | MOV C,A | CA |

| 0003 | IN | AX |

| 0004 | 07 | |

| 0005 | ADD С | AX+Y |

| 0006 | DCR A | A A-l |

| 0007 | OUT | Выход A |

| 0008 | 05 | |

| 0009 | HLT | остановка |

3.5 Задача 5

Осуществить программную реализацию временной задержки длительностью 100 мкс.

^ Руководство к выполнению

Поскольку задана временная задержка небольшой длительности, применим способ ее реализации, организовав циклический участок программы. Блок-схема, описывающая этот метод формирования временных задержек, приведена на рисунке 3.3. Как видно из этого рисунка, правее каждого блока приведена соответствующая команда и произведен расчет времени ее выполнения при условии, что тактовая частота микропроцессора fr =2 МГц ( Тт=0,5 мкс).

Д

ля нахождения числа X проанализируем содержимое рисунка 3.3. Отметим, что команды 1, 2 и 5 используются один раз, и их длительность составляет t 1-2-5= 8,5+3,5+5=17 мкс. Для получения задержки времени 100 мкс команды 3 и 4 надо повторять столько раз, чтобы этот процесс выполнялся за 100-17=83 мкс. Время же выполнения команд DCR В и JNZ Ml составляет tз-А=2,5+5=7,5 мкс. Число 83 не делится ровно на 7,5. Если задать X=10, то 7,5•10=75 мкс, что меньше числа 83 на 8 мкс. Для точного воспроизведения задержки в 83 мкс нужно добавить четыре пустых команды NOP (4·2 мкс=8 мкс). Исходя из приведенного расчета, текст подпрограммы TIME примет вид таблицы 3.11.

ля нахождения числа X проанализируем содержимое рисунка 3.3. Отметим, что команды 1, 2 и 5 используются один раз, и их длительность составляет t 1-2-5= 8,5+3,5+5=17 мкс. Для получения задержки времени 100 мкс команды 3 и 4 надо повторять столько раз, чтобы этот процесс выполнялся за 100-17=83 мкс. Время же выполнения команд DCR В и JNZ Ml составляет tз-А=2,5+5=7,5 мкс. Число 83 не делится ровно на 7,5. Если задать X=10, то 7,5•10=75 мкс, что меньше числа 83 на 8 мкс. Для точного воспроизведения задержки в 83 мкс нужно добавить четыре пустых команды NOP (4·2 мкс=8 мкс). Исходя из приведенного расчета, текст подпрограммы TIME примет вид таблицы 3.11.Таблица 3.11 –Текст подпрограммы TIME

| Адрес | Машкод | Метка | Мнемокод | Комментарий |

| 8200 8201 | 06 0А | TIME | MVIB 0AH | Загрузить в регистр В число Х=1010=0А16 |

| 8202 | 05 | Ml | DCR B | Уменьшить на 1 содержимое регистра В |

| 8203 8204 8205 | С2 02 82 | | JNZ Ml | ^ Повторить процесс, если результат предыдущей операции не равен нулю, т.е. при В  0 0 |

| 8206 | 00 | | NOP | Пустая операция |

| 8207 | 00 | | NOP | » |

| 8208 | 00 | | NOP | » |

| 8209 | 00 | | NOP | » |

| 820А | С9 | | RET | Возврат в основную программу, если В = 0 |

Список литературы

1. Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника: Учебник для вузов. – 3-е изд., перераб. и доп. - М.: Высш.шк., 2004. – 792 с.

2. Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника: Учебник для вузов. – М.: Горячая линая – Телеком, 2005. – 768 с.

3. Калабеков Б.А. Цифровые устройства и микропроцессорные системы: Учебник для вузов. – 2-е изд., перераб. и доп. – М.: Горячая линия – Телеком, 2000. – 336 с.

4. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учебное пособие для вузов. – М.: Радио и связь, 1992. – 257 с.

5. Нестеренко Б.К. Интегральные операционные усилители. Справочное пособие по применению. – М.: Энергоиздат, 1982. – 128 с.

6. Бирюков С.А. Цифровые устройства на МОП – интегральных микросхемах. – 2-е изд., переаб. и доп. – М.: Радио и связь, 1996. – 192 с.

7. Новаченко И.В., Теллец В.А., Краснодубец Ю.А. Интегральные схемы для радиоаппаратуры. – М.: Радио и связь, 1995. – 320 с.