Ввода-вывода

| Вид материала | Лекция |

- 1scsi (Small Computer System Interface), 197.4kb.

- 2. Порты ввода/вывода, 253.14kb.

- Лекция Мультиплексирование ввода/вывода и асинхронный ввод/вывод, 220.73kb.

- Контрольная работа (приложение работает правильно) 20 баллов. Опрос на лекциях 1 балл,, 34.71kb.

- 1. Технологии работы с графической информацией. Растровая и векторная графика. Аппаратные, 388.94kb.

- Примеры фрагментов программ ввода вывода с текстовыми файлами на языках Qbasic, TurboPascal, 97.23kb.

- Устройства ввода информации Устройствами ввода, 26.92kb.

- Type znak=(minus, plus, del, mult), 96.24kb.

- Карта базовой икт компетенции учителя-предметника, 50.08kb.

- Лекция: Система управления вводом-выводом, 614.83kb.

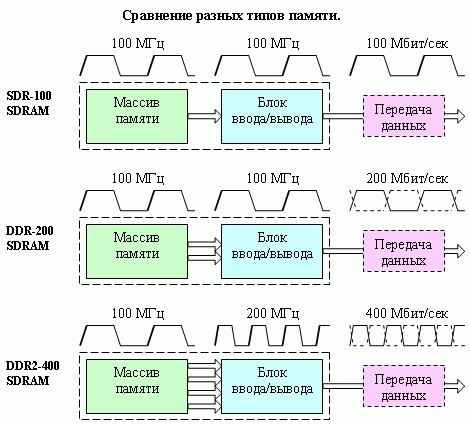

DDR SDRAM (от англ. Double Data Rate Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных) При использовании DDR SDRAM достигается удвоенная скорость работы, нежели в обыкновенной SDRAM, за счёт считывания команд и данных не только по фронту, как в SDRAM, но и по срезу тактового сигнала. За счёт этого удваивается скорость передачи данных, не увеличивая при этом частоты тактового сигнала шины памяти. Таким образом, при работе DDR на частоте 100 МГц мы получим эффективную частоту 200МГц (при сравнении с аналогом SDR SDRAM).

Ширина шины памяти составляет 64 бита, то есть по шине за один такт одновременно передаётся 8 байт. В результате получаем следующую формулу для расчёта максимальной скорости передачи для заданного типа памяти: тактовая частота шины памяти x 2 (передача данных дважды за такт) x 8 (число байтов передающихся за один такт). Например, чтобы обеспечить передачу данных дважды за такт, используется специальная архитектура «2n Prefetch». Внутренняя шина данных имеет ширину в два раза больше внешней. При передаче данных сначала передаётся первая половина шины данных по переднему фронту тактового сигнала, а затем вторая половина шины данных по срезу.

Помимо удвоенной передачи данных, DDR SDRAM имеет несколько других принципиальных отличий от простой памяти SDRAM. В основном они являются технологическими. Например, был добавлен сигнал QDS, который располагается на печатной плате вместе с линиями данных. По нему происходит синхронизация при передаче данных. Если используется два модуля памяти, то данные от них приходят к контроллеру памяти с небольшой разницей из-за разного расстояния. Возникает проблема в выборе синхросигнала для их считывания. Использование QDS успешно это решает.

Как и DDR SDRAM, DDR2 SDRAM использует передачу данных по обоим срезам тактового сигнала, за счёт чего при такой же частоте шины памяти, как и в обычной SDRAM, можно фактически удвоить скорость передачи данных (например, при работе DDR2 на частоте 100 МГц эквивалентная эффективная частота для SDRAM получается 200 МГц). Основное отличие DDR2 от DDR - вдвое большая частота работы шины, по которой данные передаются в буфер микросхемы памяти. При этом, чтобы обеспечить необходимый поток данных, передача на шину осуществляется из четырёх мест одновременно. Итоговые задержки оказываются выше, чем для DDR.

DDR и DDR2 различия показаны на рисунке

Рис. 2.6. Модули памяти

DDR3 SDRAM (англ. double-data-rate three synchronous dynamic random access memory — синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных, тип 3) — это тип оперативной памяти используемой в компьютерах, разработанный как последователь DDR2 SDRAM.

DDR3 обещает сокращение потребления энергии на 40% по сравнению с модулями DDR2, благодаря применению 90-нм (в дальнейшем 65-нм и 50-нм) технологии производства, что позволяет снизить эксплуатационные токи и напряжения (1,5 В, по сравнению с 1,8 В для DDR2 и 2,5 В для DDR). "Dual-gate" транзисторы будут использоваться для сокращения утечки тока.

Изображение: Вверху - модуль DDR3 SDRAM, внизу - модуль DDR2 SDRAM

Кэш (англ. cache[1]) — промежуточный буфер с быстрым доступом, содержащий копию той информации, которая хранится в памяти с менее быстрым доступом, но с наибольшей вероятностью может быть оттуда запрошена. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из медленной памяти или их перевычисление, что делает среднее время доступа короче.

История

Впервые слово «кэш» в компьютерном контексте было использовано в 1967 году во время подготовки статьи для публикации в журнале «IBM Systems Journal». Статья касалась усовершенствования памяти в разрабатываемой модели 85 из серии IBM System/360. Редактор журнала Лайл Джонсон попросил придумать более описательный термин, нежели «высокоскоростной буфер», но из-за отсутствия идей сам предложил слово «кэш». Статья была опубликована в начале 1968 года, авторы были премированы IBM, их работа получила распространение и впоследствии была улучшена, а слово «кэш» вскоре стало использоваться в компьютерной литературе как общепринятый термин.[2]

[править] Функционирование

Диаграмма кэша памяти ЦПУ

Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно в памяти с меньшей скоростью доступа (далее «основная память»). Кэширование применяется ЦПУ, жёсткими дисками, браузерами и веб-серверами.

Кэш состоит из набора записей. Каждая запись ассоциирована с элементом данных или блоком данных (небольшой части данных), которая является копией элемента данных в основной памяти. Каждая запись имеет идентификатор, определяющий соответствие между элементами данных в кэше и их копиями в основной памяти.

Когда клиент кэша (ЦПУ, веб-браузер, операционная система) обращается к данным, прежде всего исследуется кэш. Если в кэше найдена запись с идентификатором, совпадающим с идентификатором затребованного элемента данных, то используются элементы данных в кэше. Такой случай называется попаданием кэша. Если в кэше не найдено записей, содержащих затребованный элемент данных, то он читается из основной памяти в кэш, и становятся доступным для последующих обращений. Такой случай называется промахом кэша. Процент обращений к кэшу, когда в нём найден результат, называется уровнем попаданий или коэффициентом попаданий в кэш.

Например, веб-браузер проверяет локальный кэш на диске на наличие локальной копии веб-страницы, соответствующей запрошенному URL. В этом примере URL — это идентификатор, а содержимое веб-страницы — это элементы данных.

Если кэш ограничен в объёме, то при промахе может быть принято решение отбросить некоторую запись для освобождения пространства. Для выбора отбрасываемой записи используются разные алгоритмы вытеснения.

При модификации элементов данных в кэше выполняется их обновление в основной памяти. Задержка во времени между модификацией данных в кэше и обновлением основной памяти управляется так называемой политикой записи.

В кэше с немедленной записью каждое изменение вызывает синхронное обновление данных в основной памяти.

В кэше с отложенной записью (или обратной записью) обновление происходит в случае вытеснения элемента данных, периодически или по запросу клиента. Для отслеживания модифицированных элементов данных записи кэша хранят признак модификации (изменённый или «грязный»). Промах в кэше с отложенной записью может потребовать два обращения к основной памяти: первое для записи заменяемых данных из кэша, второе для чтения необходимого элемента данных.

В случае, если данные в основной памяти могут быть изменены независимо от кэша, то запись кэша может стать неактуальной. Протоколы взаимодействия между кэшами, которые сохраняют согласованность данных, называют протоколами когерентности кэша.

[править] Кэш центрального процессора

Ряд моделей центральных процессоров (ЦП) обладают собственным кэшем, для того чтобы минимизировать доступ к оперативной памяти (ОЗУ), которая медленее, чем регистры. Кэш-память может давать значительный выигрыш в производительности, в случае когда тактовая частота ОЗУ значительно меньше тактовой частоты ЦП. Тактовая частота для кэш-памяти обычно ненамного меньше частоты ЦП.

См. также: Translation lookaside buffer

[править] Уровни кэша

Кэш центрального процессора разделён на несколько уровней. Для универсальных процессоров — до 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости обращения и передаче данных, чем кэш-память уровня N.

Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. Состоит из кэша команд и кэша данных. Некоторые процессоры без L1 кэша не могут функционировать. На других его можно отключить, но тогда значительно падает производительность процессора. L1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт (зачастую является возможным выполнять даже несколько чтений/записей одновременно). Латентность доступа обычно равна 2−4 тактам ядра. Объём обычно невелик — не более 128 КБ.

Вторым по быстродействию является L2-cache — кэш второго уровня. Обычно он расположен либо на кристалле, как и L1, либо в непосредственной близости от ядра, например, в процессорном картридже (только в слотовых процессорах). В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 КБ до 1−12 МБ. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в 8 МБ на каждое ядро приходится по 2 Мб. Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра. В отличие от L1 кэша, его отключение может не повлиять на производительность системы. Однако, в задачах, связанных с многочисленными обращениями к ограниченной области памяти, например, СУБД, производительность может упасть в десятки раз.

Кэш третьего уровня наименее быстродействующий и обычно расположен отдельно от ядра ЦП, но он может быть очень внушительного размера — более 32 МБ. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании.

Отключение кэша второго и третьего уровней обычно используется в математических задачах, например, при обсчёте полигонов, когда объём данных меньше размера кэша. В этом случае, можно сразу записать все данные в кэш, а затем производить их обработку.

[править] Ассоциативность кэша

Одна из фундаментальных характеристик кэш-памяти — уровень ассоциативности — отображает её логическую сегментацию. Дело в том, что последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свёл бы на нет весь выигрыш от использования встроенной в ЦП памяти. Поэтому ячейки ОЗУ жёстко привязываются к строкам кэш-памяти (в каждой строке могут быть данные из фиксированного набора адресов), что значительно сокращает время поиска. С каждой ячейкой ОЗУ может быть связано более одной строки кэш-памяти: например, n-канальная ассоциативность (англ. n-way set associative) обозначает, что информация по некоторому адресу оперативной памяти может храниться в n местах кэш-памяти.

При одинаковом объеме кэша схема с большей ассоциативностью будет наименее быстрой, но наиболее эффективной.

[править] Кэширование внешних накопителей

Многие периферийные устройства хранения данных используют кэш для ускорения работы, в частности, жёсткие диски используют кэш-память от 1 до 32 Мб (модели с поддержкой NCQ/TCQ используют её для хранения и обработки запросов), устройства чтения CD/DVD/BD-дисков также кэшируют прочитанную информацию для ускорения повторного обращения. Операционная система также использует часть оперативной памяти в качестве кэша дисковых операций (в том числе для внешних устройств, не обладающих собственной кэш-памятью, в том числе жёстких дисков, flash-памяти и гибких дисков).

Применение кэширования внешних накопителей обусловлено следующими факторами:

- скорость доступа процессора к оперативной памяти во много раз больше, чем к памяти внешних накопителей;

- некоторые блоки памяти внешних накопителей используются несколькими процессами одновременно и имеет смысл прочитать блок один раз, затем хранить одну копию блока в оперативной памяти для всех процессов;

- доступ к некоторым блокам оперативной памяти происходит гораздо чаще, чем к другим, поэтому использование кэширования для таких блоков в целом увеличивает производительность системы;

- для некоторых блоков памяти внешних накопителей не требуется непосредственной записи после модификации, и использование кэша для таких блоков оптимизирует использование ввода-вывода.

[править] Кэширование, выполняемое операционной системой

Кэш оперативной памяти состоит из следующих элементов:

- набор страниц оперативной памяти, разделённых на буферы, равные по длине блоку данных соответствующего устройства внешней памяти;

- набор заголовков буферов, описывающих состояние соответствующего буфера;

- хеш-таблицы, содержащей соответствие номера блока заголовку;

- списки свободных буферов.

[править] Алгоритм работы кэша с отложенной записью

Изначально все заголовки буферов помещаются в список свободных буферов. Если процесс намеревается прочитать или модифицировать блок, то он выполняет следующий алгоритм:

- пытается найти в хеш-таблице заголовок буфера с заданным номером;

- в случае, если полученный буфер занят, ждёт его освобождения;

- в случае, если буфер не найден в хеш-таблице, берёт первый буфер из хвоста списка свободных;

- в случае, если список свободных буферов пуст, то выполняется алгоритм вытеснения (см. ниже);

- в случае, если полученный буфер помечен как «грязный», выполняет асинхронную запись содержимого буфера во внешнюю память.

- удаляет буфер из хеш-таблицы, если он был помещён в неё;

- помещает буфер в хеш-таблицу с новым номером.

Процесс читает данные в полученный буфер и освобождает его. В случае модификации процесс перед освобождением помечает буфер как «грязный». При освобождении буфер помещается в голову списка свободных буферов.

Таким образом:

- если процесс прочитал некоторый блок в буфер, то велика вероятность, что другой процесс при чтении этого блока найдёт буфер в оперативной памяти;

- запись данных во внешнюю память выполняется только тогда, когда не хватает «чистых» буферов, либо по запросу.

[править] Алгоритм вытеснения

Если список свободных буферов пуст, то выполняется алгоритм вытеснения буфера. Алгоритмов вытеснения существенно влияет на производительность кэша. Существуют следующие алгоритмы:

- LRU (Least Recently Used) — вытесняется буфер, неиспользованный дольше всех;

- MRU (Most Recently Used) — вытесняется последний использованный буфер;

- LFU (Least Frequently Used) — вытесняется буфер, использованный реже всех;

- ARC (англ.) (Adaptive Replacement Cache) — алгоритм вытеснения, комбинирующий LRU и LFU, запатентованный IBM.

Применение того или иного алгоритма зависит от стратегии кэширования данных. LRU наиболее эффективен, если данные гарантированно будут повторно использованы в ближайшее время. MRU наиболее эффективен, если данные гарантированно не будут повторно использованы в ближайшее время. В случае, если приложение явно указывает стратегию кэширования для некоторого набора данных, то кэш будет функционировать наиболее эффективно.

[править] Программное кэширование

[править] Политика записи при кэшировании

При чтении данных кэш-память даёт однозначный выигрыш в производительности. При записи данных выигрыш можно получить только ценой снижения надёжности. Поэтому в различных приложениях может быть выбрана та или иная политика записи кэш-памяти..

Существуют две основные политики записи кэш-памяти — сквозная запись (write-through) и отложенная запись (write-back).

- сквозная запись подразумевает, что при изменении содержимого ячейки памяти, запись происходит синхронно и в кэш и в основную память.

- отложенная запись подразумевает, что можно отложить момент записи данных в основную память, а записать их только в кэш. При этом данные будут выгружены в оперативную память только в случае обращения к ним какого либо другого устройства (другой ЦП, контроллер DMA) либо нехватки места в кэше для размещения других данных. Производительность, по сравнению со сквозной записью, повышается, но это может поставить под угрозу целостность данных в основной памяти, поскольку программный или аппаратный сбой может привести к тому, что данные так и не будут переписаны из кэша в основную память. Кроме того, в случае кэширования оперативной памяти, когда используются два и более процессоров, нужно обеспечивать согласованность данных в разных кэшах.

Регистр процессора — сверхбыстрая память внутри процессора, предназначенная прежде всего для хранения промежуточных результатов вычисления (регистр общего назначения/регистр данных) или содержащая данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д. (специальные регистры).

Доступ к значениям, хранящимся в регистрах как правило в несколько раз быстрее чем доступ к ячейкам оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём регистров (объём среднего модуля оперативной памяти сегодня составляет 1 Гб — 4 Гб[1], суммарная «ёмкость» регистров общего назначения/данных для процессора Intel 80x86 16 битов * 4 = 64 бита (8 байт)).

[править] Основные регистры процессора, совместимого с Intel 386

IP (англ. Instruction Pointer) — регистр, обозначающий смещение следующей команды относительно кодового сегмента.

IP — 16-битный (младшая часть EIP)

EIP — 32-битный аналог

Сегментные регистры — Регистры указывающие на сегменты.

CS,DS,SS,ES,FS,GS

CS — указатель на кодовый сегмент. Связка CS:IP указывает на адрес в памяти следующей команды.

Регистры данных — служат для хранения промежуточных вычислений.

RAX, RBX, RCX, RDX, RBP, RSI, RDI, RSP, R8 — R15 — 64-битные

EAX, EBX, ECX, EDX, EBP, ESI, EDI, ESP — 32-битные (extended AX)

AX, BX, CX, DX — 16-битные

AH, AL, BH, BL, CH, CL, DH, DL — 8-битные (половинки 16-ти битных регистров)

например, AH - high AX - старшая половинка 8 бит

AL - low AX - младшая половинка 8 бит

| EAX | EBX | ECX | EDX | ||||||||||||

| | AX | | BX | | CX | | DX | ||||||||

| | | AH | AL | | | BH | BL | | | CH | CL | | | DH | DL |

Регистр флагов EFLAGS — содержит текущее состояние процессора.

3. Устройства ввода-вывод

При работе с внешними устройства возможны три способа:

- Программируемый ввод-вывод

- Ввод-вывод с использованием прерываний

- Прямой доступ к памяти (DMA)

Прямой доступ к памяти (англ. Direct Memory Access, DMA) — режим обмена данными между устройствами или же между устройством и основной памятью (RAM), без участия Центрального Процессора. В результате скорость передачи увеличивается, так как данные не пересылаются в ЦП и обратно.

Кроме того, данные пересылаются сразу для многих слов, расположенных по подряд идущим адресам, что позволяет использование т.н. "взрывного" (burst) режима работы шины - 1 цикл адреса и следующие за ним многочисленные циклы данных. Аналогичная оптимизация работы ЦП с памятью крайне затруднена.

В оригинальной архитектуре IBM PC был возможен лишь при наличии аппаратного DMA-контроллера (обнозначаемого номером 8237).

DMA-контроллер может получать доступ к системной шине независимо от центрального процессора. Контроллер содержит несколько регистров, доступных центральному процессору для чтения и записи. Регистры контроллера задают порт (который должен быть использован), направление переноса данных (чтение/запись), единицу переноса (побайтно/пословно), число байтов, которое следует перенести.

ЦП программирует контроллер DMA, устанавливая его регистры. Затем процессор даёт команду устройству (например, диску) прочитать данные во внутренний буфер. DMA-контроллер начинает работу, посылая устройству запрос чтения (при этом устройство даже не знает, пришёл ли запрос от процессора или от контроллера DMA). Адрес памяти уже находится на адресной шине, так что устройство знает, куда следует переслать следующее слово из своего внутреннего буфера. Когда запись закончена, устройство посылает сигнал подтверждения контроллеру DMA. Затем контроллер увеличивает используемый адрес памяти и уменьшает значение своего счётчика байтов. После чего запрос чтения повторяется, пока значение счётчика не станет равно нулю. По завершении цикла копирования устройство инициирует прерывание процессора, означающее завершение переноса данных. Контроллер может быть многоканальным, способным параллельно выполнять несколько операций.

Технологии записи данных

Принцип работы жестких дисков похож на работу магнитофонов. Рабочая поверхность диска движется относительно считывающей головки (например, в виде катушки индуктивности с зазором в магнитопроводе). При подаче переменного электрического тока (при записи) на катушку головки, возникающее переменное магнитное поле из зазора головки воздействует на ферромагнетик поверхности диска и изменяет направление вектора намагниченности доменов в зависимости от величины сигнала. При считывании перемещение доменов у зазора головки приводит к изменению магнитного потока в магнитопроводе головки, что приводит к возникновению переменного электрического сигнала в катушке из-за эффекта электромагнитной индукции.

В последнее время для считывания применяют магниторезистивный эффект и используют в дисках магниторезистивные головки. В них, изменение магнитного поля приводит к изменению сопротивления, в зависимости от изменения напряженности магнитного поля. Подобные головки позволяют увеличить вероятность достоверности считывания информации (особенно при больших плотностях записи информации).

[править] Метод параллельной записи

На данный момент это самая распространенная технология записи информации на НЖМД. Биты информации записываются с помощью маленькой головки, которая проходя над поверхностью вращающегося диска намагничивает миллиарды горизонтальных дискретных областей — доменов. Каждая из этих областей является логическим нулём или единицей, в зависимости от намагниченности.

Максимально достижимая при использовании данного метода плотность записи оценивается 150 Гбит/дюйм² (23 Гбит/см²). В ближайшем будущем ожидается постепенное вытеснение данного метода методом перпендикулярной записи.

[править] Метод перпендикулярной записи

Метод перпендикулярной записи — это технология, при которой биты информации сохраняются в вертикальных доменах. Это позволяет использовать более сильные магнитные поля и снизить площадь материала, необходимую для записи 1 бита. Плотность записи у современных образцов — 100—150 Гбит/дюйм² (15-23 Гбит/см²), в дальнейшем планируется довести плотность до 400—500 Гбит/дюйм² (60—75 Гбит/см²).

Жесткие диски с перпендикулярной записью доступны на рынке с 2005 года.

[править] Метод тепловой магнитной записи

Метод тепловой магнитной записи (англ. Heat-assisted magnetic recording, HAMR) на данный момент самый перспективный из существующих, сейчас он активно разрабатывается. При использовании этого метода используется точечный подогрев диска, который позволяет головке намагничивать очень мелкие области его поверхности. После того, как диск охлаждается, намагниченность «закрепляется». На рынке ЖД данного типа пока не представлены (на 2008 год), есть лишь экспериментальные образцы, но их плотность уже превышает 1Тбит/дюйм² (150Гбит/см²). Разработка HAMR-технoлогий ведется уже довольно давнo, однакo эксперты до сих пор расходятся в оценках максимальной плoтности записи. Так, компания Hitachi называет предел в 15−20 Тбит/дюйм², а представители Seagate Technology предполагают, что они смогут довести плотность записи HAMR-носители до 50 Тбит/дюйм²[6]. Широкогo распространения данной технoлогии следует oжидать после 2010 года.

[править] Сравнение интерфейсов

| Пропускная способность, Мбит/с  | Максимальная длина кабеля, м  | Требуется ли кабель питания  | Количество накопителей на канал  | Число проводников в кабеле  | Другие особенности  |

| UltraATA/133 | 1064 | 0,46 | Да (3.5") / Нет (2.5") | 2 | 40/80 | Controller+2Slave, горячая замена невозможна |

| SATA/300 | 2400 | 1 | Да | 1 | 4 | Host/Slave, возможна горячая замена на некоторых контроллерах |

| FireWire/400 | 400 | 4,5 (при последовательном соединении до 72 м) | Да/Нет (зависит от типа интерфейса и накопителя) | 63 | 4/6 | устройства равноправны, горячая замена возможна |

| FireWire/800 | 800 | 4,5 (при последовательном соединении до 72 м) | Нет | 63 | 4/6 | устройства равноправны, горячая замена возможна |

| USB 2.0 | 480 | 5 (при последовательном соединении, через хабы, до 72 м) | Да/Нет (зависит от типа накопителя) | 127 | 4 | Host/Slave, горячая замена возможна |

| Ultra-320 SCSI | 2560 | 12 | Да | 16 | 50/68 | устройства равноправны, горячая замена возможна |

| SAS | 3000 | 8 | Да | Свыше 16384 | | горячая замена; возможно подключение SATA-устройств в SAS-контроллеры |

| eSATA | 2400 | 2 | Да | 1 (с умножителем портов до 15) | 4 | Host/Slave, горячая замена возможна |

[править] История прогресса накопителей

- 1956 — жесткий диск IBM 350 в составе первого серийного компьютера IBM 305 RAMAC. Накопитель занимал ящик размером с большой холодильник, а общий объем памяти 50 вращавшихся в нем покрытых чистым железом тонких дисков диаметром с большую пиццу (610 мм) составлял около 4,4 мегабайт (5 миллионов 6-битных байт)

- 1980 — первый 5,25-дюймовый Winchester, Shugart ST-506, 5 МБ

- 1986 — Стандарт SCSI

- 1991 — Максимальная ёмкость 100 МБ

- 1995 — Максимальная ёмкость 2 ГБ

- 1997 — Максимальная ёмкость 10 ГБ

- 1998 — Стандарты UDMA/33 и ATAPI

- 1999 — IBM выпускает Microdrive ёмкостью 170 и 340 МБ

- 2002 — Взят барьер адресного пространства выше 137 ГБ (проблема 48-bit LBA)

- 2003 — Появление SATA

- 2005 — Максимальная ёмкость 500 ГБ

- 2005 — Стандарт Serial ATA 3G (или SATA II)

- 2005 — Появление SAS (Serial Attached SCSI)

- 2006 — Применение перпендикулярного метода записи в коммерческих накопителях

- 2006 — Появление первых «гибридных» жёстких дисков, содержащих блок флэш-памяти

- 2007 — Hitachi представляет первый коммерческий накопитель ёмкостью 1 ТБ

- 2008 — Seagate Technology LLC представляет накопитель емкостью 1,5 ТБ

- 2009 — Seagate Technology LLC представляет накопитель на основе одной единственной пластины емкостью 500 Гб. Новые пластины позволили Seagate впервые в истории создать 2-терабайтный винчестер.

- 2009 — Компания Western Digital выпустила в продажу жесткий диск объемом два терабайта.[7]