Опорный конспект лекции фсо пгу 18. 2/07 Министерство образования и науки Республики Казахстан

| Вид материала | Конспект |

- Опорный конспект лекции фсо пгу 18. 2/07 Министерство образования и науки Республики, 1449.98kb.

- Опорный конспект лекции фсо пгу 18. 2/07 Министерство образования и науки Республики, 337.81kb.

- Опорный конспект лекции ффсо пгу 18. 2/05 Министерство образования и науки Республики, 1108.14kb.

- Опорный конспект лекции фсо пгу 18. 2/07 Министерство образования и науки Республики, 290.94kb.

- Опорный конспект Форма ф со пгу 18. 2/05 Министерство образования и науки Республики, 856.54kb.

- Титульный лист программы обучения по дисциплине фсо пгу 18. 3/37 для студентов (Syllabus), 677.11kb.

- Титульный лист программы обучения по дисциплине фсо пгу 18. 3/37 для студентов (Syllabus), 804.38kb.

- Методические указания Форма ф со пгу 18. 2/05 Министерство образования и науки Республики, 98.43kb.

- Методические указания Форма ф со пгу 18. 2/07 Министерство образования и науки Республики, 249.4kb.

- Рабочая программа ф со пгу 18. 2/06 Министерство образования и науки Республики Казахстан, 295.37kb.

1.1Иформационно-логические основы вычислительных машин их функциональная и структурная организация

Любая вычислительная система включает следующие узлы:

- Арифметико-логическое устройство (АЛУ), выполняющее арифметические и логические операции.

- Устройство управления (УУ), которое организует процесс выполнения программ.

- Запоминающее устройство (память) для хранения программ и данных.

- Внешние устройства для ввода–вывода информации (ВУ).

|

| Рис. 2.1. Логическая организация ЭВМ Одинарные линии называют управляющие связи, двойные – информационные. |

В общих чертах работу вычислительной системы можно описать следующим образом: устройство управления инициирует процесс чтения из памяти очередной команды программы, расшифровывает ее и подключает необходимые для ее выполнения цепи и устройства (АЛУ или ВУ), после чего цикл повторяется для выполнения следующей команды. Таким образом, все действия в ЭВМ выполняются под управлением программы, хранящейся в памяти. В связи с этим основным принципом работы ЭВМ является принцип программного управления.

Описанный принцип работы и структура ЭВМ – это классическая организация вычислительной системы, известная под названием неймановской архитектуры. Характерным ее отличием является то, что для хранения программ и данных используется одно и то же пространство памяти, т.е. содержимое ячейки памяти интерпретируется оператором обработки информации, в качестве которого в простейшем случае выступает процессор. Другим типом архитектуры является т.н. гарвардская архитектура, в которой память программ и память данных разделены и имеют собственные адресные пространства и способы доступа к ним.

Подсистема ввода-вывода в простейшем случае представлена набором адресуемых буферных схем и регистров (портов), через которые осуществляется связь с внешними и внутренними аппаратными средствами системы. Подсистема ввода-вывода обычно использует единый механизм адресации портов, размещаемых в специальном пространстве ввода-вывода. В некоторых системах для размещения пространства ввода-вывода выделяется область в пространстве памяти данных – т.н. отраженный на память ввод-вывод. Организация доступа к портам в таких системах ничем не отличается от процесса записи-считывания данных в ячейки памяти. В других системах пространство ввода-вывода размещается в специальном логически изолированном от других пространств данных пространстве - т.н. изолированный ввод-вывод. В этом случае для доступа к портам необходимы специальные команды ввода-вывода.

Современные ЭВМ могут иметь различную архитектуру, но обязательно содержат в своей структуре рассмотренные элементы и используют основной принцип функционирования ЭВМ, дополненный новыми принципами, к которым можно отнести принципы модульности, магистральности и микропрограммируемости.

Модульность – это способ построения компьютера на основе набора модулей. Модулем называется конструктивно и функционально законченный электронный блок в стандартном исполнении. Это означает, что с помощью модуля может быть реализована какая-то функция либо самостоятельно, либо совместно с другими модулями.

Магистральность – это способ соединения между различными модулями компьютера, когда входные и выходные устройства модулей соединяются одними и теми же проводами, совокупность которых называется шиной. Магистраль компьютера состоит из нескольких групп шин, разделяемых по функциональному признаку - шина адреса, шина данных, шина управления.

Микропрограммируемость – это способ реализации принципа программного управления. Суть его состоит в том, что принцип программного управления распространяется и на реализацию устройства управления. Другими словами, устройство управления строится точно так же, как и весь компьютер, только на микроуровне, т.е. в составе устройства управления имеется своя память, называемая управляющей памятью или памятью микрокоманд, свой "процессор", свое устройство управления и т. д.

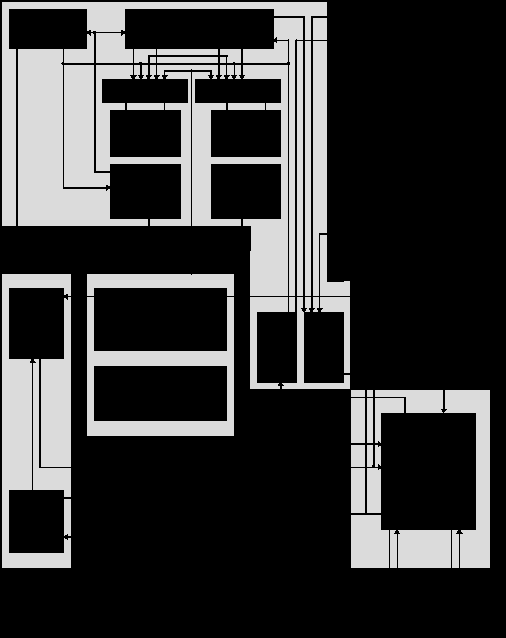

Использование рассмотренных принципов и объединение в одном устройстве, названом центральный процессор (ЦП), АЛУ и УУ, привели к видоизмененной структуре современной ЭВМ, изображенной на рис. 2.2.

Рис. 2.2 Модульная структура современной ЭВМ

Наиболее распространенной является структура вычислительной системы (ВС), имеющая две или три (в большинстве случаев) общих магистрали (шины), к которым под воздействием устройств управления могут поочередно подключаться, входящие в систему узлы (см. рис. 2.3).

Рис. 2.3. Трехмагистральная организация ЭВМ

В приведенной на рис. 2.3 схеме, обработку информации осуществляет ЦП, синхронизируемый тактовыми импульсами устройства синхронизации. Обмен информацией между МП и остальными блоками ВС осуществляется по трем магистралям (шинам): адресной, данных и управляющей. Магистраль адреса (МА, ША) служит для передачи кода адреса, по которому производится обращение к устройствам памяти ввода-вывода и прочим внешним устройствам. Обрабатываемая информация и результаты вычислений передаются по магистрали данных (МД, ШД). Магистраль управления (МУ) передает управляющие сигналы на все блоки ВС, настраивая устройства, участвующие в выполняемой команде, на нужный режим работы.

Использование в ВС трех магистралей обеспечивает высокое быстродействие и упрощает процесс вычисления. Возможно построение ВС с одной или двумя магистралями, по которым последовательно передаются код адреса и обрабатываемая информация, но при этом значительно возрастает время выполнения команды и усложняется организация обмена информацией между узлами.

2 тема. Запоминающие устройства (ЗУ) ЭВМ.

Определение, назначение, основные характеристики и классификация запоминающих устройств (ЗУ) ЭВМ. Способы организации памяти. Способы повышения емкости памяти. Оперативная память (RAM). Запоминающие устройства статического (SRAM) и динамического (DRAM) типов памяти. Контроллер динамической памяти. Кэш память. Кэширование оперативной памяти.

Память является важнейшим ресурсом любой вычислительной системы. Логически всю память ВС можно представить в виде последовательности ячеек, каждая из которых имеет свой номер, называемый адресом.

Иерархия памяти, КЭШ-память

Память вычислительной системы представляет собой иерархию запоминающих устройств (внутренние регистры процессора, различные типы сверхоперативной и оперативной памяти, диски, ленты), отличающихся объемом, средним временем доступа и стоимостью хранения данных в расчете на один бит.

Например:

- Регистровая память – емкость 64-256 слов, время доступа – 1такт процессора.

- КЭШ первого уровня или внутренний КЭШ – емкость 8k слов, время доступа – 1-2 такта процессора.

- КЭШ второго уровня или внешний КЭШ – емкость 256k слов, время доступа – 3-5 тактов процессора.

- ОЗУ – емкость до 4Г слов, время доступа – 12-55 тактов процессора,

- Внешняя память – емкость до 200Г, время доступа значительно ниже.

Таким образом, в основе иерархии памяти современных вычислительных систем лежит принцип «стоимость/производительность», т.е. с увеличением производительности возрастает и стоимость памяти, при этом пользователь всегда стремится иметь недорогую и быструю память. Кэш-память представляет некоторое решение этой проблемы.

Кэш-память – это способ организации совместного функционирования двух типов ЗУ, отличающихся временем доступа и стоимостью хранения данных, который позволяет уменьшить среднее время доступа к данным за счет динамического копирования в «быстрое» ЗУ наиболее часто используемой информации из «медленного» ЗУ.

Кэш-памятью часто называют не только способ организации работы двух типов запоминающих устройств, но и одно из устройств – «быстрое» ЗУ. Оно стоит дороже и, как правило, имеет сравнительно небольшой объем. Важно, что механизм кэш-памяти является прозрачным для пользователя, который не должен сообщать никакой информации об интенсивности использования данных и не должен никак участвовать в перемещении данных из ЗУ одного типа в ЗУ другого типа, все это делается автоматически системными средствами.

Таким образом, иерархия памяти вычислительной системы может быть схематично изображена, как это показано на рисунке 2.10.

Рис. 2.10. Иерархия ЗУ

В системах, оснащенных кэш-памятью, каждый запрос к «медленному» ЗУ выполняется в соответствии со следующим алгоритмом:

Просматривается содержимое кэш-памяти с целью определения, не находятся ли нужные данные в ней;

- Если данные обнаруживаются в кэш-памяти, то они считываются из нее, и результат передается в процессор в более «быстрое» ЗУ

- Если нужных данных нет, то они копируются из «медленного» ЗУ в кэш-память, и результат выполнения запроса передается в «быстрое» ЗУ. При копировании данных может оказаться, что в кэш-памяти нет свободного места, тогда выбираются данные, к которым в последний период было меньше всего обращений, для вытеснения из кэш-памяти. Если вытесняемые данные были модифицированы за время нахождения в кэш-памяти, то они переписываются в оперативную память. Если же эти данные не были модифицированы, то их место в кэш-памяти объявляется свободным.

На практике в кэш-память считывается не один элемент данных, к которому произошло обращение, а целый блок данных, это увеличивает вероятность так называемого «попадания в кэш», то есть нахождения нужных данных в кэш-памяти.

Принцип действия кэш-памяти основан на наличии у данных объективных свойств: пространственной и временной локальности.

Пространственная локальность состоит в следующем – если произошло обращение по некоторому адресу, то с высокой степенью вероятности в ближайшее время произойдет обращение к соседним адресам.

Временная локальность состоит в следующем – если произошло обращение по некоторому адресу, то следующее обращение по этому же адресу с большой вероятностью произойдет в ближайшее время.

1.1.1Виртуальная память

Достаточно давно пользователи столкнулись с проблемой размещения в памяти программ, размер которых превышал имеющуюся в наличии свободную память. Решением было разбиение программы на части, называемые оверлеями. 0-ой оверлей начинал выполняться первым. Когда он заканчивал свое выполнение, он вызывал другой оверлей. Все оверлеи хранились на диске и перемещались между памятью и диском средствами операционной системы. Однако разбиение программы на части и планирование их загрузки в оперативную память должен был осуществлять программист.

Развитие методов организации вычислительного процесса в этом направлении привело к появлению метода, известного под названием виртуальная память. Виртуальным называется ресурс, который пользователю или пользовательской программе представляется обладающим свойствами, которыми он в действительности не обладает. Так, например, пользователю может быть предоставлена виртуальная оперативная память, размер которой превосходит всю имеющуюся в системе реальную оперативную память.

Таким образом, виртуальная память – это совокупность программно-аппаратных средств, позволяющих использовать ОП, размер которой превосходит реально имеющуюся в системе ОП. Для организации виртуальной памяти вычислительная система должна решать следующие задачи:

- размещение данных в ЗУ разного типа, например, часть ОП, а часть на диске;

- перемещение по мере необходимости данные между ЗУ разного типа, например, подгрузка нужной части программы с диска в ОП;

- преобразование виртуальных адресов в физические.

Все эти действия выполняются автоматически, без участия программиста, то есть механизм виртуальной памяти является прозрачным по отношению к пользователю.

1.1.2Физическая организация памяти

Физически память делится на внутреннюю и внешнюю.

Внутренняя память выполняется, чаще всего, в виде микросхем высокой степени интеграции. Внутренняя или основная память может быть двух типов: оперативное запоминающее устройство (ОЗУ или RAM, Random Access Memory) или ЗУ с произвольной выборкой (ЗУПВ) и постоянное ЗУ (ПЗУ или ROM, Read Only Memory). В последнее время широкое распространение получила флэш (Flash)-память, имеющая особенности, как ОЗУ, так и ПЗУ. ОЗУ является энергозависимой памятью, поскольку вся содержащаяся в ней информация теряется при выключении питания и предназначена для временного хранения программ и данных. ПЗУ является энергонезависимой памятью, т.е. информация сохраняется и при выключении питания системы. ПЗУ предназначена для хранения управляющих работой ЭВМ стандартных программ (например, отвечающие за процедуру старта системы), констант, таблицы символов и т.д.

ПЗУ могут быть: масочными - запрограммированными на заводе изготовителе (ROM), однократно-программируемыми пользователем ППЗУ (PROM или OTP), многократно-программируемыми (репрограммируемыми) пользователем РПЗУ с ультрафиолетовым стиранием (EPROM) или с электрическим стиранием (EEPROM, Flash). Широкое распространение нашли также программируемые логические матрицы и устройства (PLM, PML, PLA, PAL, PLD, FPGA и т.д.) с большим выбором логических элементов и устройств на одном кристалле.

ОЗУ подразделяются на статическую память (SRAM), динамическую (DRAM, здесь для хранения информации необходима ее регенерация) и регистровую (RG).

В качестве оперативной памяти современные ЭВМ оснащаются модулями SIMM, DIMM, DDR и RIM, которые является динамической памятью. Указанные модули памяти представляют собой небольшие платы с установленными на ней совместимыми чипами SDRAM (Sychronous DRAM – это новая технология микросхем динамической памяти. Основное отличие данного типа памяти от остальных заключается в том, что все операции синхронизированы с тактовой частотой процессора, то есть память и CPU работают синхронно. Технология SDRAM позволяет сократить время, затрачиваемое на выполнение команд и передачу данных, за счет исключения циклов ожидания).

Модуль SIMM (Single In-line Memory Modyle) – 72-контактные модули, обычно оборудованные микросхемами памяти общей емкостью 8, 16 и 32 Мб.

Модуль DIMM (Dual In-line Memory Modyle) – 168-контактные модули памяти. DIMM обладают внутренней архитектурой, схожей с 72-контактными модулями SIMM, но благодаря более широкой шине обеспечивают повышенную производительность подсистемы «ЦП – ОП».

Модуль DDR – имею аналогичную DIMM архитектуру, а двукратный выигрыш в быстродействии осуществляется за возможности передачи двух порций данных за один такт синхронизации – по фронту и спаду импульса.

Одной из наиболее быстродействующих является память RDRAM (Rambus RAM), разработанная американской компанией Rambus. Память RDRAM является 16-разрядной, тактируется частотой 400 МГц (результирующая частота за счет использования технологии DDR составляет 800 МГц) и достигает пиковой скорости передачи данных 1.6 Гбайт/с. Использование узкой шины данных и сверхвысокой частоты значительно повышают эффективность использования и загрузку канала, максимально освобождая протокол от временных задержек.

1.1.3Внешняя память

Внешней называют память на магнитных (жесткие и гибкие диски), оптических носителях (CD-ROM) и т.п.

Кроме того существует и накопители на магнитной ленте, которые в настоящее время практически не используются и поэтому в данной главе не рассматриваются.

Дисковые накопители в зависимости от среды носителя и по применяемому методу записи (чтения) данных на (с) поверхность (и) могут подразделяться на магнитные, оптические и магнитооптические.

| Тип накопителя | Емкость, Мб | Время доступа, мс | Скорость передачи, Кбайт/с | Режим доступа |

| НГМД | 1,2; 1,44 | 65 -100 | 150 | Чтение/запись |

| НЖМД (Винчестер) | 1000-18000 | 8-20 | 500-3000 | Чтение/запись |

| CD-R | 120-800 | 15-300 | 150-1500 | Чтение/ однократная запись |

| CD-RW | 120-800 | 15-150 | 150-1500 | Чтение/Запись |

| НМОД | 128-1300 | 15-150 | 300-2000 | Чтение/запись |

Дисковая память

Носителями информации являются поверхности гибких и жестких дисков, в качестве немагнитных основ которых используются соответственно майлар (как и в магнитных лентах) и алюминиевые (в ряде случаев стеклянные) круги (диски). Стеклянные диски являются менее критичными к температурным изменениям и позволяют увеличить плотность записи информации. В настоящее время наиболее широкое распространение получили диски с напыленным магнитным слоем, а точнее, с металлической пленкой (например, кобальт).

Перед осуществлением записи на магнитный диск он должен быть специальным образом инициализирован – отформатирован. В результате форматирования на поверхности образуются концентрические окружности (синхронизирующие метки диска), называемые дорожками (track). Количество дорожек зависит от типа диска. Дорожки разбиваются на участки фиксированной длины, называемые секторами. Количество секторов на дорожке определяется типом и форматом диска, и они в основном одинаковы для всех дорожек. IBM PC-совместимые ПК могут работать с несколькими размерами секторов от 128 до 1024 байт. Стандартным сектором считается сектор из 512 байт. Данные любого размера (разрядности) размещаются в секторах с фиксированным размером, а дисковые операции записи и считывания производятся с целыми секторами.

Дорожки и сектора нумеруются с нуля, начиная с внешнего края диска, при этом сектор с нулевым номером на каждой дорожке резервируется для системных целей. Диски имеют две стороны. Так как накопители на жестких дисках могут состоять из нескольких дисков (стопка), то совокупность всех дорожек, по одной на каждой стороне с одинаковыми номерами, образует цилиндр с номером соответствующей дорожки.

Память на гибких магнитных дисках

Все НГМД, применяемые в PC, независимо от типа и размера имеют одинаковый интерфейс и унифицированные разъемы. Используемый в PC кабель-шлейф имеет перевернутый фрагмент из 7 проводов с номерами 10-16. Этот поворот позволяет подключать к контроллеру одним шлейфом до двух НГМД, причем адрес накопителя определяется его положением на шлейфе: для привода А: фрагмент перевернут, для В: – нет.

Контроллер накопителей на гибких дисках FDC (Floppy Drive Controller) является всегда внешним по отношению к накопителю и обычно располагается на одной плате с контроллером или адаптером жестких дисков.

Контроллер FDC XT поддерживает до четырех накопителей (FDD), хотя многие контроллеры имеют интерфейсные схемы только для одного шлейфа, то есть для двух накопителей. Эти контроллеры обеспечивают скорость передачи данных 250 и 300 Кбит/с.

Контроллер FDC AT поддерживает только два накопителя, но обеспечивает более высокую скорость 500 Кбит/с.

Современные контроллеры обеспечиваю скорость 1000 Кбит/с. В карте ресурсов AT имеется место под два контроллера НГМД.

Контроллеры вырабатывают запрос аппаратного прерывания IRQ6 (BIOS INT OEh) по окончании выполнения внутренних операций. Для обмена данными может использоваться канал DMA2.

Память на жестких магнитных дисках

В отличие от накопителей на гибких дисках и их контроллеров, жестко стандартизованных и поэтому легко конфигурируемых, в PC применяется множество типов накопителей на жестких дисках, их интерфейсов и контроллеров, различающихся и способами конфигурирования.

Накопители на жестких магнитных дисках НЖМД (HDD), появились с машинами PC/XT. Первые накопители имели интерфейс, являющийся расширением интерфейса НГМД, и подключались к специальной плате контроллера с модулем дополнительной BIOS, хранящей всю информацию об установленных жестких дисках. В машинах класса AT поддержку стандартного контроллера включили в системную BIOS, параметры используемых жестких дисков стали хранить в памяти CMOS.

Традиционные версии BIOS поддерживают до двух накопителей на жестких дисках и хранят их параметры в ячейках памяти CMOS. Расширенные версии BIOS для современных двухканальных контроллеров АТА поддерживают 4 жестких диска и хранят их параметры.

Для дисков ATA используются следующие режимы адресации:

- CHS (целиндр-головка-сектор, традиционная трехмерная адресация данных на диске);

- ECHS (расширенная трехмерная адресация);

- LBA (линейная адресация данных на диске через логический адрес блока).

Учитывая, что в соответствии с форматом вызова функций дискового сервиса, одно устройство может иметь 210=1024 цилиндра, 28=256 головок, 26-1=63 сектора. Таким образом, при трехмерной адресации (CHS) и размере сектора в 512 байт максимальный объем диска не может превышать 7.875 Гбайт.

HDDmax(CHS) = [210 * 28 * (26-1)] * 512 = 136 902 082 560 байт = 7.875Gb (~8,4ГБ)

Все современные винчестеры используют LBA-адресацию. В режиме LBA параметры стандартных вызовов транслируются в т.н. линейный адрес, который вычисляется однозначно в «естественном» порядке счета секторов, т.е. сектору с нулевым лог. адресом соответствует первый сектор нулевой головки нулевого цилиндра. В этом случае номер каждого сектора представляет собой 28-битное число и максимальным диском для LBA будет:

HDDmax(LBA) = 228 * 512 = 137.4Gb (128ГБ)

В тоже время большинство ПО использует CHS-адресацию. Поэтому с появлением HDD с LBA адресацией, чтоб не модернизировать имеющееся ПО, поступили следующим образом. BIOS в случае определения LBA-винчестера, переводит его параметры в CHS-версию и ОС работает с ним с CHS-винчестером. Т.е. 28-битное значение адреса LBA «раскладывается» следующим образом: 16 бит – цилиндр, 8 бит – сектор, 4 бита – головка. В результате, при получении запроса на работу с диском, BIOS переводит для контроллера это значение LBA-адрес :

В общем виде формулы вычисления такого адреса имеет вид:

LBA=(CYL*HDS*HD)*SPT+SEC-1

CYL – номер цилиндра

HD – номер головки

HDS – количество головок

SPT – количество секторов на треке

SEC – номер сектора

Для накопителей на жестких дисках используют интерфейсы ST-506/412, ESDI, АТА (неофициальное название IDE), SCSI. Накопители и контроллеры с интерфейсами ST-506/412 и ESDI практически не используются.

В настоящее время широко используются перечисленные ниже интерфейсы.

АТА-2 — расширенная спецификация ATA, включает 2 канала, 4 устройства, PIO Mode 3 (программированный ввод-вывод), DMA mode 1 , Block mode (пакетный обмен), объем диска до 8 Гбайт, поддержка LBA и CHS адресации.

Fast АТА-2 разрешает использовать DMA Mode 2 (13,3 Мбайт/с), PIO Mode 4.

ATA-3 — расширение, направленное на повышение надежности. Включает средства парольной защиты, улучшенного управления питанием, самотестирования с предупреждением приближения отказа — SMART (Self Monitoring Analysis and Report Technology).

Ultra DMA/33 — версия ATA/IDE со скоростью обмена по шине 33 Мбайт/с. Устройства ATA IDE, E-IDE, АТА-2, Fast АТА-2, ATA-3 и Ultra DMA/33 электрически совместимы.

Последние достижения в этой области – интерфейсы Ultra ATA/66, Ultra ATA/100 и Ultra ATA/133 позволяющие осуществлять передачу данных со скоростью 66Мбай/сек, 100 Мбай/сек и 133 Мбай/сек соответственно.

Возможно также подключение дисковых устройств и к параллельному порту, но через устройство, обеспечивающее один из вышеперечисленных интерфейсов. О дисках с интерфейсом USB говорить пока рано, а интерфейс FireWire является родственником SCSI-3.

Кэширование диска

Время доступа к различным блокам информации на HDD является переменной величиной, складывающейся из временами подвода магнитной головки (МГ) к искомой дорожке, времени успокоения вибрации МГ и времени подвода искомого сектора под МГ. Кэш или буфер HDD необходим, чтоб по возможности сократить время доступа к диску за счет, во первых, предварительной выборки данных, и во-вторых, за счет организации поблочного доступа. Для организации буфера используются два вида кэш-памяти аппаратная и программная.

Аппаратная кэш-память представляет собой значительный объем памяти и имеет архитектуру полного ассоциативного отображения. Она строится на плате кэш-контроллера HDD с использованием модулей высокопроизводительной памяти и имеет собственный процессор.

Программная кэш-память — это некоторая область системной памяти, зарезервированная для дискового кэша и управляемая утилитой (например, Windows SmartDrive).Объем программной кэш-памяти рекомендуется ограничивать четвертью объема системной памяти).

В многозадачных системах выгодно иметь HDD с мультисегментной кэш-памятью (для каждой задачи отводится своя часть кэша – сегмент). В адаптивной системной кэш-памяти для повышения производительности размер и количество сегментов могут изменяться.

Для эффективной работы кэш (HDD) необходимо часто оптимизировать (дефрагментировать) диск, так как при этом относящиеся к одному и тому же файлу сектора будут расположены в физически близких секторах, что приведет к большей эффективности функционирования кэш.

Общие сведения о RAID-технологиях

В RAID (Redundant Array of Independent Disks) технологии данные и информация для устранения ошибок распределяются по нескольким дискам. При этом обеспечивается повышение производительности, а также защита критически важных приложений в среде клиент-сервер. Для обеспечения бесперебойного доступа выбирается конфигурация с дублированным источником питания и функцией «горячей перекачки», которая оперативно реконструирует данные при замене отказавшего диска на новый.

С целью уменьшения платы за надежность был предложен ряд архитектур. Разработаны RAID-системы нескольких уровней. Первый уровень RAID предполагает сплошное копирование защищаемых данных. Остальные уровни RAID основаны на работе с одной копией данных, распределенной по разным дискам, при использовании схем четности. По сравнению с зеркальным отображением контроль четности позволяет снизить накладные расходы на избыточность (см. рис. 2.12). На рисунке схематично представлена система RAID 3 и дается пример восстановления потерянного блока (ФБЗ1) с использованием контрольной информации (ФБ41). При появлении отказа необходимо заменить отказавший диск и подать команду на RAID-контроллер о восстановлении массива. Получив такую информацию, компьютер рассматривает все блоки, определяет, каких данных не достает, восстанавливает утраченные фрагменты на основе информации о четности и записывает полученные блоки на новый диск. Очень важно восстановить массив как можно быстрее. Отказ второго диска будет означать полную утрату всех данных. Использовании при построении ВС RAID 3 при четырехдисковой организации приводит к повышению стоимости системы приблизительно на 25 %.

3 тема. Процессоры ЭВМ.

Процессорные устройства. Структура микропроцессорной системы. Основные блоки процессора. Работа процессора. Организация обрабатывающей части микропроцессора. RISC – процессоры с сокращенной системой команд и CISC (Complete Instruction Set Computer) процессоры с полной системой команд. Центральное устройство управления (ЦУУ). Основные функции ЦУУ. Выполнение программ в процессоре. Управление памятью и внешними устройствами. Средства программной работы процессора. Принципы организации прерываний. Приоритеты. Средства защиты памяти при организации мульти программного режима работы ЭВМ.

Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники являются архитектуры CISC и RISC. Основоположником CISC-архитектуры можно считать компанию IBM с ее базовой архитектурой IBM360, ядро которой используется с1964 года и дошло до наших дней, например, в таких современных мейнфреймах как IBM ES/9000.

Лидером в разработке микропроцессоров с полным набором команд (CISC - Complete Instruction Set Computer) считается компания Intel со своей серией x86 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров. Для CISC-процессоров характерно: сравнительно небольшое число регистров общего назначения; большое количество машинных команд, некоторые из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов; большое количество методов адресации; большое количество форматов команд различной разрядности; преобладание двухадресного формата команд; наличие команд обработки типа регистр-память.

Основой архитектуры современных высокопроизводительных рабочих станций и серверов является архитектура компьютера с сокращенным набором команд (RISC - Reduced Instruction Set Computer). Корни этой архитектуры уходят к компьютерам CDC6600, которые одни из первых начали оснащаться упрощенным набором команд для увеличения быстродействия. RISC в современном его понимании сформировалось на базе трех исследовательских проектов компьютеров: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Эти три машины имели много общего. Все они придерживались архитектуры, отделяющей команды обработки от команд работы с памятью, и делали упор на эффективную конвейерную обработку. Система команд разрабатывалась таким образом, чтобы выполнение любой команды занимало небольшое количество машинных тактов (предпочтительно один машинный такт). Сама логика выполнения команд с целью повышения производительности ориентировалась на аппаратную, а не на микропрограммную реализацию. Чтобы упростить логику декодирования команд использовались команды фиксированной длины и фиксированного формата.

Среди других особенностей RISC-архитектур следует отметить наличие достаточно большого регистрового файла (в типовых RISC-процессорах реализуются 32 или большее число регистров по сравнению с 8 - 16 регистрами в CISC-архитектурах), что позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные. Для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки.

С 1986 года началась активная промышленная реализация архитектуры RISC. К настоящему времени эта архитектура прочно занимает лидирующие позиции на мировом компьютерном рынке рабочих станций и серверов.

Следует отметить, что в последних разработках компании Intel, а также ее последователей-конкурентов (AMD, Cyrix, NexGen и др.) широко используются идеи, реализованные в RISC-микропроцессорах, так что многие различия между CISC и RISC стираются. Однако сложность архитектуры и системы команд x86 остается и является главным фактором, ограничивающим производительность процессоров на ее основе.

Процессоры Intel 8086

Родоначальником архитектуры процессоров Intel x86 является процессор Intel 8086 (1978 год). Intel 8086 представляет собой 16-битовую архитектуру со всеми внутренними регистрами, имеющими 16-битовую разрядность. К процессорам этого класса относятся микропроцессоры: Intel 80286 (24 битная архитектура), 80386 (32 битная архитектура), 80486 (32-битовые процессоры с внутренней кэш-памятью и встроенным сопроцессором (только DX)), Pentium, Pentium II и т.д.

Особенностью этих процессоров является преемственность на уровне машинных команд: программы, написанные для младших моделей процессоров, без каких-либо изменений могут быть выполнены на более старших моделях. При этом базой является система команд процессора 8086.

Структуру центрального процессора Intel 8086 можно разделить на два логических блока (рис.2.4):

- блок исполнения (EU:Execution Unit);

- блок интерфейса шин (BIU:Bus Interface Unit).

В состав EU входят: арифметическо-логическое устройство ALU, устройство управления CU и десять регистров. Устройства блока EU обеспечивают обработку команд, выполнение арифметических и логических операций.

Блок BIU ключает устройство управления шинами, блок очереди команд, регистры сегментов и предназначен для выполнения следующих функций:

- управление обменом данными с EU, памятью и внешними устройствами ввода/вывода;

- адресация памяти;

- выборка команд (осуществляется с помощью блока очереди команд Queue, который позволяет выбирать команды с упреждением).

|

| Рис. 2.4. Структура микропроцессора Intel 8086 |

Регистры микропроцессора имеют следующее назначение:

Регистры общего назначения – это 16-разрядные регистры АХ, ВХ, СХ, DX, каждый из которых состоит из двух 8-разрядных регистров, например, АХ состоит из АН (старшая часть) и AL (младшая часть).

В общем случае функция, выполняемая тем или иным регистром, определяется командами, в которых он используется. При этом с каждым регистром связано некоторое стандартное его значение:

- регистр АХ служит для временного хранения данных (регистр аккумулятор), часто используется при выполнении операций сложения, вычитания, сравнения и других арифметических и логических операций;

- регистр ВХ служит для хранения адреса некоторой области памяти (базовый регистр), а также используется как вычислительный регистр;

- регистр СХ иногда используется для временного хранения данных, но в основном служит счетчиком, в нем хранится число повторений одной команды или фрагмента программы;

- регистр DX используется главным образом для временного хранения данных, часто служит средством пересылки данных между разными программными системами, а также используется в качестве расширителя аккумулятора для вычислений повышенной точности и при умножении и делении.

Регистры указатели – это 16-разрядные регистры ВР (указатель базы), SI (индекс источника), DI (индекс результата), SP (указатель стека), IP (указатель команд).

Регистры SI, DI, BP используются в командах для хранения адресов памяти. При адресации памяти эти регистры могут быть использованы в различных комбинациях, что определяет раздичные режимами адресации.

Регистр SP определяет смещение текущей вершины стека. Указатель стека SP вместе с сегментным регистром стека SS используется для формирования физического адреса стека.

Регистр указателя команд IP, иначе называемый регистром счетчика команд и хранит адрес ячейки памяти, содержащей начало следующей команды. Микропроцессор использует регистр IP совместно с регистром CS для формирования физического адреса очередной выполняемой команды

Регистры сегментов – это 16-разрядные регистры, которые позволяют организовать память в виде совокупности четырех различных сегментов.

- CS – регистр программного сегмента (сегмента кода) определяет местоположение части памяти, содержащей программу, то есть выполняемые процессором команды;

- DS – регистр информационного сегмента (сегмента данных) идентифицирует часть памяти, предназначенной для хранения данных;

- SS – регистр стекового сегмента (сегмента стека) определяет часть памяти, используемой как системный стек;

- ES – регистр расширенного сегмента (дополнительного сегмента) указывает дополнительную область памяти, используемую для хранения данных.

Регистр флагов – это 16-разрядный регистр, содержащий биты, определяющие код условия, установленный последней выполненной командой или состояние микропроцессора. Эти биты называются флагами.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| X | X | X | X | OF | DF | IF | TF | SF | ZF | X | AF | X | PF | X | CF |

Биты регистра флагов имеют следующее назначение:

OF (признак переполнения) – равен единице, если возникает арифметическое переполнение, то есть когда объем результата превышает размер ячейки назначения;

DF (признак направления) – устанавливается в единицу для автоматического декремента в командах обработки строк, и в ноль – для инкремента;

IF (признак разрешения прерывания) – прерывания разрешены, если IF=1. Если IF=0, то распознаются лишь немаскированные прерывания;

TF (признаков трассировки) – если TF=1, то процессор переходит в состояние прерывания INT 3 после выполнения каждой команды;

SF (признак знака) – SF=1, когда старший бит результата равен единице. Иными словами, SF=0 для положительных чисел, и SF=1 для отрицательных чисел;

ZF (признак нулевого результата) – ZF=1, если результат равен нулю;

AF (признак дополнительного переноса) – этот флаг устанавливается в единицу во время выполнения команд десятичного сложения и вычитания при возникновении переноса или заема между полубайтами;

PF (признак четности) – этот признак устанавливается в единицу, если результат имеет четное число единиц;

CF (признак переноса) – этот флаг устанавливается в единицу, если имеет место перенос или заем из старшего бита результата, он полезен для произведения операций над числами длиной в несколько слов, которые сопряжены с переносами и заемами из слова в слово;

X – зарезервированные биты.

Процессоры Pentium

Архитектура микропроцессора Pentium значительно отличается от приведенной выше, что обуславливает следующие преимущества указанного класса процессоров:

- двухпотоковая суперскалярная организация, допускающая параллельное выполнение пары простых команд;

- наличие двух независимых двухканальных множественно-ассоциативных кэшей для команд и для данных, обеспечивающих выборку данных для двух операций в каждом такте;

- динамическое прогнозирование переходов;

- конвейерная организация устройства плавающей точки с 8 ступенями;

- двоичная совместимость с существующими процессорами семейства 80x86.

Упрощенная структура процессора Pentium представлена на рис. 2.5. Прежде всего, новая микроархитектура этого процессора базируется на идее суперскалярной обработки. Основные команды распределяются по двум независимым исполнительным устройствам (конвейерам U и V). Конвейер U может выполнять любые команды семейства x86, включая целочисленные команды и команды с плавающей точкой. Конвейер V предназначен для выполнения простых целочисленных команд и некоторых команд с плавающей точкой. Команды могут направляться в каждое из этих устройств одновременно, причем при выдаче устройством управления в одном такте пары команд более сложная команда поступает в конвейер U, а менее сложная - в конвейер V (при этом, однако, не все команды совместимы). Остальные устройства процессора предназначены для снабжения конвейеров необходимыми командами и данными.

В процессоре Pentium используется раздельная кэш-память команд и данных, что обеспечивает независимость обращений. За один такт из каждой кэш-памяти могут считываться два слова. Для повышения эффективности перезагрузки кэш-памяти в процессоре применяется 64-битовая внешняя шина данных.

В процессоре предусмотрен механизм динамического прогнозирования направления переходов. С этой целью на кристалле размещена небольшая кэш-память, которая называется буфером целевых адресов переходов (BTB), и две независимые пары буферов предварительной выборки команд (по два 32-битовых буфера на каждый конвейер). Буфер целевых адресов переходов хранит адреса команд, которые находятся в буферах предварительной выборки. Работа буферов предварительной выборки организована таким образом, что в каждый момент времени осуществляется выборка команд только в один из буферов соответствующей пары. При обнаружении в потоке команд операции перехода вычисленный адрес перехода сравнивается с адресами, хранящимися в буфере BTB. В случае совпадения предсказывается, что переход будет выполнен, и разрешается работа другого буфера предварительной выборки, который начинает выдавать команды для выполнения в соответствующий конвейер. При несовпадении считается, что переход выполняться не будет и буфер предварительной выборки не переключается, продолжая обычный порядок выдачи команд. Это позволяет избежать простоев конвейеров при правильном прогнозе направления перехода.

|

| Рис. 2.5. Упрощенная структура процессора Pentium |

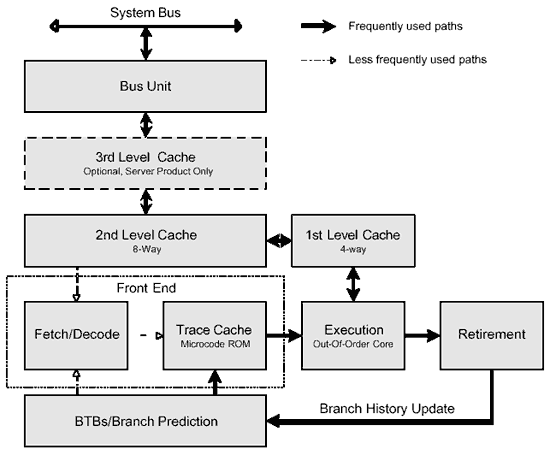

Процессоры Pentium 4

Intel Pentium 4 — это первый процессор в семействе 32-битных процессоров седьмого поколения от Intel. Несмотря на то что Intel Pentium 4 является процессором с архитектурой IA-32, последняя сильно отличается от архитектуры процессоров семейства P6 (в него входят процессоры Intel Pentium Pro, Intel Pentium II, Intel Pentium III, Intel Celeron и Intel Xeon) и даже получила специальное название — NetBurst. К основным новшествам архитектуры NetBurst являются:

- Hyper-Pipelined Technology,

- Execution Trace Cache,

- Rapid Execution Engine,

- 400 MHz System Bus,

- Advanced Dynamic Execution,

- Advanced Transfer Cache,

- Streaming SIMD Extensions 2 (SSE2).

Hyper-Pipelined Technology. Суть технологии гиперконвеерной технологии заключается в том, что Intel Pentium 4 имеет очень длинный конвейер, состоящий из 20 стадий. Для сравнения: конвейер у процессоров семейства P6 состоит всего из 10 стадий. Преимущества от использования такого новшества далеко не очевидны.

С одной стороны, более длинный конвейер позволяет упростить логику работы каждой отдельной стадии, а значит, более просто реализовать ее аппаратно, что приводит к уменьшению времени выполнения каждой отдельно взятой стадии. А это в конечном счете приводит к тому, что тактовая частота процессора может быть значительно увеличена.

С другой стороны, при обнаружении неправильно предсказанного перехода весь конвейер останавливается вместе с одновременным сбросом его содержимого, после чего разгоняется заново — и чем длиннее конвейер, тем больше времени занимает его разгон. Поэтому при увеличении длины конвейера для обеспечения роста производительности нужно повышать эффективность алгоритмов предсказания переходов.

Execution Trace Cache – это название и способ реализации L1-кэша инструкций в архитектуре NetBurst. Смысловое содержание этого термина можно перевести как «кэш трассировки выполняемых микроопераций».

В Execution Trace Cache хранятся микрооперации, полученные в результате декодирования входного потока инструкций исполняемого кода и готовые для передачи на выполнение конвейеру. Емкость Execution Trace Cache составляет 12 Кбайт.

Execution Trace Cache устроен таким образом, что вместе с кодом каждой микрооперации в нем хранятся результаты выполнения ветвей кода для этой микрооперации — в той же строке кэша (cache line), что и сама микрооперация. Это позволяет легко и своевременно выявлять микрооперации, которые никогда не будут выполнены, и быстро удалять их из L1-кэша инструкций, а также оперативно «вычищать» Execution Trace Cache от «лишних» микроопераций в случае обнаружения ошибочно предсказанного перехода. Последнее обстоятельство особенно важно, так как позволяет сократить общее время реинициализации конвейера после его остановки в результате выполнения перехода, который был предсказан неправильно.

Rapid Execution Engine. Так, в архитектуре NetBurst назван блок выполнения арифметико-логических операций. Rapid Execution Engine, во-первых, состоит из двух ALU-модулей, работающих параллельно, во-вторых, рабочая тактовая частота этих ALU-модулей в два раза выше тактовой частоты процессора — это достигается за счет регистрации как переднего, так и заднего фронта задающего тактового сигнала. Таким образом, каждый ALU-модуль способен выполнить до двух целочисленных операций за один рабочий такт процессора, а весь Rapid Execution Engine в целом — до четырех таких операций.

400 MHz System Bus. Физически системная шина у Intel Pentium 4 тактируется частотой в 100 МГц, однако благодаря использованию технологии Quad Pumping по этой шине передается четыре блока данных за один такт (аналогично тому, как это делается при передаче данных в режиме AGP 4X по AGP-шине). Так что эффективная рабочая частота системной шины у Intel Pentium 4 (которую также называют Quad Pumped Bus) составляет 400 МГц, а пропускная способность — 3,2 Гбайт/с.

Advanced Dynamic Execution — это обобщенное название механизма динамического выполнения команд (dynamic execution), используемого в NetBurst, построенного на трех базовых концепциях: предсказание переходов (branch prediction), динамический анализ потока данных (dynamic data flow analysis) и спекулятивное выполнение инструкций (out-of-order execution). Аналогичный механизм, названный Dynamic Execution, используется в процессорах семейства P6, однако в Intel Pentium 4 он улучшен.

Так, например, емкость пула, в котором хранятся готовые для обработки инструкции (out-of-order instruction window), у Intel Pentium 4 увеличена до 126 инструкций — против 42 у процессоров семейства P6.

Кроме того, в Intel Pentium 4 интегрирован более совершенный механизм предсказания переходов и количество ошибочно предсказанных переходов у него в среднем на 33% меньше, чем у процессоров с архитектурой P6.

Advanced Transfer Cache – это, в архитектуре NetBurst, L2-кэш процессора емкостью 256 Кбайт. Ширина шины, по которой идет обмен данными между Advanced Transfer Cache и процессором, составляет 256 бит (32 байта), а ее тактовая частота совпадает с тактовой частотой ядра процессора.

Streaming SIMD Extensions 2 (SSE2). В Intel Pentium 4 также интегрирован набор из 144 новых SIMD-инструкций, получивший название Streaming SIMD Extensions 2 (сокращенно — SSE2), который добавлен к базовому набору SSE-инструкций, реализованному ранее в процессоре Intel Pentium III.

Из этих 144 инструкций 68 — расширяют возможности старых SIMD-инструкций по работе с целыми числами, а 76 — являются совершенно новыми. Среди последних — инструкции, позволяющие оперировать со 128-разрядными числами (как целыми, так и вещественными с двойной точностью).

Новые SSE2-инструкции были добавлены с той же целью, что и появившийся ранее набор SSE-инструкций — для увеличения производительности системы при обработке аудио- и видеоданных.

|

| Рис. 2.6. Блок схема процессора Pentium 4 Retirement – отставка (отсрочка) Branch – переход Fetch – выборка |

Совместимые с Intel процессоры выпускают следующие производители Advanced Micro Devices (AMD), Cyrix Corp и NexGen.

1.1.4RISC-процессоры

Особенности процессоров с архитектурой SPARC

Масштабируемая процессорная архитектура компании Sun Microsystems (SPARC - Scalable Processor Architecture) является наиболее широко распространенной RISC-архитектурой, отражающей доминирующее положение компании на рынке UNIX-рабочих станций и серверов. Процессоры с архитектурой SPARC лицензированы и изготавливаются по спецификациям Sun несколькими производителями, среди которых следует отметить компании Texas Instruments, Fujitsu, LSI Logic, Bipolar International Technology, Philips и Cypress Semiconductor.

Процессоры с архитектурой SPARC занимают лидирующие позиции на рынке RISC-кристаллов (по данным независимой компании IDC за 1992 год архитектура SPARC занимала 56% рынка, далее следовали MIPS - 15% и PA-RISC - 12.2%).

Первоначально архитектура SPARC была разработана с целью упрощения реализации 32-битового процессора. В последствии по мере улучшения технологии изготовления интегральных схем она постепенно развивалось и в настоящее время имеется 64-битовая версия этой архитектуры.

В отличие от большинства RISC архитектур SPARC использует регистровые окна, которые обеспечивают удобный механизм передачи параметров между программами и возврата результатов. Архитектура SPARC была первой коммерческой разработкой, реализующей механизмы отложенных переходов и аннулирования команд. Это давало компилятору большую свободу заполнения времени выполнения команд перехода командой, которая выполняется в случае выполнения условий перехода и игнорируется в случае, если условие перехода не выполняется.

Процессоры SuperSPARC

Процессор SuperSPARC (один из первых процессоров серии SPARC) компании Texas Instruments стал основой серии рабочих станций и серверов SPARCstation/SPARCserver 10 и SPARCstation/SPARCserver 20. Имеется несколько версий этого процессора, позволяющего в зависимости от смеси команд обрабатывать до трех команд за один машинный такт, отличающихся тактовой частотой. Процессор SuperSPARC (рис. 2.7) имеет сбалансированную производительность на операциях с фиксированной и плавающей точкой. Он имеет внутренний кэш емкостью 36 Кб (20 Кб - кэш команд и 16 Кб - кэш данных), раздельные конвейеры целочисленной и вещественной арифметики и при тактовой частоте 75 МГц обеспечивает производительность около 205 MIPS (миллион команд в секунду). Для сравнения: Intel Pentium 66 МГц обеспечивает производительность 112 MIPS.

Развитием SPARC-процессоров стали процессоры hyperSPARC, 64-битовые процессоры UltraSPARC I, UltraSPARC II и т.д.

Процессоры HyperSPARC

Одной из главных задач, стоявших перед разработчиками микропроцессора hyperSPARC, было повышение производительности, особенно при выполнении операций с плавающей точкой. Поэтому особое внимание разработчиков было уделено созданию простых и сбалансированных шестиступенчатых конвейеров целочисленной арифметики и плавающей точки. Логические схемы этих конвейеров тщательно разрабатывались, количество логических уровней вентилей между ступенями выравнивалось, чтобы упростить вопросы дальнейшего повышения тактовой частоты.

Производительность процессоров hyperSPARC может меняться независимо от скорости работы внешней шины (MBus). Набор кристаллов hyperSPARC обеспечивает как синхронные, так и асинхронные операции с помощью специальной логики кристалла RT625. Отделение внутренней шины процессора от внешней шины позволяет увеличивать тактовую частоту процессора независимо от частоты работы подсистем памяти и ввода/вывода. Это обеспечивает более длительный жизненный цикл, поскольку переход на более производительные модули hyperSPARC не требует переделки всей системы.

Процессор hyperSPARC реализован в виде многокристальной микросборки (рис. 2.8), в состав которой входит суперскалярная конвейерная часть и тесно связанная с ней кэш-память второго уровня. В набор кристаллов входят RT620 (CPU) - центральный процессор, RT625 (CMTU) - контроллер кэш-памяти, устройство управления памятью и устройство тегов и четыре RT627 (CDU) кэш-память данных для реализации кэш-памяти второго уровня емкостью 256 Кбайт. RT625 обеспечивает также интерфейс с MBus.

|

| Рис. 2.7. Блок схема процессора Super SPARC |

|

| Рис. 2.8. Набор кристаллов процессора hyperSPARC |

Центральный процессор RT620 (рис. 2.9) состоит из целочисленного устройства, устройства с плавающей точкой, устройства загрузки/записи, устройства переходов и двухканальной множественно-ассоциативной памяти команд емкостью 8 Кбайт. Целочисленное устройство включает АЛУ и отдельный тракт данных для операций загрузки/записи, которые представляют собой два из четырех исполнительных устройств процессора. Устройство переходов обрабатывает команды передачи управления, а устройство плавающей точки, реально состоит из двух независимых конвейеров - сложения и умножения чисел с плавающей точкой. Для увеличения пропускной способности процессора команды плавающей точки, проходя через целочисленный конвейер, поступают в очередь, где они ожидают запуска в одном из конвейеров плавающей точки. В каждом такте выбираются две команды. В общем случае, до тех пор, пока эти две команды требуют для своего выполнения различных исполнительных устройств при отсутствии зависимостей по данным, они могут запускаться одновременно. RT620 содержит два регистровых файла: 136 целочисленных регистров, сконфигурированных в виде восьми регистровых окон, и 32 отдельных регистра плавающей точки, расположенных в устройстве плавающей точки.

|

| Рис. 2.9. Процессор RТ 620 |

Кэш-память второго уровня в процессоре hyperSPARC строится на базе RT625 CMTU, который представляет собой комбинированный кристалл, включающий контроллер кэш-памяти и устройство управления памятью, которое поддерживает разделяемую внешнюю память и симметричную многопроцессорную обработку.

RT627 представляет собой статическую память 16К, специально разработанную для удовлетворения требований hyperSPARC. Она организована как четырехканальная статическая память в виде четырех массивов с логикой побайтной записи и входными и выходными регистрами-защелками. RT627 для ЦП является кэш-памятью с нулевым состоянием ожидания без потерь (т.е. приостановок) на конвейеризацию для всех операций загрузки и записи, которые попадают в кэш-память.

Команды загрузки и записи одновременно генерируют два обращения: одно к кэш-памяти команд первого уровня емкостью 8 Кбайт и другое к кэш-памяти второго уровня. Если адрес команды найден в кэш-памяти первого уровня, то обращение к кэш-памяти второго уровня отменяется и команда становится доступной на стадии декодирования конвейера. Если же во внутренней кэш-памяти произошел промах, а в кэш-памяти второго уровня обнаружено попадание, то команда станет доступной с потерей одного такта, который встроен в конвейер. Такая возможность позволяет конвейеру продолжать непрерывную работу до тех пор, пока имеют место попадания в кэш-память либо первого, либо второго уровня, которые составляют 90% и 98% соответственно для типовых прикладных задач рабочей станции.

Существуют также недорогие варианты SPARC-процессоров, например, MicroSPARC-II, основное назначение которого - однопроцессорные низкостоимостные системы.

4 тема. Организации ввода –вывода. Вычислительные комплексы.

Организации ввода –вывода. Интерфейсы, шины расширения ввода-вывода. Способы обмена информацией. Интерфейсы персонального компьютера. Параллельные интерфейсы. LPT- порт. Режим обмена информацией: дуплексный, полудуплексный и симплексный. Последовательные интерфейсы. СОМ-порт. Способы последовательной передачи. Асинхронный и синхронный обмен информацией. Режимы передачи данных. Управление потом передачи. Котроллеры внешних устройств.. Порты ввода и вывода. Обмен информацией при прерываниях. Распределение системы обработки данных. Вычислительные комплексы. Классификация. Многомашинные вычислительные комплексы (системы). Организация функционирования многомашинной вычислительной системы (ММВС). Виды связей в ММВС. Мультипроцессорные компьютерные системы (МКС). Типы структурной организации и основы проектирования МКС.