Ульяновский Государственный Технический Университет Кафедра вычислительной техники Сравнение архитектуры фон Неймана и нейрокомпьютера реферат

| Вид материала | Реферат |

- Ульяновский Государственный Технический Университет Кафедра вычислительной техники, 216.41kb.

- Нейроинформатика. Архитектуры фон Неймана и нейрокомпьютера, 87.88kb.

- Новосибирский Государственный Технический Университет. Факультет автоматики и вычислительной, 2544.79kb.

- Новосибирский Государственный Технический Университет. Факультет автоматики и вычислительной, 1650.9kb.

- Ульяновский Государственный Технический Университет Кафедра вычислительной техники, 320.99kb.

- Образования Республики Молдова Колледж Микроэлектроники и Вычислительной Техники Кафедра, 113.64kb.

- Кафедра «Автоматизированные системы обработки информации и управления» доклад по дисциплине, 114.1kb.

- Красноярский Государственный Технический Университет Усть-Илимский филиал реферат, 389.47kb.

- Петербургский Государственный Университет Информационных Технологий, Механики и Оптики, 196.71kb.

- Ульяновский Государственный Технический Университет Цикл: «Прикладная лингвистика», 204.62kb.

Министерство образования Российской Федерации

Ульяновский Государственный Технический Университет

Кафедра вычислительной техники

Сравнение архитектуры фон Неймана и нейрокомпьютера

Реферат по инженерии знаний

студента группы МЭВд-52

Скворцова В.С.

Научный руководитель

Соснин Петр Иванович

Ульяновск

2003

История нейрокомпьютинга 3

Важные свойства нейроструктур 5

Архитектура нейрокомпьютеров 6

Особенности программирования средств аппаратной поддержки нейровычислений 13

Классическая архитектура ЭВМ 15

Преимущества и недостатки нейрокомпьютерных архитектур 19

Ссылки на использованные ресурсы 21

История нейрокомпьютинга

История развития вычислительных систем с массовым параллелизмом насчитывает уже не один десяток лет. Пожалуй, эта одна из небольшого числа областей науки и техники, где отечественные разработки находятся на уровне мировых достижений, а в некоторых случаях и превосходят их. Шли годы, изменялась элементная база и подходы к архитектуре построения современных супервычислителей, появлялись новые направления, к числу которых можно отнести и нейрокомпьютеры.

Что же следует понимать под термином нейрокомпьютер? Вопрос достаточно сложный. Нейросетевая тематика, как таковая, является междисциплинарной, ей занимаются как разработчики вычислительных систем и программисты, так и специалисты в области медицины, финансово-экономические работники, химики, физики и т.п. То, что понятно физику, совершенно не принимается медиком и наоборот - все это породило многочисленные споры и целые терминологические войны по различным направлениям применения всего где есть приставка нейро-.

Общие принципы построения нейронных сетей были заложены в начале второй половины 20 века в работах таких ученых, как: Д. Хебб, М. Минский, Ф. Розенблат. Первые нейросети состояли из одного слоя искусственных нейронов-персептронов. М. Минским были строго доказаны ряд теорем, определяющих принципы функционирования нейронных сетей. Несмотря на многочисленные преимущества персептронов: линейность, простота реализации параллельных вычислений, оригинальный алгоритм обучения и т.п., М. Минским вместе с соавторами было показано, что реализованные на его основе однослойные нейронные сети не способны решить большое число разнообразных задач. Это вызвало некоторое ослабление темпов развития нейросетевых технологий в 60-е годы. В дальнейшем многие ограничения по использованию нейросетей были сняты с разработкой многослойных нейронных сетей, определение которых было впервые введено Ф.Розенблатом: "под многослойной нейронной сетью понимается такое свойство структуры преобразования, которое осуществляется стандартной разомкнутой нейронной сетью при топологическом, а не символьном описании". Дальнейшее развитие теория нейронных сетей нашла в 70-80 годах в работах Б. Уидроу, Андерсона, Т. Кохонена, С. Гроссберга и др.

Теория нейросетей не внесла революционных новшеств в алгоритмы адаптации и оптимального управления. Самообучающиеся системы известны давно, теория адаптивных регуляторов также хорошо разработана, они широко применяются в технике. Теория нейросетей осваивает разработанные ранее методы и пытается их приспособить для создания все более эффективных нейронных систем.

Важные свойства нейроструктур

Особую важность использование нейроструктур приобретает с точки зрения

производительности ЭВМ. Согласно гипотезе Минского: реальная производительность типовой параллельной вычислительной системы из n процессоров растет как log(n) (то есть производительность системы из 100 процессоров всего вдвое выше, чем производительность 10-процессорной системы - процессоры дольше ждут своей очереди, чем вычисляют). Однако, если использовать для решения задачи нейронную сеть, то параллелизм может быть использован практически полностью - и производительность растет "почти пропорционально" n.

Следовательно, основные преимущества нейрокомпьютеров связаны с массовым параллелизмом обработки, что обуславливает высокое быстродействие, низким требованиями к стабильности и точности параметров элементарных узлов, устойчивостью к помехам и разрушениям при большой пространственной размерности системы, причём устойчивые и надёжные нейросистемы могут создаваться из низконадёжных элементов, имеющих большой разброс параметров.

Архитектура нейрокомпьютеров

В дальнейшем в данном обзоре под нейрокомпьютером будет пониматься вычислительная система с MSIMD архитектурой, в которой процессорный элемент однородной структуры упрощен до уровня нейрона, резко усложнены связи между элементами и программирование перенесено на изменение весовых коэффициентов связей между вычислительными элементами.

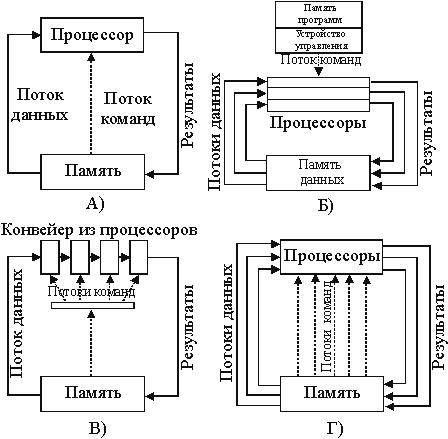

Остановимся на классификации архитектур вычислительных систем по

Б.М. Когану: Вычислительную систему с одним потоком команд и данных (однопроцессорная ЭВМ - SISD) (рис.1а). Вычислительную систему с общим потоком команд (SIMD - одиночный поток команд и множественный поток данных) (рис.1б). Вычислительную систему множественным потоком команд и одиночным потоком данных (MISD - конвейерная ЭВМ) (рис.1в).

Вычислительная система с множественным потоком команд и данных (рис.1г) (MIMD).

Элементарным строительным элементом нейронной сети (НС) является нейрон, который осуществляет взвешенное суммирование поступающих на его вход сигналов. Результат такого суммирования образует промежуточный выходной сигнал, который преобразуется активационной функцией в выходной сигнал нейрона. По аналогии с электронными системами активационную функцию можно считать нелинейной усилительной характеристикой искусственного нейрона, имеющей большой коэффициент усиления для слабых сигналов и c падающим усилением для больших возбуждений. Коэффициент усиления вычисляется как отношение выходного сигнала нейрона к вызвавшему его небольшому приращению взвешенной суммы входных сигналов. Кроме этого для обеспечения увеличения вычислительной мощности многослойными НС, по сравнению с однослойными, необходимо чтобы активационная функция между слоями была нелинейной, т.е. учитывая ассоциативность операции умножения матриц любую многослойную нейросеть без нелинейных активационных функций можно свести к эквивалентной однослойной нейросети, которые весьма ограничены по своим вычислительным возможностям. Но вместе с этим наличие нейлинейностей на выходе нейрона не может служить определяющим критерием, хорошо известны и успешно работают нейросети и без нелинейных преобразований на выход, получившие название нейросети на линиях задержки.

Алгоритмический базис нейрокомпьютеров обеспечивает теория нейронных сетей (НС). Нейронная сеть - это сеть с конечным числом слоёв из однотипных элементов - аналогов нейронов с различными типами связи между слоями.

Среди основных преимуществ НС отмечены: инвариантность методов синтеза НС к размерности пространства признаков и размерам НС, адекватность современным перспективным технологиям, отказоустойчивость в смысле монотонного, а не катастрофического изменения качества решения задачи в зависимости от числа вышедших из строя элементов.

Решение математических задач в нейросетевой логическом базисе определяют теоретические положения нейроматематики. Выделены следующие этапы решения практически любой задачи в нейросетевом логическом базисе: формирование входного сигнала НС, формирование выходного сигнала НС, формирование желаемого выходного сигнала НС, формирование сигнала ошибки и функционала оптимизации, формирование структуры нейронной сети, адекватной выбранной задаче, разработка алгоритма настройки НС, эквивалентного процессу решения задачи в нейросетевом логическом базисе, проведение исследований процесса принятия решения задачи. Всё вышеизложенное делает построение современных систем управления с использованием нейросетевого подхода и на основе нейросетевого логического базиса одним из самых перспективных направлений реализации многоканальных и многосвязанных систем управления.

Как было отмечено, нейрокомпьютер - это вычислительная система с MSIMD архитектурой, т.е. с параллельными потоками одинаковых команд и множественным потоком данных. Давайте разберемся, каким боком относятся нейрокомпьютеры к параллельным ЭВМ. На сегодня можно выделить три основных направления развития вычислительных систем с массовым параллелизмом (ВСМП):

1. ВСМП на базе каскадного соединения универсальных SISD, SIMD, MISD микропроцессоров. Элементная база - универсальные RISC или CISC процессоры: Intel, AMD, Sparc, Alpha, Power PC, MIPS и т.п.

2. На базе процессоров с распараллеливанием на аппаратном уровне. Элементная база - DSP процессоры: TMS, ADSP, Motorola.

3. ВСМП на специализированной элементной базе. Элементная база от специализированных однобитовых процессоров до нейрочипов.

Для каждого из направлений сегодня существуют решения, реализующие те или иные нейросетевые парадигмы. Для большей ясности в дальнейшем будем считать, что нейросетевые системы, реализованные на аппаратных платформах первого направления (пусть и мультипроцессорных) будем относить к нейроэмуляторам - т.е. системам реализующим типовые нейрооперации (взвешенное суммирование и нелинейное преобразование) на программном уровне. Нейросетевые системы, реализованные на аппаратных платформах второго и третьего направления в виде плат расширения стандартных вычислительных систем (1-го направления) - будем называть нейроускорителями (взвешенное суммирование, как правило, реализуется аппаратно, например, на основе трансверсальных фильтров, а нелинейные преобразования - программно) и системы, реализованные на аппаратной платформе третьего направления в виде функционально законченных вычислительных устройств, следует относить к нейрокомпьютерам (все операции выполняются в нейросетевом логическом базисе). Подводя итоги терминологической "войны" можно отметить, что нейрокомпьютеры можно смело отнести к вычислительным системам с высоким параллелизмом (MSIMD архитектуры), реализованным на основе специализированной элементной базы, ориентированной на выполнение нейросетевых операций в нейросетевом логическом базисе.

Одной из особенностей нейросетевых методов обработки информации является высокая параллельность вычислений и, следовательно, целесообразность использования специальных средств аппаратной поддержки. В значительной мере успех в решении рассмотренных задач обусловлен использованием оригинальных ускорительных плат. Такие платы работают параллельно с процессором обыкновенного ПК и несут на себе основную вычислительную нагрузку, превращая основной процессор компьютера в устройство управления и обслуживания мощных вычислительных средств, расположенных на ускорительной плате.

Например в НТЦ "Модуль" разработаны многопроцессорные ускорительные платы МЦ5.001 и МЦ5.002. Первая из них имеет в своем составе 4 микропроцессора TMS320C40 с тактовой частотой 50 МГц и пиковой производительностью 275 MIPS. Каждый процессор имеет свою локальную статическую память объемом 1 Мбайт. К 2 процессорам дополнительно подключены 2 блока динамической памяти объемом 16 Мбайт каждый. К одному из процессоров подключена также статическая память объемом 1 Мбайт, используемая для обмена данными с ПК. Процессоры соединены друг с другом специальными высокоскоростными каналами с пропускной способностью 20 Мбайт/с каждый. Наращивание и комплексирование плат осуществляется на материнской плате ПК с помощью шины ISA.

Ускорительная плата МЦ5.002 содержит 6 процессоров TMS320C40 и выполнена в конструктиве VME, что позволяет использовать ее в бортовых системах, расположенных на летательном аппарате.

Нейропроцессор обычно состоит из двух основных блоков: скалярного, выполняющего роль универсального вычислительного устройства, и векторного, ориентированного на выполнение векторно-матричных операций. Скалярное устройство обеспечивает интерфейсы с памятью и коммуникационными портами, позволяющими объединять процессоры в вычислительные сети различной конфигурации. Основное назначение скалярного устройства - подготовка данных для векторной части процессора. Для этого существует несколько режимов адресации, интерфейс с памятью, наборы арифметических и логических операций, возможность работы с регистровыми парами.

Центральным звеном нейропроцессора является целочисленное векторное устройство, обладающее возможностями обработки данных различной разрядности. Оно оперирует n-разрядными словами. Таким образом, процессор рассчитан на высокопроизводительную обработку больших массивов целочисленных данных.

К примеру отечественный нейропроцессор, разработанный в НТЦ "Модуль": Скалярное устройство обеспечивает интерфейсы с памятью и 2 коммуникационными портами. Скалярное устройство имеет адресных регистров и такое же количество регистров общего назначения разрядностью 32 бита каждый.

Центральным звеном нейропроцессора является целочисленное векторное устройство, обладающее возможностями обработки данных различной разрядности. Оно оперирует 64-разрядными словами, которые могут быть разбиты на целочисленные составляющие практически произвольной разрядности в пределах от 1 до 64 бит. На каждую инструкцию векторного процессора затрачивается от 1 до 32 тактов. При этом одновременно обрабатывается до 32 64-разрядных слов. Для организации непрерывной подачи данных в операционное устройство (ОУ) векторного процессора используются внутренние блоки памяти, называемые векторными регистрами. Они выполняют роль буфера операндов, буфера для хранения матрицы весов, очереди результатов. При выполнении команды в операционном устройстве операнды по очереди извлекаются из внутреннего буфера и подаются на один из входов ОУ. Внутри ОУ производятся вычисления, а их результат заносится в буфер результатов. Векторные инструкции, хотя и занимают несколько тактов процессорного времени, могут выполняться параллельно с инструкциями скалярного процессора. Таким образом, процессор рассчитан на высокопроизводительную обработку больших массивов целочисленных данных.

Нейропроцессор выполнен по технологии 0,5 км. Его тактовая частота 33 МГц. На специальных векторно-матричных операциях он дает увеличение производительности в десятки раз по сравнению с процессором TMS320C40. Благодаря наличию коммуникационных портов с интерфейсом, идентичным портам TMS320C40, нейропроцессор может быть интегрирован в гетерогенную многопроцессорную систему.

Для нейропроцессора разработан полный пакет системного программного обеспечения, включая символьный отладчик, и ряд прикладных библиотек, в частности библиотеку векторно-матричных вычислений.

Особенности программирования средств аппаратной поддержки нейровычислений

Специфика рассматриваемых вычислительных средств и решаемых задач обуславливает новые требования к технике программирования. Программисту приходится оперировать другими категориями, по-другому строить логику программы, решать задачи, которые не могли возникнуть при традиционном программировании. Перед ним стоит задача - максимально эффективно использовать ресурсы вычислительной системы, правильно распределить нагрузку между процессорами, задействовать их специфичные возможности.

Здесь на первый план выходят методы параллельной обработки данных. Причем слова "параллельная обработка" можно понимать как обработку на параллельно работающих процессорах, так и одновременную обработку нескольких элементов данных на одном процессоре. Современный процессор позволяет выполнять несколько инструкций за один такт, что заставляет программиста продумывать как способы организации самих вычислений, так и способы подготовки данных, для того чтобы параллельно выполняемые процессы не блокировали друг друга.

Трудности, возникающие при программировании многопроцессорных систем, хорошо известны: синхронизация параллельных процессов, механизмы обмена данными, проблемы "критических участков", когда несколько процессов задействуют одни и те же ресурсы. Еще одной важной особенностью современных процессоров является высокая разрядность операндов, например 64 бита, что позволяет размещать в них по несколько малоразрядных элементов данных и обрабатывать их параллельно. Примером эффективного использования отмеченной особенности современных процессоров является технология MMX, где 64-разрядный регистр разбивается на 8 независимых байтов или на 4 16-битных слова, которые обрабатываются параллельно. Независимость элементов состоит в том, что при смещениях или вычитании не происходит заимствования битов у соседних элементов.

Классическая архитектура ЭВМ

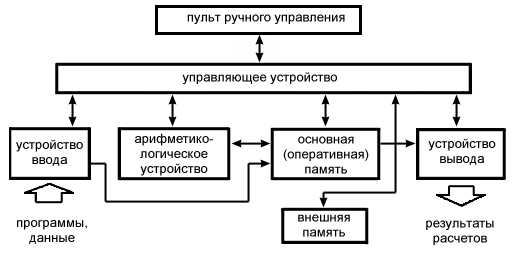

Упрощенная структура ЭВМ представлена на рис. ЭВМ содержит следующие основные устройства: арифметико-логическое устройство, память, управляющее устройство, устройство ввода данных в машину, устройство вывода из нее результатов расчета и пульт ручного управления.

Арифметико-логическое устройство (АЛУ) производит арифметические и логические преобразования над поступающими в него машинными словами, т. е. кодами определенной длины, представляющими собой числа или другой вид информации.

Память хранит информацию, передаваемую из других устройств, в том числе поступающую в машину извне через устройство ввода, и выдает во все другие устройства информацию, необходимую для протекания вычислительного процесса. Память машины в большинстве случаев состоит из двух существенно отличающихся по своим характеристикам частей: быстродействующей основной или оперативной (внутренней) памяти (ОП) и сравнительно медленно действующей, но способной хранить значительно больший объем информации внешней памяти (ВнП).

Оперативная память содержит некоторое число ячеек, каждая из которых служит для хранения машинного слова или его части. Ячейки нумеруются, номер ячейки называется адресом.

В запоминающих устройствах, реализующих в ЭВМ функцию памяти, выполняются операции считывания хранимой информации для передачи в другие устройства и записи информации, поступающей из других устройств. При считывании слова из ячейки содержимое последней не меняется и при необходимости слово может быть снова взято из той же ячейки. При записи хранившееся в ячейке слово стирается и его место занимает новое.

Непосредственно в вычислительном процессе участвует только ОП, и лишь после окончания отдельных этапов вычислений из ВнП в ОП передается информация, необходимая для следующего этапа решения задачи.

Управляющее устройство (УУ) автоматически без участия человека управляет вычислительным процессом, посылая всем другим устройствам сигналы, предписывающие им те или иные действия, в частности включает АЛУ на выполнение нужной операции.

Автоматическое управление процессом решения задачи достигается на основе принципа программного управления, являющегося основной особенностью ЭВМ.

Другим важнейшим принципом является принцип хранимой в памяти программы. Согласно этому принципу команды программы, закодированные в цифровом виде, хранятся в памяти наравне с числами. В команде указываются не сами участвующие в операциях числа, а адреса ячеек ОП, в которых они находятся, и адрес ячейки, куда помещается результат операции.

Поскольку программа хранится в памяти, одни и те же команды могут нужное число раз извлекаться из памяти и выполняться. Более того, так как команды представляются в машине в форме чисел, то над командами как над числами машина может производить операции ("модификации команд").

Команды выполняются в порядке, соответствующем их расположению в последовательных ячейках памяти, кроме команд безусловного и условного переходов, изменяющих этот порядок соответственно безусловно или только при выполнении некоторого условия, обычно задаваемого в виде равенства нулю, положительного или отрицательного результата предыдущей команды или отношения типа >, =, < для указываемых командой чисел. Именно благодаря наличию команд условного перехода ЭВМ может автоматически изменять соответствующим образом ход вычислительного процесса, решать сложные логические задачи.

Перед решением задачи на ЭВМ программа и исходные данные должны быть помещены в ее память. Предварительно эта информация обычно заносится во внешнюю память. Затем при помощи устройства ввода программа и исходные данные считываются в ОП.

Устройство вывода служит для выдачи из машины результатов расчета, например, путем печатания их на печатных устройствах или отображения на экране дисплея. При помощи пульта управления оператор пускает и останавливает машину, а при необходимости может вмешиваться в процесс решения задачи.

Представленная на рис. 1.1 структура (модель) вычислительной машины, получившая название фоннеймановской, благодаря ее изящной простоте и большой гибкости при управлении вычислительным процессом с самых первых шагов электронной вычислительной техники и по сей день доминирует при построении различных ЭВМ.

Однако в последние годы конструкторы ЭВМ, стремясь достигнуть существенного повышения их производительности, в ряде случаев отходят от модели фон Неймана.

Приведем один из примеров. В фоннеймановской машине с общей памятью для данных и команд имеется всего одна шина (магистраль) для передачи из памяти в другие устройства команд и данных, что ведет к снижению скорости работы ЭВМ.

Возможно построение машины с отдельными памятями и шинами для хранения и передачи команд и данных, допускающей параллельное во времени извлечение их из памяти и передачу по шинам. Такая структура (модель) получила название гарвардской, так как была реализована впервые в 1944 г. в Гарвардском университете (США) в ранней релейной вычислительной машине, предшествовавшей появлению электронных вычислительных машин. Гарвардская модель реализована, в частности, в некоторых микропроцессорах.

Преимущества и недостатки нейрокомпьютерных архитектур

Подытожим привлекательные черты распределенной обработки информации в искусственных нейросетях:

- Параллелизм обработки информации - глобальность связей между нейронами. До обучения эти связи произвольны, но обучение на примерах "проявляет" конкретную структуру сети под конкретную задачу.

- Высокая скорость. Она возможна вследствие внутреннего параллелизма сети и простой реализации в виде быстродействующих электронных микросхем.

- Единый и эффективный принцип обучения нейросетей - минимизация эмпирической ошибки методом её обратного распространения по сети. Извне задается лишь цель обучения - то есть способ определения ошибки по выходам сети. Далее сеть постепенно модифицирует свою конфигурацию, минимизируя эту ошибку, то есть, все лучше справляясь с возложенной на неё задачей.

- Надежность функционирования. Избыточность связей приводит к тому, что значения каждого веса по отдельности не играют решающей роли. Вывод из строя ограниченного числа нейронов или обрыв некоторых связей не сказываются критическим образом на качестве работы всей сети. В обычных компьютерах такие неисправности приводят к полному выходу из строя.

- Способность решать неформализованные задачи - следует из способности нейросетей самостоятельно вырабатывать весьма сложные алгоритмы обработки данных, формализовать которые самостоятельно зачастую не могут даже лучшие эксперты в данной предметной области. Отсюда - относительная дешевизна нейросетевых разработок.

- Перепрограммируемость. Нейронные микросхемы легко адаптируются к новым условиям экспериментов.

К недостатку нейронных сетей можно отнести их скрытный характер функционирования, т.к. иногда бывает трудно понять критерии, которые нейронная сеть использует при работе.

Ссылки на использованные ресурсы

1. u/~stasson/neurox.php

2. niki.net/~alchemist/NN/Bondarev/lecture1.htm

3. /Education/Books/Neural%20Net/Bmst/Book3/kussl3.htm

4. .free.net/edu/msd/students/2000/11/index.php

5. 4.bmstu.ru/neurnews.php

6. u/cdo/programmes/os/11.htm

7. .ru/projects/InterSearch/diplom2_3.php