Российская федерация федеральная служба по интеллектуальной собственности, патентам и товарным знакам

| Вид материала | Документы |

СодержаниеТроичный инвертор на кмоп транзисторах |

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 56.11kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 18.96kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 92.21kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 31.66kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 35.17kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 73.08kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 72.99kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 59.93kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 38.13kb.

- Российская федерация федеральная служба по интеллектуальной собственности, патентам, 22.29kb.

| | | | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |

| | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |

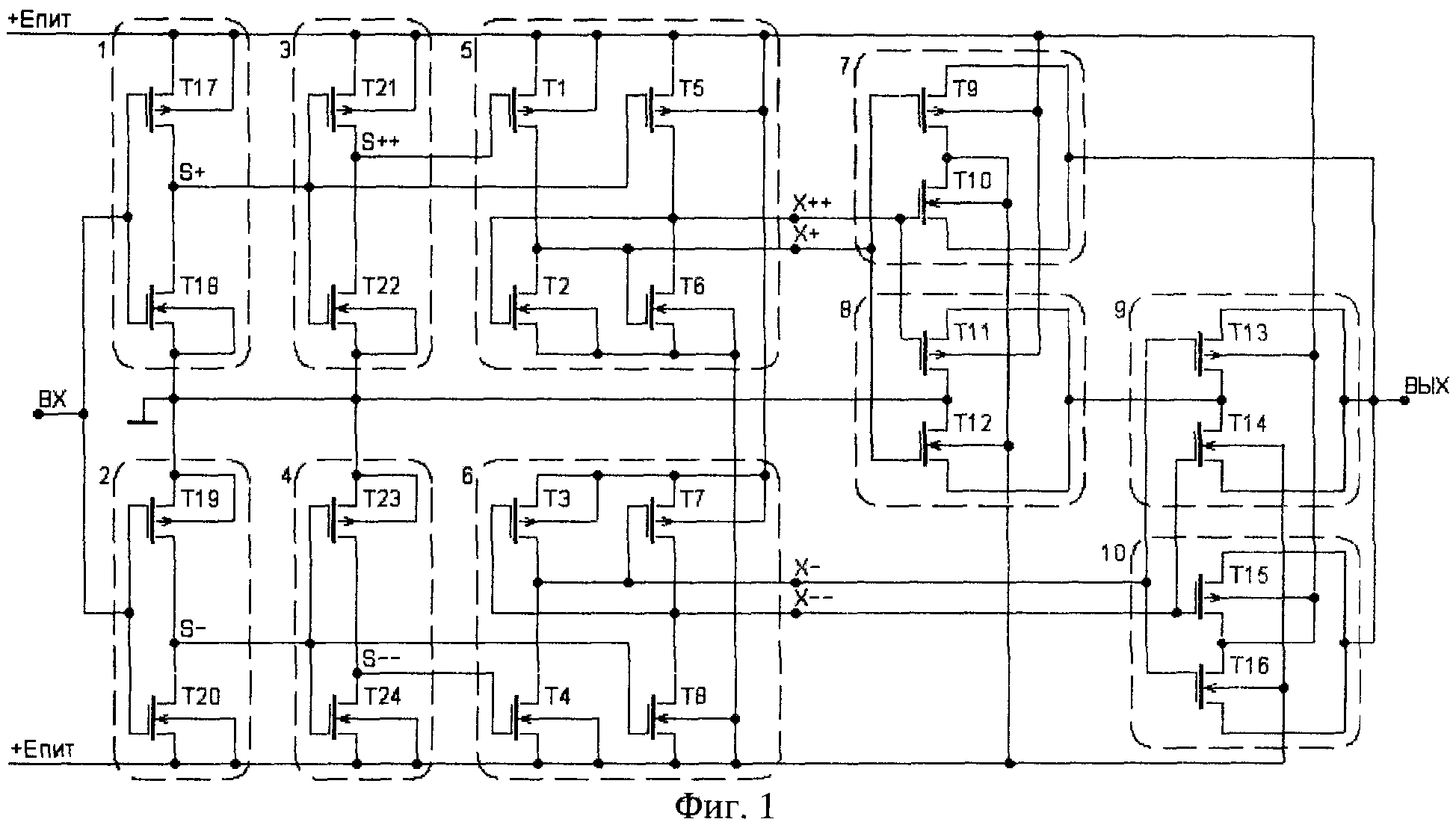

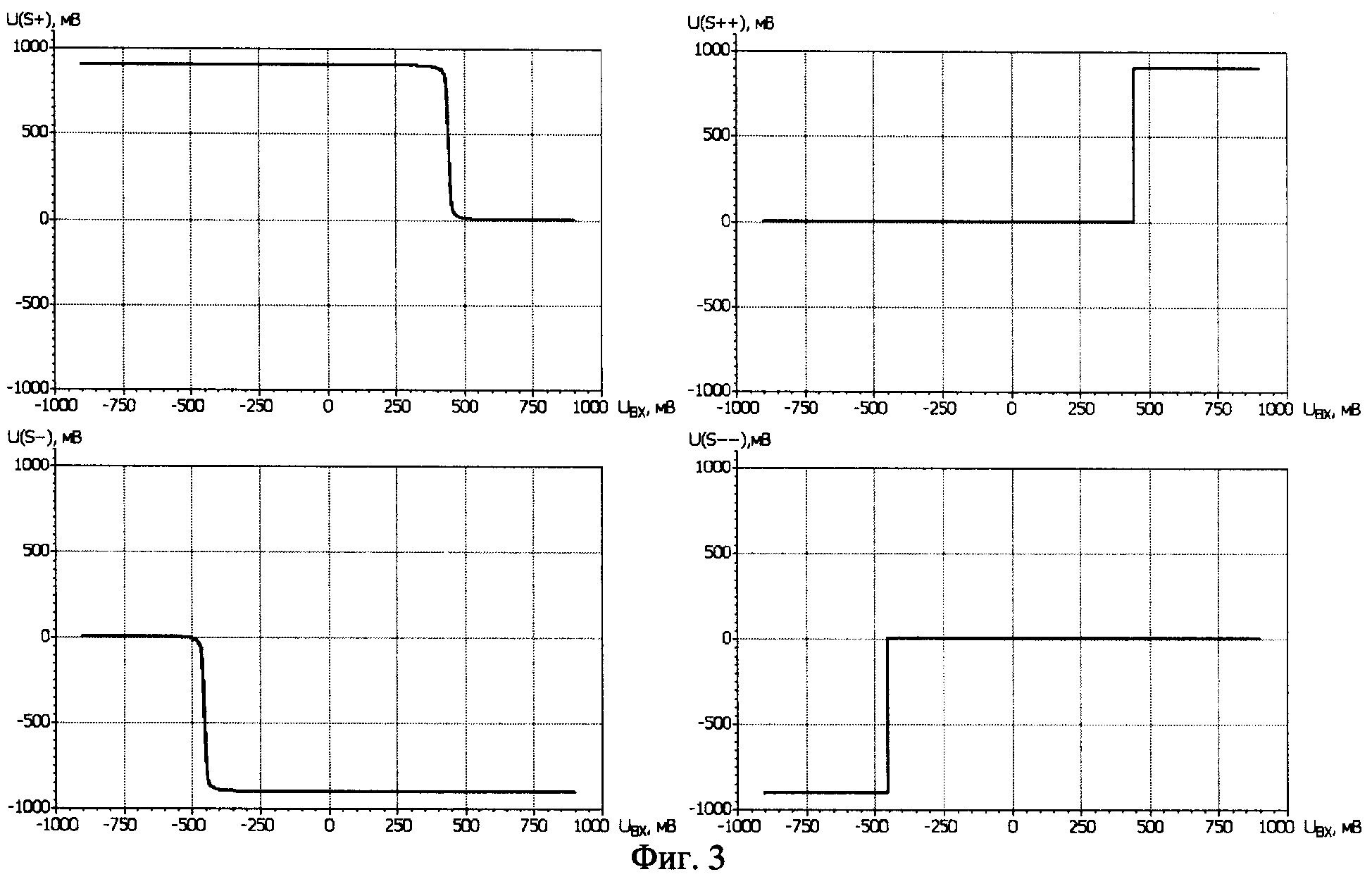

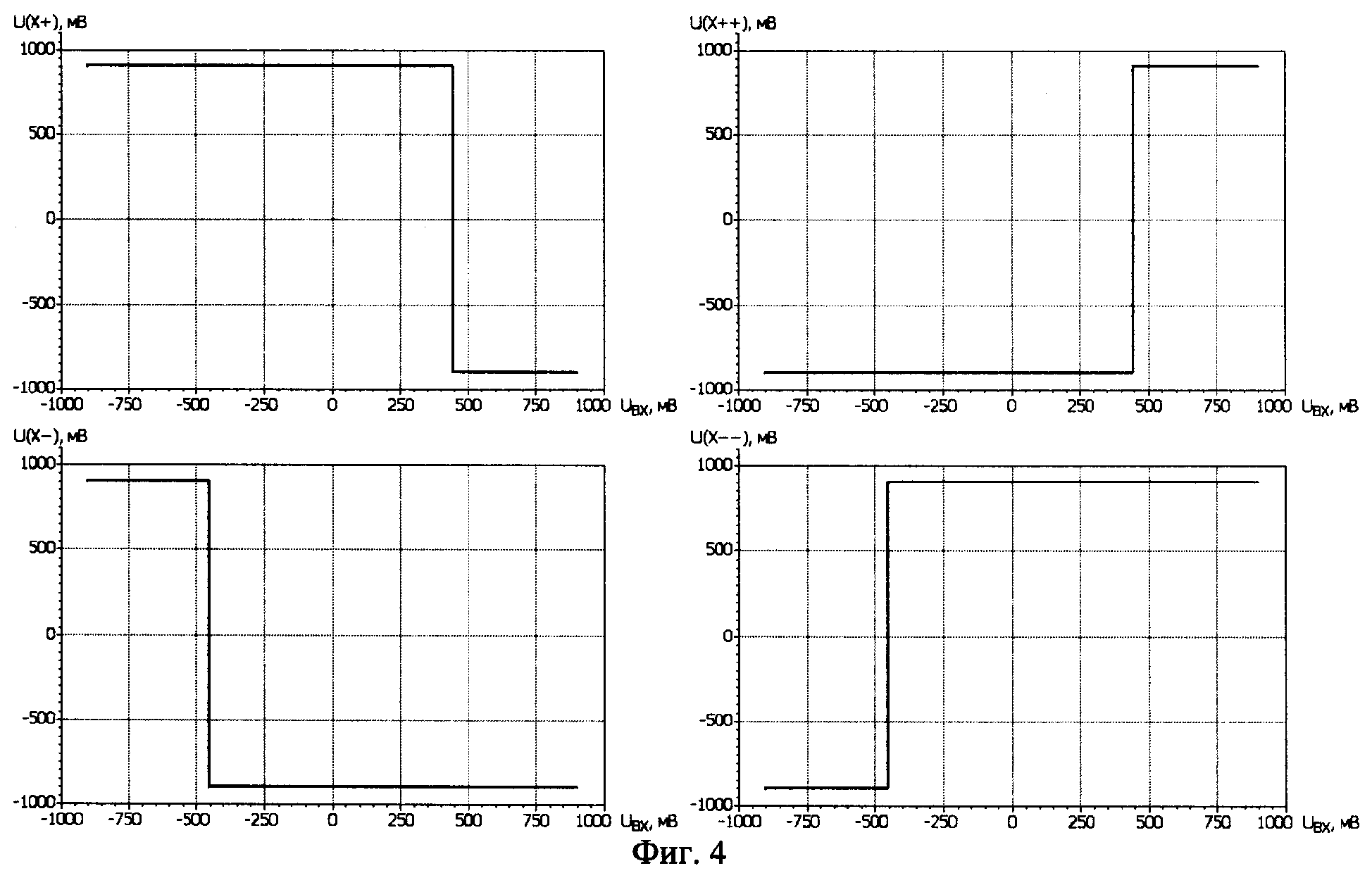

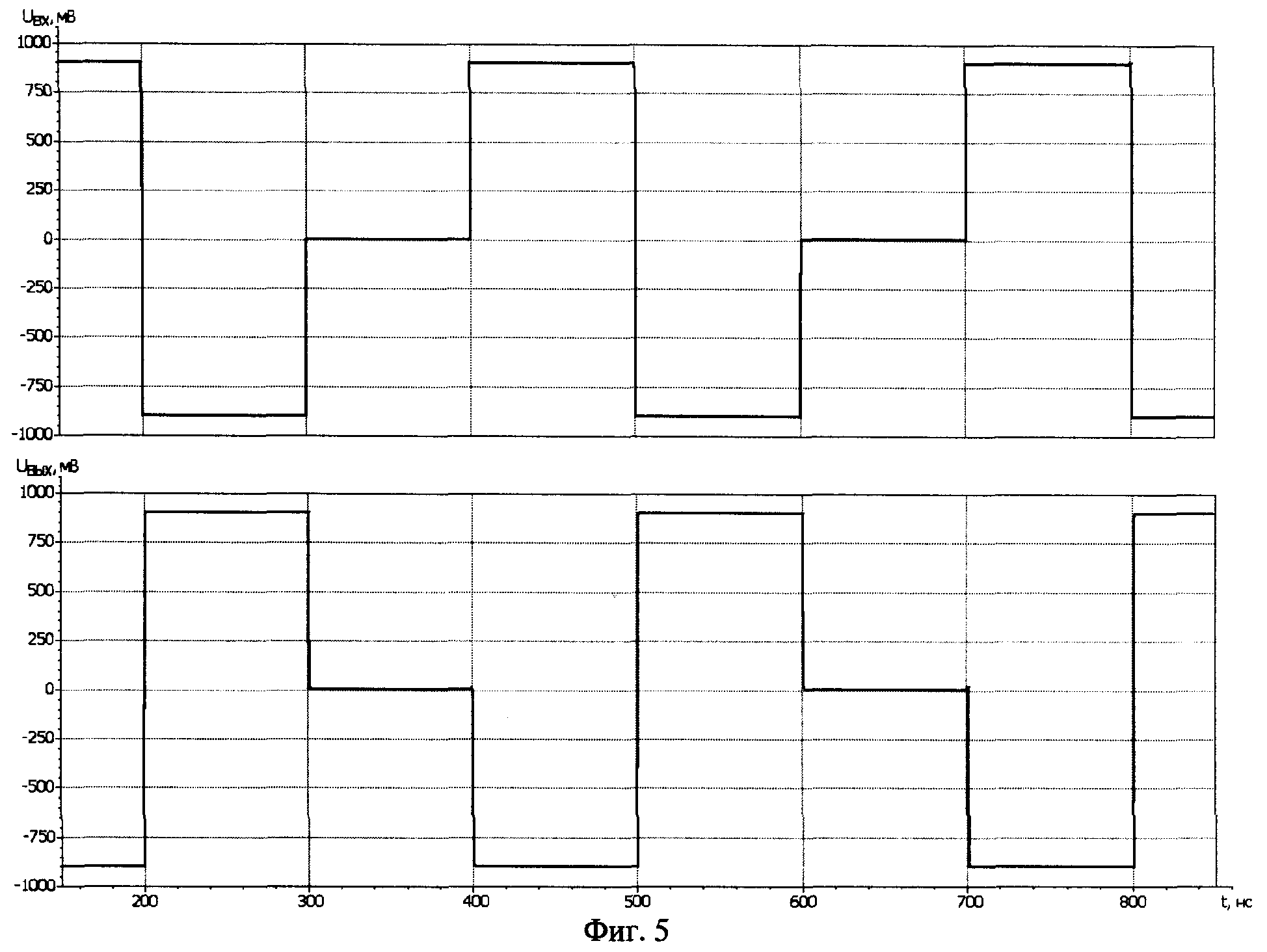

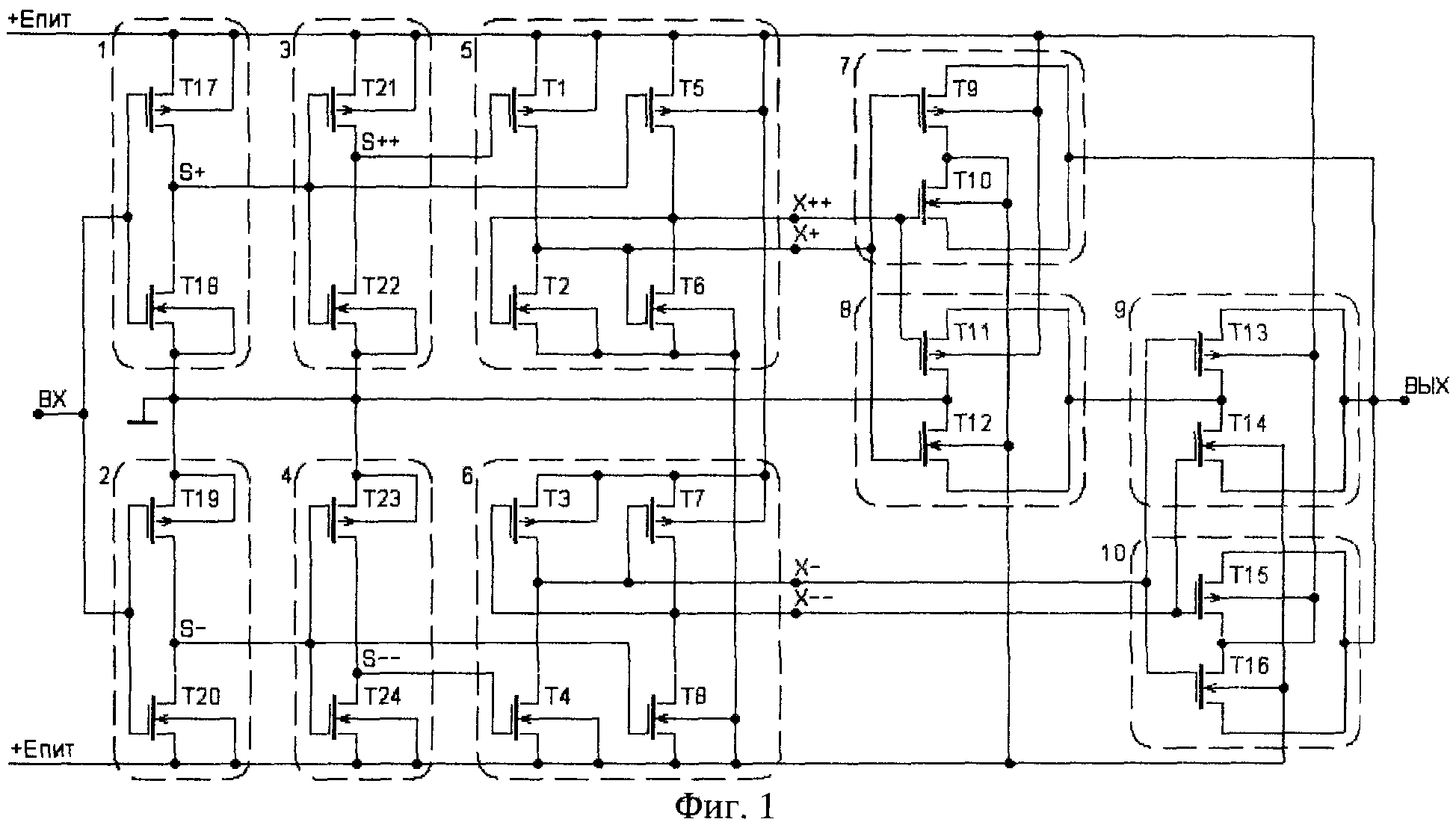

(54) ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ (57) Реферат: Изобретение относится к цифровой технике и может использоваться для выполнения логической функции инвертирования в троичных устройствах. Технический результат заключается в снижении статической потребляемой мощности за счет уменьшения величины статических токов до значений, обусловленных токами утечки МОП транзисторов. Троичный инвертор состоит из инвертирующих цепей (1)-(4), триггерных цепей (5) и (6), комплементарных ключей (7)-(10) на основе МОП транзисторов. Входом являются входы цепей (1) и (2). Каждая инвертирующая цепь содержит комплементарные пары транзисторов, затворы и стоки которых попарно соединены. Каждая триггерная цепь состоит из двух компонентов на основе комплементарной пары транзисторов. Инвертирующие цепи, триггерные цепи и комплементарные ключи соединены так, как указано в формуле изобретения. При заданном логическом состоянии на входе обеспечивается замыкание ключей так, что напряжение на выходе соответствует требуемому значению троичного кода. При любом логическом состоянии на выходе невозможно протекание сквозного статического тока за счет наличия транзисторов в режиме отсечки. 5 ил., 2 табл.  Изобретение относится к цифровой технике и может быть использовано для выполнения логической функции инвертирования в троичных цифровых устройствах. Аналогами заявляемого устройства являются: схемы троичных логических элементов (патент Германии  19832101, кл. H03K 19/20, 2000), схема троичного инвертора на комплементарных металл-оксид-полупроводник (КМОП) транзисторах (патент Японии 19832101, кл. H03K 19/20, 2000), схема троичного инвертора на комплементарных металл-оксид-полупроводник (КМОП) транзисторах (патент Японии  2005080257, кл. H03K 19/20, 2005), троичное логическое устройство «И» (патент Российской Федерации 2005080257, кл. H03K 19/20, 2005), троичное логическое устройство «И» (патент Российской Федерации  2281605, кл. H03K 19/20, 2006), универсальная схема троичных логических элементов (патент Японии 2281605, кл. H03K 19/20, 2006), универсальная схема троичных логических элементов (патент Японии  2007208512, кл. H03K 19/20, 2007), троичный инвертор (патент Японии 2007208512, кл. H03K 19/20, 2007), троичный инвертор (патент Японии  2007036757, кл. H03K 19/20, 2007). 2007036757, кл. H03K 19/20, 2007).Ближайшим прототипом заявляемого устройства является троичный инвертор на КМОП транзисторах (C.N.Rozon, H.T.Mouftah. Realization of a three-valued logic built-in testing structure // IEEE J. Solid-State Circuits. June 1990. V.25.  3. P.814-820), который содержит схему управления и набор КМОП ключей. Значения троичного кода «-1» и «+1» соответствуют напряжениям отрицательной и положительной шин двуполярного источника питания, а значение «0» - потенциалу земляной шины. Входом троичного инвертора является вход схемы управления. Схема управления формирует сигналы для коммутации выхода троичного инвертора с шинами источника питания согласно логической функции инвертирования. При заданном логическом состоянии на входе обеспечивается замыкание ключей так, что напряжение на выходе соответствует требуемому значению троичного кода. 3. P.814-820), который содержит схему управления и набор КМОП ключей. Значения троичного кода «-1» и «+1» соответствуют напряжениям отрицательной и положительной шин двуполярного источника питания, а значение «0» - потенциалу земляной шины. Входом троичного инвертора является вход схемы управления. Схема управления формирует сигналы для коммутации выхода троичного инвертора с шинами источника питания согласно логической функции инвертирования. При заданном логическом состоянии на входе обеспечивается замыкание ключей так, что напряжение на выходе соответствует требуемому значению троичного кода.Существенный недостаток известных схем троичных инверторов, в том числе и прототипа, заключается в значительной статической потребляемой мощности при напряжении на входе инвертора, соответствующем значению троичного кода «0». Значительное потребление мощности обусловлено протеканием сквозного статического тока, величина которого определяется токами канала МОП транзисторов в линейном режиме и режиме насыщения. Задача предлагаемого изобретения - снижение статической потребляемой мощности в схеме троичного инвертора за счет уменьшения величины статических токов до значений, которые определяются токами утечки МОП транзисторов. Решение поставленной задачи достигается тем, что в схеме управления, содержащей первый МОП транзистор с каналом p-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком второго МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; третий МОП транзистор с каналом p-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком четвертого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; пятый МОП транзистор с каналом p-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком шестого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания, а затвор шестого МОП транзистора соединен со стоком первого МОП транзистора; седьмой МОП транзистор с каналом p-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком восьмого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания, а затвор седьмого МОП транзистора соединен со стоком третьего МОП транзистора; и формирующей сигналы для коммутации четырех КМОП ключей, причем первый КМОП ключ, который в замкнутом состоянии коммутирует выход инвертора к отрицательной шине питания, состоит из девятого МОП транзистора с каналом p-типа и десятого МОП транзистора с каналом n-типа, стоки которых подключены к отрицательной шине питания, а истоки соединены с выходом инвертора; второй и третий КМОП ключи соединены последовательно и в замкнутом состоянии коммутируют выход инвертора к земляной шине; второй КМОП ключ состоит из одиннадцатого МОП транзистора с каналом p-типа и двенадцатого МОП транзистора с каналом n-типа, стоки которых подключены к земляной шине; третий КМОП ключ состоит из тринадцатого МОП транзистора с каналом p-типа и четырнадцатого МОП транзистора с каналом n-типа, истоки которых соединены с выходом инвертора; истоки одиннадцатого и двенадцатого МОП транзисторов и стоки тринадцатого и четырнадцатого МОП транзисторов соединены; четвертый КМОП ключ, который в замкнутом состоянии коммутирует выход инвертора к положительной шине питания, состоит из пятнадцатого МОП транзистора с каналом p-типа и шестнадцатого МОП транзистора с каналом n-типа, истоки которых подключены к положительной шине питания, а стоки соединены с выходом инвертора; затворы девятого и двенадцатого МОП транзисторов соединены со стоком первого МОП транзистора, затворы десятого и одиннадцатого МОП транзисторов соединены со стоком пятого МОП транзистора, затворы тринадцатого и шестнадцатого МОП транзисторов соединены со стоком третьего МОП транзистора, затворы четырнадцатого и пятнадцатого МОП транзисторов соединены со стоком седьмого МОП транзистора, подложки девятого, одиннадцатого, тринадцатого и пятнадцатого МОП транзисторов подключены к положительной шине питания, а подложки десятого, двенадцатого, четырнадцатого и шестнадцатого МОП транзисторов подключены к отрицательной шине питания, в отличие от прототипа, затвор второго МОП транзистора соединен со стоком пятого МОП транзистора, затвор третьего МОП транзистора соединен со стоком седьмого МОП транзистора, в схему управления добавлены восемь МОП транзисторов, которые пронумерованы с семнадцатого по двадцать четвертый, причем исток и подложка семнадцатого МОП транзистора с каналом p-типа подключены к положительной шине питания, а сток соединен со стоком восемнадцатого МОП транзистора с каналом n-типа, исток и подложка которого подключены к земляной шине; исток и подложка девятнадцатого МОП транзистора с каналом p-типа подключены к земляной шине, а сток соединен со стоком двадцатого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; на затворы семнадцатого, восемнадцатого, девятнадцатого и двадцатого МОП транзисторов подается входной сигнал; исток и подложка двадцать первого МОП транзистора с каналом p-типа подключены к положительной шине питания, а сток соединен со стоком двадцать второго МОП транзистора с каналом n-типа, исток и подложка которого подключены к земляной шине; исток и подложка двадцать третьего МОП транзистора с каналом p-типа подключены к земляной шине, а сток соединен со стоком двадцать четвертого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; затворы пятого, двадцать первого и двадцать второго МОП транзисторов соединены со стоком семнадцатого МОП транзистора; затворы восьмого, двадцать третьего и двадцать четвертого МОП транзисторов соединены со стоком девятнадцатого МОП транзистора; затвор первого МОП транзистора соединен со стоком двадцать первого МОП транзистора, а затвор четвертого МОП транзистора соединен со стоком двадцать третьего МОП транзистора. За счет введения дополнительных МОП транзисторов и специального схемотехнического решения в предложенном троичном инверторе на КМОП транзисторах при напряжении на входе, соответствующем как значению троичного кода «0», так и значениям «-1» и «+1», протекание статического тока обусловлено лишь токами утечки МОП транзисторов, которые существенно меньше токов канала МОП транзисторов в линейном режиме и режиме насыщения. За счет уменьшения величины статических токов до значений токов утечки МОП транзисторов осуществляется снижение статической потребляемой мощности в схеме троичного КМОП инвертора. Предлагаемое изобретение иллюстрируется графическими материалами, представленными на фиг.1-5: на фиг.1 изображена схема троичного инвертора на КМОП транзисторах; на фиг.2 приведена передаточная характеристика по напряжению троичного инвертора на КМОП транзисторах; на фиг.3 представлены зависимости напряжений в узлах (S+), (S++), (S-), (S--) схемы управления от напряжения на входе (ВХ) троичного инвертора на КМОП транзисторах; на фиг.4 представлены зависимости напряжений на выходах (Х+), (Х++), (Х-), (Х--) схемы управления от напряжения на входе (ВХ) троичного инвертора на КМОП транзисторах; на фиг.5 приведены эпюры напряжений на входе (ВХ) и выходе (ВЫХ) схемы троичного инвертора на КМОП транзисторах. Заявляемый троичный инвертор на КМОП транзисторах (фиг.1) состоит из четырех инвертирующих цепей (1)-(4), двух триггерных цепей (5) и (6) и четырех КМОП ключей (7)-(10). Инвертирующие цепи (1)-(4) и триггерные цепи (5) и (6) образуют схему управления, вход которой является входом инвертора (ВХ). Вход схемы управления представляют затворы МОП транзисторов инвертирующих цепей (1) и (2). Каждая инвертирующая цепь (1)-(4) состоит из МОП транзистора с каналом p-типа и МОП транзистора с каналом n-типа, затворы и стоки которых попарно соединены. Истоки МОП транзисторов с каналом p-типа Т17 и Т21 инвертирующих цепей (1) и (3) подключены к положительной шине питания (+Eпит), а истоки МОП транзисторов с каналом n-типа Т18 и Т22 - к земляной шине. Истоки МОП транзисторов с каналом p-типа Т19 и Т23 инвертирующих цепей (2) и (4) подключены к земляной шине, а истоки МОП транзисторов с каналом n-типа Т20 и Т24 - к отрицательной шине питания (-Eпит). Выходы инвертирующих цепей с номерами (1), (2), (3) и (4) обозначены соответственно (S+), (S-), (S++) и (S--). Каждая из триггерных цепей (5) и (6) состоит из двух компонентов на основе МОП транзистора с каналом p-типа и МОП транзистора с каналом n-типа, стоки которых соединены. Истоки МОП транзисторов с каналом p-типа Т1 и Т5 триггерной цепи (5) подключены к положительной шине питания (+Eпит), а истоки МОП транзисторов с каналом n-типа Т2 и Т6 - к отрицательной шине питания (-Eпит). При этом МОП транзисторы с каналом n-типа Т2 и Т6 в триггерной цепи (5) включены так, что сток каждого соединен с затвором другого. Затворы МОП транзисторов с каналом p-типа Т5 и Т1 в триггерной цепи (5) соединены с выходами (S+) и (S++) инвертирующих цепей (1) и (3) соответственно. Истоки МОП транзисторов с каналом p-типа Т3 и Т7 триггерной цепи (6) подключены к положительной шине питания (+Eпит), а истоки МОП транзисторов с каналом n-типа Т4 и Т8 - к отрицательной шине питания (-Eпит). При этом МОП транзисторы с каналом p-типа Т3 и Т7 в триггерной цепи (6) включены так, что сток каждого соединен с затвором другого. Затворы МОП транзисторов с каналом n-типа Т8 и Т4 в триггерной цепи (6) соединены с выходами (S-) и (S--) инвертирующих цепей (2) и (4) соответственно. Выходами схемы управления являются выходы (Х+) и (Х++) триггерной цепи (5) и выходы (Х-) и (Х--) триггерной цепи (6). К выходам схемы управления подключены четыре КМОП ключа (7)-(10), коммутирующие выход инвертора (ВЫХ) с шинами источника питания. Каждый из КМОП ключей состоит из МОП транзистора с каналом p-типа и МОП транзистора с каналом n-типа, затворы которых соединены с выходами одной из триггерных цепей. Для коммутации выхода инвертора (ВЫХ) к отрицательной шине питания (-Eпит) служит КМОП ключ (7), причем затвор МОП транзистора с каналом p-типа Т9 соединен с выходом (Х+) схемы управления, а затвор МОП транзистора с каналом n-типа Т10 - с выходом (Х++). Для коммутации выхода инвертора (ВЫХ) к земляной шине служит цепь из последовательно соединенных КМОП ключей (8) и (9), причем затворы МОП транзисторов с каналом p-типа Т11 и Т13 соединены с выходами (Х++) и (Х-) схемы управления, а затворы МОП транзисторов с каналом n-типа Т12 и Т14 - с выходами (Х+) и (Х--) соответственно. Для коммутации выхода инвертора (ВЫХ) к положительной шине питания (+Eпит) служит КМОП ключ (10), причем затвор МОП транзистора с каналом p-типа Т15 соединен с выходом (Х--) схемы управления, а затвор МОП транзистора с каналом n-типа Т16 - с выходом (Х-). Подложки МОП транзисторов с каналом n-типа Т18 и Т22 и МОП транзисторов с каналом p-типа Т19 и Т23 подключены к земляной шине. Подложки остальных МОП транзисторов с каналом p-типа подключены к положительной шине питания (+Eпит), а МОП транзисторов с каналом n-типа - к отрицательной шине питания (-Eпит). Устройство работает следующим образом. Сигнал с входа (ВХ) схемы троичного инвертора на КМОП транзисторах (фиг.1) одновременно поступает на затворы МОП транзистора с каналом p-типа Т17 и МОП транзистора с каналом n-типа Т18 инвертирующей цепи (1) и на затворы МОП транзистора с каналом p-типа Т19 и МОП транзистора с каналом n-типа Т20 инвертирующей цепи (2). В каждой из инвертирующих цепей (1) и (2) при любом логическом состоянии на входе (ВХ), если МОП транзистор с каналом p-типа работает в линейном режиме, то МОП транзистор с каналом n-типа оказывается в режиме отсечки, и наоборот, если МОП транзистор с каналом n-типа работает в линейном режиме, то МОП транзистор с каналом p-типа оказывается в режиме отсечки. При напряжении на входе (ВХ), соответствующем значению троичного кода «-1», МОП транзисторы Т17 и Т19 работают в линейном режиме, а МОП транзисторы Т18 и Т20 находятся в режиме отсечки. Напряжение в узле (S+) соответствует значению троичного кода «+1», а напряжение в узле (S-) - значению троичного кода «0». При напряжении на входе (ВХ), соответствующем значению троичного кода «0», МОП транзисторы Т17 и Т20 работают в линейном режиме, а МОП транзисторы Т18 и Т19 находятся в режиме отсечки. Напряжение в узле (S+) соответствует значению троичного кода «+1», а напряжение в узле (S-) - значению троичного кода «-1». При напряжении на входе (ВХ), соответствующем значению троичного кода «+1», МОП транзисторы Т18 и Т20 работают в линейном режиме, а МОП транзисторы Т17 и Т19 находятся в режиме отсечки. Напряжение в узле (S+) соответствует значению троичного кода «0», а напряжение в узле (S-) - значению троичного кода «-1». Таким образом, при любом логическом состоянии на входе (ВХ) за счет наличия в инвертирующих цепях (1) и (2) транзисторов в режиме отсечки невозможно, ни протекание сквозного статического тока от положительной шины питания (+Eпит) до земляной шины в инвертирующей цепи (1), ни протекание сквозного статического тока от земляной шины до отрицательной шины питания (-Eпит) в инвертирующей цепи (2), ни протекание сквозного статического тока от положительной шины питания (+Eпит) до отрицательной шины питания (-Eпит) через инвертирующие цепи (1) и (2). Протекание статического тока в инвертирующих цепях (1) и (2) обусловлено лишь токами утечки МОП транзисторов. Логические состояния сигналов в схеме троичного инвертора на КМОП транзисторах представлены в таблице 1. В зависимости от логического состояния сигнала на входе (ВХ), представленного в первом столбце таблицы 1, сигналы, сформированные инвертирующими цепями (1) и (2) на обозначенных соответственно выходах (S+) и (S-), представлены во втором и третьем столбцах таблицы 1. Сигнал с выхода (S+) инвертирующей цепи (1) поступает на затворы МОП транзистора с каналом p-типа Т21 и МОП транзистора с каналом n-типа Т22 инвертирующей цепи (3), а сигнал с выхода (S-) инвертирующей цепи (2) поступает на затворы МОП транзистора с каналом p-типа Т23 и МОП транзистора с каналом n-типа Т24 инвертирующей цепи (4). При любых логических состояниях на выходах инвертирующих цепей (1) и (2) транзисторы в каждой из инвертирующих цепей (3) и (4), аналогично вышеописанному, работают один в линейном режиме, а другой - в режиме отсечки. Согласно таблице 1 при напряжении на входе (ВХ), соответствующем значению троичного кода «-1», напряжение в узле (S+) соответствует значению троичного кода «+1», а напряжение в узле (S-) - значению троичного кода «0», МОП транзисторы Т22 и Т24 работают в линейном режиме, а МОП транзисторы Т21 и Т23 находятся в режиме отсечки. Напряжение в узле (S++) соответствует значению троичного кода «0», а напряжение в узле (S--) - значению троичного кода «-1». При напряжении на входе (ВХ), соответствующем значению троичного кода «0», напряжение в узле (S+) соответствует значению троичного кода «+1», а напряжение в узле (S-) - значению троичного кода «-1», МОП транзисторы Т22 и Т23 работают в линейном режиме, а МОП транзисторы Т21 и Т24 находятся в режиме отсечки. Напряжения в узлах (S++) и (S--) соответствуют значению троичного кода «0». При напряжении на входе (ВХ), соответствующем значению троичного кода «+1», напряжение в узле (S+) соответствует значению троичного кода «0», а напряжение в узле (S-) - значению троичного кода «-1», МОП транзисторы Т21 и Т23 работают в линейном режиме, а МОП транзисторы Т22 и Т24 находятся в режиме отсечки. Напряжение в узле (S++) соответствует значению троичного кода «+1», а напряжение в узле (S--) - значению троичного кода «0». Таким образом, при любом логическом состоянии на входе (ВХ) за счет наличия в инвертирующих цепях (3) и (4) транзисторов в режиме отсечки невозможно, ни протекание сквозного статического тока от положительной шины питания (+Eпит) до земляной шины в инвертирующей цепи (3), ни протекание сквозного статического тока от земляной шины до отрицательной шины питания (-Eпит) в инвертирующей цепи (4), ни протекание сквозного статического тока от положительной шины питания (+Eпит) до отрицательной шины питания (-Eпит) через инвертирующие цепи (3) и (4). Протекание статического тока в инвертирующих цепях (3) и (4) обусловлено лишь токами утечки МОП транзисторов. Сигналы, сформированные инвертирующими цепями (3) и (4) на обозначенных соответственно выходах (S++) и (S--) в зависимости от логического состояния сигнала на входе (ВХ), представлены в четвертом и пятом столбцах таблицы 1. Сигналы с выходов (S+) и (S++) инвертирующих цепей (1) и (3) поступают на затворы МОП транзисторов с каналом p-типа Т5 и Т1 триггерной цепи (5) соответственно. При этом на выходе триггерной цепи (5) формируются сигналы (Х+) и (Х++), представленные в шестом и седьмом столбцах таблицы 1. Сигналы с выходов (S-) и (S--) инвертирующих цепей (2) и (4) поступают на затворы МОП транзисторов с каналом n-типа Т8 и Т4 триггерной цепи (6) соответственно. При этом на выходе триггерной цепи (6) формируются сигналы (Х-) и (Х--), представленные в восьмом и девятом столбцах таблицы 1. При напряжениях на входе (ВХ), соответствующих значениям троичного кода «-1» и «0», напряжение в узле (S+) соответствует значению троичного кода «+1», а напряжение в узле (S++) - значению троичного кода «0», МОП транзисторы Т1 и Т6 в триггерной цепи (5) работают в линейном режиме, а МОП транзисторы Т2 и Т5 находятся в режиме отсечки. Напряжение в узле (Х+) соответствует значению троичного кода «+1», а напряжение в узле (Х++) - значению троичного кода «-1». При напряжении на входе (ВХ), соответствующем значению троичного кода «+1», напряжение в узле (S+) соответствует значению троичного кода «0», а напряжение в узле (S++) - значению троичного кода «+1», МОП транзисторы Т2 и Т5 в триггерной цепи (5) работают в линейном режиме, а МОП транзисторы Т1 и Т6 находятся в режиме отсечки. Напряжение в узле (Х+) соответствует значению троичного кода «-1», а напряжение в узле (Х++) - значению троичного кода «+1». При напряжении на входе (ВХ), соответствующем значению троичного кода «-1», напряжение в узле (S-) соответствует значению троичного кода «0», а напряжение в узле (S--) - значению троичного кода «-1», МОП транзисторы ТЗ и Т8 в триггерной цепи (6) работают в линейном режиме, а МОП транзисторы Т4 и Т7 находятся в режиме отсечки. Напряжение в узле (X-) соответствует значению троичного кода «+1», а напряжение в узле (X--) - значению троичного кода «-1». При напряжениях на входе (ВХ), соответствующих значениям троичного кода «0» и «+1», напряжение в узле (S-) соответствует значению троичного кода «-1», а напряжение в узле (S--) - значению троичного кода «0», МОП транзисторы Т4 и Т7 в триггерной цепи (6) работают в линейном режиме, а МОП транзисторы Т3 и Т8 находятся в режиме отсечки. Напряжение в узле (Х-) соответствует значению троичного кода «-1», а напряжение в узле (Х--) - значению троичного кода «+1». Таким образом, при любом логическом состоянии на входе (ВХ) за счет наличия в триггерных цепях (5) и (6) транзисторов в режиме отсечки невозможно протекание сквозного статического тока от положительной шины питания (+Eпит) до отрицательной шины питания (-Eпит). Протекание статического тока в триггерных цепях (5) и (6) обусловлено лишь токами утечки МОП транзисторов. Сигналы (Х+), (Х++), (Х-) и (Х--) с выходов триггерных цепей (5) и (6) управляют работой КМОП ключей (7)-(10). Согласно таблице 1 при напряжении на входе (ВХ), соответствующем значению троичного кода «-1», напряжение в узлах (Х+) и (Х-) соответствует значению троичного кода «+1», а напряжение в узлах (Х++) и (X--) - значению троичного кода «-1», КМОП ключи (8) и (10) замкнуты, а КМОП ключи (7) и (9) разомкнуты. Замкнутый КМОП ключ (10) коммутирует выход (ВЫХ) к положительной шине питания (+Eпит). За счет разомкнутых КМОП ключей (7) и (9) пути для протекания сквозного тока от положительной шины питания (+Eпит) к остальным шинам источника питания отсутствуют. При напряжении на входе (ВХ), соответствующем значению троичного кода «0», напряжение в узлах (Х+) и (Х--) соответствует значению троичного кода «+1», а напряжение в узлах (Х-) и (Х++) - значению троичного кода «-1», КМОП ключи (8) и (9) замкнуты, а КМОП ключи (7) и (10) разомкнуты. Замкнутые последовательно включенные КМОП ключи (8) и (9) коммутируют выход (ВЫХ) к земляной шине. За счет разомкнутых КМОП ключей (7) и (10) пути для протекания сквозного тока от земляной шины к остальным шинам источника питания отсутствуют. При напряжении на входе (ВХ), соответствующем значению троичного кода «+1», напряжение в узлах (Х+) и (Х-) соответствует значению троичного кода «-1», а напряжение в узлах (Х++) и (Х--) - значению троичного кода «+1», КМОП ключи (7) и (9) замкнуты, а КМОП ключи (8) и (10) разомкнуты. Замкнутый КМОП ключ (7) коммутирует выход (ВЫХ) к отрицательной шине питания (-Eпит). За счет разомкнутых КМОП ключей (8) и (10) пути для протекания сквозного тока от отрицательной шины питания (-Eпит) к остальным шинам источника питания отсутствуют. Таким образом, протекание статического тока в КМОП ключах (7)-(10) обусловлено лишь токами утечки МОП транзисторов.

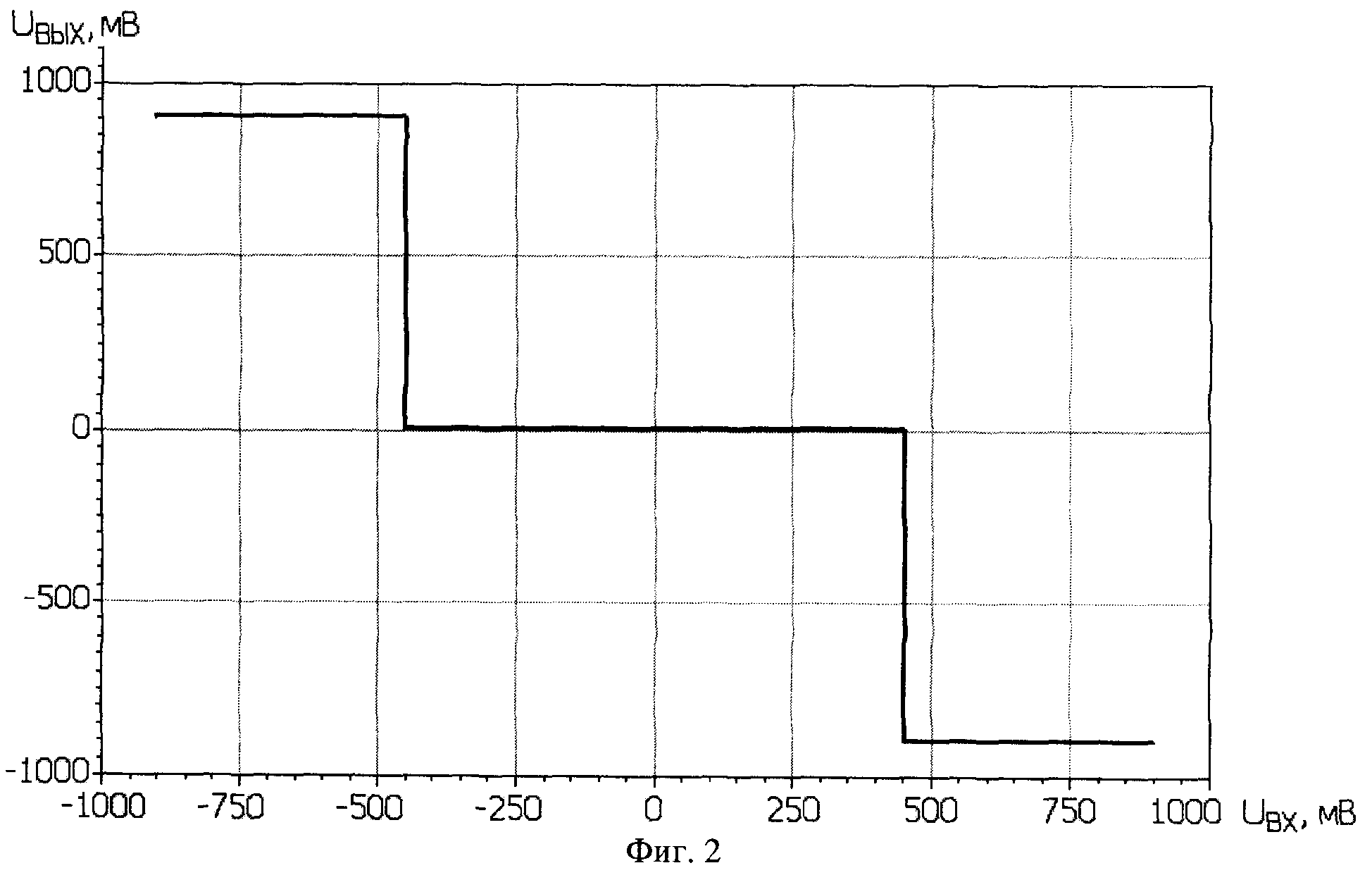

Представленное описание работы устройства подтверждается результатами моделирования схемы троичного инвертора на КМОП транзисторах. Моделирование проводилось при напряжении питания ±0,9 В с использованием параметров 0,18 мкм МОП технологии. На фиг.2 приведена передаточная характеристика по напряжению троичного инвертора на КМОП транзисторах. Напряжение +0,9 В соответствует значению троичного кода «+1», напряжение 0 В - значению троичного кода «0», а напряжение -0,9 В - значению троичного кода «-1». Пороги переключения составляют -0,45 В и +0,45 В. На фиг.3 представлены зависимости напряжений в узлах (S+), (S++), (S-), (S--) схемы управления от напряжения на входе (ВХ) троичного инвертора на КМОП транзисторах. На фиг.4 представлены зависимости напряжений на выходах (Х+), (Х++), (Х-), (X--) схемы управления от напряжения на входе (ВХ). На фиг.5 приведены эпюры напряжений на входе (ВХ) и выходе (ВЫХ) схемы троичного инвертора на КМОП транзисторах. Представленные на фиг.2-5 графики подтверждают правильность функционирования троичного инвертора на КМОП транзисторах, зависимости напряжений на графиках соответствуют зависимостям значений троичного кода в таблице 1. Статические токи, протекающие в схеме троичного инвертора на КМОП транзисторах, от положительной шины источника питания (+Eпит) и отрицательной шины источника питания (-Eпит) обозначены I+Eпит и I-Eпит соответственно. Данные из таблицы 2 подтверждают, что при напряжениях на выходе (ВЫХ) троичного инвертора на КМОП транзисторах, соответствующих значениям троичного кода «+1», «0», «-1», величины статических токов обусловлены лишь токами утечки МОП транзисторов и составляют десятки пикоампер. Оценка показывает, что при тех же параметрах технологии, напряжении питания и аналогичных размерах транзисторов в схеме прототипа при напряжении на входе, соответствующем значению троичного кода «0», статический ток составляет десятки микроампер.

Таким образом, результаты моделирования троичного инвертора на КМОП транзисторах подтверждают правильное функционирование схемы. Протекание статического тока в схеме троичного инвертора на КМОП транзисторах обусловлено лишь токами утечки МОП транзисторов. За счет уменьшения величины статических токов до значений токов утечки МОП транзисторов обеспечено снижение статической потребляемой мощности. Формула изобретения Троичный инвертор на КМОП транзисторах, состоящий из четырех КМОП ключей и схемы управления, содержащей первый МОП транзистор с каналом р-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком второго МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; третий МОП транзистор с каналом р-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком четвертого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; пятый МОП транзистор с каналом р-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком шестого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания, а затвор шестого МОП транзистора соединен со стоком первого МОП транзистора; седьмой МОП транзистор с каналом р-типа, исток и подложка которого подключены к положительной шине питания, а сток соединен со стоком восьмого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания, а затвор седьмого МОП транзистора соединен со стоком третьего МОП транзистора; и формирующей сигналы для коммутации четырех КМОП ключей, причем первый КМОП ключ, который в замкнутом состоянии коммутирует выход инвертора к отрицательной шине питания, состоит из девятого МОП транзистора с каналом р-типа и десятого МОП транзистора с каналом n-типа, стоки которых подключены к отрицательной шине питания, а истоки соединены с выходом инвертора; второй и третий КМОП ключи соединены последовательно и в замкнутом состоянии коммутируют выход инвертора к земляной шине; второй КМОП ключ состоит из одиннадцатого МОП транзистора с каналом р-типа и двенадцатого МОП транзистора с каналом n-типа, стоки которых подключены к земляной шине; третий КМОП ключ состоит из тринадцатого МОП транзистора с каналом р-типа и четырнадцатого МОП транзистора с каналом n-типа, истоки которых соединены с выходом инвертора; истоки одиннадцатого и двенадцатого МОП транзисторов и стоки тринадцатого и четырнадцатого МОП транзисторов соединены; четвертый КМОП ключ, который в замкнутом состоянии коммутирует выход инвертора к положительной шине питания, состоит из пятнадцатого МОП транзистора с каналом р-типа и шестнадцатого МОП транзистора с каналом n-типа, истоки которых подключены к положительной шине питания, а стоки соединены с выходом инвертора; затворы девятого и двенадцатого МОП транзисторов соединены со стоком первого МОП транзистора, затворы десятого и одиннадцатого МОП транзисторов соединены со стоком пятого МОП транзистора, затворы тринадцатого и шестнадцатого МОП транзисторов соединены со стоком третьего МОП транзистора, затворы четырнадцатого и пятнадцатого МОП транзисторов соединены со стоком седьмого МОП транзистора, подложки девятого, одиннадцатого, тринадцатого и пятнадцатого МОП транзисторов подключены к положительной шине питания, а подложки десятого, двенадцатого, четырнадцатого и шестнадцатого МОП транзисторов подключены к отрицательной шине питания, отличающийся тем, что затвор второго МОП транзистора соединен со стоком пятого МОП транзистора, затвор третьего МОП транзистора соединен со стоком седьмого МОП транзистора, в схему управления добавлены восемь МОП транзисторов, которые пронумерованы с семнадцатого по двадцать четвертый, причем исток и подложка семнадцатого МОП транзистора с каналом р-типа подключены к положительной шине питания, а сток соединен со стоком восемнадцатого МОП транзистора с каналом n-типа, исток и подложка которого подключены к земляной шине; исток и подложка девятнадцатого МОП транзистора с каналом р-типа подключены к земляной шине, а сток соединен со стоком двадцатого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; на затворы семнадцатого, восемнадцатого, девятнадцатого и двадцатого МОП транзисторов подается входной сигнал; исток и подложка двадцать первого МОП транзистора с каналом р-типа подключены к положительной шине питания, а сток соединен со стоком двадцать второго МОП транзистора с каналом n-типа, исток и подложка которого подключены к земляной шине; исток и подложка двадцать третьего МОП транзистора с каналом р-типа подключены к земляной шине, а сток соединен со стоком двадцать четвертого МОП транзистора с каналом n-типа, исток и подложка которого подключены к отрицательной шине питания; затворы пятого, двадцать первого и двадцать второго МОП транзисторов соединены со стоком семнадцатого МОП транзистора; затворы восьмого, двадцать третьего и двадцать четвертого МОП транзисторов соединены со стоком девятнадцатого МОП транзистора; затвор первого МОП транзистора соединен со стоком двадцать первого МОП транзистора, а затвор четвертого МОП транзистора соединен со стоком двадцать третьего МОП транзистора. РИСУНКИ

| | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | | | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||