Вначале 70-х годов появилась первая большая интегральная микросхема, выполнявшая функции центрального процессора (ЦП) вычислительной машины

| Вид материала | Документы |

- Первая программа для вычислительной машины была написана: Адой Лавлейс, 90.62kb.

- Проектирование работы в организации функции управления организацией, 764.2kb.

- Реферат Интегральная, 452.33kb.

- 1 История развития информатики, 44.2kb.

- Операционная система в наибольшей степени определяет облик всей вычислительной системы, 1557.26kb.

- Определения, 430.8kb.

- Инте Республики Коми 02. 12. 2002г.) (новая редакция) г. Инта 2003г статья, 545.3kb.

- Лавлейс, Ада Авгу́ста А́да Кинг (урождённая Ба́йрон), графиня Ла́влейс, 45.48kb.

- Разработка межкластерного коммутатора для организации многопроцессорного вычислительного, 99.46kb.

- Программа дисциплины гсэ. 01 Методология и история кибернетики, информатики и вычислительной, 194.68kb.

1 2

ПРЕДИСЛОВИЕ

В начале 70-х годов появилась первая большая интегральная микросхема, выполнявшая функции центрального процессора (ЦП) вычислительной машины. Из-за своего микроминиатюрного исполнения и, возможно, довольно слабых функциональных возможностей она была названа микропроцессором. После примерно двухлетнего периода адаптации пользователей к новому компоненту цифровых систем началось беспрецедентно быстрое развитие микропроцессорной техники. За короткое время сменилось несколько поколений микропроцессоров, и новейшие 16-битные микропроцессоры по своим возможностям приближаются к современным мини-ЭВМ. Быстро расширяющаяся сфера применений микропроцессоров, по-видимому, окажет заметное влияние на дальнейшее развитие практически всех областей народного хозяйства. Массовый выпуск недорогих микропроцессоров позволяет рассредоточить вычислительные возможности по всем компонентам системы, что улучшает ее экономические показатели. Доступность микропроцессоров оправдывает их применение в таких областях, в которых использование других средств вычислительной техники невозможно по экономическим соображениям.

В России освоен промышленный выпуск более десяти микропроцессорных семейств Изданные переводные монографии содержат довольно общие сведения, и их можно рекомендовать только для первого знакомства с микропроцессорной техникой. К тому же в переводной литературе описаны микропроцессоры, не имеющие отечественных аналогов. Если с аппаратными средствами микропроцессорных систем можно познакомиться по техническим описаниям, то литература по программированию микропроцессорных систем практически отсутствует. Предлагаемый материал призван, в некоторой степени, восполнить этот пробел.

Выбор в качестве объекта изучения микропроцессора К580ИК80 (зарубежный аналог—микропроцессор 8080 фирмы Intel) объясняется тем, что он выполнен по классической структуре, в течение продолжительного времени он был и остается весьма популярным до сих пор. Достаточно напомнить, что 8080 в течение ряда лет оставался самым распространенным зарубежным микропроцессором и в последующих разработках фирмы Intel (микропроцессоры 8080А, 8085) сохранена программная совместимость с 8080. Кроме того, наличие у этого микропроцессора фиксированной системы команд облегчает составление прикладных программ.

При подготовке материалов лекций автор использовал терминологию и обозначения на схемах, принятых в справочниках. Мнемоническое обозначение команд сохранено в виде, принятом в зарубежной практике.

1 МИКРОПРОЦЕССОР К580ИК80

Микропроцессор К580ИК80 (далее сокращенно К580) представляет собой монолитный параллельный 8-битный процессор, имеющий фиксированную систему команд и классическую архитектуру с отдельными шинами адреса и данных. Он рассчитан на самые разнообразные применения в качестве ядра микропроцессорной системы (МП системы), выполняющего функции преобразования цифровых данных. Основная область его применения — специализированные системы (контроллеры), работающие по фиксированной программе. Микропроцессор выполнен по NMOП-технологии и выпускается в 48-контактном керамическом корпусе с двусторонним расположением выводов (типа DIP). На кристалле микропроцессора размещено около 5000 транзисторов.

1.1 АРХИТЕКТУРА МП СИСТЕМЫ НА БАЗЕ К580

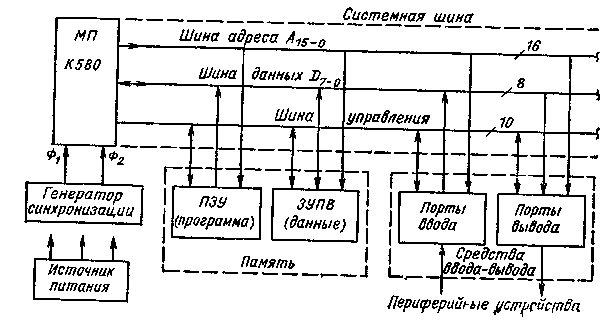

Общий вид системы на базе микропроцессора К580 показан на рисунке 1.1. В ней выделяют три основных компонента — центральный процессор, функции которого выполняет микропроцессор, память и средства ввода-вывода.

Рисунок 1.1 - Основные компоненты МП системы

Микропроцессор является единственным активным компонентом системы и реализует следующие функции:

- управляет выполнением команд программы: выбирает команду, считывает операнды, преобразует их в соответствии со смыслом команды и определяет адрес следующей команды;

- управляет обменом различной информацией между компонентами системы;

- реагирует на разнообразные внешние сигналы.

Память МП системы представлена программным энергонезависимым постоянным запоминающим устройством (ПЗУ), допускающим только считывание хранимой информации, и полупроводниковой оперативной энергозависимой памятью (или запоминающим устройством с произвольной выборкой — ЗУПВ), выполняющей операции считывания (READ) и записи (WRITE), которые называются также обращением (доступом) к памяти.

В функциональном отношении память состоит из однотипных ячеек, длина (разрядность) которых совпадает с длиной слова микропроцессора, т. е. составляет 8 бит (1 байт). Ячейки пронумерованы, номера их называются адресами, и для обращения к ячейке достаточно указать ее адрес. Совокупность ячеек, к которым потенциально может адресоваться микропроцессор, называется адресным пространством (полем) памяти, а фактически имеющиеся ячейки образуют рабочее (физическое) пространство памяти МП системы.

Адресное пространство микропроцессора К580 составляет 64 Кбайт (65536 ячеек). Адресное пространство графически изображается в виде столбца из 64 Кстрок (ячеек) с шестнадцатиразрядными двоичными адресами от 00...00 до 11...11. В последнее время в современной зарубежной и отечественной литературе адреса представляются в шестнадцатеричной системе счисления, как 0000…FFFF. В МП системе различные области адресного пространства группируются в блоки, образующие так называемую карту памяти. Блоки могут относиться к аппаратным устройствам, например блоки ПЗУ и ЗУПВ, или к программным образованьям, например основная программа, подпрограммы, стандартные программы ввода-вывода и др. Нумерация ячеек обычно производится сверху вниз и реже — снизу вверх.

Средства ввода-вывода (ВВ) представлены портами ввода (входными портами) и вывода (выходными портами). Информация от устройств ввода поступает в порты ввода и считывается микропроцессором, а порты вывода воспринимают информацию от микропроцессора и передают ее в устройства вывода. В простейшем случае порты ввода и вывода представляют собой буферные регистры, имеющие определенные адреса и выполняющие функции сопряжения МП системы с разнообразными периферийными устройствами («внешним миром»).

Взаимодействие микропроцессора с памятью и средствами ВВ осуществляется по системной шине, состоящей из нескольких десятков линий (число линий в шине иногда называют ее шириной). Рассмотрим основные характеристики этих линий [].

Функциональное назначение:

линии адреса, образующие шину адреса A15 – А0;

линии данных, образующие шину данных D7 – D0;

линии управления, образующие шину управления;

линии синхронизации и питания.

Направление передачи информации:

- линии, направленные в микропроцессор;

- линии, направленные от микропроцессора;

- двунаправленные линии, по которым сигналы передаются в обоих направлениях.

В микропроцессоре К580 двунаправленными являются только линии шины данных D7 – D0, а все остальные— однонаправленными.

Протокол обмена информацией по системной шине.

Этот протокол включает в себя правила организации последовательностей сигналов, обеспечивающих правильную передачу информации между компонентами системы.

Электрические спецификации сигналов, действующих на линиях системной шины.

Примерами таких спецификаций являются гарантированные уровни электрических напряжений, идентифицирующих логические состояния 0 и 1, нагрузочная способность и др.

Рассмотрим функциональное назначение линий.

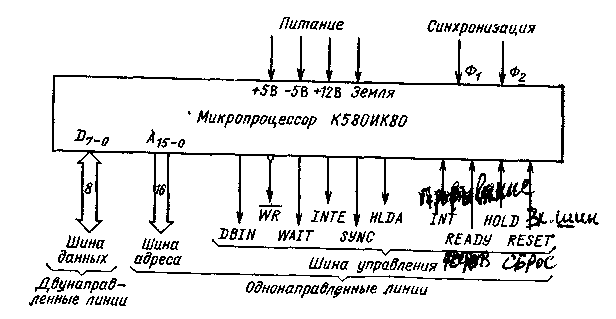

На рисунке 1.2 приведена системная шина МП систем на базе микропроцессора К580.

Шина адреса (адресная шина, адресная магистраль, адресный канал), состоящая из 16 линий (A15 – А0), предназначена для передачи адресов от микропроцессора в память и порты ввода-вывода. Другими словами, сигналы адреса идентифицируют внешние регистр-источник или регистр-получатель, участвующие в обмене данными с одним из внутренних регистров микропроцессора.

Рисунок 1.2 - Линии системной шины

Шестнадцать линий шины адреса определяют адресное пространство из 64 Кбайт. Старшие восемь линий адреса (A15 – А8) называются адресом страницы, а младшие восемь линий (A7 – А0)—адресом в странице (или строкой).

При записи адресов чаще всего используется 16-ричная система, поэтому диапазон адресов составляет от 000016 до FFFF16 (далее основание системы не указывается). Память системы организуется по круговому принципу, т. е. после ячейки с максимальным адресом FFFF следует ячейка с минимальным адресом 0000.

Применение 16-битной шины адреса в микропроцессорах с 8-битным словом данных представляется весьма логичным:

- адрес можно хранить в двух смежных ячейках памяти;

- адресного пространства из 64 Кбайт достаточно для широкого диапазона применений.

В процессе выполнения программы адреса формируются в микропроцессоре и передаются в другие компоненты системы.

Для реализации в системе специального режима обмена данными с быстродействующими периферийными устройствами, называемого прямым (непосредственным) доступом к памяти, в схеме микропроцессора на линиях шины адреса предусмотрен буфер с Z-состоянием, т. е. буфер с тремя возможными состояниями, два из которых соответствуют уровням напряжений логических 0 и 1 (при этом компонент подключен к шине адреса), а третье - это высокоимпедансное (плавающее – с большим выходным сопротивлением) состояние, когда компонент отключен от шины.

Шину данных (информационная магистраль, числовая магистраль, канал данных, информационная шина), являющуюся основным информационным трактом МП системы, образуют восемь двунаправленных тристабильных линий D7 – D0. По этой шине осуществляется обмен любой информацией между всеми компонентами системы, в частности, по ней передаются команды, операнды, результаты операций, вводимые и выводимые данные. Двунаправленность шины данных означает возможность передачи информации в обоих направлениях (от микропроцессора и в микропроцессор). Направление передачи определяется специальными управляющими сигналами, которые генерирует микропроцессор. Разумеется, в любой момент времени по шине данных производится одна передача в одном направлении, т. е. шина данных работает в мультиплексном режиме.

Чтобы упростить подключение компонентов МП системы к общей шине данных, на выходах линий данных (шине данных) всех компонентов обычно предусматриваются буферы с Z-состоянием. Управление состоянием буферов осуществляется внешними сигналами выбора кристалла CS (разрешения кристалла СЕ, выбора устройства DS). Обычно они формируются путем декодирования сигналов со старших линий шины адреса.

Шина управления (управляющая шина, управляющая магистраль, управляющий канал), состоящая из десяти линий, служит для передачи управляющих сигналов, определяющих характер и порядок функционирования компонентов МП системы. Управляющие сигналы микропроцессора К580 можно объединить в следующие группы.

1 Группа сигналов управления состоянием микропроцессора:

1.1 - входной сигнал сброса (инициализации) RESET, заставляющий микропроцессор начать выполнение программы с нулевой ячейки памяти;

1.2 - входной сигнал готовности READY, поступающий от других компонентов МП системы, который служит для приостановки действий микропроцессора до тех пор, пока компонент не будет готов к обмену данными с микропроцессором. Наличие этого сигнала позволяет организовать асинхронный обмен данными с такими компонентами, быстродействия которых недостаточно для работы синхронно с микропроцессором;

1.3 - выходной сигнал ожидания WAIT, свидетельствующий о том, что микропроцессор приостановлен.

2 Группа сигналов управления шинами адреса и данных:

2.1 - выходной сигнал считывания (приема) DBIN, определяющий направление передачи по шине данных в микропроцессор. Слово из адресуемого внешнего регистра, представленное уровнями напряжений на шине данных, загружается в один из внутренних регистров микропроцессора;

2,2 - выходной сигнал записи (выдачи)

, определяющий направление передачи по шине данных от микропроцессора. Уровни напряжений на линиях шины данных представляют собой слово из внутреннего регистра, подлежащее записи в адресуемый внешний регистр;

, определяющий направление передачи по шине данных от микропроцессора. Уровни напряжений на линиях шины данных представляют собой слово из внутреннего регистра, подлежащее записи в адресуемый внешний регистр;2.3 - входной сигнал запроса шины (захвата) HOLD, информирующий микропроцессор о том, что быстродействующее периферийное устройство должно использовать шины адреса и данных для прямого обмена данными с памятью МП системы без участия микропроцессора. Реагируя на этот сигнал, микропроцессор приостанавливает выполнение программы и переводит буферы шин адреса и данных в высокоимпедансное состояние. Таким образом реализуется упомянутый выше режим прямого доступа к памяти (ПДП).

2.4 - выходной сигнал подтверждения запроса шин (захвата) HLDA, означающий, что буфера шин адреса и данных микропроцессора переведены в высокоимпедансное состояние и шинами может распоряжаться периферийное устройство, инициировавшее прямой доступ к памяти.

3 Группа сигналов, связанных с прерываниями, т. е. с запросами периферийных устройств на обмен информацией:

3.1 - входной сигнал запроса прерывания INТ, означающий готовность периферийного устройства к обмену данными. Реагируя на этот сигнал, микропроцессор прерывает выполнение текущей программы, временно запоминает ее состояние, обслуживает периферийное устройство (обменивается с ним данными), после чего восстанавливает прежнее состояние и возобновляет выполнение прерванной программы;

3.2 - выходной сигнал разрешения прерывания INТЕ, определяющий возможность или невозможность обслуживаний микропроцессором запросов периферийных устройств.

При высоком уровне INTE микропроцессор реагирует на сигнал INT (прерывания разрешены), а при низком – не реагирует (прерывания запрещены или замаскированы). Сигнал INТЕ является выходным сигналом внутреннего триггера разрешения прерываний, состоянием которого можно управлять программно: команда EI разрешает прерывания, а команда DI — запрещает. Следовательно, программист всегда может защитить от прерываний критические участки прикладной программы.

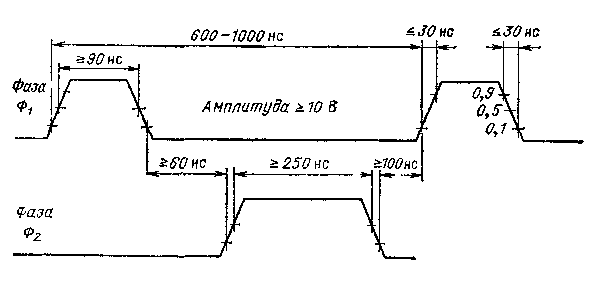

Микропроцессор имеет три линии синхронизации. На входы Ф1 и Ф2 подаются двухфазные неперекрывающиеся сигналы от главного генератора синхронизации («часов»). Они определяют моменты выполнения большинства действий в МП системе, т. е, создают временную базу функционирования системы. Период сигналов синхронизации определяет производительность МП системы. На рис. 1.3 показаны сигналы синхронизации микропроцессора К580. Начала тактов определяются нарастающими фронтами сигналов Ф1, а большинство действий в системе привязано к нарастающим фронтам сигналов Ф2.

Выходной сигнал синхронизации SYNC идентифицирует начало каждого машинного цикла, в течение которого микропроцессор адресуется к внешнему регистру, обменивается с ним данными и при необходимости производит внутреннее преобразование данных. Одновременно с сигналом SYNC микропроцессор выдает на шину данных байт состояния, содержащий информацию о действиях микропроцессора в текущем машинном цикле.

Рисунок 1.3 - Двухфазные сигналы синхронизации

При рассмотрении управляющих сигналов нетрудно заметить парность некоторых из них (READY—WAIT, HOLD—HLDA). Реакция на сигнал, инициировавший некоторое действие, ответным сигналом, который подтверждает выполнение этого действия, называется квитированием («рукопожатием», или согласованным обменом). С помощью квитирования вводится асинхронный режим интерфейса компонентов МП системы и обеспечивается максимальное быстродействие, поскольку на каждое действие отводится временной интервал, фактически необходимый для производства этого действия.

Сделаем небольшое отступление, касающееся кодирования и обозначения сигналов. Во всех МП системах применяются электрические сигналы, представленные двумя уровнями напряжения (двоичные сигналы). В позитивной логике единице соответствует более положительный (высокий) уровень напряжения, а логическому нулю — более отрицательный (низкий). В негативной логике используется противоположное кодирование. Чтобы избежать возможной путаницы между сигналами позитивной и негативной логики, введем следующее соглашение.

Если сигнал вызывает выполнение некоторого действия или обозначает определенное условие при высоком уровне напряжения или при переходе от низкого уровня к высокому, будем называть его активным при высоком уровне напряжения, или Н-активным. Если сигнал вызывает выполнение закрепленной за ним функции, имея низкий уровень напряжения или при переходе от высокого уровня к низкому, будем называть его активным при низком уровне, или L-активным. Согласно этим определениям в микропроцессоре К580 есть только один L-активный сигнал

, а все остальные сигналы являются Н-активными. На схемах L-активные сигналы обозначаются небольшим кружком (инверсия) в месте входа или выхода соответствующих им линий. В тексте активные сигналы отмечаются чертой отрицания над наименованием сигнала. Основная причина введения L-активных сигналов скрыта в простоте объединения по ИЛИ сигналов от нескольких источников (монтажное ИЛИ). Кроме того, выходной каскад с L-активным сигналом большую часть времени находится в выключенном состоянии, т. е. потребляет минимальную энергию.

, а все остальные сигналы являются Н-активными. На схемах L-активные сигналы обозначаются небольшим кружком (инверсия) в месте входа или выхода соответствующих им линий. В тексте активные сигналы отмечаются чертой отрицания над наименованием сигнала. Основная причина введения L-активных сигналов скрыта в простоте объединения по ИЛИ сигналов от нескольких источников (монтажное ИЛИ). Кроме того, выходной каскад с L-активным сигналом большую часть времени находится в выключенном состоянии, т. е. потребляет минимальную энергию.Для избежания ошибок при определении моментов изменения уровней сигналов (передний и задний фронт, положительный и отрицательный фронт) переход от низкого уровня к высокому называется нарастающим фронтом и обозначается ↑, а от высокого к низкому — спадающим фронтом и обозначается - ↓.

Одной из особенностей компонентов МП системы, обеспечивающей возможность их электрического сопряжения друг с другом и с разнообразными периферийными устройствами, является ТТЛ-совместимость. Выбop такого стандарта для интерфейса объясняется очень широким распространением приборов и устройств на ТТЛ- схемах. Все входные и выходные сигналы микропроцессора К580 совместимы с ТТЛ- схемами. Выходные сигналы микропроцессора являются маломощными—их нагрузочная способность эквивалентна одному входу ТТЛ- схемы, а емкостная нагрузка не должна превышать 100 пкФ.

В большинстве МП систем нагрузки на линии шин адpeca и данных, а также на линии некоторых управляющих сигналов могут превышать предельно допустимые для микропроцессора. В таких ситуациях необходимо использовать микросхемы усилителей-формирователей (драйверов).

Напряжения питания микропроцессора К580 составляют + 12 В ±5%, +5 В±5%;—5 В ±5%, потребляемая мощность не превышает 1 Вт, а рабочий температурный диапазон составляет от —10 до +70°C.

1 2 ПРОГРАММНАЯ МОДЕЛЬ МП-СИСТЕМЫ

Основным элементом архитектуры МП системы обычно является регистр, т. е. некоторое физическое устройство, способное воспринимать, хранить и выдавать слово информации. Разрядность всех регистров в системе равна или кратна длине слова микропроцессора. Из всего разнообразия схем триггерных регистров наибольшее распространение в МП системах получили простейшие регистры-защелки (фиксаторы), выполненные на D-триггерах. Восьмибитный регистр-защелка имеет восемь входных линий DI7 – DI0, восемь выходных линий D7 – D0 и управляющий сигнал С (сигнал синхронизации). При высоком уровне сигнала С выходные сигналы на линиях D7 – D0 повторяют значения входных сигналов на этих линиях (с определенной задержкой распространения). Когда сигнал С изменяется от высокого уровня к низкому, на выходных линиях D7 – D0 фиксируются и сохраняются (эффект «защелкивания») те значения сигналов на входных линиях DI7 – DI0, которые действовали в момент перехода. Для правильной работы регистра-защелки необходимо, чтобы входные сигналы не изменялись в течение некоторого интервала времени до начала действия спадающего фронта сигнала С и в течение некоторого интервала времени после окончания действия этого фронта. Первый из этих интервалов называют временем установления (set-up time), второй — временем сохранения (hold time). Регистр-защелка обычно имеет асинхронный вход сброса CLR.

Ячейки памяти и порты ввода-вывода, по существу, являются регистрами, и поэтому любая МП система состоит из огромного числа регистров, а функционирование ее (выполнение программы) заключается в передачах слов между регистрами. Порядок передач, часть из которых сопровождается преобразованиями слов, определяется последовательностью команд программы. Команды дешифрируются устройством управления (управляющим автоматом) микропроцессора и преобразуются в определенные последовательности управляющих сигналов.

Команды состоят из двух полей: поля операции (оператор), которое определяет выполняемое действие или операцию, и поля операнда — данные, участвующие в операции. Длина оператора обычно составляет 1 байт, и содержимое его называется кодом операции. В микропроцессорах используется адресный принцип построения команд — в поле операнда содержится не значение операнда, хотя это допускается в командах с непосредственной адресацией, а адрес регистра, содержащего операнд и называемого регистром-источником, или S-регистром.

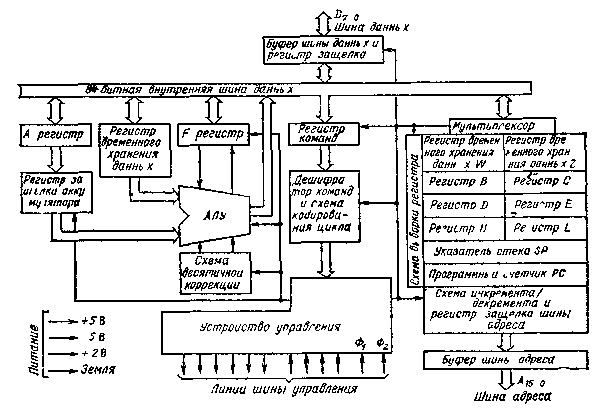

Рисунок 1.4 - Структурная схема микропроцессора

Блок регистров организован в шесть 16-битных регистров: программный счетчик PC, указатель стека SP, регистр временного хранения W, Z и три пары 8-битных регистров общего назначения В, С; D, Е; Н, L. Программный счетчик хранит адрес текущей ячейки программной памяти. Указатель стека адресует последнюю занятую ячейку (или «верхушку») стека. Перед загрузкой в стек каждого байта производится декремент (уменьшение содержимого на 1) указателя стека, а после извлечения из стека каждого байта выполняется автоматический инкремент указателя стека. Инициализация указателя стека производится специальной командой LXI SP, поэтому в качестве стека допускается использовать любую область внешнего ОЗУ. Регистр W, Z недоступен программисту и используется при выполнении команд для временного хранения слов.

В микропроцессоре К580 применяются одно- и двухадресные команды, причем двухадресными являются только команды межрегистровых передач. В таких командах приходится адресовать регистр-источник и регистр-получатель (D-регистр). Во всех бинарных командах, связанных с преобразованием данных, в качестве подразумеваемого и поэтому неадресуемого операнда используется содержимое важнейшего внутреннего регистра микропроцессора — аккумулятора, или А-регистра (накопительный регистр, накапливающий сумматор, накопитель, регистр-сумматор, регистр результата). Обычно результат операции загружается в аккумулятор. Таким образом, аккумулятор является узловой точкой всех преобразований данных и основным рабочим регистром микропроцессора. Он выполнен как регистр-защелка, вход которого связан с выходом АЛУ, а выход подключается к одному из входов АЛУ.

Арифметическо-логическое устройство представляет собой сложную двухвходовую комбинационную схему, которая сигналами от устройства управления коммутируется на выполнение определенной операции. Арифметическо-логическое устройство микропроцессора К580 рассчитано на параллельное преобразование двух 8-битных операндов.

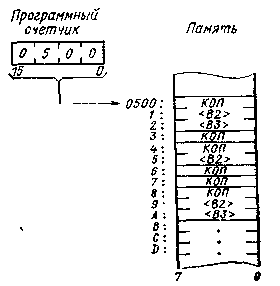

При указании в команде полного 16-битного адреса памяти она становится 3-байтной: первым байтом <В1> всегда является код операции; вторым — байт <В2>, содержащий младшие 8 бит адреса А7-А0; а третьим—байт <В3>, содержащий старшие 8 бит адреса А15-А8. Такая команда занимает в программной памяти три смежные ячейки. Для сокращения длины программы и экономии программной памяти в микропроцессор введены такие режимы адресации, которые позволяют применять одно- и двухбайтные команды. На рисунке 1.5 показано размещение фрагмента программы в памяти. Для хранения текущего адреса программной памяти используется программный счетчик PC или Р-регистр (счетчик команд, счетчик инструкций, счетчик адреса команды, указатель команды). При каждом обращении к программной памяти производится автоматическое увеличение содержимого программного счетчика на единицу, называемое инкрементом.

Рисунок 1.5 - Размещение команд программы в памяти

Выполнение команды в МП системе, как и любой вычислительной машине, состоит из следующих крупных этапов: выборка команды, считывание операнда и собственно выполнение операции. В свою очередь каждый из этапов включает в себя несколько более мелкиx шагов. Рассмотрим выполнение 3-байтной команды, считая, что в программном счетчике содержится адрес 0500.

На первом шаге содержимое программного счетчика по шине адреса передается в память и сигналом считывания DBIN производится выборка первого байта команды — им всегда является код операции. По шине данных код операции передается в микропроцессор, загружается в регистр команд и хранится в нем в течение всего последующего времени выполнения команды. Одновременно с этим производится инкремент программного счетчика, который указывает на следующую ячейку программной памяти с адресом 0501.

Регистр команд связан со сложной схемой дешифрирования и синхронизации, из которой информация о коде операции поступившей из памяти команды передается в устройство управления. На это же устройство подаются сигналы синхронизации и внешние управляющие сигналы. Устройство управления генерирует необходимые последовательности сигналов, коммутирующих схемы самого микропроцессора и поступающих в другие компоненты системы. Основу устройства управления микропроцессора К580 составляют программируемые логические матрицы.

По коду операции устройство управления распознает 3-байтную команду и осуществляет необходимые действия по выборке второго и третьего байтов команды. Для этого содержимое PC (в данном случае 0501) по шине адреса передается в память, осуществляется считывание второго байта <В2> команды и передача его по шине данных в младшие биты регистра адреса памяти (регистр Z). Одновременно производится инкремент PC, который указывает на следующую ячейку программной памяти с адресом 0502. Аналогично в старшие биты регистра адреса памяти (регистр W) считывается третий байт <ВЗ> данной команды. Выборка команды завершена, a PC содержит адрес 0503.

На этапе считывания операнда содержимое регистра адреса памяти по шине адреса передается в память, сигнал DBIN производит считывание, байт операнда по шине данных передается в микропроцессор и загружается в один из регистров для временного хранения. Теперь микропроцессор готов к собственно выполнению операции. Устройство управления подключает на входы АЛУ регистр с операндом и аккумулятор и коммутирует схему АЛУ на выполнение операции, определяемой кодом операции, хранящимся в регистре команд. Арифметическо-логическое устройство выполняет операцию, и формируемый на его выходах результат загружается в аккумулятор. (Трехбайтные команды в микропроцессоре К580 связаны только с передачами слов, поэтому третий этап описан здесь для некоторой гипотетической команды).

На этом выполнение команды завершается, и микропроцессор готов к выполнению следующей команды, адрес которой уже сформирован в программном счетчике.

Временной интервал выполнения одной команды называется циклом команды. Характерной особенностью микропроцессоров является независимость циклов команд от значений операндов. Поэтому циклы команд можно измерять числом периодов сигналов синхронизации (тактов). Зная эти значения и частоту генератора синхронизации, можно точно определить время выполнения любого сегмента программы.

Рассмотренный пример выполнения 3-байтной команды показывает, что собственно ее выполнение занимает небольшую долю цикла команды, а значительная часть его приходится на подготовительные действия — выборку команды и считывание операнда. Для сокращения длины программы и увеличения производительности микропроцессора в его состав необходимо ввести дополнительные внутренние регистры.

Одну из групп образуют регистры адреса, рассчитанные на хранение 16-битных адресов и называемые указателями памяти. В микропроцессоре К580 таким особым указателем памяти является указатель стека SP, используемый при организации вложенных подпрограмм и обработке многоуровневых прерываний. Кроме того, в качестве указателей памяти используются регистровые пары В-(В, С), D-(D, E), Н-(Н, L). Наличие указателей памяти позволяет с помощью косвенной адресации обращаться к памяти 1-байтными командами. Важно подчеркнуть, что все указатели памяти являются программно доступными, т. е. их содержимое можно модифицировать с помощью специальных команд.

Вторую группу образуют регистры общего назначения (РОН), разрядность которых равна длине слова микропроцессора и которые могут хранить любые данные. (Синонимы: сверхоперативная, локальная, внутренняя или «блокнотная» память микропроцессора, общие регистры, универсальные регистры). Специальными командами можно загрузить в любой РОН данные из памяти, передать данные из одного РОН в другой и запомнить содержимое любого РОН в памяти. Гораздо важнее то, что содержимое любого РОН может быть операндом в разнообразных операциях. Команды, оперирующие содержимым РОН, оказываются короткими и выполняются за минимальное время, так как этап считывания операнда из памяти в них отсутствует. В микропроцессоре К580 есть шесть РОН: В, С, D, E, H, L с 3-битными внутренними адресами от 000 до 101. Аккумулятор А можно использовать как РОН с адресом 111. При составлении прикладных программ приходится избирать то или иное направление их выполнения в зависимости от особенностей (признаков) текущих результатов, т. е. принимать решения в соответствии со складывающейся ситуацией. Для этого при выполнении многих команд микропроцессор формирует двоичные признаки (флажки), отражающие особенности результата выполненной команды. Значение каждого признака фиксируется в специальном триггере. Если какая-либо особенность имеет место, то в соответствующем триггере записывается 1 (флажок установлен); в противном случае триггер фиксирует 0 (флажок сброшен). Совокупность триггеров флажков образует регистр флажков, или F-регистр, называемый также регистром кода условия. Содержимое аккумулятора и F-регистра будем называть в дальнейшем словом состояния программы. Для его обозначения будем использовать аббревиатуру PSW (processor status word). Входы F-регистра через комбинационную схему связаны с выходом АЛУ, и вместе с формированием результата операции производится установка или сброс флажков.

В микропроцессоре К580 имеются следующие флажки:

С — флажок переноса. Устанавливается при наличии переноса из старшего бита результата (в операциях вычитания флажок С становится флажком заема);

S — флажок знака. Совпадает со значением старшего бита результата;

Z — флажок нуля. Устанавливается при нулевом результате;

Р — флажок паритета. Устанавливается при наличии в результате четного числа единиц. Используется термин «паритет» вместо обычного термина, «четность», так как иногда приходится подчеркивать четный паритет (even parity) и нечетный паритет (odd parity).

AC — флажок вспомогательного переноса (полупереноса). Устанавливается при возникновении переноса из третьего бита в четвертый, т. е. из младшей тетрады в старшую.

В F-регистре флажки распределены следующим образом: бит 7 — флажок S, бит 6 — флажок Z, бит 4 — флажок АС, бит 2 — флажок Р, бит 0 — флажок С. Биты 5 и 4 содержат нули, а бит 1 — единицу. Важнейшим из флажков является флажок С, называемый иногда битом связи. Наличие его позволяет организовать на малоразрядном микропроцессоре обработку данных любой длины путем последовательной обработки байтов oпeрандов.

В микропроцессоре предусмотрен обширный набор команд условной передачи управления (разветвлений), осуществляющих выбор одного из двух направлений в зависимости от значений проверяемого флажка. Выполнение команд разветвлений часто называют принятием решений, поскольку именно эти команды придают МП системе черты «интеллекта», адаптации к складывающейся ситуации.

В точном соответствии со смыслом выполняемой команды в микропроцессоре должны производиться передачи слов между многочисленными внутренними регистрами. Оказалось удобным организовать их по внутренней двунаправленной шине данных, состоящей из восьми линий. Естественно, передачи по шине приводят к тому, что в любой момент времени на нее можно выдать содержимое только одного регистра-источника. Обычно и принимает данные с шины только один регистр-получатель. Выходные схемы регистра-источника и входные схемы регистра-получателя коммутируются управляющими сигналами.

Обмен 8-битными словами между внутренней шиной данных и блоком регистров производится через мультиплексор выбора регистра. Имеются также линии передачи 16-битных слов между блоком регистров и схемой инкремента/декремента (инкрементор/декрементор). Эта схема представляет собой быстродействующую комбинационную схему, выходное слово которой в зависимости управляющих сигналов представляет собой увеличенное или уменьшенное на 1 значение входного слова, Шестнадцатибитные слова из любой пары регистров можно загрузить в регистр-защелку адреса, который управляет буферами шины адреса и схемой инкремента/декремента. Последняя преобразует слова в соответствии с заданной операцией и возвращает их в блок регистров. Введение схемы инкремента/декремента обеспечивает совмещение инкремента программного счетчика с другими действиями микропроцессора. В состав узла АЛУ входят аккумулятор, регистр-защелка аккумулятора, регистр временного хранения данных, регистр флажков и параллельное 8-битное АЛУ. Предусмотрена также схема десятичной коррекции, которая позволяет обрабатывать двоично-кодированные десятичные числа (ДКД-числа, или BCD-числа). Результат операции с выхода АЛУ можно передать на внутреннюю шину или загрузить в аккумулятор. Регистр временного хранения принимает информацию с внутренней шины и может выдавать ее в АЛУ, регистр флажков или на внутреннюю шину.

Чтобы изолировать внутреннюю шину данных от внешней, введены тристабильные буферные элементы с регистрами-защелками. В режиме записи (вывода) код с внутренней шины данных загружается в регистр-защелку, триггеры которого управляют выходными буферами внешней шины данных. Выходные буферы отключаются при считывании (вводе) или при выполнении операций, не связанных с обменом данными. В режиме считывания информация с внешней шины данных передается на внутреннюю шину данных.

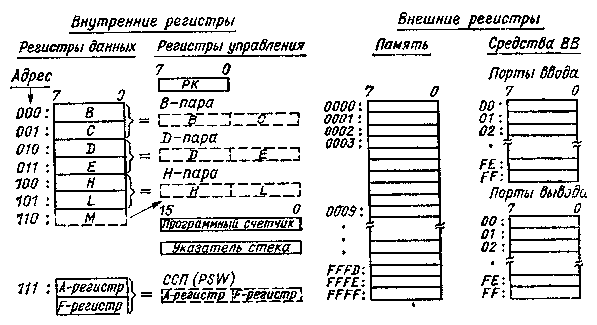

В технической документации обычно приводятся более подробные структурные схемы микропроцессоров. Однако для подавляющего большинства пользователей анализировать внутреннее устройство (микроархитектуру) микропроцессора совсем не обязательно, тем более что по мере роста степени интеграции оно неизбежно будет становиться все более сложным. Достаточную для практического использования микропроцессоров информацию дает программная (регистровая) модель МП системы. В нее включается только те регистры, к которым можно обращаться программно. Знания программной модели вместе со знанием системы команд (они образуют макроархитектуру системы) вполне достаточно для составления прикладных программ. Проектирование аппаратных средств МП систем облегчается при наличии типовых конфигураций, построенных из микросхем, входящих в микропроцессорное семейство.

Рисунок l.6 - Программная модель МП системы

На рисунке 1.6 показана программная модель МП системы на базе микропроцессора К580. Особенностью микропроцессора является возможность программного объединения (конкатенации) 8-битных РОН в 16-битные регистровые пары. Пары могут хранить 16-битные операнды или выступать в качестве указателей памяти. Основным указателем памяти служит Н-пара, которая адресуется в командах как РОН с адресом 110. Ячейка памяти, адрес которой определяется содержимым Н-пары, обозначается М (memory — память). Микропроцессор может адресовать до 256 портов ввода, до 256 портов вывода, а также 64 К ячеек памяти.

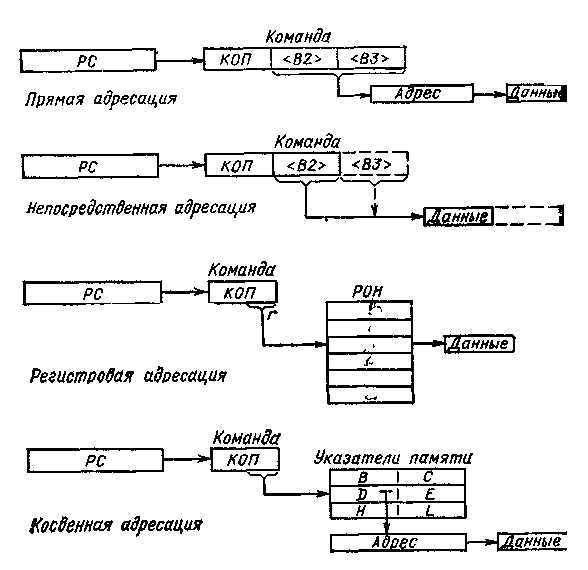

1.3 РЕЖИМЫ АДРЕСАЦИИ И СИСТЕМА КОМАНД

В поле операнда всех команд каким-либо образом определяются данные, участвующие в операции, или операнды. Способ определения операнда называется режимом адресации. Для микропроцессоров разработано около двух десятков режимов адресации, направленных на сокращение длины программ и времени их выполнения. Особенность большинства МП систем заключается в своеобразной организации памяти: фиксированная программа хранится в ПЗУ, а изменяющиеся данные— в ОЗУ. Другими словами, программа и данные хранятся в различных областях памяти. Это ограничивает передачи команд и данных в пространстве памяти, так как модифицировать содержимое программного ПЗУ при выполнении программы невозможно. Кроме того, небольшая длина слова микропроцессора затрудняет манипуляции адресами, поэтому режимы адресации МП систем, аналогичные по названию режимам адресации больших и средних вычислительных машин, могут существенно различаться. Режимы адресации микропроцессора K580 показаны на рисунке 1.7.

Наиболее простой, но и наиболее неэкономичной, является прямая адресация (полная адресация, расширенная адресация, абсолютная адресация): в поле операнда содержится полный 16-битный адрес памяти. С помощью прямой адресации можно обращаться к любой ячейке адресного пространства.

Рисунок 1.7 - Режимы адресации

При необходимости включения в программу фиксрованных значений (кодов символов, слов-масок и др.) применяется непосредственная адресация, в которой операндом является второй байт <В2> самой команды. В микропроцессоре К580 допускается непосредственно адресовать 16-битные слова (<В2> — младший байт, <ВЗ> — старший байт), используемые для инициализации указателей памяти.

При использовании регистровой адресации операндом является содержимое РОН, адресуемого в команде. Команды с таким режимом адресации оказываются короткими (1-байтными) и выполняются достаточно быстро. В 1-байтных командах передач MOV r1, r2 адресуются два РОН, так как их адреса имеют всего по 3 бита.

При выполнении 1-байтных команд с неявной (неотъемлемой) адресацией подразумевается, что операнд находится в определенном внутреннем регистре микропроцессора и его специально адресовать не нужно. Например, все команды сдвига микропроцессора К580 оперируют содержимым аккумулятора. Во всех бинарных операциях преобразования данных подразумевается, что одним из операндов является содержимое аккумулятора и что результат операции загружается в аккумулятор. Неявная адресация применяется также в унарных операциях типа инвертирования аккумулятора.

Удобным средством, позволяющим компактно адресвать все пространство памяти, является косвенная адресация. В этом режиме поле операнда определяет не регистр с данными, а указатель памяти, содержащий адрес операнда. Для быстрого выполнения команд с косвенной адресацией в качестве указателя памяти должен выступать один из внутренних 16-битных регистров микропроцессора. В микропроцессоре К580 основным указателем памяти служит Н-пара, т.е. регистры (Н, L), адресуемая как РОН с адресом 110. В командах загрузки и запоминания аккумулятора в качестве указателей памяти могут выступать В- и D-пары. В 1-байтных командах загрузки в стек и извлечения из стека также применяется косвенная адресация: в них память адресуется указателем стека. Косвенная адресация широко применяется при обработке регулярных структур данных типа массивов. В указатель памяти сначала загружается базовый (начальный) адрес массива, а переход к последовательным элементам массива осуществляется с помощью инкремента указателя памяти.

Одним из недостатков микропроцессора К580 считается отсутствие индексной адресации. В данном режиме исполнительный адрес образуется путем сложения второго байта <В2> команды, рассматриваемого как целое без знака и называемого смещением, и содержимого внутреннего 16-битного индексного регистра. Индексную адресацию, как и косвенную, удобно применять в циклических программах. Заметим, что при необходимости индексную адресацию в микропроцессоре К580 можно реализовать программно, разумеется, за счет непроизводительных потерь времени и увеличения длины программы.

Базовая система команд микропроцессора К580 включает 78 простых команд. Однако многие базовые команды порождают несколько различных кодов операций, поэтому общее их число составляет 244. Команды принято классифицировать на несколько групп, объединяя команды с аналогичным функциональным назначением. Некоторые команды могут быть отнесены более чем к одной группе, и на них следует обратить особое внимание, так как они часто удобны при программировании. Далее при рассмотрении команд применяются их мнемонические обозначения на языке ассемблера.

а) Команды межрегистровых передач

В любой прикладной программе возникает необходимость передать содержимое регистра-источника (S-peгистра) в регистр-получатель (D-регистр). Эту функцию выполняют многочисленные команды межрегистровых передач (пересылок) D← (S). Здесь и далее запись в круглых скобках (X) обозначает содержимое регистра, например, Х.

Содержимое S-регистра и состояние флажков не изменяются, поэтому иногда команды данной группы называются командами копирования содержимого S-регистра в D-регистр.

Однобайтные команды передачи имеют вид MOV D, S. В качестве D и S можно указывать любой РОН и аккумулятор. Например, команда MOV В, А с кодом 01 000 111 передает содержимое аккумулятора в регистр В. Следует обратить внимание на структуру кода операции команды MOV В, А (111 – внутренний адрес регистра А, 000 - внутренний адрес регистра В).

С помощью косвенной адресации команда MOV может обращаться к памяти, используя в качестве указателя памяти регистры (Н, L). Например, команда MOV M, С с кодом 01 110 001 передает содержимое регистра С в ячейку памяти, адресуемую Н-парой: [Н, L]← (C). Запись в квадратных скобках [ADDR] обозначает элемент памяти – источник, содержащий информацию об адресе. Заметим, что команды передачи содержимого внутреннего регистра микропроцессора в память часто называют командами запоминания.

Команда MOV L, M имеет следующий смысл: L←([Н, L]). Содержимое ячейки ОЗУ, адрес которой находится в регистровой паре H,L, загружается в регистр L. Команды передачи содержимого ячейки памяти во внутренний регистр обычно называются командами загрузки.

Однобайтные команды LDAX В и LDAX D загружают в аккумулятор содержимое ячейки памяти, адресуемой соответственно парами регистров (В, С) и (D, E). Команды запоминания STAX В и STAX D осуществляют передачу содержимого аккумулятора в память.

Особенностью микропроцессора К580 являются I-байтные команды передач 16-битных операндов. Команды SPHL и PCHL передают содержимое регистров (Н,L) в указатель стека SP и программный счетчик PC соответственно. Интересна команда обмена XCHG, производящая обмен содержимого регистров (D, E) и (Н, L): (D,E)↔(Н, L).

В 2-байтных командах передач MVI r,<В2> применяется непосредственная адресация: второй байт команды <В2> передается в адресуемый регистр: r ← <В2>. В качестве r можно указывать любой РОН, аккумулятор или ячейку памяти М, адресуемую регистрами (Н, L).

В 3-байтных командах передач используются прямая и непосредственная адресации. Команда LDA загружает в аккумулятор содержимое ячейки памяти, адресуемой вторым и третьим байтами команды: А ← ([<ВЗ>,<В2>]), а команда запоминания STA производит противоположную передачу: [<ВЗ>, <В2>] ← (А). Команда LHLD применяется для загрузки основного указателя памяти — регистров (Н, L) из двух смежных ячеек памяти L←([

Трехбайтные команды LXI rp, где rp означает регистровые пары В, D, H и указатель стека SP, применяются для загрузки начальных значений (инициализации) внутренних указателей памяти. Например, команда LXI В имеет следующее содержание: С← <В2>, В←<ВЗ>.

В группу команд межрегистровых передач включаютcя 2-байтные команды ввода IN и вывода OUT. Второй байт <В2> этих команд представляет собой 8-битный адрес порта ввода или вывода (ВВ), а получателем (источником) может быть только аккумулятор. Таким образом, микропроцессор позволяет адресовать до 256 портов вводa и до 256 портов вывода. Конечно, это не означает, что в МП системе можно подключать по 256 устройств ввода и вывода, так как для каждого устройства кроме информационных портов необходимы каналы обмена управляющей информацией.

Реализация ВВ с помощью специальных команд называется аккумуляторным (изолированным) ВВ. Здесь адресное пространство портов ВВ отделено от адресного пространства памяти. При организации в МП системе ВВ, отображенного на память, порты ВВ считываются ячейками памяти с определенными адресами. Следовательно, все команды с обращением к памяти, адресующие порты ВВ, становятся командами ВВ и специальные команды не нужны.

Целесообразно обратить особое внимание па команды передач между внутренними регистрами микропроцессора, так как они наиболее часто встречаются в программах. Пусть, например, возникла необходимость передать содержимое регистров (D, Е) в указатель стека SP. Специальная команда такой передачи в системе команд отсутствует. Однако нетрудно установить, что передачу SP ← (D, E) осуществляет последовательность из трех однобайтных команд: XCHG, SPHL, XCHG.

Удобным средством представления команд данной группы являются матрицы источников-получателей. Каждая строка матрицы соответствует некоторому S-регистру, а каждый столбец — некоторому D-регистру МП системы. Элементами матрицы служат команды, осуществляющие передачи D ←(S). Рекомендуется самостоятельно построить матрицы источников-получателей для 8- и 16-битных операндов.

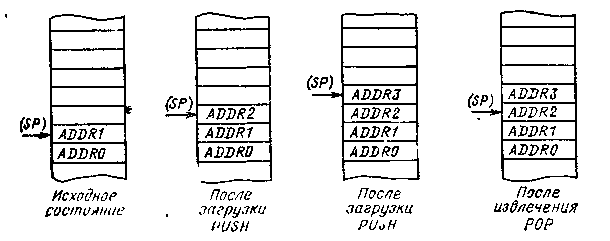

В группу команд межрегистровых передач следует отнести команды PUSH загрузки в стек и команды POP извлечения из стека, которые рассмотрены далее.

б) Команды арифметических операций

Вычислительные возможности микропроцессора К580 ограничены простыми командами сложения и вычитания 8-битных операндов. Операции умножения и деления, а также операции с другими форматами данных реализуются с помощью подпрограмм, что приводит к значительному уменьшению производительности МП системы.

Операнды представляются в формате целого со знаком в дополнительном коде с диапазоном изменений от —128 до +127. Напомним, что старший бит представляет собой знак S и сумма дополнительных кодов операндов равна дополнительному коду суммы, если переполнение исключено, а возникающий перенос из знакового бита игнорируется. В арифметических операциях одним из неадресуемых операндов является содержимое аккумулятора, результат загружается в аккумулятор и в соответствии с полученным результатом производится модификация всех флажков.

Сложение и вычитание осуществляются однобайтными командами ADD r: А ← (А) + (г) и SUB г : А ←(А) — (г). Флажок С в операции вычитания устанавливается, если уменьшаемое меньше вычитаемого, т. е. он превращается во флажок заема.

Во многих применениях базовой длины слова микропроцессора недостаточно и приходится вводить многобайтные числа с последовательной обработкой отдельных байтов. В памяти такие числа хранятся в смежных ячейках и адресуются по младшему байту. При обработке многобайтных чисел очень удобны команды сложения с переносом ADC r: A ←(A) + (r)+C и вычитания с заемом SBB r: А ← (А) — (г)—С.

В системе команд имеются 2-битные команды сложения и вычитания с непосредственной адресацией: адресуемым операндом служит второй байт <В2> команды. Это команды ADI: А ←(А)+<В2>, SUI: A ←(А) — <В2>, АСI: (А) ←(А)+<В2>+С, SBI: А ←(А) — <В2> —С.

Команды арифметического сравнения СМР r: (А) – (r) и CPI: (А)—<В2> производят вычитание из содержимого аккумулятора значения адресуемого операнда, модифицируют по результату все флажки, но не изменяют содержимое аккумулятора. Наличие команд такого неразрушающего сравнения упрощает, например, поиск в массиве заданного слова-эталона. Значение отыскиваемого слова загружается в аккумулятор, базовый адрес массива загружается в регистры (Н, L), а затем с помощью команды СМР М элементы массива сравниваются со словом-эталоном. Факт равенства фиксируется по флажку Z=l.

Для несложной обработки больших массивов числовых данных удобно ввести формат двоично-кодированных десятичных чисел, или BCD-чисел. В этом формате байт содержит две десятичные цифры (тетрады) в коде 8421. Сложение BCD-чисел выполняется в два этапа:

операнды складываются как двоичные числа;

производится коррекция в общем случае неправильного промежуточного результата.

Однобайтная команда десятичной коррекции аккумулятора DAA в два приема корректирует 8-битное значение в аккумуляторе на две BCD-цифры с правильной установкой флажка С:

1. Если младшая тетрада содержит число, большее 9, или если установлен флажок межтетрадного переноса АС = 1, то содержимое аккумулятора увеличивается на 6.

2. Если после этого старшая тетрада аккумулятора содержит число, большее 9, или если установлен флажок С, то в старшую тетраду прибавляется 6.

Например, промежуточный результат двоичного сложения BCD-чисел 79 и 39 имеет вид 1011 0010 (С = 0, АС=1), а после выполнения команды DAA получаем 0001 1000 (С = 1), т.е. правильный результат 118.

Следует специально подчеркнуть, что команда DAA не корректирует результат двоичного вычитания.

При программировании часто возникает необходимость увеличения (инкремента) или уменьшения (декремента) значения операнда на единицу. Эти действия легко осуществляются командами ADI и SUI, второй байт <В2> который равен единице. Для сокращения длин программ и времени их выполнения в системе команд предусмотрены 1-байтные команды инкремента INR r: r ←(r) + l и декремента DCR г: г ←(г)—1. Эти команды не изменяют значения флажка С.

Особенностью микропроцессора К580 являются арифметические операции с 16-битными операндами. В них операнды считаются целыми без знака, и значения всех флажков не изменяются. Команды инкремента INX rp и декремента DCX rp позволяют увеличить или уменьшить содержимое регистров (В, С), (D, E), (H, L) и указателя стека SP на единицу. Команда двойного сложения DAD rp: H, L ←(H, L) + (rp) суммирует содержимое регистра (H, L) и адресуемого 16-битного регистра rp. При выполнении команд DAD rp модифицируется флажок переноса С. Заметим, что команда DAD H эквивалентна удвоению содержимого регистров (H, L), т, е. сдвигу на один разряд влево.

в) Команды логических операций и сдвигов

Логические операции являются поразрядными, т. е. выполняются независимо для всех 8 бит операндов. Неадресуемый операнд находится в аккумуляторе, туда загружается результат операции. По результату операции модифицируются состояния всех флажков, кроме флажка переноса С, который никогда не может быть установлен в единицу н поэтому принудительно сбрасывается.

При выполнении команды ANA r: А ←(А)(г) производится поразрядная конъюнкция операндов. Данная команда применяется для проверки значения определенного бита слова в аккумуляторе с помощью другого слова-маски. Если, например, необходимо проверить состояние второго бита D2 некоторого двоичного числа, то маска должна иметь вид 0000 0100. После выполнения команды ANA по флажку Z можно судить о состоянии бита D2: Z=

. Кроме того, с помощью команды ANA, используя слово-маску, можно сбрасывать определенные биты слова в аккумуляторе.

. Кроме того, с помощью команды ANA, используя слово-маску, можно сбрасывать определенные биты слова в аккумуляторе.Команда ORA r: А ←(А) \/ (г) осуществляет поразрядную дизъюнкцию операндов. Эта команда применяется для установки определенных битов слова в аккумуляторе с помощью слова-маски, а также упаковки слова из полей других слов. Например, результатом операции ORA с операндами 0000X3X2X1X0 и Y7Y6Y5Y40000 будет упакованное слово Y7Y6Y5Y4X3X2X1X0.

Команда ИСКЛЮЧАЮЩЕГО ИЛИ XRA r: А ←(А)

(г) производит поразрядное сложение операндов по mod 2. Команда XRA применяется для инвертирования определенных битов слова с помощью слова-маски на основе тождества 1

(г) производит поразрядное сложение операндов по mod 2. Команда XRA применяется для инвертирования определенных битов слова с помощью слова-маски на основе тождества 1 Х =

Х = . Например, для инвертирования седьмого и первого битов некоторого двоичного числа маска имеет вид 10000010. Другое применение команды XRA связано со сравнением слов на абсолютное равенство. В единственном случае, когда операнды поразрядно совпадают, результат операции содержит нули во всех разрядах (соответственно тождеству Х

. Например, для инвертирования седьмого и первого битов некоторого двоичного числа маска имеет вид 10000010. Другое применение команды XRA связано со сравнением слов на абсолютное равенство. В единственном случае, когда операнды поразрядно совпадают, результат операции содержит нули во всех разрядах (соответственно тождеству Х Х = 0), о чем сигнализирует флажок Z=1.

Х = 0), о чем сигнализирует флажок Z=1.Двухбайтные команды с непосредственной адресацией соответствующих логических операций имеют мнемонические обозначения ANI, ORI, XRI. Операндами этих команд являются содержимое аккумулятора и второй байт <В2> команды, а результат загружается в аккумулятор.

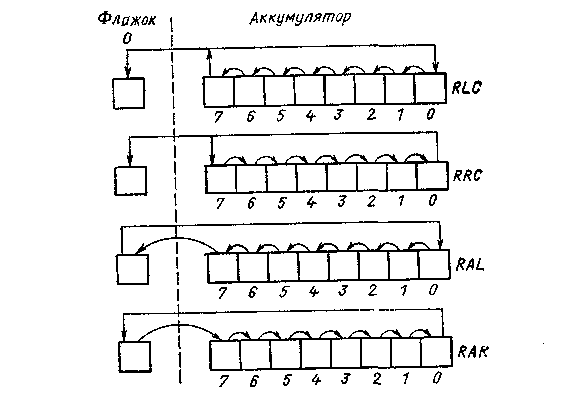

Операндом унарных 1-байтных команд сдвига является содержимое аккумулятора, в котором формируется результат. Сдвиги выполняются влево и вправо только на один разряд. В зависимости от того, что помещается в освобождающийся при сдвиге бит и как используются выдвигающийся (спадающий) бит и флажок переноса, вводится несколько команд сдвигов. Пояснение четырех команд сдвига микропроцессора К580 приведено на рисунке 1.8.

Рисунок 1.8 - Команды сдвига

В командах циклического сдвига (ротациях) влево RLC и вправо RRC выдвигающийся бит помещается в освобождающийся и, кроме того, фиксируется во флажке переноса С. В командах сдвига через перенос влево RAL и вправо RAR выдвигающийся бит помещается во флажок переноса С, а текущее значение флажка С передается в освобождающийся бит.

К логическим операциям можно отнести 1-байтные команды инвертирования аккумулятора СМА: А ←(

); установки флажка переноса STC: С ←1 и инвертирования флажка переноса CMC: С ←(

); установки флажка переноса STC: С ←1 и инвертирования флажка переноса CMC: С ←( ).

).г) Команды передачи управления

К окончанию текущей команды, а точнее — после выборки команды из памяти в программном счетчике PC сформирован адрес следующей по порядку команды. При естественном порядке выполнения команд, соответствующем простейшим линейным программам, производятся выборка и исполнение этой следующей команды, формируется адрес следующей команды и т. д. Однако линейные прикладные программы на практике не встречаются. В разветвляющихся и циклических программах и при использовании подпрограмм приходится выполнять не следующую по порядку команду, а команду, находящуюся в другой ячейке программной памяти. Для этого достаточно загрузить в PC адрес новой ячейки, называемый адресом перехода. Такая процедура называется передачей управления, а специальные команды, которыми она реализуется, называются командами передачи управления, или командами управления программой. В системе команд микропроцессора К580 предусмотрен обширный набор команд передачи управления.

Команда безусловной передачи управления без возврата JMP, называемая также безусловным переходом или просто переходом, состоит из байта кода операции и двух байтов полного 16-битного адреса перехода. При ее исполнении адрес перехода загружается в PC, а текущее содержимое PC теряется: РС ←<ВЗ>,<В2>. Данная команда, соответствующая оператору GOTO, позволяет передать управление любой ячейке адресного пространства. Современная методика создания структурированных программ рекомендует использовать минимум команд JMP.

Трехбайтные команды условной передачи управления без возврата, называемые также условными переходами или разветвлениями (и даже развилками!), осуществляют передачу управления только при удовлетворении некоторого условия, заданного в коде операции. Если условие не удовлетворяется, то передачи управления не происходит, а выполняется следующая по порядку команда, т. е. в этой ситуации команда разветвления эквивалентна холостой команде.

Проверяемым условием является текущее значение одного из флажков, указываемых в коде операции. Для удобства программирования предусмотрены команды разветвлений, осуществляющие передачу управления по единичному и нулевому значению каждого из флажков, кроме флажка АС. Например, команда JZ передает управление, т. е. осуществляет загрузку РС ←<ВЗ> ,<В2>, если флажок Z=l, а команда JNZ — если флажок Z = 0. Аналогичные парные команды имеются для флажков C(JC, JNC), S(JM, JP) и P(JPE, JPO). Всего, таким образом, получается восемь команд разветвлений.

Трехбайтные команды безусловной передачи управления с возвратом, называемые также вызовами CALL, состоят из байта кода операции и адреса перехода, представляющего собой начальный адрес подпрограммы. При выполнении вызова необходимо временно запомнить текущее содержимое программного счетчика (т. е. адрес команды, следующей за командой CALL, и называемый адресом возврата), загрузить адрес перехода команды CALL в PC, а после выполнения подпрограммы передать адрес возврата в PC. Последняя функция реализуемая специальной 1-байтной командой возврата RETURN. Таким образом, вызов одной подпрограммы и возврат из нее осуществляется сравнительно простыми средствами — необходим 16-битный регистр для временного запоминания адреса возврата.

Ситуация несколько усложняется, если вызванная подпрограмма вызывает еще одну, а эта вторая — третью и т. д. (организуются вложенные подпрограммы). Фактически проблема вложения сводится к запоминанию адресов возврата в порядке вызовов подпрограмм и к возврату их в PC по мере выполнения подпрограмм. Для этого необходимо блок регистров, работающий таким образом, что последний включенный в него адрес возврата извлекается первым. Такой блок регистров называется стеком, магазином или буфером LIFO. Максимальное число запоминаемых в стеке слов называется его глубиной.

В МП системах на базе микропроцессора К580 для стека выделяется специальная область ОЗУ, и его глубина считается неограниченной. Для идентификации последней занятой ячейки стека, называемой его верхушкой, в микропроцессоре имеется внутренний 16-битный регистр — указатель стека SP.

Рисунок 1.9 - Операции стека с подвижной верхушкой

При выполнении команды PUSH rp в ячейку памяти с адресом (SP)-1 записывается содержимое восьми старших разрядов регистровой пары rp, а в ячейку с адресом (SP)-2 содержимое восьми младших разрядов этой регистровой пары. Содержимое регистра SP уменьшается на 2 (стек «растет вверх», в область меньших адресов). Когда выполняется команда POP rp извлечения данных из стека, содержимое верхушки стека передается в младшие 8 бит регистровой пары rp, а содержимое ячейки стека, адрес которой на единицу больше адреса верхушки (записанного в регистре SP), передается в старшие 8 бит регистровой пары rp. После этого содержимое регистра SP увеличивается на 2. Для правильной работы стека команды PUSH и POP обязательно должны быть парными. Иллюстрация работы стека с подвижной верхушкой показана на рис. 1.9.

Таким образом, команда CALL фактически является командой PUSH PC с последующей загрузкой в PC второго и третьего байтов команды CALL. Выполнение ее несколько усложняется тем обстоятельством, что для запоминания в стеке 16-битного адреса возврата приходится использовать две 8-битные ячейки. Поэтому команда CALL производит следующие действия: [(SP)-1] ←(PCH); [(SP)-2] ←(РСL,); РC ←<ВЗ>,<В2>; SP ←(SP)-2; где (SP) —содержимое указателя стека до выполнения команды CALL, а РСH и РСL соответственно старшие и младшие 8 бит программного счетчика. Однобайтная команда возврата RETURN эквивалентна команде POP PC: PCL ←([SP]); РСH ←([SP+l]); SP ←(SP)+2.

В командах условных вызовов и возвратов проверяется состояние указанного в коде операции флажка и, если оно удовлетворяет условию, осуществляются вызов и возврат, а если не удовлетворяет — выполняется следующая по порядку команда. Имеются команды, проверяющие единичное и нулевое значения каждого из четырех флажков:

- флажок Z: вызовы CZ, CNZ; возвраты RZ, RNZ;

- флажок С: вызовы СС, CNC; возвраты RC, RNC;

- флажок S: вызовы СМ, СР; возвраты RM, RP;

- флажок Р: вызовы СРЕ, СРО; возвраты RPE, RPO.

В системе команд микропроцессора имеется особая 1-байтная команда вызова, предназначенная для обработки прерываний и введения контрольных точек (разрывов) при отладке программ. Она называется рестартом (повторным запуском) и имеет мнемоническое обозначение RST. В коде операции рестарта 11ААА111 три бита ААА формируются подсистемой прерываний или указываются программистом. Выполнение команды рестарта сводится к двум действиям:

текущее содержимое PC загружается в стек;

в PC передается код 00000000 ООАААООО.

Следовательно, в зависимости от значений ААА микропроцессор переходит к одной из восьми ячеек, находящихся в первых адресах памяти: 0000, 0008, 0010,..., ...,0038.

Особенной командой безусловной передачи управления без возврата оказывается PCHL: PC ←(H,L), в результате выполнения которой микропроцессор продолжает программу с адреса, загруженного в программный счетчик из регистров (H,L).

Внешний стек, служащий для временного хранения адресов возврата в командах вызовов, удобно использовать для запоминания содержимого внутренних регистров. Необходимость такого запоминания возникает в следующих ситуациях.

Ограниченного числа внутренних РОН при программировании часто «не хватает» для размещения промежуточных результатов, которые потребуются в программе несколько позже. Для освобождения внутренних регистров содержимое их загружается в стек, а по мере необходимости извлекается из стека.

В мультипрограммной среде и при обработке прерываний микропроцессор должен прерывать выполнение текущей программы и переключаться на выполнение другой программы (так называемое контекстное переключение). Разумеется, при таком переключении необходимо сохранять состояние программы, т. е. содержимое всех внутренних регистров или, по крайней мере, тех из них, которые будут использоваться в новой программе, с последующим восстановлением состояния прерванной программы. Как минимум, при контекстном переключении следует временно запоминать слово состояния процессора PSW — содержимое аккумулятора и регистра флажков.

В системе команд микропроцессора имеется команда PUSH PSW загрузки в стек PSW, а также соответствующая команда POP PSW извлечения PSW из стека и загрузки его в регистр флажков и аккумулятор. Выполнение этих команд сопровождается автоматической модификацией SP.

В ряде случаев очень удобной оказывается специфическая 1-байтная команда XTHL: (L) ↔([SP]), (H) ↔([SP+1]) обмена содержимого регистров (Н, L) и двух соседних ячеек стека, т. е. последних загруженных в стек данных. Значение SP при выполнении команды XTHL не изменяется.

Фактическая область стека определяется программистом с помощью команды с непосредственными данными LXI SP: SP ←<ВЗ>,<В2>. Следует инициализировать указатель стека до использования в программе команд загрузки данных в стек и извлечения данных из стека и позаботиться о том, чтобы при выполнении программы область стека не использовалась для других целей.

д) Команды управления микропроцессором

Однобайтные команды данной, обычно немногочисленной, группы применяются для задания режима работы микропроцессора.

Команда останова HLT вызывает прекращение выполнения программы и переводит микропроцессор в состояние останова (подробнее см. в следующем параграфе).

Команда разрешения прерываний EI устанавливает внутренний триггер INTE разрешения прерываний в такое состояние (INТЕ = 1), когда микропроцессор реагирует на запросы прерываний, поступающие от периферийных устройств, инициирующих обмен данными.

Команда запрещения (маскирования) прерываний DI устанавливает вышеупомянутый триггер в такое состояние (INTE = 0), когда микропроцессор не воспринимает запросов прерываний от периферийных устройств.

Наконец, своеобразная холостая команда NOP не производит никаких действий, кроме инкремента программного счетчика для перехода к следующей команде. Команда NOP обычно используется в так называемых программных циклах задержки, в которых микропроцессор генерирует сигналы программируемой длительности.

Сделаем заключительное замечание о системе команд. При рассмотрении двоичных кодов операций они представляются неупорядоченными. Однако минимизация устройства управления при проектировании микропроцессора приводит к тому, что коды операций с близким по смыслу содержанием оказываются соседними. Система команд микропроцессора К580 допускает компактное табличное представление, если за основу взять восьмеричные коды операций. Строки таблицы следует отметить цифрами старшей триады (с нулевым старшим битом), а столбцы — цифрами двух младших триад. Рекомендуется самостоятельно построить таблицу восьмеричных кодов операций [10,11].

1.4. ФУНКЦИОНИРОВАНИЕ МИКРОПРОЦЕССОРА

В настоящем разделе кратко рассматриваются действия микропроцессора, которые он производит в ходе выполнения команд программы.

а) Цикл команды

В микропроцессоре К580 каждая команда выполняется в течение одного — пяти машинных циклов Mi, называемых также процессорными циклами. Число машинных циклов команды определяется числом обращений к внешним подсистемам (памяти и средствам ввода-вывода) для обмена информацией между микропроцессором и адресуемым внешним регистром. Исключение составляет команда DAD, выполняемая за три машинных цикла с обращением к памяти только в первом цикле. Первым и обязательным машинным циклом M1 всех команд является выборка кода операции. Машинный цикл состоит из двух фаз. На этапе обязательной фазы, называемой фазой адресации, микропроцессор через шину адреса идентифицирует внешний регистр и обменивается информацией между ним и определенным внутренним регистром по шине данных. Необязательная фаза, называемая фазой выполнения, связана с дешифрированием кода операции и внутренним преобразованием данных.

Машинный цикл состоит из 3—5 машинных тактов Ti, называемых также функциональными состояниями или просто состояниями микропроцессора. Такты определяются как временной интервал между двумя последовательными нарастающими фронтами сигнала синхронизации Ф1, а число их в машинном цикле определяется содержанием выполняемой команды. Циклы команд варьируются от 4 тактов (один машинный цикл) до 18 тактов (пять машинных циклов). При частоте синхронизации, например, 1,25 МГц, циклы команд составляют от 3,2 до 14,4 мкс .

Первые три такта всех машинных циклов унифицированы и образуют фазу адресации. Собственно адресация внешнего регистра-источника или регистра-получателя осуществляется в такте Т1. По нарастающему фронту сигнала Ф2 микропроцессор выдает на шину адреса сигналы адреса (номинальная задержка стабилизации сигналов адреса составляет 200 нс, максимальная 270 нс). Они сохраняются стабильными до нарастающего фронта сигнала Ф2 такта, следующего за тактом Т3 текущего машинного цикла. Источником адреса могут быть следующие внутренние регистры: программный счетчик, указатель стека, одна из регистровых пар В, D или Н, а также содержимое регистра (W, Z) в командах ввода, вывода и передачи управления.

Такт Т2, который всегда следует зa тактом Т1, отведен для проверки необходимости реакции на некоторые управляющие сигналы, влияющие на функционирование микропроцессора. По нарастающему фронту сигнала Ф2 проверяются уровни внешних сигналов готовности READY, запроса ПДП HOLD, а также внутреннего сигнала подтверждения останова HLTA. Кроме того, в такте Т2 последнего машинного цикла каждой команды проверяется уровень внешнего сигнала запроса прерывания INТ. Пока будем считать, что указанные сигналы имеют такие уровни, которые не изменяют нормального течения машинного цикла (READY=1, HOLD = 0, HLTA= О, INT=0).

Помимо проверки значений управляющих сигналов в зависимости от функции текущего машинного цикла в такте Т2 производятся следующие действия:

если текущий машинный цикл связан с обращением к программной памяти, то выполняется инкремент программного счетчика РС=РС+1;

если текущий цикл Mi предназначен для считывания (ввода) данных в микропроцессор, то по нарастающему фронту сигнала Ф2 генерируется сигнал считывания DBIN (номинальная задержка 130 нс, максимальная 200 нс);

если текущий цикл Mi связан с записью (выводом) данных из микропроцессора, то по нарастающему фронту сигнала Ф2 на шине данных формируются сигналы выводимого слова (номинальная задержка 220 нс, максимальная 280 нс).

Такт ТЗ отведен для обмена информацией между внутренним регистром микропроцессора и адресованным в такте Т1 внешним регистром. Когда в текущем Mi осуществляется ввод данных в микропроцессор, то сигналы данных от внешнего регистра, коммутируемые сигналом DBIN, должны стабилизироваться не менее чем за 50 нс до спадающего фронта сигнала Ф1, и оставаться стабильными не менее 130 нс после нарастающего фронта сигнала Ф2 такта ТЗ. Если в текущем Mi микропроцессор выводит данные, то по нарастающему фронту сигнала Ф1 генерируется L-активный сигнал

(номинальная задержка составляет 70 нc, максимальная 120 нc). Сигнал DBIN снимается по нарастающему фронту сигнала Ф2 (с максимальной задержкой 200 нc), а сигнал

(номинальная задержка составляет 70 нc, максимальная 120 нc). Сигнал DBIN снимается по нарастающему фронту сигнала Ф2 (с максимальной задержкой 200 нc), а сигнал  снимается по нарастающему фронту следующего сигнала Ф1 (с максимальной задержкой 120 нc).

снимается по нарастающему фронту следующего сигнала Ф1 (с максимальной задержкой 120 нc).В тактах Т4 и Т5 первого машинного цикла M1 всех команд производится дешифрирование кода операции, необходимые внутренние передачи и преобразования данных. Например, в тактах Т4 и Т5 команд INR (INX) и OCR (DCX) осуществляется инкремент или декремент адресуемого регистра (регистровой пары), в командах разветвлений проверяется указанное в них условие, в такте Т4 команды СМА инвертируется аккумулятор и т. п. Интересно отметить, что в командах сложения (вычитания), сдвигов и логических операций собственно выполнение операции и загрузка результата в аккумулятор производятся в тактах Т1 и Т2 следующей команды. В командах передачи управления адрес перехода вначале фиксируется в регистре (W, Z), а в тактах Т1 и Т2 следующей команды выдается на шину адреса и увеличенный на единицу загружается в программный счетчик. Такое совмещение действий увеличивает производительность микропроцессора.

Рассмотренный принцип формирования машинного цикла дает возможность определить число машинных циклов в каждой команде. Приведем некоторые примеры.

Однобайтные команды MOV r1, r2 (r1, r2 ≠ M) выполняются за один машинный цикл, выборка кода операции (фаза адресации) и передача между внутренними регистрами (фаза выполнения). Однобайтные команды MOV r, М или MOV M, r выполняются за два цикла: выборка кода операции (Ml) и передача между внутренним регистром и ячейкой памяти, адресуемой Н-парой (М2). Двухбайтная команда ORI состоит из трех циклов: выборка кода операции (Ml), считывание второго байта <В2> операнда, выполнение операции. Трехбайтная команда STA выполняется за четыре цикла: три цикла выборки команды и цикл запоминания содержимого аккумулятора в ячейке памяти. Однобайтная (но самая длинная) команда XTHL выполняется за пять циклов: выборка кода операции, два никла передачи содержимого двух верхних ячеек стека в регистры (W, Z) и два цикла передачи в указанные ячейки стека содержимого регистров (Н, L) с последующей передачей содержимого (W, Z) в (H, L).

Число машинных циклов восьми команд условных вызовов (СС, CMC, GZ и т.д.) зависит от значения проверяемого в них условия, т.e. состояния соответствующего триггера флажка. Если проверяемое условие, которое анализируется в тактах Т4 и Т5 машинного цикла Ml, не удовлетворяется, то эти команды выполняются в течение циклов Ml, M2, МЗ выборки 3-байтной команды. Если условие удовлетворяется, то условные вызовы выполняются за пять машинных циклов. В двух дополнительных циклах (М4 и М5) производится загрузка в стек содержимого программного счетчика.

б) Байт состояния

Несколько упрощенно можно считать, что МП система на базе микропроцессора К580 состоит из пяти внешних подсистем: памяти, стека, ввода, вывода и прерывания. Все подсистемы подключаются к шинам адреса и данных параллельно и поэтому адрес внешнего регистра, формируемый в такте Т1, одновременно дешифрируется всеми подсистемами. Однако в любом машинном цикле микропроцессор может обмениваться информацией только с одной подсистемой. Следовательно, адресной информации на шине адреса для однозначной идентификации внешнего регистра недостаточно, и ее необходимо дополнить «старшими битами», адресующими подсистему. Кроме того, для отладки МП системы обычно требуется информация о текущем состоянии микропроцессора. Такую дополнительную информацию содержит байт состояния, который выдается на шину данных в такте Т1 всех машинных циклов по нарастающему фронту сигнала Ф2. Импульсным сигналом, идентифицирующим наличие на шине данных байта состояния, служит выходной Н-активный сигнал синхронизации SYNC, также генерируемый в такте Т1 по нарастающему фронту Ф2. Стабильные уровни сигналов состояния и Н-уровень сигнала SYNC сохраняются до нарастающего фронта Ф2 в такте Т2. Допустимые задержки сигналов состояния (номинальная 220 нс, максимальная 280 нс) и сигнала SYNC (номинальная 130 нс, максимальная 200 нс) выбраны таким образом, чтобы спадающий фронт SYNC приходился на стабильные уровни сигналов состояния. Поэтому сигнал SYNC можно непосредственно использовать для загрузки байта состояния с шины данных во внешний регистр-защелку, где он сохраняется до следующего машинного цикла.

Отдельные биты байта состояния имеют следующее содержание:

D0 (INTA) —подтверждение прерывания. Представляет реакцию микропроцессора на воспринятый им запрос прерывания от периферийного устройства. Формируется только в машинном цикле Ml и используется для ввода в регистр команд микропроцессора команды рестарта RST из подсистемы прерываний, как бы «заменяющей» программную память;

D1 (

) —запись — вывод. Идентифицирует микропроцессор в текущем машинном цикле как получатель информации (

) —запись — вывод. Идентифицирует микропроцессор в текущем машинном цикле как получатель информации ( = 1) или как источник информации (

= 1) или как источник информации ( =0);

=0);D2 (STACK) — стек. Определяет указатель стека в качестве источника адреса (на шине адреса в текущем цикле находится содержимое указателя стека);

D3 (HLTA) — подтверждение останова. Формируется в машинном цикле М2 команды останова HLT и сигнализирует о том, что микропроцессор прекратил выполнение программы;

D4 (OUT) — вывод. Формируется в машинном цикле МЗ команды OUT и идентифицирует выбор подсистемы вывода. На шине адреса находится адрес порта вывода;

D5 (M1)—первый машинный цикл команды. Формируется в цикле Ml всех команд и определяет выборку из программной памяти кода операции;

D6 (INP) —ввод. Формируется в машинном цикле МЗ команды IN и идентифицирует выбор подсистемы ввода. На шине адреса находится адрес порта ввода;

D7 (MEMR) — считывание из памяти. Определяет выполнение в текущем машинном цикле считывания из памяти.

Основное назначение битов состояния — генерирование управляющих сигналов для внешних подсистем. Поэтому определение их диктуется простотой интерфейса, а не однозначной идентификацией машинного цикла. Всего имеется 10 типов машинных циклов, которые приведены в таблице 1.1.

Приведем для всех типов машинных циклов внутренние указатели памяти, содержимое которых находится на шине адреса:

программный счетчик — циклы:

ВЫБОРКА КОДА ОПЕРАЦИИ,

ПРЕРЫВАНИЕ,

ОСТАНОВ,

ПРЕРЫВАНИЕ ПРИ ОСТАНОВ;

регистровые пары ВС, DE, HL — циклы:

СЧИТЫВАНИЕ ИЗ ПАМЯТИ,

ЗАПИСЬ В ПАМЯТЬ;

Указатель стека —циклы:

СЧИТЫВАНИЕ ИЗ СТЕКА,

ЗАПИСЬ В СТЕК;

Регистровая пара W,Z — циклы:

ВВОД,

ВЫВОД.

Отметим, что при выполнении команд IN и OUT 1-байтный адрес порта ввода или вывода, являющийся вторым байтом <В2> команды, в цикле М2 параллельно загружается в регистры W и Z.

Таблица 1.1 - Типы машинных циклов

В цикле МЗ адрес порта выдается одновременно на линии А15 – А8 и А7 – А0. Такой прием используется для выравнивания нагрузки на линии адреса, так как одну часть портов можно подключить к линиям А15 – А8, а другую — к линиям А7 – А0. Зная общее содержание команды, типы машинных циклов и принцип организации машинного цикла, нетрудно построить последовательность типов машинных циклов для любой команды. Приведем некоторые примеры.

Команды MOV r1,r2 (r1,r2 ≠ М) имеют один цикл: «ВЫБОРКА КОДА ОПЕРАЦИИ». Команды MOV M, г выполняются за два цикла: «ВЫБОРКА КОДА ОПЕРАЦИИ» и «ЗАПИСЬ В ПАМЯТЬ». Команда OUT выполняется за три цикла: «ВЫБОРКА КОДА ОПЕРАЦИИ», «СЧИТЫВАНИЕ ИЗ ПАМЯТИ», «ВЫВОД». Команда LDA включает четыре цикла: «ВЫБОРКА КОДА ОПЕРАЦИИ», «СЧИТЫВАНИЕ ИЗ ПАМЯТИ», «СЧИТЫВАНИЕ ИЗ ПАМЯТИ», «СЧИТЫВАНИЕ ИЗ ПАМЯТИ». Команда CALL выполняется за пять циклов: «ВЫБОРКА КОДА ОПЕРАЦИИ», «СЧИТЫВАНИЕ ИЗ ПАМЯТИ», «СЧИТЫВАНИЕ ИЗ ПАМЯТИ», «ЗАПИСЬ В СТЕК», «ЗАПИСЬ В СТЕК».

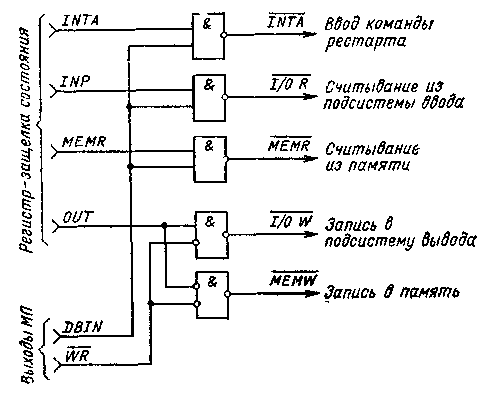

Приведем схему формирования основных управляющих сигналов, которые используются в МП системах на базе микропроцессора К580 (рисунок 1.10). Как видно из рисунка, все приведенные управляющие сигналы являются L-активными. Такое кодирование упрощает интерфейс с внешними подсистемами, которые обычно имеют L-активные входы выбора устройства DS или выбора БИС CS.

Рисунок 1.10 - Схема формирования управляющих сигналов

в) Особые случаи циклов команд

Ранее отмечалось, что в такте Т2 всех машинных циклов микро. процессор проверяет значения входных сигналов готовности READY, запроса прямого доступа к памяти HOLD, а также значение внутреннего сигнала подтверждения останова HLTA. Кроме того, в последнем машинном цикле всех команд проверяется уровень сигнала прерывания INT. Рассмотрим реакции микропроцессора на указанные сигналы несколько подробнее.