Вначале 70-х годов появилась первая большая интегральная микросхема, выполнявшая функции центрального процессора (ЦП) вычислительной машины

| Вид материала | Документы |

- Первая программа для вычислительной машины была написана: Адой Лавлейс, 90.62kb.

- Проектирование работы в организации функции управления организацией, 764.2kb.

- Реферат Интегральная, 452.33kb.

- 1 История развития информатики, 44.2kb.

- Операционная система в наибольшей степени определяет облик всей вычислительной системы, 1557.26kb.

- Определения, 430.8kb.

- Инте Республики Коми 02. 12. 2002г.) (новая редакция) г. Инта 2003г статья, 545.3kb.

- Лавлейс, Ада Авгу́ста А́да Кинг (урождённая Ба́йрон), графиня Ла́влейс, 45.48kb.

- Разработка межкластерного коммутатора для организации многопроцессорного вычислительного, 99.46kb.

- Программа дисциплины гсэ. 01 Методология и история кибернетики, информатики и вычислительной, 194.68kb.

1 2

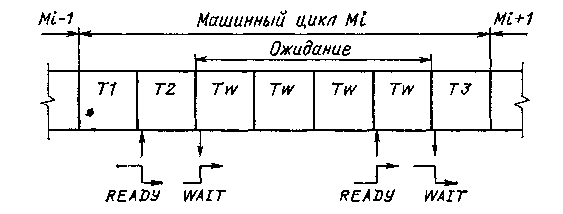

Реакция микропроцессора на сигнал READY. Когда быстродействия внешней подсистемы, например памяти, недостаточно для синхронного обмена данными с микропроцессором, она может приостановить действия микропроцессора установкой L-уровня на линии READY, т. е. «растянуть» машинный цикл на целое число периодов синхронизации. Чтобы микропроцессор отреагировал на L-ypoвень READY в текущем машинном цикле, этот уровень должен стабилизироваться минимум за 180 нc до спадающего фронта сигнала Ф2 и сохраняться стабильным до окончания импульса Ф2. При соблюдении данного условия микропроцессор не переходит к такту Т3 и вводит состояние ожидания Tw (рисунок 1.11). В состояниях на шине адреса сохраняется выданный в такте Т1 адрес внешнего регистра, а также сигнал DBIN, если текущий цикл Mi связан передачей данных в микропроцессор. Для квитирования (подтверждения) перехода в состояние Tw микропроцессор по нарастающему фронту сигнала Ф1 формирует Н-уровень на линии WAIT.

Рисунок 1.11 - Введение состояний ожидания

Продолжительность состояний ожидания определяется действием L-уровня на входе READY. Когда внешняя подсистема готова к обмену данными, она должна установить на линии READY Н-уровень. Чтобы микропроцессор отреагировал на готовность, Н-уровень должен стабилизироваться не менее чем за 180 нс до спадающего фронта Ф2. После этого микропроцессор вводит такт ТЗ и по нарастающему фронту Ф1 снимает сигнал WAIT.

Номинальная задержка начала и окончания сигнала WAIT относительно нарастающего фронта Ф1 составляет 70 нc, а максимальная 120 нc. Разумеется, введение состояний ожидания несколько уменьшает производительность МП системы.

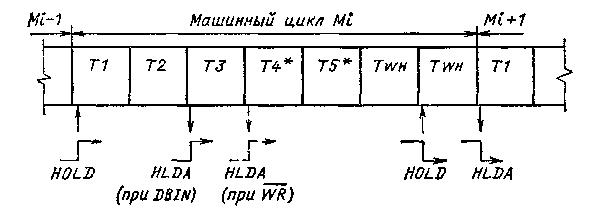

Реакция микропроцессора на сигнал HOLD. Если в МП системе имеются периферийные устройства с высокой скоростью передачи данных, например накопитель на гибком магнитном диске, то обмен между ними организуется в режиме прямого доступа к памяти (ПДП). Когда периферийное устройство (точнее, контроллер ПДП) инициирует запрос ПДП, микропроцессор приостанавливает выполнение программы и переводит внутренние буферы шин адреса и данных в высокоимпедансное состояние. Шинами начинает управлять контролер ПДП, организуя обмен данными между периферийным устройством и памятью МП системы.

Инициирование ПДП осуществляется установкой Н-уровня на входной линии запроса ПДП HOLD. В наиболее простом пакетном режиме Н-уровень HOLD сохраняется до окончания передачи блока данных, но ПДП может осуществляться и для передачи отдельных байтов. Микропроцессор реагирует на Н-уровень HOLD в текущем машинном цикле Mi, если этот уровень стабилизировался минимум за 180 нс до нарастающего фронта Ф2 (рисунок 1.12). Рекомендуется синхронизировать сигнал HOLD с сигналом Ф1.

Рисунок 1.12 - Организация прямого доступа к памяти

Напомним, что микропроцессор в такте Т1 адресовал внешний регистр, но обмен с ним производится только в такте ТЗ. Если разрешить ПДП до такта ТЗ, то в дальнейшем пришлось бы снова адресовать внешний регистр, что усложнило бы устройство управления и временную диаграмму работы микропроцессора. Поэтому микропроцессор обязательно заканчивает обмен с внешним регистром и только после этого вводит состояние ПДП TWH. Заметим, что при такой организации ПДП сигнал READY имеет более высокий приоритет, чем сигнал HOLD. После такта ТЗ текущего машинного цикла Mi могут следовать либо необязательные такты Т4 и Т5, отводимые на внутренние преобразования данных, либо такт Т1 следующего машинного цикла. Микропроцессор формирует Н-уровень квитирующего сигнала HLDA подтверждения запроса ПДП по нарастающему фронту Ф1, (номинальная задержка 70 нc, максимальная 120 нc), а по нарастающему фронту Ф2 с задержкой не более 200 нc переводит буферы шин адреса и данных в высокоимпедансное состояние. Если в текущем цикле Mi производится считывание в микропроцессор (действует сигнал DBIN), то генерирование HLDA и отключение от шин адреса и данных осуществляется в такте ТЗ, а если в текущем цикле Mi производится запись из микропроцессора (действует сигнал

), то аналогичные действия осуществляются в такте, следующем за ТЗ, если, наконец, текущий цикл содержит Т4 и Т5, то они совмещаются с ПДП. После окончания ПДП микропроцессор всегда вводит такт Т1 следующего машинного цикла Mi+1.

), то аналогичные действия осуществляются в такте, следующем за ТЗ, если, наконец, текущий цикл содержит Т4 и Т5, то они совмещаются с ПДП. После окончания ПДП микропроцессор всегда вводит такт Т1 следующего машинного цикла Mi+1.Когда между периферийным устройством и памятью МП системы передан необходимый блок данных, контроллер ПДП устанавливает L-уровень на линии HOLD и микропроцессор выходит из состояния TWH.

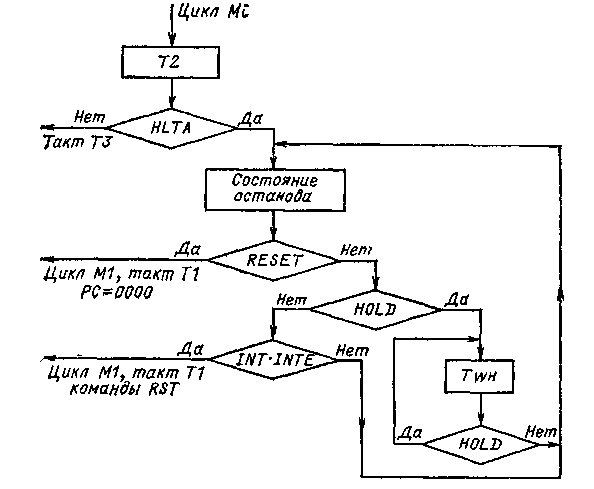

Реакция микропроцессора на команду останова HLT. Однобайтная команда HLT выполняется следующим образом. В машинном цикле Ml, состоящем из четырех тактов Т1 — Т4, производятся выборка и дешифрирование команды, а в цикле М2 осуществляется собственно «выполнение» команды. В такте Т1 цикла М2 микропроцессор выдает на шину адреса содержимое программного счетчика, а на шину данных — байт состояния с установленным битом подтверждения останова HLTA. В такте Т2 по нарастающему фронту сигнала Ф2 с максимальной задержкой 200 нс внутренние буферы шин адреса и данных переводятся в высокоимпедансное состояние, а по нарастающему фронту сигнала Ф1 в следующем такте формируется Н-уровень на линии ожидания WAIT. Выполнение программы прекращается, и в состоянии останова микропроцессор может находиться в течение любого временного интервала.

Из состояния останова микропроцессор выводится следующими способами:

1 путем подачи Н-уровня на вход сброса RESET с продолжительностью не менее трех периодов синхронизации. Когда на линии RESET после этого устанавливается L-уровень, то по нарастающему фронту сигнала Ф1 генерируется внутренний сигнал сброса Он загружает в программный счетчик нули и заставляет устройство уравления сформировать следующий такт как такт Т1 машинного цикла M1 - выборки кода операции. Следовательно, микропроцессор обращается к ячейке 0000, которая обычно является начальным адресом подпрограммы инициализации системы;

2 путем подачи Н-уровня на вход прерывания INT. Микропроцессор реагирует на этот сигнал только в том случае, если установлен внутренний триггер разрешения прерывания (INТЕ=1). Следовательно, при необходимости точного запуска микропроцессора из состояния останова сигналом INТ до команды HLT необходимо разрешить прерывания с помощью команды EI. Реагируя на сигнал INT, микропроцессор вводит цикл Ml выборки команды рестарта. Если же микропроцессор остановлен и INТЕ=0, то единственным средством запуска оказывается сигнал RESET.

Рисунок 1.13 - Введение состояния останова

Важно подчеркнуть, что в состоянии останова микропроцессор стандартным образом реагирует на сигнал HOLD запроса ПДП с формированием сигнала HLDA подтверждения ПДП для контроллера ПДП. Действия микропроцессора в состоянии останова показаны на рисунке 1.13.

Реакция микропроцессора на сигнал INT. В БИС микропроцессора имеется несложная схема обработки прерываний с двумя внешними сигналами: на входную линию прерывания INT подключаются сигналы готовности медленных периферийных устройств к обмену данными, а сигнал на выходной линии разрешения прерываний INTE определяет, будет микропроцессор реагировать на запросы прерываний (INТЕ = 1) или нет (INТЕ=0).

При восприятии запроса прерывания (INT=1, INTE=1) необходимо: прервать текущую программу; временно запомнить содержимое программного счетчика, как адрес возврата; передать управление обработчику прерываний того периферийного устройства, запрос которого воспринят; восстановить состояние прерванной программы и возобновить ее выполнение. Для временного запоминания содержимого PC и других внутренних регистров, которые будет модифицировать обработчик прерываний, удобно использовать стек.

В МП системах на базе микропроцессора К580 реализована так называемая векторная приоритетная система прерываний. Асинхронный сигнал прерывания, идентифицируемый Н-уровнем на линии INТ, может появиться в любой момент цикла команды. Внутренняя схема синхронизирует внешний запрос и устанавливает соответствие с сигналами системной синхронизации, обеспечивая завершение выполнения текущей команды. В последнем такте последнего машинного цикла всех команд (кроме команды разрешения прерываний) при действии INТ =1 и INТЕ=1 по нарастающему фронту сигнала Ф2 устанавливается внутренний триггер прерываний. Это приводит к тому, что следующим тактом оказывается такт Т1 машинного цикла «ПРЕРЫВАНИЕ». Он напоминает цикл «ВЫБОРКА КОДА ОПЕРАЦИИ», так как в байте состояния установлен бит Ml, но одновременно установлен и бит подтверждения прерывания INTA, который квитирует восприятие микропроцессором запроса прерывания, а бит считывания из памяти MEMR сброшен.

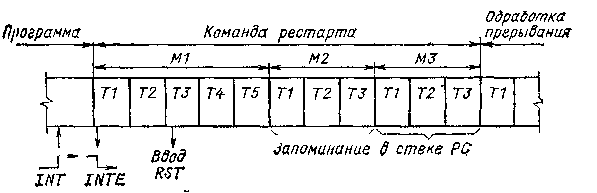

Рисунок 1.14 - Выполнение команды рестарта

В такте Т1 микропроцессор выдает на шину адреса содержимое PC, а на шину данных —байт состояния (Ml = l, INTA=1, MEMR= 0). В том же такте по нарастающему фронту Ф2 с максимальной задержкой 200 нс формируется L-уровень на выходе INTE (рисунок 1.14). Следовательно, микропроцессор будет игнорировать последующие запросы прерываний до тех пор, пока триггер разрешения прерываний не будет установлен командой EI. В такте Т2 генерируется сигнал считывания DBIN, который в обычном цикле Ml вводит код операции из программной памяти в регистр команды. Но в цикле «ПРЕРЫВАНИЕ» обращение к программной памяти запрещено (бит MЕМR = 0), и поэтому код операции должна сформировать подсистема прерываний. Заметим, что в такте Т2 цикла «ПРЕРЫВАНИЕ» инкремент PC не производится (формируется внутренний сигнал запрещения выхода схемы инкремента), поэтому в нем сохраняется адрес команды, которая выполнялась бы при отсутствии прерывания. Кроме того, в такте Т2 сбрасывается внутренний триггер прерывания. Очевидно, для загрузки содержимого PC в стек подсистема прерывания должна сформировать команду вызова. Стандартная команда вызова CALL является 3-байтной и выполняется за пять машинных циклов, Чтобы ускорить реакцию микропроцессора на прерывания и упростить интерфейс с подсистемой прерываний, в систему команд включена специальная 1-байтная команда вызова, называемая рестартом (RESTART, или RST) с кодом операции 11ААА111. Трехбитное поле ААА, называемое вектором, должно быть сформировано периферийным устройством, на запрос которого реагирует микропроцессор. В такте ТЗ команда рестарта с шины данных загружается в регистр команд, а такты Т4 и Т5 отведены на дешифрирование команды RST.

Команда RST инициирует выполнение двух действий:

содержимое PC загружается в стек. Для этого вводятся трех-тактные циклы М2 и МЗ «ЗАПИСЬ В СТЕК»;

в PC передается код 00000000 ООАААООО, который «направляет» микропроцессор к начальному адресу обработчика прерываний. Таким образом, биты ААА однозначно идентифицируют периферийное устройство, сформировавшее запрос на обслуживание.

После указанных действий обычным образом вводится цикл «ВЫБОРКА КОДА ОПЕРАЦИИ» первой команды обработчика прерываний, и производятся необходимые действия по обмену данными с периферийным устройством. Последней командой обработчика прерываний должна быть команда возврата RETURN, которая возвращает в PC запомненный в стеке адрес возврата.

При анализе временных соотношений прерывания необходимо учесть, что при выполнении команды разрешения прерываний EI микропроцессор не реагирует на сигнал INT, т. е. после EI обязательно выполняется следующая команда. На линии INТ должен сохраняться Н-уровень до выдачи бита подтверждения прерывания INTA.