Организация шин. Принципы построения мпс. Архитектура мп. Организация внешней памяти мк

| Вид материала | Конспект |

- Изучение нового материала Изучаемые вопросы: • Из каких устройств состоит компьютер, 231.35kb.

- Рабочая программа По дисциплине «Сетевые технологии» По специальности 230102. 65 Автоматизированные, 210.65kb.

- 1. Общие принципы построения ЭВМ принципы построения и архитектура ЭВМ, 70.58kb.

- Организация работы органа студенческого самоуправления во внешней среде, 16kb.

- Принципы и особенности организации новой системы государственной (итоговой) аттестации, 10.02kb.

- Лекция 3, 170.54kb.

- Введение в экономическую информатику, 2107.81kb.

- А. Ю. Пантелеев Национальный исследовательский ядерный университет «мифи» Масштабируемая, 11.38kb.

- Архитектура пк. Магистрально-модульный принцип построения, 244.23kb.

- Стратегическое планирование 4 1 Распределение ресурсов 6 2 Адаптация к внешней среде, 541.11kb.

ФСПО. «МК и МП» Конспект лекции №1.2

Организация шин. Принципы построения МПС. Архитектура МП.

Организация внешней памяти МК

План лекции:

- Организация шин

- Принципы построения микропроцессорных систем

- Обобщенная структурная схема МПС

- Архитектура МП

- Анализ подключения внешней памяти

1.Организация шин

Ш

ина — это информационный канал, который объединяет все функциональные блоки МПС и обеспечивает обмен данными.

ина — это информационный канал, который объединяет все функциональные блоки МПС и обеспечивает обмен данными. Конструктивно шина представляет собой n проводников и один общий проводник (земля). Данные по шине передаются в виде слов, которые являются группами бит.

В параллельной шине п бит информации передаются по отдельным линиям одновременно, в последовательной шипе — по одной линии последовательно во времени.

Все основные блоки МПС соединены с единой параллельной шиной, которая называется системной шиной SB (System Bus). Системная шина содержит три шины: адреса, данных и управления.

Ш

ина адреса АВ (Address Bus) является однонаправленной. Она предназначена для передачи адреса ячейки памяти или устройства ввода/вывода. Направление передачи по шине адреса — от МП к внешним устройствам. Варианты условных обозначений однонаправленной параллельной шины показаны на рисунке 1, где стрелка указывает направление передачи.

ина адреса АВ (Address Bus) является однонаправленной. Она предназначена для передачи адреса ячейки памяти или устройства ввода/вывода. Направление передачи по шине адреса — от МП к внешним устройствам. Варианты условных обозначений однонаправленной параллельной шины показаны на рисунке 1, где стрелка указывает направление передачи.

Рисунок 1 – Варианты условных обозначений однонаправленной параллельной 16-разрядной шины

Шина данных DB (Data Bus) является двунаправленной. Она предназначена для передачи данных между блоками МПС. Информация по одним и тем же линиям DB может передаваться в двух направлениях — как к МП, так и от него. Варианты условных обозначений двунаправленной шины показаны на рисунке 2.

Рисунок 2 – Варианты условных обозначений двунаправленной параллельной 8-разрядной шины.

Шина управления СВ (Control Bus) предназначена для передачи управляющих сигналов. Хотя направление управляющих сигналов может быть разным, однако шина управления не является двунаправленной, поскольку для сигналов разного направления используются отдельные линии.

2.Принципы построения микропроцессорных систем

В основу построения МПС-систем положено три принципа:

- магистральности;

- модульности;

- микропрограммного управления.

Принцип магистральности определяет характер связей между функциональными блоками МПС — все блоки соединяются с единой системной шиной.

Принцип модульности состоит в том, что система строится на основе ограниченного количества типов конструктивно и функционально законченных модулей.

Каждый модуль МПС имеет вход управления третьим (высокоимпедансным) состоянием. Этот вход называется CS (Chip Select) — выбор кристалла, или ОЕ (Output Enable) — разрешение выхода. Действие сигнала CS для триггера показано на рисунок 3. Выходной сигнал триггера Q появится на выходе лишь при активном (в данном случае — нулевом) уровне сигнала CS . Если CS = 1, триггер переводится в высокоимпедансное состояние. Выход триггера является трехстабильным, т. е. может находиться в одном из трех состояний: логической единицы, логического нуля или высокоимпедансном.

Рисунок 3 Действие сигнала CS для триггера

В каждый момент времени к системной шине МПС подсоединено лишь два модуля — передающий и принимающий информацию. Остальные модули находятся в высокоимпедансном состоянии (рисунок 4).

Рисунок 4 – Подключение модулей к системной шине

Это объясняется тем, что для построения МПС используются высокоскоростные и маломощные БИС, выводы которых не рассчитаны на большой ток, который возможен при подключении нескольких приёмников, кроме того это приводит к увеличению помех наводимых в проводниках схемы и соответственно уменьшается надёжность устройства. Наличие нескольких передатчиков не допускается, очевидно, по причине возможных конфликтов и, соответственно, искажения информации или выходу БИС из строя.

Принципы магистральности и модульности позволяют наращивать управляющие и вычислительные возможности МП путем подсоединения других модулей к системной шине.

Принцип микропрограммного управления состоит в возможности осуществления элементарных операций — микрокоманд (сдвигов, пересылок информации, логических операций). Используя определенные комбинации микрокоманд, можно создать технологический язык, т. е. набор команд, который максимально соответствует назначению системы.

3.Обобщенная структурная схема МПС

Обобщенная структурная схема МПС показана на рисунке 5.

В состав МПС входят: центральный процессор (ЦП), ПЗУ, ОЗУ, система прерываний, таймер, устройства ввода/вывода (УВВ).

Рисунок 5 – Обобщенная структурная схема МПС

Постоянное и оперативное запоминающие устройства (ПЗУ, ОЗУ) образуют систему памяти, предназначенную для хранения информации в виде двоичных чисел. Память организована в виде массива ячеек, каждая из которых имеет свой адрес и содержит байт или слово. Байтом называется группа из 8 бит, а слово может иметь любую длину в битах. Наиболее часто под словом понимают двоичное число длиной два байта. Для обращения к ячейке памяти необходимо выдать ее адрес на шину адреса

Модуль центрального процессора осуществляет обработку данных и управляет всеми остальными модулями системы. Центральный процессор, кроме БИС МП, содержит схемы синхронизации и интерфейса с системной шиной. Он осуществляет выборку кодов команд из памяти, дешифрует их и выполняет.

Устройства ввода/вывода или внешние устройства — это устройства, предназначенные для ввода информации в МП или вывода информации из него Примерами УВВ являются дисплеи, печатающие устройства, клавиатура, цифро-аналоговый и аналогоцифровой преобразователи, реле, коммутаторы. Для соединения УВВ с системной шиной их сигналы должны соответствовать определенным стандартам, что реализуется с помощью интерфейсов ввода/вывода.

Система прерываний позволяет МПС реагировать на внешние сигналы — запросы прерываний, источниками которых могут быть: сигналы готовности от внешних устройств, сигналы от генераторов, сигналы с выходов датчиков. При появлении запроса на прерывание ЦП прекращает выполнение основной программы и переходит к выполнению подпрограммы обслуживания запроса прерывания. Для построения системы прерываний МПК содержат БИС специальных программируемых контроллеров прерываний.

Таймер предназначен для реализации функций, связанных с отсчетом времени. После того как МП загружает в таймер число, задающее частоту, задержку или коэффициент деления, таймер реализует необходимую функцию.

4.Архитектура микропроцессора

Понятие архитектуры микропроцессора определяет его составные части, а также связи и взаимодействие между ними. Архитектура включает:

- структурную схему МП;

- программную модель МП (описание функций регистров);

- информацию об организации памяти (емкость и способы адресации памяти);

- описание организации процедур ввода/вывода.

Существуют два основных типа архитектуры — фон-неймановская и гарвардская.

Фон-неймановскую архитектуру (рисунок 6, а) предложил в 1945 году американский математик Джо фон Нейман. Особенностью этой архитектуры является то, что программа и данные находятся в общей памяти, доступ к которой осуществляется по одной шине данных и команд. К достоинствам данной архитектуры можно отнести ее универсальность, т.к. программист сам решает, сколько памяти отвести для хранения программ, а сколько для данных. Фон-неймановская архитектура используется в микропроцессорах при построении персональных компьютеров.

Гарвардская архитектура впервые была реализована в 1944 году в релейной вычислительной машине Гарвардского университета (США). Особенностью этой архитектуры является то, что память данных и память программ разделены и имеют отдельные шину данных и шину команд (рисунок 6, б), что позволяет повысить быстродействие МП системы. На базе гарвардской архитектуры построено большинство микроконтроллеров.

Структурные схемы обоих типов архитектур содержат: процессорный элемент, память, интерфейсы ввода/вывода (ИВВ) и УВВ.

Память и ИВВ для разных типов МП могут быть как внутренними, т. е. размещаться на том же кристалле, что и процессорный элемент, так и внешними. Процессорный элемент содержит регистры, арифметико-логическое устройство (АЛУ), устройство управления и выполняет функции обработки данных и управления процессами обмена информацией. Память обеспечивает хранение данных и кодов команд программы. Интерфейсы ввода/вывода предназначены для связи с УВВ, например, с клавиатурой, дисплеем, печатающими устройствами, датчиками. Все элементы структурной схемы соединены с помощью шин.

Рисунок 6 – Основные типы архитектур: а -- фон-неймановская; б -- гарвардская

5.Анализ подключения внешней памяти

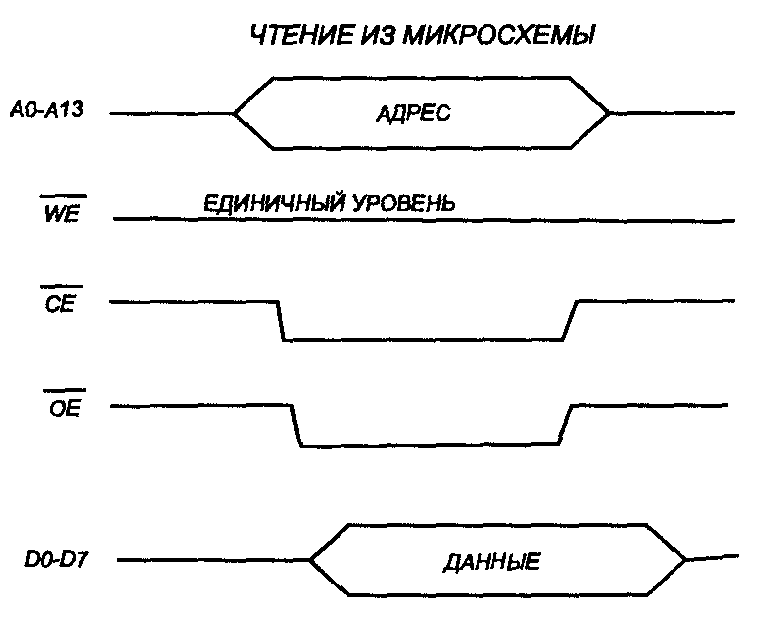

Внешняя память данных представляет собой одну или несколько самостоятельных микросхем памяти. Чаще всего используют статическую память с байтовой организацией объемом 2К*8 или 8К*8 бит (1К = 1024). Такие микросхемы; имеют 8 выводов данных (D0-D7), по которым осуществляется одно-временная запись в микросхему всех 8 бит в выбранную ячейку памяти или чтение 8 бит из этой ячейки. Далее, в таких микросхемах есть 11 или. 13 адресных входов (А0-А10 или А0-А12), комбинация сигналов на которых задает адрес ячейки, к которой мы обращаемся. Вход (Write Enable – Разрешение Записи) определяет характер обращения: если на нем установлена 1, то осуществляется чтение из выбранной ячейки; при WE = 0 в ячейку будет записана информация. Вход (Chip Enable - Разрешение Кристала) активизирует микросхему памяти — когда на ее входе СЕ установлена 1, она выключена, при СЕ = 0 она допускает запись в нее информации и чтение из нее записанных данных. Нулевой сигнал на входе (Output Enable – Разрешение Вывода) включает выходные буферы микросхемы памяти на пропускание информации по линиям данных D0-D7, единичный сигнал переводит эти линии в третье состояние, т. е. отключает находящиеся внутри микросхемы ячейки памяти от ее ножек. Описываемые микросхемы изображены на рисунке 7.

Рисунок 7 – Обозначение микросхем памяти

Работа с подобными микросхемами должна осуществляться следующим образом. Положим, мы хотим записать число 145D = 10010001В в ячейку с адресом 84D = 54Н = 1010100В. Для этого МК должен установить записываемое число на линиях данных D0-D7 микросхемы (D0=D4=D7=1, D1=D2-D3=D5=D6=0), а адрес ячейки — на адресных линиях (А2=А4=А6=1, А0=А1=АЗ=А5=0; А7, А8 и последующие старшие адреса вплоть до А10 для микросхем объемом 2К* 8 или до А12 для микросхем 8К*8 также должны быть установлены в 0). Установив адресную информацию и данные, МК одновременно с этим или чуть позже должен установить 0 на входе WE микросхемы (будет запись) и 0 на СЕ (знак того, что мы обращаемся именно к этой микросхеме). Как только после этого на входе ОЕ микросхемы памяти МК установит 0, осуществится запись числа 145 в ее 84-ю ячейку.

Соответственно, если мы хотим прочитать данные из все той же, к примеру, 84-й ячейки, мы должны, как и в предыдущем случае, установить адрес ячейки на адресных линиях, и одновременно с этим или чуть позже установить 1 на входе WE микросхемы (будет чтение) и 0 на СЕ (знак того, что мы обращаемся именно к этой микросхеме). Как только после этого на входе ОЕ микросхемы памяти МК установит 0, осуществится чтение числа из выбранной ячейки, и оно появится на линиях данных D0-D7 микросхемы памяти. Сказанное поясняется временными диаграммами, приведенными на рисунке 8.

Рисунок 8 – Диаграммы чтения и замиси микросхем памяти

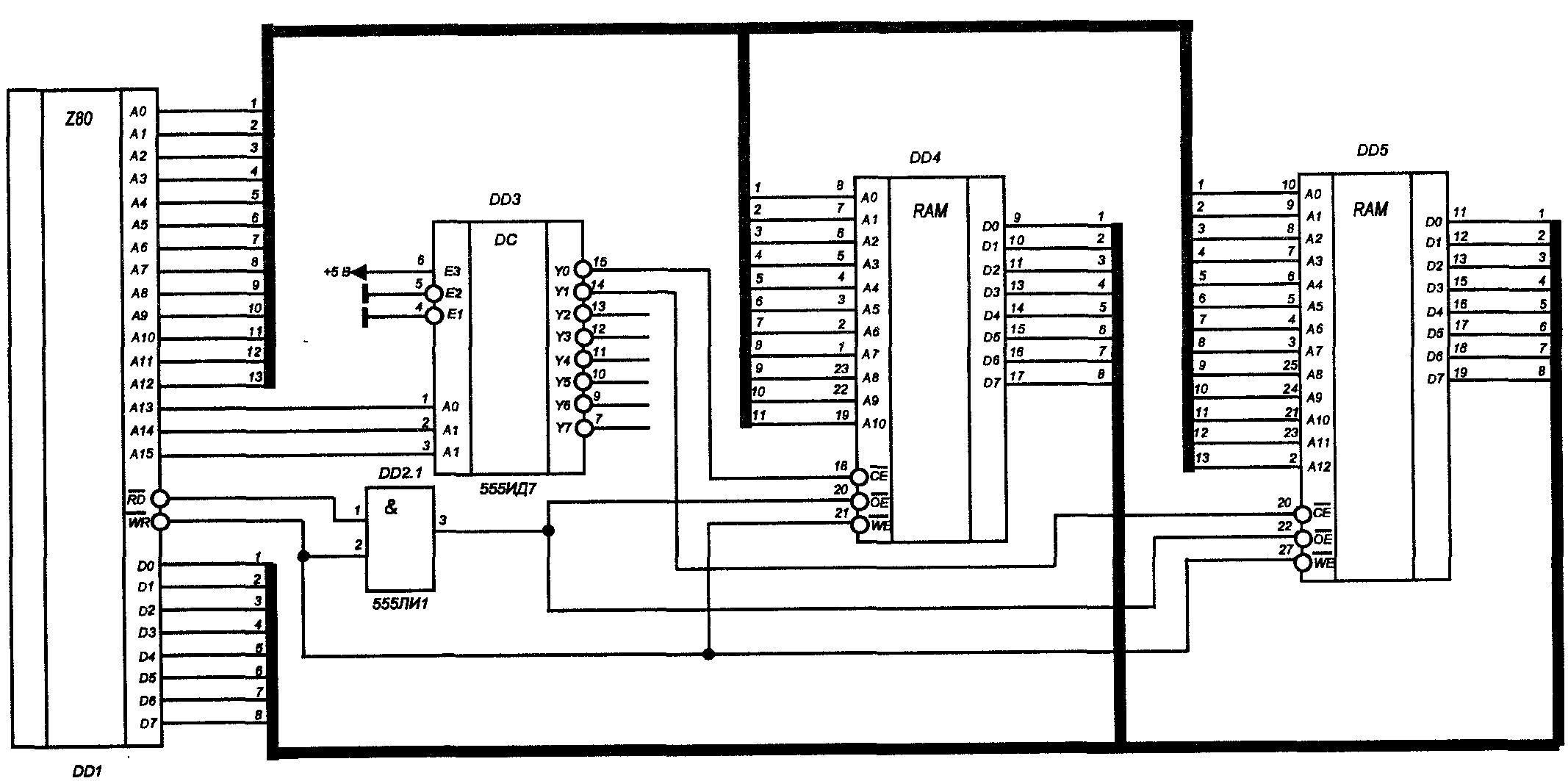

Пример подключения внешней памяти данных к микропроцессору Z80

У Z80 есть выводы трех так называемых шин — адреса, данных и управления.

Шестнадцать выводов Z80 (А0, Al, А2,..., А14 и А15) называются адресными выходами, их соединяют с адресными входами микросхем памяти. Совокупность линий, осуществляющих эти соединения, и есть шина адреса. Соответственно, шина данных, состоящая из 8 проводников, соединяет выводы данных микросхем памяти и микропроцессора (у него, как и у микросхем памяти, их тоже 8, и обозначаются они также— D0, D1,..., D7).

Из сигналов управления у Z80 нас интересуют только два – (Read - Чтение) и (Write - Запись). С их помощью, как показано на рисунке 9, осуществляется управление памятью.

Рисунок 9 Подключение микросхем памяти к микропроцессору Z80

При обращении к памяти Z80 формирует на своих выводах А0-А15 адрес ячейки, к которой будет происходить обращение (запись или чтение). Как будет показано чуть ниже, соответствующая комбинация сигналов на А13-А15 сформирует при помощи дешифратора DD3 нулевой сигнал на входе СЕ той или иной микросхемы.

При записи на выводах данных D0-D7 процессора появится байт, который предстоит записать в память, и чуть-чуть позже его появления — нулевой сигнал на выходе WR (RD при этом останется в 1). Как нетрудно догадаться, микросхема DD2 в любом цикле обращения (как чтения, когда RD=0, так и записи, когда WR =0) сформирует нуль на входах ОЕ микросхем ОЗУ.

Соответственно при чтении выводы данных превращаются во входы, и на них процессор ничего не выводит, а после установки адреса он переводит в 0 сигнал RD (WR при этом остается в 1).

В каждой из микросхем памяти есть своя нулевая, первая, вторая и т. д. ячейки, вплоть до 2048-й. Обратите внимание, что входы СЕ микросхем соединены с выходами дешифратора DD3, в частности СЕ DD4 — с DD3.15, а СЕ DD5 —- с DD3.14. На выходе DD3.15 нулевой сигнал возникнет в том случае, когда на своих трех старших адресных выходах микропроцессор установит следующую комбинацию сигналов: А15=0, А14=0, А13=0. Соответственно, нуль на DD3.14 появится, если А15=0, А14=0, А13=1. Следовательно, чтобы вести обмен с 84-й ячейкой микросхемы DD4, микропроцессор должен установить на адресных выходах комбинацию А0=А1=0; А2=1; А3=0; А4=1; А5=0; А6=1; А7=А8=А9=А10=А13=А14=А15=0. Поскольку у DD4 отсутствуют входы А11 и А12, и эти адресные линии к ней не подводятся, то их состояние (нули или единицы) никак не сказывается на адресе выбираемой ячейки в этой микросхеме. Для определенности положим, что и они должны быть при обращении к DD4 нулевыми. Таким образом, в изображенной на рисунке 9 системе к 84-й ячейке микросхемы DD4 микропроцессор обратится, установив на адресной шине 0000000001010100В=0054Н=84. Другими словами, 84-я ячейка памяти нашей системы находится именно в DD4.

Для обращения к 84-ой ячейки DD5 процессор должен установить на адресной шине 0010000001010100В=2054Н=8276. Иначе говоря, 84-я ячейка памяти микросхемы DD5 является 8276-й ячейкой системы памяти.

Пример подключения внешней памяти данных к микрокронтроллеру семейства x51

Линии порта Р2 микроконтроллера при обращении к внешней памяти выводят адресные биты А8-А15. Далее, сигнал формируется на Р3.7, a — на Р3.6.

Линии порта Р0 представляют мультиплексированную во времени шину адреса/данных. Т.е. линии P0 используются для ввода/вывода информации с шины данных. Но, кроме того, в первый момент обращения к памяти по этим же линиям выводятся адреса А0...А7, и одновременно с этим устанавливается в 1 сигнал на выходе ALE (адреса стробируются сигналом ALE). Спустя 2 периода тактового генератора ALE сбрасывается в 0, и через несколько наносекунд после этого адресная информация пропадает с линий порта Р0, давая возможность вести по ним обмен данными. А для того, чтобы использовать адреса А0-А7, применяют 8-разрядный регистр-защелку типа 555ИР22, информация в котором фиксируется по спаду сигнала на его входе STB. В качестве этого сигнала, как нетрудно догадаться, используется сигнал ALE (это основное его назначение). Сказанное иллюстрируется на рисунке 10.

Рисунок 10 Подключение микросхем памяти к микроконтроллеру семейства х51

Таким образом, работа МК с внешней памятью данных осуществляется следующим образом. Прочитав команду обращения к внешней памяти, микроконтроллер выводит по линиям порта Р2 старшие 8 бит адреса, а по линиям Р0 — младшие. Одновременно с этим он устанавливает в 1 сигнал на выходе ALE. Когда эта 1 поступает на вход STB регистра-защелки DD3, информация с его входов D0-D7 напрямую поступает на выходы Q0- Q7, соединенные с младшими 8 линиями шины адреса. Спустя некоторое время ALE устанавливается в 0. Перепад из 1 в 0 на входе STB DD3 приводит к защелкиванию в регистрах выходов Q0-Q7 поступающей на них информации, и защелкнутые младшие 8 бит адреса остаются неизменными на выходах Q0-Q7 до следующего цикла обмена с внешней памятью. Старшие 8 бит, выводимые через Р2, также не меняются до завершения текущего цикла работы с внешним ОЗУ.

Поскольку А0-А7 запомнены в регистре-защелке, они снимаются с выводов порта Р0, и последние превращаются в выводы шины данных. Если МК записывает данные во внешнее ОЗУ, записываемый байт выводится им на Р0.0-Р0.7, и устанавливается в 0 сигнал на его выходе WR (РЗ.6). Появление же нулевых сигналов на входах WE и ОЕ, соответствующей микросхемы памяти приводит к записи в нее байта, поданного на ее входы D0-D7. Нулевой сигнал на ОЕ, формирует микросхема DD2. Сказанное иллюстрируется временными диаграммами на рисунке 11.

Рисунок 11 Временные диаграммы циклов обмена МК с внешней памятью данных

В отличие от схемы на рисунке 9 в схеме на рисунке 10 отсутствует дешифратор, управлявшийся адресами А13-А15. Вместо этого на входы СЕ микросхем памяти поданы сигналы с А13 и А14. Такое решение возможно, если вы точно знаете, что в вашей системе не будет использоваться более трех микросхем внешней памяти (дешифратор DD3 на рисунке 9 позволял работать с 8-ю микросхемами). При обращении к DD4 МК должен установить следующую комбинацию старших адресов: А13=0, А14=А15=1. Соответственно для DD5 А13= 1, А14=0, А15= 1. А какая комбинация потребовалась бы для 3-й микросхемы, если ее вход СЕ соединить с А15?

Процесс чтения информации микроконтроллером аналогичен только что рассмотренному процессу записи с той лишь разницей, что МК устанавливает в 0 не WR , a RD, и данные на шину данных поступают не с него, а с соответствующей микросхемы памяти.

Описанный способ выдачи адресной информации по выводам шины данных очень распространен (он применялся, например, в процессорах 8086/8088, на которых были выполнены первые IBM PC), и называется мультиплексированием шин адреса/данных.

Подключения внешней памяти программ к микрокронтроллеру семейства x51

Микроконтроллеры семейства х51 допускают работу с внешней памятью программ, в качестве которой выступают микросхемы ПЗУ объемом до 64 кбайт. Их подключение и работа аналогичны подключению и работе в режиме чтения микросхем памяти данных ОЗУ. В качестве сигнала чтения используется сигнал вывода вместо сигнала.

Контрольные вопросы

- Назовите принципы построения МПС и охарактеризуйте их.

- Приведите типовую структуру МПС и объясните назначения функциональных модулей.

- Объясните назначение входа управления третьим состоянием.

- Дайте определение архитектуры МП.

- Укажите различия между гарвардской и фон-неймановской архитектурами.

Темы для сообщений

- Типы корпусов микросхем.

- Арифметико-логическое устройство.

- Регистры общего назначения.

- Стек.