Инженерная логика против классической

| Вид материала | Книга |

- Программа курса и темы практических занятий; Логика в таблицах и схемах. Логика как, 1722.34kb.

- Логика в образовании, 153.37kb.

- Математическая логика, 1012.22kb.

- Курс: 1 семестр 2 дисциплина: Инженерная графика задания для самостоятельной работы, 459.93kb.

- Логика богочеловечества, 213.06kb.

- Гуманитарное образование в технических вузах России в 19 20 веках, 261.32kb.

- Активизирующий опросник "За и против", 392.33kb.

- Отчет о выполнении 1 этапа проекта кафедры «Инженерная графика и дизайн», 95.62kb.

- «Инженерная экономика и маркетинг», 412.65kb.

- Н. В. Папуловская Математическая логика Методическое пособие, 786.38kb.

Глава восьмая

ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ.

8.1. Структура и характеристики ПЛИС.

Проектирование цировых устройств на базе традиционных серий ИС насчитывает более 30 лет и стало давно привычным делом даже для радиолюбителей. Однако разработчики сталкиваются с некоторыми проблемами: большой размер плат, невысокая надёжность из-за значительного числа корпусов и соединений между ними, при которых теряется быстродействие устройства и возрастает энергопотребление. К тому же отладка и настройка таких устройств сложна, трудоёмка и зачастую приводит к появлению навесных проводников и деталей. Устранить эти проблемы помогает применение новейших технологий, а в частности использование программируемых логических интегральных схем (ПЛИС, в зарубежной аббревиатуре - PLD)[39]. Основным отличием ПЛИС от базовых матричных кристаллов (БМК) и заказных ИС является возможность проектирования отладки и тиражирования специализированной схемы самим разработчиком непосредственно на рабочем месте. Это обусловлено как технологией изготовления ПЛИС (EPROM/EEPROM), так и наличием развитых средств автоматизации.

Для многих разработчиков аппаратуры ЦОС стало ясно, что программируемые логические интегральные схемы (ПЛИС) — удобная в освоении и применении элементная база, альтернативы которой зачастую не найти. Последние годы характеризуются резким ростом плотности упаковки элементов на кристалле, многие ведущие производители либо начали серийное производство, либо анонсировали ПЛИС с эквивалентной ёмкостью более 1 млн. логических вентилей. Цены на ПЛИС неуклонно падают. Так, ещё в 1998г. ПЛИС ёмкостью 100 000 вентилей стоила в Москве, в зависимости от производителя, приёмки и быстродействия, от 1500 до 3000 у.е., а спустя 2 года такая микросхема стоит от 100 до 350 у.е., то есть цены упали практически на порядок, и эта тенденция устойчива. Что касается ПЛИС ёмкостью 10000 – 30 000 логических вентилей, то появились микросхемы стоимостью менее 10 у.е.

Приведём известную классификацию ПЛИС [39] по структурному признаку, так как она даёт наиболее полное представление о классе задач, пригодных для решения на той или иной ПЛИС. Следует заметить, что общепринятой оценкой логической ёмкости ПЛИС является число эквивалентных вентилей, определяемое как среднее число вентилей “2И-НЕ”, необходимых для реализации эквивалентного проекта на ПЛИС и базовом матричном кристалле (БМК). Понятно, что эта оценка весьма условна, поскольку ПЛИС не содержат вентилей “2И-не” в чистом виде, однако для проведения сравнительного анализа различных архитектур она вполне пригодна. Основным критерием такой классификации является наличие, вид и способы коммутации элементов логических матриц. По этому признаку можно выделить несколько классов ПЛИС.

Программируемые логические матрицы — наиболее традиционный тип ПЛИС, имеющий программируемые матрицы “И” и “ИЛИ”. В зарубежной литературе соответствующими этому классу аббревиатурами являются FPLA (Field Programmable Logic Array) и FPLS (Field Programmable Logic Sequensers). Примерами таких ПЛИС могут служить отечественные схемы K556PT1, PT2,PT21. Недостаток такой архитектуры — слабое использование ресурсов программируемой матрицы “ИЛИ”, поэтому дальнейшее развитие получили микросхемы, построенные по архитектуре программируемой матричной логики (PAL — Programmable Array Logic) — это ПЛИС, имеющие программируемую матрицу ”И” и фиксированную матрицу “ИЛИ”. К этому классу относятся большинство современных ПЛИС небольшой степени интеграции. В качестве примеров можно привести отечественные ИС КМ1556ХП4, ХП6, ХП8, ХЛ8, ранние разработки (середина–конец 1980-х годов) ПЛИС фирм INTEL, ALTERA, AMD, LATTICE и др. Разновидностью этого класса являются ПЛИС, имеющие только одну (программируемую) матрицу “И”, например, схема 85C508 фирмы INTEL. Следующий традиционный тип ПЛИС — программируемая макрологика. Они содержат единственную программируемую матрицу “И-НЕ” или “ИЛИ-НЕ”, но за счёт многочисленных инверсных обратных связей способны формировать сложные логические функции. К этому классу относятся, например, ПЛИС PLHS501 и PLHS502 фирмы SIGNETICS, имеющие матрицу “И-НЕ”, а также схема XL78C800 фирмы EXEL, основанная на матрице “ИЛИ-НЕ”.

Вышеперечисленные архитектуры ПЛИС содержат небольшое число ячеек, к настоящему времени морально устарели и применяются для реализации относительно простых устройств, для которых не существует готовых ИС средней степени интеграции. Естественно, для реализации алгоритмов ЦОС они непригодны. ИС ПМЛ (PLD) имеют архитектуру, весьма удобную для реализации цифровых автоматов. Развитие этой архитектуры — программируемые коммутируемые матричные блоки (ПКМБ) — это ПЛИС, содержащие несколько матричных логических блоков (МЛБ), объединённых коммутационной матрицей. Каждый МЛБ представляет собой структуру типа ПМЛ, то есть программируемую матрицу “И”, фиксированную матрицу “ИЛИ” и макроячейки. ПЛИС типа ПКМБ, как правило, имеют высокую степень интеграции (до 10000 эквивалентных вентилей, до 256 макроячеек). К этому классу относятся ПЛИС семейства MAX5000 и MAX7000 фирмы ALTERA, схемы XC7000 и XC9500 фирмы XILINX, а также большое число микросхем других производителей (Atmel, Vantis, Lucent и др.). В зарубежной литературе они получили название Complex Programmable Logic Devices (CPLD). Другой тип архитектуры ПЛИС — программируемые вентильные матрицы (ПВМ), состоящие из логических блоков (ЛБ) и коммутирующих путей — программируемых матриц соединений. Логические блоки таких ПЛИС состоят из одного или нескольких относительно простых логических элементов, в основе которых лежит таблица перекодировки (ТП, Look-up table — LUT), программируемый мультиплексор, D-триггер, а также цепи управления. Таких простых элементов может быть достаточно много, например, у современных ПЛИС ёмкостью до 1 млн. вентилей число логических элементов достигает нескольких десятков тысяч. За счёт такого большого числа логических элементов они содержат значительное число триггеров, а также некоторые семейства ПЛИС имеют встроенные реконфигурируемые модули памяти (РМП, embedded array block — EAB), что делает ПЛИС данной архитектуры весьма удобным средством реализации алгоритмов цифровой обработки сигналов, основными операциями в которых являются перемножение, умножение на константу, суммирование и задержка сигнала. Вместе с тем, возможности комбинационной части таких ПЛИС ограничены, поэтому совместно с ПВМ применяют ПКМБ (CPLD) для реализации управляющих и интерфейсных схем. В зарубежной литературе такие ПЛИС получили название Field Programmable Gate Array (FPGA). К FPGA (ПВМ) классу относятся ПЛИС XC2000, XC3000, XC4000, Spartan, Virtex фирмы XILINX; ACT1, ACT2 фирмы ACTEL, а также семейства FLEX8000 фирмы ALTERA, некоторые ПЛИС Atmel и Vantis. Типичным примером FPGA ПЛИС могут служить микросхемы семейства Spartan фирмы XILINX (рис. 1). Множество конфигурируемых логических блоков (Configurable Logic Blocks — CLBs) объединяются с помощью матрицы соединений. Характерными для FPGA-архитектур являются элементы ввода/вывода (input/output blocks — IOBs), позволяющие реализовать двунаправленный ввод/вывод, третье состояние и т. п.

Особенностью современных ПЛИС является возможность тестирования узлов с помощью порта JTAG (B-scan), а также наличие внутреннего генератора (Osc) и схем управления последовательной конфигурацией.

Фирма Altera пошла по пути развития FPGA-архитектур и предложила в семействе FLEX10K так называемую двухуровневую архитектуру матрицы соединений (рис. 2). ЛЭ объединяются в группы — логические блоки (ЛБ). Внутри логических блоков ЛЭ соединяются посредством локальной программируемой матрицы соединений, позволяющей соединять любой ЛЭ с любым. Логические блоки связаны между собой и с

Р

ис.1

элементами ввода/вывода посредством глобальной программируемой матрицы соединений (ГПМС). Локальная и глобальная матрицы соединений имеют непрерывную структуру — для каждого соединения выделяется непрерывный канал. Дальнейшее развитие архитектур идёт по пути создания комбинированных архитектур, сочетающих удобство реализации алгоритмов ЦОС на базе таблиц перекодировок и реконфигурируемых модулей памяти, характерных для FPGA-структур и многоуровневых ПЛИС с удобством реализации цифровых автоматов на CPLD-архитектурах. Так, ПЛИС APEX20K фирмы Altera (рис. 3) содержат в себе логические элементы всех перечисленных типов, что позволяет применять ПЛИС как основную элементную для “систем на кристалле” (system-on-chip, SOC).

В основе идеи SOC лежит интеграция всей электронной системы в одном кристалле (например, в случае ПК такой чип объединяет процессор, память, и т. д.). Компоненты этих систем разрабатываются отдельно и хранятся в виде файлов параметризируемых модулей. Окончательная структура SOC-микросхемы выполняется на базе этих “виртуальных компонентов” с помощью программ систем автоматизации проектирования (САПР) электронных устройств — EDA (Electronic Design Automation). Благодаря стандартизации в одно целое, можно объединять “виртуальные компоненты” от разных разработчиков.

Как известно, при выборе элементной базы систем обработки сигналов обычно руководствуются следующими критериями отбора: быстродействие; логическая ёмкость, достаточная для реализации алгоритма; схемотехнические и конструктивные параметры ПЛИС, надёжность, рабочий диапазон температур, стойкость к ионизирующим излучениям и т. п.; стоимость владения средствами разработки, включающая как стоимость программного обеспечения, так наличие и стоимость аппаратных средств отладки; стоимость оборудования для программирования ПЛИС или конфигурационных ПЗУ; наличие методической и технической поддержки; наличие и надёжность российских поставщиков; стоимость микросхем.

Рассмотрим с этих позиций продукцию ведущих мировых производителей ПЛИС, доступную на российском рынке.

Фирма Altera Corporation, (101 Innovation Drive, San Jose, CA 95134, USA, a.com/) была основана в июне 1983 года. В настоящее время High-end продуктом этой фирмы является семейство APEX20K, особенности архитектуры которого упоминались выше, а в табл. 1 приведены основные параметры ПЛИС этого семейства.

Таблица 1. Основные характеристики ПЛИС семейства APEX20K фирмы ALTERA

Кроме того, Altera выпускает CPLD семейств MAX3000, MAX7000, MAX9000 (устаревшие серии специально не упоминаются) и FPGA семейств FLEX10K, FLEX8000, FLEX6000.

Необходимо подчеркнуть, что емкостная нагрузка выходов ПЛИС Altera составляет не более 33 пФ. При этом нужно иметь в виду, что в среднем погонная ёмкость кабеля составляет 1 пФ/см, т.е. при обычной длине кабеля в 1,5 м требуется буферирование ПЛИС. Токовая нагрузка не превышает 24 мА(I0).

Дополнительным фактором при выборе ПЛИС Altera является наличие достаточно развитых бесплатных версий САПР. В табл. 2 приведены основные характеристики пакета MAX+PLUS II BASELINE ver. 9.3 фирмы Altera, который можно бесплатно “скачать” с сайта a.com/ или получить на CD Altera Digital Library, на котором содержится также и полный набор документации по архитектуре и применению ПЛИС[40].

Кроме того, ПЛИС фирмы Altera выпускаются с возможностью программирования в системе непосредственно на плате. Для программирования и загрузки конфигурации устройств опубликована схема загрузочного кабеля ByteBlaster и ByteBlasteMV. Следует отметить, что новые конфигурационные ПЗУ EPC2 позволяют программировать с помощью этого устройства, тем самым отпадает нужда в программаторе, что, естественно, снижает стоимость владения технологией. ПЛИС фирмы Altera выпускаются в коммерческом и индустриальном диапазоне температур.

Компания Xilinx Inc. (2100 Logic Drive, San Jose, CA 95124-3400, USA, x.com/) была основана в феврале 1984, её High-end продуктом являются ПЛИС семейства Virtex, основные характеристики которых представлены в табл. 3.

Таблица 2. Основные характеристики пакета MAX+PLUS II BASELINE ver. 9.3.

Таблица 3. Основные характеристики ПЛИС семейства Virtex фирмы XILINX

Архитектура семейства Virtex характеризуется широким разнообразием высокоскоростных трассировочных ресурсов, наличием выделенного блочного ОЗУ, развитой логикой ускоренного переноса. ПЛИС данной серии обеспечивают высокие скорости межкристального обмена — до 200 МГц (стандарт HSTL IV). Кристаллы серии Virtex за счёт развитой технологии производства и усовершенствованного процесса верификации имеют достаточно низкую стоимость (до 40% от эквивалентной стоимости серии XC4000XL). Помимо семейства Virtex, Xilinx выпускает FPGA семейств XC3000A, XC4000E, Spartan, XC5200, а также CPLD XC9500 и малопотребляющую серию CoolPLD. Существует бесплатная версия САПР — WebPACK, поддерживающая CPLD XC9500 и CoolPLD, ввод описания алгоритма с помощью языка описания аппаратуры VHDL.

Следует заметить, что Xilinx существенно обновил модельный ряд как своих ПЛИС, так и программного обеспечения, которое теперь разрабатывается с участием фирмы Synopsys. ПЛИС Xilinx выпускаются в коммерческом и индустриальном диапазоне температур с военной (Military) и космической (Space) приёмкой.

Компания Actel Corporation (955 East Arques Avenue, Sunnyvale, CA 94086-4533, USA, .com/) была основана в 1985 году. Особенностью ПЛИС Actel является применение так называемой Antifuse-технологии, представляющей собой создание металлизированной перемычки при программировании. Данная технология обеспечивает высокую надёжность и гибкие ресурсы трассировки, а также не требуется конфигурационное ПЗУ. По этой технологии выпускаются семейства ACT1, ACT2, 1200XL, а также новые семейства 54SX, А40МХ и А42МХ (со встроенными модулями памяти), имеющие хорошие показатели цена/логическая ёмкость (ПЛИС, заменяющая 300–350 корпусов ТТЛ, стоит 10$, при частоте > 250 МГц).

Данные ПЛИС являются хорошей альтернативой БМК при среднесерийном производстве.Новое семейство ProASIC фирмы Actel обладает ёмкостью до 500 000 эквивалентных логических вентилей. Его отличительной особенностью является энергонезависимость, благодаря применению FLASH-технологии, и наличие интегрированного на кристалле запоминающего устройства.

Для проектирования устройств на ПЛИС фирмой Actel бесплатно (до 31.01.2000) распространяется пакет Actel DeskTOP, содержащий средства ввода проекта, моделирования, генерации тестов разработки VeriBest и средства синтеза разработки Synplicity. Пожалуй, система проектирования Actel DeskTOP является наиболее мощным из всех бесплатных пакетов САПР ПЛИС.

К сожалению, микросхемы Actel, выпускаемые по Antifuse-технологии, требуют применения специального программатора, стоимость которого пока ещё весьма высока. Однако, их отличает высокая надёжность, поэтому они являются весьма перспективной базой для специальных применений. Так, ПЛИС серии RH1280 имеют следующие характеристики:

допустимая доза облучения 300000 РАД;

логическая ёмкость 16000 эквивалентных вентилей;

быстродействие до 135 МГц.

ПЛИС данного типа были применены в марсоходе в системе управления и обработки изображения цифровой видеокамеры робота-марсохода и в формирователе кадра для передачи информации на Землю. В настоящее время выпущены радиационно-стойкие ПЛИС новых семейств.

ПЛИС всех семейств Actel выпускаются в коммерческом и индустриальном диапазоне температур, а также с военной и космической приёмкой.

8.2. Система проектирования MAX+PLUS ALTERA

В предыдущем разделе были рассмотрены основные архитектуры ПЛИС и дана информация о фирмах-производителях. В этом разделе мы рассмотрим работу над проектом в среде системы MAX+PLUS II фирмы ALTERA. В предыдущем разделе данной главы были приведены основные характеристики свободно распространяемой через Internet версии MAX+PLUS II Baseline, в дальнейшем изложении мы будем ориентироваться преимущественно на неё.

Название системы MAX+PLUS II является аббревиатурой от Multiple Array MatriX Programmable Logic User System. Система MAX+PLUS II имеет средства удобного ввода проекта, компиляции и отладки, а также непосредственного программирования устройств.

Процедуру разработки нового проекта от концепции до завершения можно упрощённо представить следующим образом:

1.создание нового файла проекта или иерархической структуры нескольких файлов проекта с помощью любого сочетания редакторов в системе MAX+PLUS II, то есть графического, текстового и сигнального редакторов;

2.задание имени файла — проекта верхнего уровня в качестве имени проекта;

3.назначение семейства ПЛИС для проекта;

4.открытие окна компилятора Compiler и выбор кнопки Start для начала компиляции проекта. По желанию пользователя можно подключить модуль извлечения временных параметров проекта Timing SNF Extractor для создания файла, используемого при временном моделировании;

5. в случае успешной компиляции возможен временной анализ, для чего следует выполнить следующее: для проведения временного анализа задержек открыть окно Timing Analyzer, выбрать режим анализа и нажать кнопку Start; для проведения симуляции нужно сначала создать векторной тестовый вектор в файле канала тестирования (.scf), пользуясь сигнальным редактором, или в файле вектора (.vec), пользуясь текстовым редактором. Затем открыть окно отладчика Simulator и нажать кнопку Start;

6.открытие окна программатора Programmer с по-следующим выбором одного из двух способов: использование программатора MPU (Master Programming Unit) или подключение загрузочных устройств BitBlaster, Byte-Blaster или FLEX Download Cable к устройству, программируемому в системе;

7. выбор кнопки Program для программирования устройств с памятью типа EPROM или EEPROM либо выбор кнопки Configure для конфигурации устройства с памятью типа SRAM.

ПО системы MAX+PLUS II содержит 11 приложений и главную управляющую программу. Различны приложения, обеспечивающие создание проекта, могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. В это же время может работать одно из фоновых приложений, например, компилятор, симулятор, анализатор синхронизации и программатор. Одни и те же команды разных приложений работают одинаково, что облегчает задачу разработки логического дизайна.

Hierarchy Display

Обзор иерархии - отображает текущую инрархичнскую структуру файлов в виде дерева светвями, представляющими собой подпроекты

Graphic Editor

Графический редактор - позволяет разрабатывать схемный логический проект в формате реального отображения на экране WYSIWYG

Symbol Editor

Символьный редактор - позволяет редактировать существующие символы и создавать новые

Text Editor

Текстовый редактор - позволяет создавать и редактировать текстовые файлылогического дизайна, написанные на языках AHDL, VHDL, Verilog HDL

Waveform Editor

Сигнальный редактор - выполняет двойную функцию: инструмент для рахработки дизайна и инструмент для ввода тестовых векторов и наблюдения результатов тестирования

Floorplan Editor

Поуровневый планировщик - позволяет графическими средствами делать назначения контактам устройства и ресурсов логических элементов

Compiler

Компилятор - обрабатывает графические проекты

Simulator

Симулятор - позволяет тестировать логические операции и внутреннюю синхронизацию проектируемой логической цепи

Timing Analyzer

Временной анализатор - анализирует работу проектируемой логической цепи после того, как она была синтезирована и оптимизирована компилятором

Programmer

Программатор - позволяет программировать, конфигурировать, проводить верификацию и тестировать ПЛИС фирмы ALTERA

Message Processor

Генератор сообщений - выдает на экран сообщения об ошибках, предупреждающие и информационные сообщения

Перед тем как начать работать в системе MAX+PLUS II, следует понять разницу между файлами проекта, вспомогательными файлами и проектами.

Файл проекта — это графический, текстовый или сигнальный файл, созданный с помощью графического или сигнального редакторов системы MAX+PLUS II или в любом другом, использующем промышленные стандарты, схемном или текстовом редакторе либо при помощи программы netlist writer, имеющейся в пакетах, поддерживающих EDIF, VHDL и Verilog HDL. Этот файл содержит логику для проекта MAX+PLUS II и компилируется компилятором. Компилятор может автоматически обрабатывать следующие файлы проекта: графические файлы проекта (.gdf); текстовые файлы проекта на языке AHDL (.tdf); сигнальные файлы проекта (.wdf); файлы проекта на языке VHDL (.vhd); файлы проекта на языке Verilog (.v); схемные файлы OrCAD (.sch); входные файлы EDIF (edf); файлы формата Xilinx Netlist (.xnf); файлы проекта Altera (.adf); файлы цифрового автомата (.smf).

Вспомогательные файлы — это файлы, связанные с проектом MAX+PLUS II, но не являющиеся частью его иерархического дерева. Большинство таких файлов не содержит логики проекта. Некоторые из них создаются автоматически приложением системы MAX+PLUS II, другие — пользователем. Примерами вспомогательных файлов являются файлы назначений и конфигурации (.acf), символьные файлы (.sym), файлы отчета (.rpt) и файлы тестовых векторов (.vec).

Проект состоит из всех файлов иерархической структуры проекта, в том числе вспомогательных и выходных файлов. Именем проекта является имя файла проекта верхнего уровня без расширения. Система MAX+PLUS II выполняет компиляцию, тестирование, анализ синхронизации и программирование сразу целого проекта, хотя пользователь может в это время редактировать файлы этого проекта в рамках другого проекта. Для каждого проекта желательно создавать отдельный подкаталог в рабочем каталоге системы MAX+PLUS II.

В системе MAX+PLUS II легко доступны все инструменты для создания проекта. Разработка проекта ускоряется за счёт имеющихся стандартных функций, в том числе примитивов, мегафункций, библиотеки параметризованных модулей (LPM) и макрофункций устаревшего типа микросхем 74 серии. В системе MAX+PLUS II есть три редактора для разработки проекта: графический, текстовый и сигнальный, а также два вспомогательных редактора: поуровневый планировщик и символьный редактор.

В иерархической структуре проекта на любом уровне допускается смешанное использование файлов с расширениями “.gdf .tdf .vhd .v .edf .sch”. Однако файлы с расширением “.wdf .xnf .adf .smf ” должны быть либо на самом нижнем иерархическом уровне проекта, либо быть единственными.

Во всех приложениях MAX+PLUS II есть возможность с помощью команд из меню Assign вводить, редактировать и удалять типы назначений ресурсов, устройств и параметров, которые управляют компиляцией проекта. Пользователь может делать назначения для текущего проекта независимо от того, открыт ли какой-нибудь файл проекта или окно приложений. Доступны следующие типы назначений.

Clique assignment (Назначение клики) задаёт, какие логические функции должны оставаться вместе в одном и том же блоке логической структуры LAB, блоке ячеек памяти EAB, в одном ряду или устройстве.

Chip assignment (Назначение кристалла) задаёт, какие логические функции должны быть реализованы в одном и том же устройстве в случае разделения проекта на несколько устройств.

Pin assignment (Назначение контакта) назначает вход или выход одной логической функции конкретному контакту или нескольким контактам чипа.

Location assignment (Назначение ячейки) назначает единственную логическую функцию конкретной ячейке чипа.

Probe assignment (Назначение зонда) присваивает уникальное имя входу или выходу логической функции.

Connected pin assignment (Назначение соединенных контактов) задаёт внешнее соединение двух или более контактов на схеме пользователя.

Local routing assignment (Назначение местной разводки) присваивает коэффициент разветвления по выходу узла логическому элементу, находящемуся в том же блоке LAB, что и узел, или в соседнем LAB, прилежащем к узлу, с использованием общих местных разводок.

Device assignment (Назначение устройства) назначает тип ПЛИС, на которой реализуется проект.

Logic option assignment (Назначение логической опции) управляет логическим синтезом отдельных логических функций во время компиляции с применением стиля логического синтеза.

Timing assignment (Назначение временных параметров) управляет логическим синтезом и подгонкой отдельных логических функций для получения требуемых характеристик для времени задержки tPD (вход – неподрегистренный выход), tCO (синхросигнал – выход), tSU (синхросигнал – время установки), fMAX (частота син-хросигнала).

Можно определить глобальные опции устройства для компилятора, чтобы он использовал их для всех устройств при обработке проекта. Для резервирования дополнительных возможностей на будущее можно задать процентное соотношение контактов и логических элементов, которые должны оставаться неиспользованными во время текущей компиляции.

С использованием команды Global Project Para-meters можно задать имена и глобальные установки, которые будут использованы компилятором для параметров всех параметризованных функций в проекте.

При помощи команды Global Project Timing Require-ments можно ввести глобальные требования по синхронизации для поекта, задавая общие характеристики для времени задержки tPD (вход – нерегистрируемый выход), tCO (синхросигнал – выход), tSU (синхросигнал – время установки), fMAX (частота синхросигнала).

Команда Global Project Logic Synthesis позволяет сделать глобальные установки для компилятора в части логического синтеза проекта.

Все пять редакторов MAX PLUS II и три редактора создания дизайна (графический, текстовый и сигнальный) имеют общие функции, такие как, например, создание, сохранение и открытие файла. Кроме того, приложения редактора MAX PLUS II имеют следующие общие функции: создание файлов символов и файлов с прототипами функций (Include-файлы); поиск узлов; траверз иерархического дерева; всплывающие окна меню, зависящего от контекста; временной анализ; поиск и замена фрагментов текста; отмена последнего шага редактирования, его возвращения, вырезка, копирование, вставка и удаление выбранных фрагментов, обмен фрагментами между приложениями MAX PLUS II или приложениями Windows; печать.

Графический редактор (Graphic Editor) обеспечивает проектирование в реальном формате изображения (WYSIWIG). Графические файлы проекта (.gdf) или схемные файлы OrCAD (.sch), созданные в данном графиче-ском редакторе, могут включать любую комбинацию символов примитивов, мегафункций и макрофункций. Символы могут представлять собой любой тип файла проекта (.gdf .sch .tdf .vhd .v .wdf .edf .xnf .adf .smf).

Инструмент выбора (“стрелка”) облегчает разработку дизайна. Он позволяет двигать и копировать объекты, а также вводить новые символы. Когда вы помещаете его на контакт или конец линии, он автоматически преобразуется в инструмент рисования ортогональных линий. Если им щелкнуть на тексте, он автоматически преобразуется в инструмент редактирования текста.

Графический редактор обеспечивает ряд других возможностей. Например, можно увеличивать или уменьшать масштаб отображения на экране, выбирать гарнитуру и размер шрифта, задавать стили линий, устанавливать и отображать направляющие, получать зеркальное отображение, поворачивать выделенные фрагменты на 90, 180 или 270 градусов; задавать размер и ориентацию текущего листа схемы.

Символьный редактор (Symbol Editor) позволяет просматривать, создавать и редактировать символ.

Символьный файл имеет то же имя, что и проект, и расширение “.sym”. Команда Creat Default Symbol меню File, которая есть в графическом, текстовом и сигнальном редакторах, создает символ для любого файла проекта. Символьный редактор обладает следующими характеристиками: можно переопределить символ, представляющий файл проекта, создавать и редактировать выводы и их имена, используя входные, выходные и двунаправленные выводы, а также задавать варианты ввода символа в файл графического редактора, задать значения параметров и их значения по умолчанию; сетка и направляющие помогают выполнить точное выравнивание объектов, в символе можно вводить комментарии.

Текстовый редактор (Text Editor) является инструментом для создания текстовых файлов проекта на языках описания аппаратуры: AHDL (.tdf), VHDL (.vhd), Verilog HDL (.v). В этом текстовом редакторе можно работать также с произвольным файлом формата ASCII. Все перечисленные файлы проекта можно создавать в любом текстовом редакторе, однако данный редактор имеет встроенные возможности ввода файлов проекта, их компиляции и отладки с выдачей сообщений об ошибках и их локализацией в исходном тексте или в тексте вспомогательных файлов; кроме того, существуют шаблоны языковых конструкций для AHDL, VHDL и Verilog HDL, выполнено окрашивание синтаксических конструкций. В данном редакторе можно вручную редактировать файлы назначений и конфигурации (.acf), а также делать установки конфигурации для компилятора, симулятора и временного анализатора. Пользуясь данным текстовым редактором, можно создавать тестовые векторы (.vec), используемые для тестирования, отладки функций и при вводе сигнального проекта. Можно также создавать командные файлы (.cmd — для симулятора и .edc — для EDIF), а также макробиблиотеки (.lmf).

В текстовом редакторе MAX PLUS II обеспечивается контекстная справка. Сигнальный редактор (Waveform Editor) служит инструментом создания описания проекта, ввода тестовых векторов и просмотра результатов тестирования. Пользователь может создавать сигнальные файлы проекта (.wdf), которые содержат временные диаграммы, описывающие логику работы проекта, а также файлы каналов тестирования (.scf), которые содержат входные вектора для тестирования и функциональной отладки. Разработка описания проекта в сигнальном редакторе является альтернативой его созданию в графическом или текстовом редакторах. Здесь можно графическим способом задавать комбинации входных логических уровней и требуемых выходов. Созданный таким образом файл WDF может содержать как логические входы, так и входы цифрового автомата, а также выходы комбинаторной логики, счётчиков и цифровых автоматов. Способ разработки дизайна в сигнальном редакторе лучше подходит для цепей с чётко определёнными последовательными входами и выходами, то есть для цифровых автоматов, счётчиков и регистров. С помощью сигнального редактора можно легко преобразовывать временные диаграммы сигналов целиком или частично, создавая и редактируя узлы и группы. Простыми командами можно создавать файл таблицы ASCII-символов (.tbl) или импортировать файл тестовых векторов в формате ASCII (.vec) для создания файлов тестируемых каналов SCF и сигнального дизайна WDF. Можно также сохранить файл WDF как SCF для проведения тестирования или преобразовать SCF в WDF для использования его в качестве файла проекта. Сигнальный редактор имеет следующие отличительные черты: можно создать или отредактировать узел, задав его тип; при разработке WDF можно задать тип логики узла, задать значения по умолчанию в логическом узле, а также имя состояния по умолчанию в узле типа цифрового автомата, для упрощения создания тестового вектора можно легко добавить в файл тестируемых каналов SCF несколько узлов или все из информационного файла симулятора (.snf), существующего для полностью откомпилированного проекта, можно объединять от 2 до 256 узлов для создания новой группы (шины) или разгруппировывать объединённые ранее в группу узлы. Можно также объединять группы с другими группами. Значение группы может быть отображено в двоичной, десятичной, шестнадцатеричной или восьмеричной системе счисления с преобразованием или без в код Грэя, можно копировать, вставлять, перемещать или удалять выбранную часть (“интервал”) сигнала, а также весь узел или группу. Можно также инвертировать, вставлять, переписывать, повторять, расширять или сжимать интервал сигнала любой длины с любым логическим уровнем, тактовым сигналом, последовательностью счёта или именем состояния, задать сетку для выравнивания переходов между логическими уровнями, в любом месте файла можно вводить комментарии между сигналами, менять масштаб отображения.

Для облегчения тестирования можно сделать наложение любых выходов в текущем файле или наложить второй файл сигнального редактора для сравнения сигналов его узлов и групп с соответствующими сигналами текущего файла.

Поуровневый планировщик (Floorplan Editor) предназначен для назначения ресурсов физических устройств и просмотра результатов разводки, сделанных компилятором. В окне поуровневого планировщика могут быть представлены два типа изображения:

Device View (Вид устройства) показывает все контакты устройства и их функции;

LAB View (Вид логического структурного блока) показывает внутреннюю часть устройства, в том числе все логические структурные блоки (LAB) и отдельные логические элементы.

После выполнения всех назначений и задания проекта приступают к его компиляции. Сначала компилятор извлекает информацию об иерархических связях между файлами проекта и проверяет проект на простые ошибки ввода описания проекта.

Компилятор применяет разнообразные способы увеличения эффективности проекта и минимизации использования ресурсов устройства. Если проект слишком большой, чтобы быть реализованным в одном устройстве, компилятор может автоматически разбить его на части для реализации в нескольких устройствах того же самого семейства, при этом число соединений между устройствами минимизируется. В файле отчёта (.rpt) затем будет отражено, как проект будет реализован в одном или нескольких устройствах.

Кроме того, компилятор создает программирующие файлы, используемые программатором для программирования одного или нескольких устройств. У разработчика также есть возможность настроить обработку проекта. Например, можно задать стиль логического синтеза проекта по умолчанию и другие параметры логического синтеза в рамках всего проекта, что позволит провести логический синтез в соответствии с вашими потребностями. Кроме того, вы можете ввести требования по синхронизации в рамках всего проекта, точно задать разбиение большого проекта на части для реализации в нескольких устройствах и выбрать варианты параметров устройств, которые будут применены для всего проекта в целом. Загрузку готового проекта в ПЛИС или конфигурационное ПЗУ выполняют с помощью программатора (Programmer).

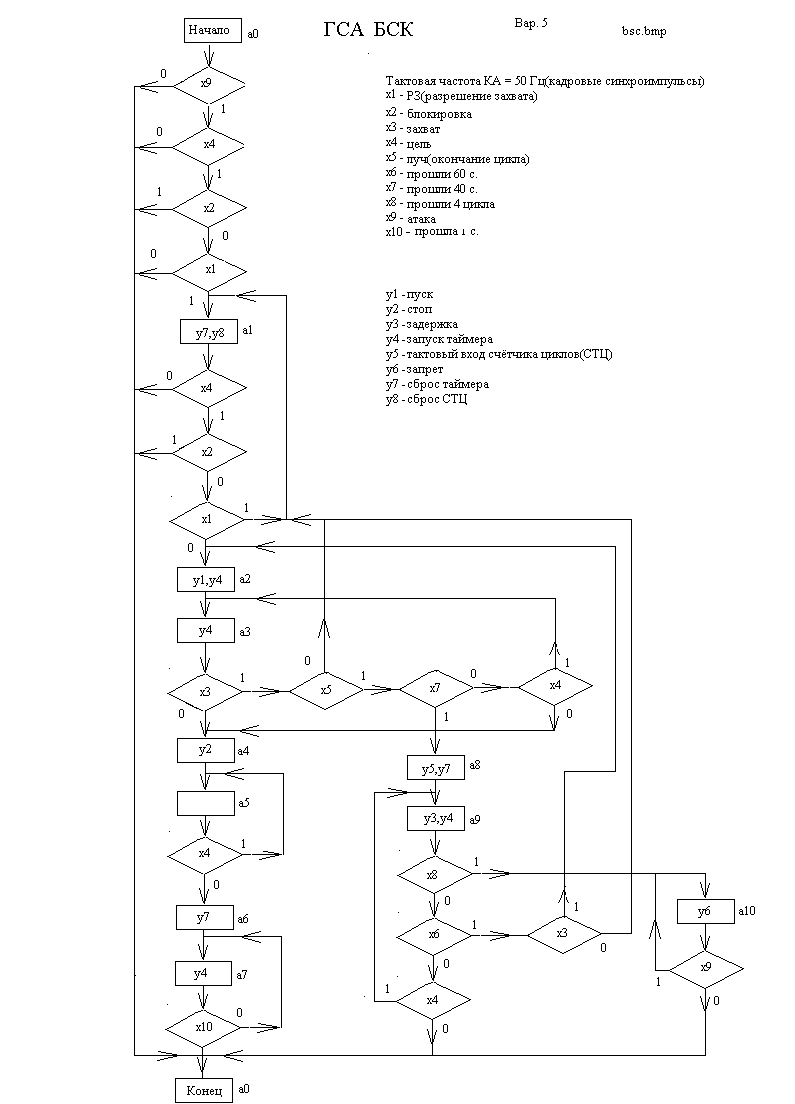

Ниже приводится пример текстового файла для проекирования МПА,представленного на ГСА.

TITLE "Блок связи и команд";

INCLUDE "tm1";

INCLUDE "tm2";

INCLUDE "ctc";

INCLUDE "dff";

SUBDESIGN bsc

(

f50,reset,z1,z2,z3,z4,z5,z7,z9: INPUT;

y1,y2,y3,y6,q[3..0] : OUTPUT;

y4,y5,y7,y8 : output;

)

VARIABLE

mtm1 : tm1;

mtm2 : tm2;

mctc : ctc;

rg[3..0] : DFF;

z6,z8,z10,d[3..0] : NODE;

BEGIN

rg[].clk = f50;

rg[].clrn = reset;

rg[].d = d[];

q[] = rg[].q;

mtm1.clk = f50 & y4;

mtm1.reset = !y7;

mtm2.clk = mtm1.ct5;

mtm2.reset = !y7;

z10 = mtm2.ct0;

z6 = mtm2.ct6;

mctc.clk = y5;

mctc.reset = !y8;

z8 = mctc.ct2;

table

q[3..0],z10,z9,z8,z7,z6,z5,z4,z3,z2,z1 => d[3..0];

0 , x , 0, x, x, x, x, x, x, x, x => 0;

1 , x , x, x, x, x, x, x, x, 1, x => 0;

12 , x , 0, x, x, x, x, x, x, x, x => 0;

15 , x , x, x, x, x, x, x, x, x, x => 0;

0 , x , 1, x, x, x, x, x, x, x, x => 1;

1 , x , x, x, x, x, x, 0, x, 0, x => 1;

14 , x , x, 0, x, x, x, 1, x, x, x => 1;

1 , x , x, x, x, x, x, 1, x, 0, x => 2;

2 , x , x, x, x, x, x, 1, x, x, 1 => 2;

9 , x , x, x, 0, x, x, x, x, x, x => 2;

11 , x , x, 0, x, 1, x, x, 0, x, 1 => 2;

2 , x , x, x, x, x, x, 1, x, x, 0 => 3;

7 , x , x, x, x, x, x, x, x, x, 0 => 3;

8 , 1 , x, x, x, x, x, x, x, x, x => 3;

11 , x , x, 0, x, 1, x, x, 1, x, x => 3;

11 , x , x, 0, x, 1, x, x, 0, x, 0 => 3;

3 , x , x, x, x, x, x, x, x, x, x => 4;

4 , x , x, x, 0, x, 1, x, 1, x, x => 4;

4 , x , x, x, x, x, x, x, 0, x, x => 5;

5 , x , x, x, x, x, x, x, x, x, x => 6;

6 , 0 , x, x, x, x, x, x, x, x, 1 => 6;

6 , 1 , x, x, x, x, x, x, x, x, x => 7;

7 , x , x, x, x, x, x, x, x, x, 1 => 7;

6 , 0 , x, x, x, x, x, x, x, x, 0 => 8;

8 , 0 , x, x, x, x, x, x, x, x, x => 8;

4 , x , x, x, 1, x, 1, x, 1, x, x => 9;

9 , x , x, x, 1, x, x, x, x, x, x => 9;

4 , x , x, x, x, x, 0, x, 1, x, x => 10;

10 , x , x, x, x, x, x, x, x, x, x => 11;

11 , x , x, 0, x, 0, x, x, x, x, x => 11;

11 , x , x, 1, x, x, x, x, x, x, x => 12;

12 , x , 1, x, x, x, x, x, x, x, x => 12;

14 , x , x, 1, x, x, x, 1, x, x, x => 12;

2 , x , x, x, x, x, x, 0, x, x, x => 13;

13 , x , x, x, x, x, x, x, x, x, x => 14;

14 , x , x, x, x, x, x, 0, x, x, x => 14;

end table;

table

q[3..0]=> y1,y2,y3,y4,y5,y6,y7,y8;

0 => 0, 0, 0, 0, 0, 0, 0, 0;

1 => 0, 0, 0, 0, 0, 0, 1, 1;

2 => 0, 0, 0, 0, 0, 0, 1, 1;

3 => 1, 0, 0, 0, 0, 0, 1, 0;

4 => 0, 0, 0, 0, 0, 0, 0, 0;

5 => 0, 1, 0, 0, 0, 0, 1, 0;

6 => 0, 0, 0, 1, 0, 0, 0, 0;

7 => 0, 0, 0, 0, 0, 0, 0, 0;

8 => 0, 0, 0, 1, 0, 0, 0, 0;

9 => 0, 0, 1, 0, 0, 0, 0, 0;

10 => 0, 0, 0, 0, 1, 0, 1, 0;

11 => 0, 0, 0, 1, 0, 0, 0, 0;

12 => 0, 0, 0, 0, 0, 1, 0, 0;

13 => 0, 0, 0, 0, 1, 0, 0, 0;

14 => 0, 0, 0, 0, 0, 0, 0, 0;

15 => 0, 0, 0, 0, 0, 0, 0, 0;

end table;

end;

На копии экрана симулятора представлены временные диаграммы работы МПА БСК.

8.3. Общая характеристика СБИС, выпускаемых фирмой ALTERA

СБИС программируемой логики (СБИС ПЛ) - цифровые СБИС высокой степени интеграции, имеющие программируемую пользователем внутреннюю структуру и предназначенные для реализации сложных цифровых устройств. Использование СБИС ПЛ и соответствующих средств автоматизации проектирования позволяет в сжатые сроки создавать конкурентноспособные устройства и системы, удовлетворяющие жестким требованиям по производительности, энергопотреблению, надежности, массо-габаритным параметрам, стоимости.

Одним из общепризнанных мировых лидеров в области производства СБИС ПЛ являетсяамериканская фирма ALTERA. Оптимальное сочетание таких параметров как быстродействие, потребление энергии, степень интеграции, стоимость делает СБИС ПЛ фирмы ALTERA идеальным средством для построения плат расширения ПЭВМ, систем управления и телекоммуникации, устройств цифровой обработки сигналов для стационарных и мобильных систем связи.

В настоящее время фирма ALTERA выпускает семь семейств СБИС ПЛ. Основные характеристики наиболее популярных из них приведены в таблице.

1) единица измерения - число эквивалентных логических вентилей (вентилей типа 2И-НЕ);

2) при использовании внутренней памяти доступные пользователю логические ресурсы СБИС не уменьшаются.

Семейство MAX (Multiple Array matriX) 7000 объединяет семь серий СБИС. СБИС этого семейства позволяют заменить устройство, содержащее до сотни корпусов микросхем средней степени интеграции, и обеспечивают: задержку распространения сигнала от любого входа до выхода СБИС не более 5 нс; устойчивую работу на частотах до 151 МГц; возможность регулирования скорости переключения выходных буферов; возможность использования четырех режимов работы выходных буферов: вход, выход, двунаправленный, открытый коллектор; возможность задания режима пониженного энергопотребления (Turbo-off) как для всей СБИС в целом, так и для цепей распространения отдельных сигналов; возможность программирования и репрограммирования после распайки на плате; возможность задания режима секретности разработки (Design Security); работу с пониженным (3.3 В) напряжением питания. СБИС ряда серий семейства MAX 7000 соответствуют требованиям стандарта шины PCI.

Семейство FLEX (Flexible Logic Element matriX) 8000A объединяет шесть серий СБИС. СБИС этого семейства позволяют заменить устройство, занимающее десятки плат, выполненных на микросхемах средней степени интеграции, и обеспечивают возможность: устойчивой работы на частотах до 294 МГц; эмуляции внутренней шины с тремя состояниями; работы с пониженным напряжением питания (3.3 В); работы в системах со смешанным напряжением питания (3.3 В, 5.0В); реализации неограниченного числа циклов реконфигурирования, в том числе "на лету", т.е. без выключения питания СБИС; регулирования скорости переключения выходных буферов; использования трех режимов работы выходных буферов: вход, выход, двунаправленный. Все СБИС этого семейства совместимы со стандартом шины PCI.

Семейство MAX (Multiple Array matriX) 9000 объединяет четыре серии микросхем. СБИС этого семейства позволяют заменить устройство, занимающее десятки плат, выполненных на микросхемах средней степени интеграции, и обеспечивают возможность: устойчивой работы на частотах до 117 МГц; независимого использования логической части и триггера макроячейки; задания режима пониженного энергопотребления (power-saving mode) как для всей СБИС в целом, так и для цепей распространения отдельных сигналов; программирования и репрограммирования после распайки на плате; работы в системах со смешанным напряжением питания (3.3 В, 5.0В); регулирования скорости переключения выходных буферов; использования трех режимов работы выходных буферов: вход, выход, двунаправленный. СБИС ряда серий семейства MAX 9000 совместимы со стандартом шины PCI.

Семейство FLEX (Flexible Logic Element matriX) 10K объединяет семь серий СБИС. СБИС этого семейства позволяют заменить устройство, занимающее сотни плат, выполненных на микросхемах средней степени интеграции, и обеспечивают возможность: устойчивой работы на частотах до 450 Мгц; реализации на кристалле статической памяти и ПЗУ объемом до 24 Кбит; независимого использования логической части и триггера каждого логического элемента; эмуляции внутренней шины с тремя состояниями; умножения внутренней тактовой частоты; работы в системах со смешанным напряжением питания (3.3 В, 5.0В); реализации неограниченного числа циклов репрограммирования, в том числе "на лету", т.е. без выключения питания СБИС; регулирования скорости переключения выходных буферов; использования четырех режимов работы выходных буферов: вход, выход, двунаправленный, открытый коллектор. Все СБИС этого семейства совместимы со стандартом шины PCI.

Основными тенденциями развития выпускаемых фирмой Altera семейств СБИС ПЛ являются: увеличение степени интеграции; повышение гибкости в использовании внутренних ресурсов; уменьшение энергопотребления в расчете на эквивалентный логический вентиль; повышение быстродействия. Кроме того, еще одной, немаловажной, тенденцией является непрерывное снижение стоимости СБИС.

СБИС семейств FLEX10K и FLEX8000

СБИС данных семейств имеют в целом сходную внутреннюю архитектуру в основе которой лежит логический элемент (ЛЭ). ЛЭ содержит четырехвходовую таблицу перекодировок (ПЗУ), обеспечивающую реализацию логических функций, синхронный триггер и некоторую дополнительную логику. ЛЭ объединяются в группы - логические блоки (каждый из блоков содержит восемь ЛЭ). Внутри логических блоков ЛЭ соединяются посредством локальной программируемой матрицы соединений, позволяющей соединять любой ЛЭ с любым. Логические блоки связаны между собой и с элементами ввода-вывода посредством глобальной программируемой матрицы соединений. Локальная и глобальная матрицы соединений имеют непрерывную структуру - для каждого соединения выделяется единый, непрерывный в рамках СБИС (либо логического блока) канал. Двухуровневая архитектура и использование непрерывной структуры соединений на каждом уровне иерархии обеспечивают: высокое быстродействие реализуемых устройств; возможность точного предсказания задержки распространения сигналов; высокую скорость автоматической разводки СБИС; возможность размещения выводов СБИС в соответствии с требованиями разработчика. Каждый элемент ввода-вывода содержит: триггер, позволяющий реализовать временное хранение принимаемого и передаваемого бита данных; буфер, работающий в режимах: ввод, вывод, двунаправленный, выход с открытым коллектором (FLEX 10K) и обеспечивающий возможность управления его скоростью переключения. Отличительной особенностью семейства FLEX 10K является наличие модулей памяти общей емкостью до 24 кбит, использование которой не ведет к уменьшению доступных разработчику логических ресурсов (логических элементов). Основные характеристики СБИС указанных семейств приведены в таблице 1 и таблице 2.

Таблица 1. СБИС FLEX10K

- е

диница измерения - число эквивалентных логических вентилей (вентилей типа 2И-НЕ);

2) тестирование проводилось для СБИС с градацией быстродействия -3.

Таблица 2. СБИС FLEX8000A

1) единица измерения - число эквивалентных логических вентилей (вентилей типа 2И- НЕ);

2) тестирование проводилось для СБИС с градацией быстродействия -2.

8.4. Сравнительные стоимости ПЛИС фирм Xilinx и ALTERA

Фирма ALTERA производит микросхемы программируемой логики, средства проектирования и программирования для них и занимает первое место в мире по объему продаж СБИС ПЛ, охватывая свыше 30 процентов рынка, немного опережает своего основного конкурента Ц фирму Xilinx. Используя СБИС ПЛ и САПР фирмы ALTERA Вы можете: реализовать цифровую часть проекта любой сложности на одном кристалле; сократить время проектирования, полностью исключив этап макетирования и начав разработку печатной платы одновременно с разработкой СБИС ПЛ; вносить изменения на любой стадии проектирования или в законченный проект без переразводки печатной платы; обеспечить работу системы с тактовыми частотами свыше 250 МГц; ускорить и упростить процесс проектирования цифрового устройства, используя настраиваемые библиотечные модули типовых функциональных узлов; вводить проект в схемном виде или используя текстовое описание, использовать возможности других средств САПР; уменьшить стоимость разработки.

Для проектирования цифровых устройств фирма ALTERA предлагает САПР с различными функциональными возможностями. Полнофункциональный САПР BASELINE предлагается бесплатно. Установив его сприлагаемого к письму компакт диска "Altera Digital Library" и зарегистрировавшись на www.altera.com Вы становитесь пользователем лицензионного программного продукта, который позволяет: использовать СБИС ПЛ логической емкостью до 16 тысяч эквивалентных логических вентилей; осуществлять графический (схемный) ввод, текстовый ввод на языке AHDL; использовать в качестве входных файлы формата EDIF и формата .sch (Orcad); использовать широкий набор готовых функциональных устройств, настраиваемых пользователем (умножающие и делительные устройства, FIFO и т.д.); проводить временной анализ задержек сигналов и тактовых частот; выполнять функциональное и временное моделирование на тестах, заданных в виде временных диаграмм, что обеспечивает достоверность результатов проектирования; с помощью программатора или устройств BITBLASTER и BYTEBLASTER программировать СБИС ПЛ, в том числе программировать и перепрограммировать микросхемы прямо на плате используя технологический разъем. В таблице 1 приведены данные по типовым системам разработки цифровых устройств (для РС) и простейшим средствам программирования СБИС ПЛ фирм Xilinx и ALTERA. Выпускаемые фирмой ALTERA СБИС ПЛ имеют логическую емкость от 600 до 1 000 000 эквивалентных логических вентилей и обеспечивают самое высокое быстродействие среди микросхем данного класса и низкое энергопотребление. С номенклатурой СБИС ПЛ и их техническими характеристиками Вы познакомитесь в "Altera Digital Library".

В таблице 2 проведено сравнение близких по логической емкости СБИС ПЛ фирм Xilinx и ALTERA, упакованных в близкие по числу выводов корпуса и имеющих низшее быстродействие в своем классе.

Анализ данных в Табл. 1 и Табл. 2 показывает: для работы с проектами цифровых устройств сложностью до ~50 микросхем серии 74 ALTERA предоставляет бесплатно полнофункциональные средства проектирования и возможность простой реализации средств программирования СБИС ПЛ; цена СБИС ПЛ фирмы ALTERA по большинству позиций существенно ниже сопоставимых по техническим характеристикам СБИС ПЛ фирмы Xilinx.

Таблица 1: Основные системы разработки цифровых устройств и средства программирования СБИС ПЛ фирм Xilinx и ALTERA

Примечание: * Все цены в таблицах приведены с учетом НДС по состоянию на июнь 1999 г.

Таблица 2: С

равнительные стоимости сопоставимых по техническим характеристикам СБИС программируемой логики фирм Xilinx и ALTERA.

П

римечания:* В одном конфигурируемом логическом блоке (CLB) СБИС ПЛ семейства XC4000 содержится две LC (четырехвходовая таблица перекодировки и триггер), в CLB семейства Virtex Ц четыре LC; ** В СБИС ПЛ семейства XC4000 память использует ресурс LC, выделенные блоки памяти отсутствуют.

8.5. РЕКОМЕНДАЦИИ ПО ПРИМЕНЕНИЮ ПЛИС

Безусловно, самым эффективным решением проблем проектирования микроконтроллеров является их микропроцессорная реализация. Резкое расширение номенклатуры БИС семейства 80С51, появление дешёвых микро-ЭВМ PIC и широкий ассортимент микроконтроллеров вообще, и в частности имеющих системы команд на языках высокого уровня, делает архаичным использование ПЛИС. Однако, применение микро-ЭВМ имеет ряд ограничений. Прежде всего, это связано со сбоями. Предусмотреть все последствия сбоев в программе, насчитывающей десятки килобайт, практически невозможно. Решает проблему применение диагностических процессоров. Однако отсутствие финансирования не позволит создать БИС диагностического процессора в ближайшие годы. Кроме того, необходимо проведение сложных мероприятий по помехозащите. Решающим фактором в пользу применения ПЛИС может явиться высокое быстродействие. Но в последнее время этот параметр утратил своё значение, поскольку созданы МЭВМ высокой производительности.

Следовательно, ПЛИС следует применять тогда, когда алгоритм работы МКУ относительно прост(менее 2 кбайт в программном эквиваленте), не решены проблемы помехозащиты и требуется надёжная бессбойная работа микроконтроллера.

«Читай и слушай для собственного развлечения рассказы о хитроумных системах, вникай в интересные вопросы, поставленные там со всей изощрённостью, какой только может наделить их пылкая фантазия, но смотри на всё это только как на упражнения для ума и возвращайся каждый раз к согласию со здравым смыслом...»

(Честерфилд «Письма к сыну»)