Удк 001(06) Инновационные проекты

| Вид материала | Документы |

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 33.84kb.

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 24.41kb.

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 57.81kb.

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 131.54kb.

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 137.31kb.

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 31.02kb.

- Удк 001(06) Инновационные проекты, студенческие идеи, проекты, предложения, 69.92kb.

- Удк 001(06) Инновационные проекты, 23.67kb.

- Инновационные программы и проекты в области социального неблагополучия семьи и детей,, 120.85kb.

- Программа: «Инновационная деятельность высшей школы» Подпрограмма: «Инновационные научно-технические, 220.34kb.

УДК 001(06) Инновационные проекты. Студенческие идеи, проекты, предложения

А.В. МИХЕЕВ

Научный руководитель – Ю.А. ПОПОВ, д.т.н., профессор

Московский инженерно-физический институт (государственный университет)

РАЗРАБОТКА УСТРОЙСТВА КОНТРОЛЯ

УНИТАРНОГО КОДА “ОДИН ИЗ ЧЕТЫРЕХ”

Для уменьшения потерь от порождаемых неисправностями ЭВМ ошибок надо контролировать достоверность (безошибочность) работы машины и предотвращать распространение ошибки в вычислительном процессе, так как в противном случае существенно усложняются и удлиняются процедуры проверки правильности работы программы, определения и устранения искажений в программе, данных и промежуточных результатах. С этой целью ЭВМ снабжают системой автоматического контроля правильности работы машины, которая при появлении ошибки немедленно приостанавливает вычисления и инициирует работу средств автоматического восстановления вычислительного процесса, а при необходимости и средств автоматического диагностирования, локализующих неисправность.

Основными способами контроля комбинационных схем являются контроль путем дублирования, проверки выходных сигналов и с помощью образования контрольных бит.

Наличие системы автоматического контроля способствует увеличению готовности и обслуживаемости ЭВМ.

Для генерирования кода 1 из 4-х используется дешифратор на два входа (комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах).

Данную комбинационную схему можно проконтролировать по выходным сигналам.

Разработка устройства контроля проходит в несколько взаимосвязанных этапов:

1. Словесное описание разрабатываемого устройства (что должно делать).

2. На основе словесного описания составляем таблицу истинности для разрабатываемого устройства.

3. На основе таблицы истинности выписываем СДНФ или СКНФ соответствующих булевых функций.

4. Анализируем полученную функцию на минимальную форму (тупиковую). Если нужно минимизируем функцию, приводя к минимальной форме.

5. Выбирается базис на основе полученной минимальной формы функции и на этом базисе реализуется схема устройства.

Устройство контроля кода 1 из 4-х должно тестировать шины следующим образом. Если на всех шинах логические нули, единицы или более одной единицы, то устройство контроля выдает сообщение об ошибке. В качестве устройства получения кода 1 из 4-х используется двухвходовой дешифратор.

С

Таблица 2

оставим таблицу истинности (табл. 1) для четырех выходов дешифратора. Позволим себе некоторый произвол, а именно, в качестве сигнала ошибки на выходе устройства тестирования принимаем логическую “1”. Четыре выхода предполагают 16-ть комбинаций логических сигналов. При этом ошибка возникает всякий раз, когда в комбинации больше одной единицы или все нули, единицы.

Таблица 1.

| N | 3 | 2 | 1 | 0 | A |

| 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 |

| 10 | 1 | 0 | 1 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 1 |

| 13 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 |

Надо учесть еще комбинации, когда на выходе дешифратора появляется унитарный код, но он не соответствует двоичному коду на входе дешифратора (на входе код “00”, на выходе 0010 -“1” не на нулевом, а на первом выходе).

Чтобы это учесть (защита от двойного сбоя) к каждой из четырехразрядной комбинации сигналов, соответствующих одной единице на выходе дешифратора, добавляем два разряда. Эти разряды соответствуют четырем комбинациям на входе дешифратора. При этом жестко закрепляем, какие двоичные разряды, к каким тетрадам добавляются (код входа с соответствующим ему кодом выхода).

| Код входа 00 01 10 11 | Склейка + + + + | Код выхода 0001 0010 0100 1000 | Результат 000001 010010 100100 111000 |

Выбор в качестве сигнала ошибки логической единицы позволяет представить функцию в виде СКНФ, а не СДНФ. Это дает выигрыш в числе инверсий. Например, если код 000001 в СДНФ это

, то в СКНФ этот код имеет вид

, то в СКНФ этот код имеет вид  - очевиден выигрыш. В свою очередь это позволяет сократить объем оборудования для аппаратной реализации функции. Уменьшение числа инверторов в два раза.

- очевиден выигрыш. В свою очередь это позволяет сократить объем оборудования для аппаратной реализации функции. Уменьшение числа инверторов в два раза.Из таблицы истинности видно, что комбинационная схема функционирует нормально на четырех наборах (0001, 0010, 0100, 1000), что соответствует значению логического “0” на выходе “А” устройства контроля.

Представляем функцию в виде СКНФ для выхода “А” с учетом входных кодов:

Данная функция одновременно и тупиковая.

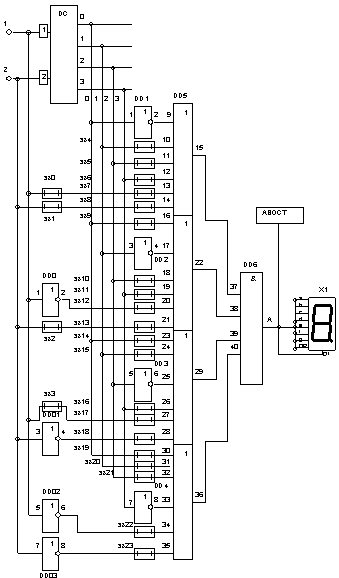

Для реализации функции используем базис NOT, OR, AND (восемь логических элемента NOT, четыре 6OR и один логический элемент 4AND). Соединяем элементы в соответствии с СКНФ. Полученная схема (рис. 1) является устройством контроля унитарного кода 1 из 4-х для одного двухвходового дешифратора или УКУК.

Для отображения сообщения об ошибки используется буквенная индикация. Сигнал ошибки высвечивается на дисплее семисегментного индикатора в виде буквы “Е.” (Error). Индикатор непосредственно подключается к выходу “А” устройства тестирования. Кроме индикации предусмотрен сигнал на “АВОСТ” (система автоматической остановки процесса).

Рис. 1.

Принцип работы семисегментного индикатора на два разряда показан на рис.2. Один из вариантов данных индикаторов – индикаторы с дисплеями на светодиодах. Они ведут себя как обычные диоды, но прямое напряжение для них составляет от 1,5 до 2,5 вольта.

Рис. 2.

Когда светодиод открыт (подача сигнала на ножки A, D, E, F, G, DP и d1- выбор корпуса (активация нужного разряда)), через него протекает ток, он излучает свет. Для получения яркости свечения обычно требуется ток от 5 до 20 мА. Диоды не перегорают и бывают трех цветов (красный, желтый, зеленый).

Для создания устройства контроля может быть применена как ТТЛ (ТТЛШ), так и КМОП (КМДП) – технология. Это зависит от предъявляемых к устройству в конкретной ситуации требований.

Логические уровни ТТЛ (ТТЛШ) и КМОП схем.

| Тип микросхемы | Напряжение питания, В | Логические уровни, В | |

| высокий (1) | низкий (0) | ||

| ТТЛ(ТТЛШ) | 5±10% В | 2,4 | 0,4 |

| КМОП | 5 10 15 | 2,5 5 7,5 | 0 0 0 |

Рассмотрим основные этапы работы схемы.

Пусть на входах дешифратора (DC) 1 и 2 появился двоичный код. Этот код поступает на DC и на первый слой УКУК (слой из инверторов DD0-DD03 и элементов задержки (ЭЗ0-ЭЗ3)). После срабатывания DC на его выходах 0-3 образуется некий код, который по шинам 0-3 поступает одновременно с сигналами со слоя один на слой два УКУК, состоящий из тех же элементов что и первый. После срабатывания второго слоя информация в виде набора сигналов низкого и высоко уровней поступает на слой три, который состоит из 4-х логических элементов 4OR, выполняющих операцию логического сложения. После отработки слоя два на его выходах образуется код виде тетрады. Данный код поступает на пятый слой (логический элемент 4AND) на котором выполняется операция логического умножения. На выходе элемента 4AND или “A” формируется сигнал высокого или низкого уровня, который поступает на индикатор Х1 (ножки A, D-G, DP и D1) и “АВОСТ”. Если схема DC работает нормально или нет еще каких-либо нештатных ситуаций (на выходах DC – унитарный код, соответствующий входной информации), то индикатор Х1 и “АВОСТ” неактивны. Если наоборот, на выходе “A” высокий уровень, который активирует индикатор Х1 (загорается буква “E.” - Error) и “АВОСТ”.

Для тестирования четырех одновременно работающих дешифраторов на два входа можно использовать четыре совместно реализованных на одной подложке представленных выше устройств контроля. У данного устройства будет возможность сигнализировать об ошибке на конкретной шине путем активации только одного разряда индикатора.

Рис. 3.

Кроме этого предусмотрено четыре сигнала на АВОСТ, чтобы отключать только неисправный дешифратор. Схема варианта подключения микросхемы УКУК к четырем дешифраторам представлена на рис. 3.

Список литературы

1. Савельев А.Я. Прикладная теория цифровых автоматов: Учеб. Для вузов по спец. ЭВМ. М.: Высш. шк. 1987. 272 с. ил.

2. Шахнов В.А. Микропроцессоры. В 5-ти кн.: Учеб. Пособие для СПТУ. /Кн. 1. Комплекты интегральных микросхем. М.: Высш. шк., 1988. 175 с. ил.

3. Коган Б.М., Мкртумян И.Б. Основы эксплуатации ЭВМ: Учеб. пособие для вузов. / Под ред. Б.М. Кагана. 2-е изд., перераб. и доп. М.: Энергоатомиздат, 1988. 432 с. ил.

4. Мукосеев В.В., Сидоров И.Н. Маркировка и обозначение радиоэлементов. Система цветовой и буквенно-цифровой маркировки отечественных и зарубежных радиоэлектронных элементов. Справочник. М.: Горячая линия – Телеком, 2001 352 с.: ил. (Массовая радиобиблиотека; 1240).

5. ГуровВ.В. Синтез комбинационных схем в примерах и решениях: Учеб. пособие. М.: МИФИ, 2001. 54 с.: ил.

6. Партала О.Н. Цифровая электроника. Издание 2-е, доп. СПб: Наука и техника, 2001. 224 с.: ил.

7. Пухальский Г.И. Проектирование микропроцессорных устройств: Учеб. пособие для вузов. СПб.: Политехника, 2001. 544 с.: ил.

8. Столлингс В. Структура и организация компьютерных систем, 5-е изд.: Пер., с англ М.: Издательский дом “Вильямс”, 2002. 896 с.: ил.

9. ГуровВ.В. Основы организации вычислительных машин: Учеб. пособие. М.: МИФИ, 2004. 163 с.: ил.

10. Электронный учебник – искусство схемотехники.

ISBN 5-7262-0710-6. НАУЧНАЯ СЕССИЯ МИФИ-2007. Том 11