Методические указания к курсовой работе по дисциплине «Аппаратные средства вычислительной техники»

| Вид материала | Методические указания |

- Задачи дисциплины: -изучение основ вычислительной техники; -изучение принципов построения, 37.44kb.

- Методические указания к курсовой работе по дисциплине «Управленческие решения», 145.2kb.

- Методические указания к курсовой работе для специальностей 220100 Вычислительные машины,, 87.91kb.

- Методические указания для студентов специальности 230105 «Программное обеспечение вычислительной, 223.95kb.

- Методические указания к курсовой работе по дисциплине «численные методы», 134.12kb.

- Методические указания к курсовому проектированию по дисциплине «Техническое обслуживание, 248.21kb.

- Методические указания По дисциплине «Разработка и эксплуатация удаленных баз данных», 370.7kb.

- Методические рекомендации по организации и защите курсовой работы по дисциплине для, 794.15kb.

- Методические указания к курсовой работе по дисциплине «Теория автоматического управления», 552.83kb.

- Методические указания к курсовой работе по дисциплине «Материаловедение и ткм», 699.8kb.

Федеральное агентство по образованию

Пензенский государственный университет

Блок памяти микропроцессорной системы

Методические указания к курсовой работе по дисциплине

«Аппаратные средства вычислительной техники»

ПЕНЗА 2009

УДК 681.3

Даны указания к выполнению курсовой работы по разработке блока памяти микропроцессорной системы. Представлены варианты технических заданий на разработку блока памяти; приведены рекомендации по построению блока памяти.

Методические указания подготовлены на кафедре «Информационная безопасность систем и технологий» и предназначены для студентов специальности 090105 «Комплексное обеспечение информационной безопасности автоматизированных систем».

Ил. Х, табл. Х, библиогр. Х назв.

Составитель: А.П. Иванов

Рецензент: А.А. Елпатов, к.т.н, старший инженер Центра правительственной связи ФАПСИ в Пензенской области

1 Содержание курсовой работы

Курсовая работа должна содержать пояснительную записку (ПЗ) формата А4 и графическую часть, в которую должны входить функциональная электрическая схема (1 лист формата А4) и принципиальная электрическая схема разработанного блока памяти (1 лист формата А1) и перечень элементов к ней формата А4, а также временная диаграмма работы разработанного блока памяти.

ПЗ оформляется в объеме 2535 листов и должна содержать (по порядку брошюрования):

- титульный лист;

- реферат, в котором приводятся сведения об объеме работы, количестве иллюстраций, таблиц, использованных источников и приложений, ключевые слова, сведения о сущности выполнения работы и важнейшие характеристики разработанных схем;

- содержание работы, в которое включены все имеющиеся в ПЗ заголовки с нумерацией листов;

- введение, в котором обоснована необходимость проведения работы, сформулирована её цель, дана краткая характеристика разработанных схем;

- техническое задание (ТЗ) на курсовую работу;

- описание следующих процессов: обоснование выбора элементной базы; разработки алгоритмов работы разработанного блока памяти и его описание; построение заданных структур ПЗУ и ОЗУ; общую структуру проектируемой памяти; разработки функциональной и принципиальной схем разработанного блока памяти и их описание; построение временных диаграмм работы блока памяти; результаты проверки работоспособности отдельных частей разработанной схемы блока памяти;

- заключение с кратким изложением основных результатов работы и характеристикой выполнения требований ТЗ;

- список использованных источников (учебников, пособий, справочников и т.п.), выполненный по требования ГОСТ 7.1-84. Нумерация источников дается в порядке ссылок на них в тексте ПЗ.

- приложения в которых помещают материалы, связанные с выполнением работы, имеющие, как правило, самостоятельное значение и которые загромождают основной текст.

Защита работы включает в себя краткий доклад (продолжительность 35 минут), отражающий существо и основные результаты проведенной разработки, и ответы на вопросы, позволяющие оценить обоснованность принятых технических решений, степень овладения теоретическими знаниями и умение их практического использования.

2 Указания по оформлению курсовой работы

Текстовые документы ПЗ должны выполняться в соответствии с требованиями ГОСТ 7.32-2001 на сброшюрованных листах формата А4 без основных надписей (малых и больших штампов). Титульный лист оформляется по образцу, приведенному в приложении А, на котором проставляются все подписи.

Каждый раздел ПЗ начинается с нового листа, разделы имеют единую нумерацию арабскими цифрами. После номера раздела точка не ставится. Номера подразделов состоят из номера раздела и номера подраздела, разделенных точкой. Наличие текста вне разделов и подразделов не допускается. Нумерация страниц ПЗ сквозная, включая приложения. Номер страницы проставляется арабскими цифрами в центре нижней части листа без точки. На титульном листе номер не ставится.

Текст должен быть оформлен печатным способом через полтора интервала, шрифтом с размером кегля не менее 12, с соблюдением полей по ГОСТ 7.32-2001.

3 Техническое задание к курсовой работе

Разработать в соответствии с вариантом блок памяти микропроцессорной системы, состоящий из ПЗУ и статического ОЗУ. Микропроцессорная система работает в реальном режиме.

Разрядность шины адреса (ША) - 20, шины данных (ШД) - 8.

Адреса, покрываемые пространствами ПЗУ и ОЗУ, и емкость микросхемы выбрать из таблиц Б1, Б2 приложения Б.

Построить в соответствии с дополнительными исходными данными функциональную и принципиальную схему блока памяти и выполнить перечень элементов к ней. Разработать алгоритм работы блока памяти и построить временные диаграммы его работы, а также реализовать и исследовать часть блока памяти с помощью программы EWB.

Варианты задания и необходимые исходные данные приведены в приложении Б.

4 Общие сведения

Дисциплина “Аппаратные средства вычислительной техники” предполагает изучение структуры и функционирования микропроцессорной системы.

Структура микропроцессорной системы представлена тремя блоками:

- центрального процессорного устройства, в котором выполняются все операции преобразования информации;

- памяти, где хранится базовая информация для функционирования микропроцессорной системы, и записываются программы пользователя;

- устройств ввода-вывода, обеспечивающим получение и выдачу информации при работе пользователя с микропроцессорной системой.

В курсовой работе предлагается к изучению блок памяти. Необходимо, предварительно изучив теорию, построить пространство памяти заданного объема и конфигурации.

4.1 Устройства памяти

Устройства памяти микропроцессорной системы (МПС) могут быть внешними (винчестер, дисковод, CD-ROM и т.д.) и внутренними.

Рассматривается только внутренняя память МПС, которая может быть:

- постоянной (ROM) или ПЗУ,

- оперативной (RAM) или ОЗУ.

В свою очередь ПЗУ по способу записи/перезаписи информации различаются следующим образом.

ПЗУ – постоянные запоминающие устройства, в основу которых положены диодные матрицы. Матрицы прожигаются на заводе-изготовителе, пользователь ничего изменить не может (рисунок 1).

ППЗУ – перепрограммируемые ПЗУ (матрицы поставляются пользователю с уровнем 1 во всех узлах, пользователь может только один раз прожечь матрицу по своей программе).

РПЗУ - репрограммируемые (т.е. многократно программируемые) ПЗУ.

Рисунок 1 - Элемент диодной матрицы:

при подаче U>Uдоп диод сгорает, остается перемычка;

при сгоревшем диоде Uузла=0;

при функционирующем диоде Uузла=1.

По способу стирания информации РПЗУ могут быть: ультрафиолетовыми и электрическими.

Оперативные запоминающие устройства ОЗУ могут быть: динамическими (DRAM) и статическими (SRAM).

В динамических ОЗУ, построенных на МОП-транзисторных ячейках с дополнительной емкостью, информация после считывания пропадает, поэтому требуется ее регенерация (восстановление), а значит, такие ОЗУ при своей очевидной дешевизне имеют низкое быстродействие.

Статические ОЗУ, построенные на триггерных ячейках, хранят информацию после считывания и регенерации не требуют, имеют высокое быстродействие, хотя и существенно дороже динамических ОЗУ.

Современные схемы ОЗУ сочетают в себе обе технологии (SDRAM).

4.2 Статические ОЗУ. Принципы построения

Шина адреса (рисунок 2) подключается к микросхеме памяти по N адресным входам: A0–AN–1.

Рисунок 2 - Микросхема статической памяти

Шина данных подключается по входам/выходам D, количество которых зависит от того, сколько матриц размещено в кристалле.

CS – вход выборки кристалла, управляет подключением буфера данных к шине.

– вход запись/чтения, определяет подключение входного или выходного буфера данных к шине данных.

– вход запись/чтения, определяет подключение входного или выходного буфера данных к шине данных. Рассмотрим принцип выбора ячейки памяти по адресу.

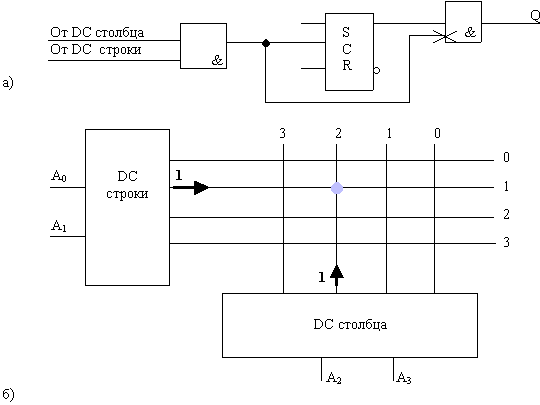

Входы адресной шины подключаются к дешифраторам (DC) строки и столбца матрицы. Предположим, что к микросхеме подключается четыре адресных линии (А0–А3), причем линии А0, А1 подаются на DC строки, а линии А2, А3 – на DC столбца.

Предположим, что на адресных входах указан адрес 9, т.е. 1001.

Таким образом, DC строки по А0 = 1, А1 = 0 установит 1 на выходе 1, а DC столбца по А2 = 0, А3 = 1 установит 1 на выходе 2.

Во всех узлах матрицы расположены триггеры. Вход синхронизации триггера и его выход на общую для данной матрицы линию данных подключаются, как показано на рисунке 3а.

Рисунок 3 - Выбор ячейки по адресу: а – триггера; б – элемента матрицы

Очевидно, что функционировать будет только тот триггер, у которого на входы элемента И от DC строки и DC столбца попадут 1.

В нашем случае будет выбран элемент матрицы, обведенный в кружок (рисунок 3б).

4.3 Принцип записи/чтения информации

Инициализируем элемент матрицы, подав адрес на адресные входы. Теперь покажем, как будет происходить процесс записи/чтения данных. Заметим, что каждая матрица имеет один общий провод данных, т.е. каждый разряд данных записан в своей матрице. Адресация таких матриц производится параллельно.

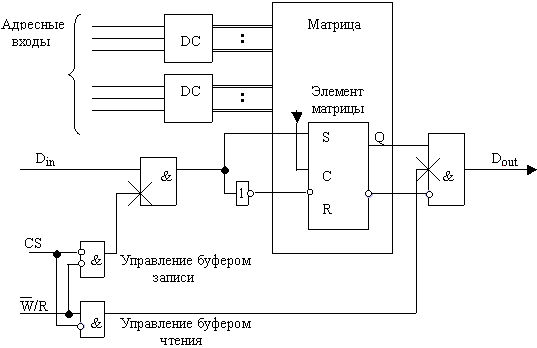

Рассмотрим обращение к одному разряду данных. Только при подаче на вход CS уровня 0 (рисунок 4) на выходе управляющих схем буферов чтения и записи может появиться 1. Причем на выходе управления буфером записи 1 появится при 0 на входе

, а на выходе управления буфером чтения – при 1 на

, а на выходе управления буфером чтения – при 1 на  .

.

Рисунок 4 - Функции входов CS и

4.4 Построение пространства памяти заданного объема

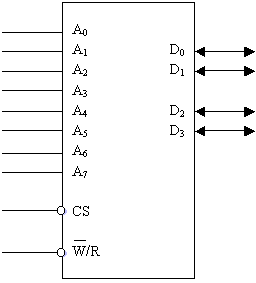

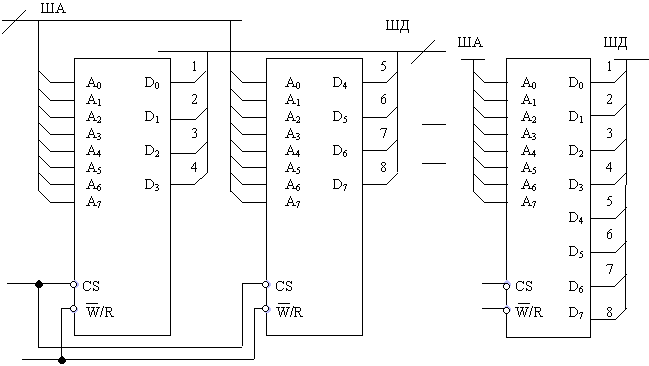

Из микросхем SRAM небольшой емкости можно составить память любого заданного объема. Предположим, что в нашем распоряжении есть микросхемы SRAM емкостью 2564 (рисунок 5).

Рисунок 5 - Микросхема памяти 2564

Необходимо составить память устройства емкостью 1 Кбайт или 1К8. Схема 2564 имеет 4 матрицы по 256 ячеек (256=28), т.е. схема имеет 8 адресных входов.

Для того чтобы обеспечить чтение/запись байта информации, надо добавить еще 4 матрицы внешним соединением (т.е. объединить 2 микросхемы).

Получим эквивалентную схему, позволяющую хранить 256 байт информации.

Для построения памяти на 1 Кбайт необходимо 4 таких схемы:

1К=210; 210/28=22=4.

Рисунок 6 - Получение эквивалентной схемы 2568

Доступ к такой памяти осуществляется по 10 адресным линиям (1К=210): непосредственно к схеме подключаются 8 адресных линий, а 2 – к дешифратору, с помощью которого выбирается одно из 4 направлений.

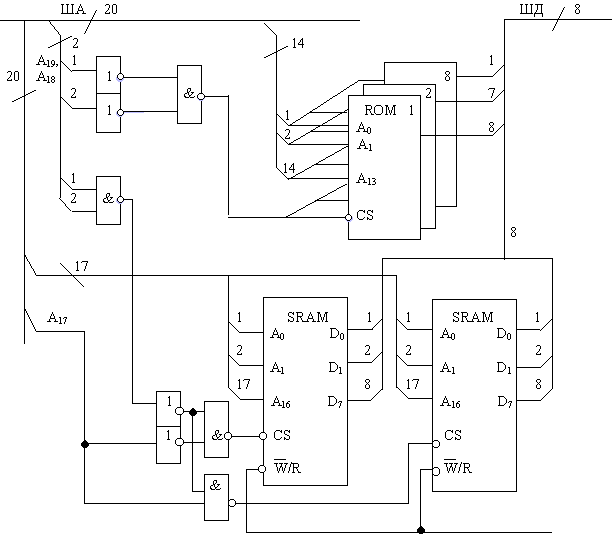

Общая схема памяти (см. рисунок 7) составлена из эквивалентных схем (см. рисунок 6), исходная микросхема представлена на рисунке 5.

5 Пример решения задачи

Предположим, что адреса, покрываемые ПЗУ и ОЗУ:

ПЗУ от 00000Н до 03FFFH;

ОЗУ от 0C0000H до 0FFFFFH.

Шина адреса 20-разрядная, следовательно, адрес памяти записывается на пяти 16-ричных разрядах (один 16-ричный разряд представляется на 4 двоичных). В адресах ОЗУ в этом случае первый 0 пишется для определения C и F как символов числа, а не букв.

Рисунок 7 - Схема оперативной статической памяти объемом 1Кбайт

Определение емкости ПЗУ и ОЗУ

По полученному диапазону адресов определим емкость ПЗУ и ОЗУ.

Определим количество изменяющихся разрядов и запишем адрес в двоичном коде.

ПЗУ

Начальный адрес: 00000000000000000000b.

Конечный адрес: 00000011111111111111b.

Изменились 14 разрядов, значит, емкость ПЗУ - 214.

Для 8-разрядной шины данных емкость ПЗУ 2148:

214=21024,

210=1К - килобит,

таким образом, емкость ПЗУ равна 16К8.

ОЗУ

Начальный адрес: 11000000000000000000b.

Конечный адрес: 11111111111111111111b.

Изменилось 18 разрядов.

Для 8-разрядной шины данных емкость ОЗУ равна:

2188,

218=21028= 256К,

таким образом, емкость ОЗУ равна 256К8.

Для изображения схемы необходимо определить

- емкости микросхем ОЗУ и ПЗУ по таблице Б2;

- структуры ОЗУ и ПЗУ (количество микросхем, способ соединения);

- общую структуру памяти.

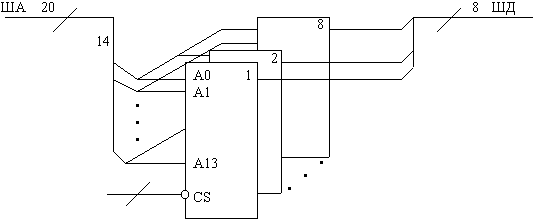

Пусть ПЗУ имеет емкость 16К1 (рисунок 8), а ОЗУ - 128К 8 (рисунок 9).

Таким образом, схема ПЗУ имеет 14 адресных входов 16К=214, один вход/выход данных и вход CS (выборки кристалла).

Схема ОЗУ имеет 17 адресных входов 128К=217, 8 входов/выходов данных, входы CS и

.

.

Определение ПЗУ и ОЗУ

Структура ПЗУ

Емкость ПЗУ - 16К8. Емкость микросхемы 16К1, значит, для получения нужной емкости ПЗУ необходимо объединить параллельно по адресным входам и входу CS 8 микросхем, каждая из которых обеспечит один разряд шины данных (рисунок 10).

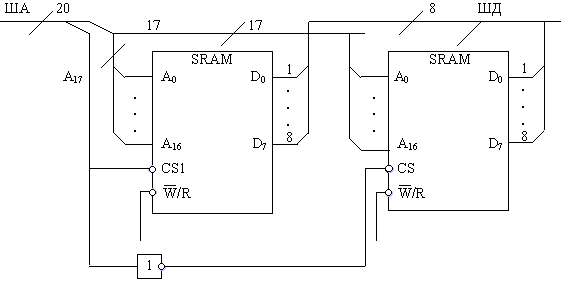

Структура ОЗУ

Емкость ОЗУ 256К8, емкость микросхемы 128К8, значит, для построения такого ОЗУ необходимы 2 микросхемы.

Рис. 10. Структура ПЗУ 16К 8

Для построения ОЗУ обратимся к адресам, на которых работает эта память. По заданию изменяются 18 младших разрядов А0–А17. Для каждой микросхемы могут изменяться лишь 17 адресов А0–А16. Следовательно, старший разряд определяет направление на микросхему. Если А17–0, задействуется первая микросхема ОЗУ, если 1 - вторая.

Рисунок 11. Структура ОЗУ 256К 8

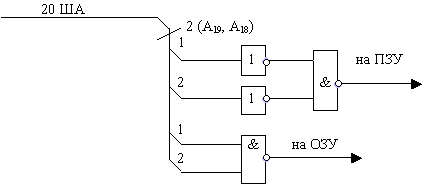

Общая структура памяти (рисунок 13)

По заданию начальные адреса ПЗУ и ОЗУ следующие:

ПЗУ (00000H – 00000000000000000000b),

ОЗУ (0C0000H – 11000000000000000000b).

По состоянию разрядов: А19, А18 - 00 работает ПЗУ, а по состоянию А19, А18 - 11 работает ОЗУ. С помощью простейшей логики можно построить дешифратор направлений ПЗУ/ОЗУ (рисунок 12).

Рисунок 12 - Дешифратор направлений ПЗУ/ОЗУ

Рисунок 13 - Общая структура проектируемой памяти

Список литературы

- Угрюмов Е.П. Цифровая схемотехника. - СПб: БХВ-СПб, 2000.

- Большие интегральные микросхемы запоминающих устройств: справочник. - М.: Радио и связь, 1990.

- Потемкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат,1988. - 320 с.

ПРИЛОЖЕНИЕ А

(справочное)

Образец оформления титульного листа ПЗ

Федеральное агентство по образованию

Пензенский государственный университет

Кафедра "Информационная безопасность систем и технологий"

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовой работе

на тему "Блок памяти микропроцессорной системы"

ПГУ 3.090105.001 ПЗ

Дисциплина: Аппаратные средства вычислительной техники

Автор работы: _________________

Группа:_______________________

Вариант задания:_______________

Количество баллов: _____________

Работа принята с оценкой:_______

Дата сдачи работы:_____________

Руководитель работы:___________

Пенза 2008

ПРИЛОЖЕНИЕ Б

(обязательное)

Варианты задания и исходные данные

Исходные данные:

- микропроцессорная система работает в реальном режиме;

- разрядность шины адреса (ША) – 20;

- разрядность шины данных (ШД) - 8.

Таблица Б1 – Адреса, покрываемые ПЗУ и ОЗУ

| № варианта | Адреса, покрываемые ПЗУ | Адреса ОЗУ |

| 1 | 00000H 0FFFFH | 20000H 3FFFFH |

| 2 | 00000H 1FFFFH | 40000H 5FFFFH |

| 3 | 00000H 07FFFH | 60000H 7FFFFH |

| 4 | 00000H 1FFFFH | 80000H 9FFFFH |

| 5 | 00000H 03FFFH | 0C0000H 0DFFFFH |

| 6 | 00000H 0FFFFH | 0A0000H 0BFFFFH |

| 7 | 00000H 07FFFH | 0E0000H FFFFFH |

| 8 | 00000H 1FFFFH | 40000H 7FFFFH |

| 9 | 00000H 07FFFH | 80000H BFFFFH |

| 10 | 00000H 03FFFH | 0C0000H 0FFFFFH |

| 11 | 00000H 0FFFFH | 0C0000H 0FFFFFH |

| 12 | 00000H 1FFFFH | 80000H BFFFFH |

| 13 | 00000H 07FFFH | 40000H 7FFFFH |

| 14 | 00000H 1FFFFH | 0E0000H FFFFFH |

| 15 | 00000H 03FFFH | 0A0000H 0BFFFFH |

| 16 | 00000H 0FFFFH | 0C0000H 0DFFFFH |

| 17 | 00000H 07FFFH | 80000H 9FFFFH |

| 18 | 00000H 1FFFFH | 60000H 7FFFFH |

| 19 | 00000H 07FFFH | 40000H 5FFFFH |

| 20 | 00000H 03FFFH | 20000H 3FFFFH |

| 21 | 00000H 0FFFFH | 0C0000H 0DFFFFH |

| 22 | 00000H 1FFFFH | 0C0000H 0FFFFFH |

| 23 | 00000H 07FFFH | 80000H 9FFFFH |

| 24 | 00000H 1FFFFH | 80000H BFFFFH |

| 25 | 00000H 03FFFH | 60000H 7FFFFH |

| 26 | 00000H 0FFFFH | 40000H 7FFFFH |

| 27 | 00000H 07FFFH | 40000H 5FFFFH |

| 28 | 00000H 1FFFFH | 0E0000H FFFFFH |

| 29 | 00000H 07FFFH | 20000H 3FFFFH |

| 30 | 00000H 03FFFH | 0A0000H 0BFFFFH |

Таблица Б2 – Микросхемы ПЗУ и ОЗУ

| № варианта | Микросхема ПЗУ | Микросхема ОЗУ |

| 1 | 32К 1 | 64К 1 |

| 2 | 64К 4 | 128К 4 |

| 3 | 64К 1 | 64К 8 |

| 4 | 16К 4 | 64К 4 |

| 5 | 32К 4 | 32К 4 |

| 6 | 64К 8 | 128К 1 |

| 7 | 32К 8 | 32К 8 |

| 8 | 16К 8 | 256К 1 |

| 9 | 32К 1 | 32К 1 |

| 10 | 16К 1 | 128К 8 |

| 11 | 16К 1 | 128К 1 |

| 12 | 32К 1 | 32К 8 |

| 13 | 16К 8 | 256К 1 |

| 14 | 32К 8 | 32К 1 |

| 15 | 64К 8 | 64К 1 |

| 16 | 32К 4 | 128К 4 |

| 17 | 16К 4 | 64К 8 |

| 18 | 64К 1 | 64К 4 |

| 19 | 64К 4 | 32К 4 |

| 20 | 32К 1 | 128К 8 |

| 21 | 32К 1 | 64К 1 |

| 22 | 32К 8 | 128К 4 |

| 23 | 32К 4 | 64К 8 |

| 24 | 64К 1 | 32К 8 |

| 25 | 32К 1 | 256К 1 |

| 26 | 16К 1 | 32К 1 |

| 27 | 16К 8 | 64К 4 |

| 28 | 64К 8 | 32К 4 |

| 29 | 16К 4 | 128К 1 |

| 30 | 64К 4 | 128К 8 |

Содержание

| 1 Содержание курсовой работы . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . | 3 |

| 2 Указания по оформлению курсовой работы . . . . . . . . . . . . . . . . . . . . . . | 4 |

| 3 Техническое задание к курсовой работе. . . . . . . . . . . . . . . . . . . . . . . . . | 4 |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| | |

| Список литературы . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . | |

| Приложение А. Справочное. Образец оформления титульного листа ПЗ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . | |

| Приложение Б. Обязательное. Варианты задания и исходные данные . . | |