Методические указания к выполнению курсовой работы по дисциплине «Вычислительная техника» для студентов специальности «Сети связи и системы коммутации» пермь 2009

| Вид материала | Методические указания |

- Методические указания по выполнению курсовой работы для студентов направления 230100, 392.17kb.

- Методические указания к выполнению курсовой работы для студентов всех форм обучения, 197.12kb.

- Соболева Наталья Владимировна методические указания, 73.26kb.

- Методические указания по выполнению курсовой работы Ижевск, 289.74kb.

- Методические указания для выполнения курсовой работы по дисциплине «Теория принятия, 547.84kb.

- Курс лекций для студентов очного и заочного отделений по специальности 210406 «Сети, 1072.35kb.

- Методические указания к выполнению курсовой работы для студентов специальности 350400, 219.24kb.

- Методические указания к выполнению курсовой работы Владивосток, 732.88kb.

- Методические указания к выполнению лабораторных работ по курсу «вычислительная техника, 640.55kb.

- Методические указания к выполнению курсовой работы по дисциплине «организация производства», 2093.85kb.

3 Задание к курсовой работе

При выборе варианта индивидуального задания необходимо пользоваться приведенным ниже перечнем – таблица 1

Номер варианта соответствует порядковому номеру студента в списочном составе.

Таблица 1

| № варианта | Тематика работы (исследуемое устройство) | Исследуемый блок в данном устройстве. | № варианта для блока |

| | АЛУ для выполнения логических операций; | Регистр, сумматор | |

| | АЛУ для выполнения арифметических операций с фиксированной запятой; | Регистр, сумматор | |

| | Умножитель с плавающей запятой; | Регистр, сумматор | |

| | Параллельное АЛУ | Регистр, сумматор | |

| | Специализированное АЛУ | Счетчик, сумматор | |

| | Блок кэш-памяти | Запоминающие устройства, шифратор | 6. |

| | Арифметический ускоритель | счетчик, сумматор | 7 |

| | Блок микропрограммного управления; | Запоминающие устройства, микропроцессорный элемент | 8 |

| | Адаптер интерфейсов | Мультиплексор, кодопреобразователь | 9 |

| | Контроллер ввода-вывода | Шифратор, микропроцессорный элемент | 1 |

| | Контроллер НГМД | Шифратор, микропроцессорный элемент | 2 |

| | Контроллер НМД | Шифратор, микропроцессорный элемент | 3 |

| | Контроллер графопостроителя (плоттер) | Дешифратор, микропроцессорный элемент | 4 |

| | Контроллер печатающего устройства; | Дешифратор, микропроцессорный элемент, | 5 |

| | Арбитр системной магистрали; | Кодопреобразователь, мультиплексор | 6 |

| | Блок ОЗУ персональной ЭВМ; | Дешифратор, Запоминающее устройство | 7 |

| | Разработка математической модели узла ЭВМ | Запоминающее устройство, микропроцессорный элемент | 3 |

3.1 Задания к построению цифровых блоков

3.1.1 Проектирование Шифратора

Таблица 2

| № варианта | Базис (логическая функция) | Число входов и выходов | Номер возбужденного входа | Двоичный код на выходах | |||

| Х4 | Х3 | Х2 | Х1 | ||||

| 1 | ИЛИ-НЕ | 8-3 | 5 | - | 0 | 0 | 0 |

| 2 | И-НЕ | 10-4 | 7 | 0 | 0 | 0 | 1 |

| 3 | ИЛИ-НЕ | 16-4 | 9 | 1 | 1 | 1 | 0 |

| 4 | И-НЕ | 8-3 | 4 | - | 0 | 1 | 0 |

| 5 | ИЛИ-НЕ | 10-4 | 6 | 0 | 1 | 1 | 1 |

| 6 | И-НЕ | 16-4 | 8 | 1 | 1 | 0 | 0 |

| 7 | ИЛИ-НЕ | 8-3 | 3 | - | 0 | 1 | 1 |

| 8 | И-НЕ | 10-4 | 2 | 1 | 0 | 0 | 0 |

| 9 | ИЛИ-НЕ | 16-4 | 10 | 1 | 1 | 0 | 1 |

| 10 | И-НЕ | 8-3 | 1 | - | 1 | 0 | 0 |

- Приведите условное графическое обозначение микросхемы шифратора, имеющего указанное в табл.2 количество входов- выходов, опишите ее принцип действия.

- Объясните назначения данного шифратора (таб.2), укажите назначение его выводов.

- Составьте таблицу истинности для данного шифратора.

- Запишите логическую схему выражения для выходов шифратора через операцию ИЛИ.

- Постройте логическую схему шифратора в базисе, указанном в табл.2, предварительно записав логические выражения для выходов данного шифратора через указанную логическую операцию.

- Описать работу схемы: на каком входе шифратора действует сигнал логической «I» , если на выходах зафиксирован двоичный код, указанный в таб.2.

- Укажите сигналы на входах и выходах логической схемы шифратора для заданного номера возбужденного входа.

3.1.2 Проектирование Дешифратора

Таблица 3

| № варианта | Базис (логическая функция) | Число входов и выходов | Двоичный код на входах | Номер выхода дешифратора | |||

| Х4 | Х3 | Х2 | Х1 | ||||

| 1 | И-НЕ | 3-8 | - | 1 | 1 | 1 | 3 |

| 2 | ИЛИ-НЕ | 4-10 | 1 | 0 | 0 | 1 | 8 |

| 3 | И-НЕ | 4-16 | 1 | 1 | 1 | 0 | 13 |

| 4 | ИЛИ-НЕ | 3-8 | - | 1 | 0 | 1 | 4 |

| 5 | И-НЕ | 4-10 | 0 | 0 | 1 | 1 | 7 |

| 6 | ИЛИ-НЕ | 4-16 | 1 | 0 | 1 | 1 | 10 |

| 7 | И-НЕ | 3-8 | - | 1 | 1 | 0 | 5 |

| 8 | ИЛИ-НЕ | 4-10 | 1 | 0 | 0 | 0 | 9 |

| 9 | И-НЕ | 4-16 | 1 | 1 | 1 | 1 | 12 |

| 10 | ИЛИ-НЕ | 3-8 | - | 1 | 0 | 0 | 6 |

- Приведите условное графическое обозначение микросхемы дешифратора, имеющего указанное в табл. 3 количество входов-выходов, опишите ее

- Объясните назначение данного дешифратора, укажите назначение его выводов.

- Составьте таблицу истинности для данного дешифратора.

- Запишите логическое выражение для выходов дешифратора через операцию И.

- Постройте логическую схему дешифратора в базисе, указанном в таблице 3, предварительно записав логические выражения для выходов данного дешифратора через указанную по варианту логическую операцию.

- Укажите сигналы предложенного в таблице 3 двоичного кода на входах и выходах логических элементов схемы

- Опишите работу схемы: какой двоичный код присутствует на входах дешифратора, если «выбранным» является номер выхода, указанный в табл. 3.

3.1.3 Проектирование мультиплексора или демультиплексора

Таблица 4

| № варианта | Число каналов | № подключенного канала | Наличие стробирующего сигнала |

| 1 | 4 | 3 | - |

| 2 | 8 | 5 | + |

| 3 | 10 | 7 | - |

| 4 | 12 | 11 | + |

| 5 | 16 | 13 | - |

| 6 | 5 | 2 | + |

| 7 | 11 | 10 | - |

| 8 | 13 | 9 | + |

| 9 | 6 | 4 | - |

| 10 | 9 | 1 | + |

- Приведите условное графическое обозначение, микросхемы мультиплексора или демультиплексора предложенного в табл. 4, опишите ее.

- Объясните назначение данного мультиплексора (демультиплексора), укажите назначение его выводов.

- Приведите закон функционирования данного мультиплексора (демультиплексора) в виде таблицы истинности.

- Запишите логические выражения для выхода 0.

- Постройте логическую схему данного мультиплексора (демультиплексора)

- Какой код должен быть установлен на адресных выходах, если необходимо подключить канал, номер которого указан в табл. 4.

- Подайте на адресные входы любой код и укажите, какой при этом будет подключен к выходу 0 информационный канал.

- Приведите соотношение, связывающее максимальное число подключенных информационных каналов, и число адресных входов.

3.1.4 Проектирование кодопреобразователя

Таблица 5

| Цифра | Вариант 1 | Вариант 2 | Вариант 3 | Вариант 4 | Вариант 5 | ||||||||||||||||||||

| | A | B | C | D | | A | B | C | D | | A | B | C | D | | A | B | C | D | | A | B | C | D | |

| 0 | | 0 | 0 | 0 | 0 | | 0 | 0 | 0 | 0 | | 0 | 0 | 1 | 1 | | 0 | 0 | 0 | 0 | | 0 | 0 | 0 | 0 |

| 1 | | 0 | 0 | 0 | 1 | | 0 | 0 | 0 | 1 | | 0 | 1 | 0 | 0 | | 0 | 0 | 0 | 1 | | 0 | 0 | 0 | 1 |

| 2 | | 0 | 0 | 1 | 0 | | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | 1 | | 0 | 0 | 1 | 1 | | 0 | 0 | 1 | 0 |

| 3 | | 0 | 0 | 1 | 1 | | 0 | 0 | 1 | 1 | | 0 | 1 | 1 | 0 | | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | 1 |

| 4 | | 0 | 1 | 0 | 0 | | 0 | 1 | 0 | 0 | | 0 | 1 | 1 | 1 | | 0 | 1 | 1 | 0 | | 0 | 1 | 1 | 0 |

| 5 | | 0 | 1 | 0 | 1 | | 1 | 0 | 1 | 1 | | 1 | 0 | 0 | 0 | | 0 | 1 | 1 | 1 | | 1 | 0 | 0 | 1 |

| 6 | | 0 | 1 | 1 | 0 | | 1 | 1 | 0 | 0 | | 1 | 0 | 0 | 1 | | 0 | 1 | 0 | 1 | | 1 | 0 | 1 | 0 |

| 7 | | 0 | 1 | 1 | 1 | | 1 | 1 | 0 | 1 | | 1 | 0 | 1 | 0 | | 0 | 1 | 0 | 0 | | 1 | 1 | 0 | 1 |

| 8 | | 1 | 0 | 0 | 0 | | 1 | 1 | 1 | 0 | | 1 | 0 | 1 | 1 | | 1 | 1 | 0 | 0 | | 1 | 1 | 1 | 0 |

| 9 | | 1 | 0 | 0 | 1 | | 1 | 1 | 1 | 1 | | 1 | 1 | 0 | 0 | | 1 | 1 | 0 | 1 | | 1 | 1 | 1 | 1 |

| Вариант 6 | Вариант 7 | Вариант 8 | Вариант 9 | Вариант 10 | ||||||||||||||||||||

| | A | B | C | D | | A | B | C | D | | A | B | C | D | | A | B | C | D | | A | B | C | D |

| | 1 | 1 | 1 | 1 | | 1 | 1 | 1 | 1 | | 1 | 1 | 0 | 0 | | 1 | 1 | 1 | 1 | | 1 | 1 | 1 | 1 |

| | 1 | 1 | 1 | 0 | | 1 | 1 | 1 | 0 | | 1 | 0 | 1 | 1 | | 1 | 1 | 1 | 0 | | 1 | 1 | 1 | 0 |

| ` | 0 | 1 | 0 | 1 | | 1 | 1 | 0 | 1 | | 1 | 0 | 1 | 0 | | 1 | 1 | 0 | 0 | | 1 | 1 | 0 | 1 |

| | 0 | 1 | 0 | 0 | | 1 | 1 | 0 | 0 | | 1 | 0 | 0 | 1 | | 1 | 1 | 0 | 1 | | 1 | 0 | 1 | 0 |

| | 0 | 0 | 1 | 1 | | 1 | 0 | 1 | 1 | | 1 | 0 | 0 | 0 | | 1 | 0 | 0 | 1 | | 1 | 0 | 0 | 1 |

| | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | 0 | | 0 | 1 | 1 | 1 | | 1 | 0 | 0 | 0 | | 0 | 1 | 1 | 0 |

| | 0 | 0 | 0 | 1 | | 0 | 0 | 1 | 1 | | 0 | 1 | 1 | 0 | | 1 | 0 | 1 | 0 | | 0 | 1 | 0 | 1 |

| | 1 | 0 | 0 | 0 | | 0 | 0 | 1 | 0 | | 0 | 1 | 0 | 1 | | 1 | 0 | 1 | 1 | | 0 | 0 | 1 | 0 |

| | 0 | 1 | 1 | 1 | | 0 | 0 | 0 | 1 | | 0 | 1 | 0 | 0 | | 0 | 0 | 1 | 1 | | 0 | 0 | 0 | 1 |

| | 0 | 1 | 1 | 0 | | 0 | 0 | 0 | 0 | | 0 | 0 | 1 | 1 | | 0 | 0 | 1 | 0 | | 0 | 0 | 0 | 0 |

Согласно данным для каждого варианта, приведенных в таблице 5, спроектировать и реализовать кодопреобразователь.

В отчете должны содержаться все этапы проектирования, схема кодопреобразователя выводы о проделанной работе

3.1.5 Проектирование счетчика

Таблица 6

| № варианта | Тип микросхемы | Двоичный код | Число входных импульсов |

| 1 | К155Ие7 | 1010 | 69 |

| 2 | К155ИЕ6 | 1101 | 57 |

| 3 | К531ИЕ15 | 1000 | 75 |

| 4 | К555ИЕ10 | 1001 | 80 |

| 5 | К555ИЕ14 | 1110 | 54 |

| 6 | К555ИЕ18 | 0111 | 63 |

| 7 | К155ИЕ7 | 0011 | 82 |

| 8 | К155ИЕ6 | 1011 | 67 |

| 9 | К531ИЕ15 | 1010 | 73 |

| 10 | К555ИЕ10 | 1100 | 58 |

- Приведите логическую схему четырехразрядного суммирующего счетчика на асинхронных Т-триггерах с инверсными динамическими входами.

Постройте временную диаграмму работы данного счетчика.

- Выберите из табл. 6 микросхему счетчика для своего варианта. Приведите условное графическое обозначение заданной микросхемы.

- Укажите назначение всех выводов. Объясните назначение данного счетчика.

- Определите разрядность счетчика (n) и коэффициент пересчета (N). Определите максимальное значение числа, которое может быть зафиксировано счетчиком в одном цикле, и запишите его двоичным кодом.

- Укажите на схеме сигналы, подаваемые на входы счетчика для предварительной записи двоичного кода, заданного табл. 6.

- Укажите номер входа, на который поступают импульсы, подлежащие счету в режиме сложения.

- Выполните расчет и укажите на выходах двоичный код, зафиксированный в счетчике в режиме сложения после поступления заданного числа входных импульсов, если предварительно в нем был записан заданный двоичный код.

Методические указания по выполнению

Разрядность счетчика (n) можно определить по количеству выходов разрядов. Коэффициент перерасчета (N) для двоичного счетчика определяется по формуле: N=2n.

Примечание. Счетчики К155ИЕ6 и К555ИЕ14 являются двоично-десятичными, их коэффициент перерасчета N =10.

Максимально значение числа, зафиксированное счетчиком в одном цикле, определяется по формуле: N – 1.

выделите цветным карандашом на рисунке информационные входы и управляющий вход предварительной записи. Определите, какой из входов предназначен для ввода старшего разряда заданного двоичного кода. Определите на указанных входах счетчики логические сигналы в соответствии с заданным двоичным кодом.

Пример: расчета двоичного кода в счетчике.

Определите код двоичного числа, зафиксированного суммирующим счетчиком с коэффициентом пересчета N=16, после поступления на его вход 83 импульсов, если предварительно в нем был установлен двоичный код 1011.

Дано:

N = 16

m = 83

A = 1011

____________________

Двоичный код - ?

Определим, сколько импульсов предварительно просчитал счетчик, зафиксировав исходный код 1011:

А = 1011(2) = 11(10)

Определим общее число импульсов, поступающих в счетчик:

11 + 83 = 94

Чтобы зафиксировать число 94, счетчик просчитает несколько (К) полных циклов и в последнем цикле зафиксирует остаток:

94- К * 16 = 94 – 5 * 16 = 14(10) = 1110(2)

Остаток – число 14 двоичным кодом 1110 будет зафиксирован на выходах счетчика.

3.1.6 Проектирование регистра

Таблица 7

| № варианта | Тип регистра | Тип микросхемы | Двоичное число |

| 1 | Левого сдвига | К500ИР141 | 1110 |

| 2 | Правого сдвига | К1500ИР141 | 11011011 |

| 3 | Параллельный | К155ИР13 | 11101010 |

| 4 | Последовательно-параллельный | К155ИР1 | 1100 |

| 5 | Параллельно-последовательный | К203ИР2 | 1101 |

| 6 | Левого сдвига | К500ИР141 | 1011 |

| 7 | Правого сдвига | К1500ИР141 | 10101101 |

| 8 | Параллельный | К155ИР13 | 10111001 |

| 9 | Последовательно-параллельный | К1500ИР141 | 11111011 |

| 10 | Параллельно-последовательный | К155ИР13 | 11011110 |

- Выберите из табл. 7 микросхему регистра для заданного варианта. Приведите условное графическое обозначение заданной микросхемы. Укажите назначение всех выводов. Определите тип регистра.

- Приведите логическую схему четырехразрядного регистра заданного типа табл.7 на D – триггерах. Обозначьте входы и выходы.

- Перечислите основные функции, выполняемые заданным регистром.

- Определите разрядность регистра (n).

- Укажите на схеме сигналы, подаваемые на информационные входы регистра в режиме записи заданного двоичного числа ( табл. 7) в параллельной форме.

- Укажите номера и типы входов, на которые надо подавать управляющие сигналы в режиме параллельной записи.

- Укажите на выходах двоичное число, зафиксированное в регистре после выполнения сдвига вправо на 4 разряда. Постройте диаграмму сдвига. Укажите номер входа, на который поступают импульсы сдвига.

Методически указания по выполнению

В задании используются универсальные регистры, разрядность которых (n) можно определить по количеству выходов.

Выделите цветным карандашом информационные входы регистра. Определите, какой из входов предназначен для ввода старшего разряда числа. С учетом этого запишите заданное двоичное число

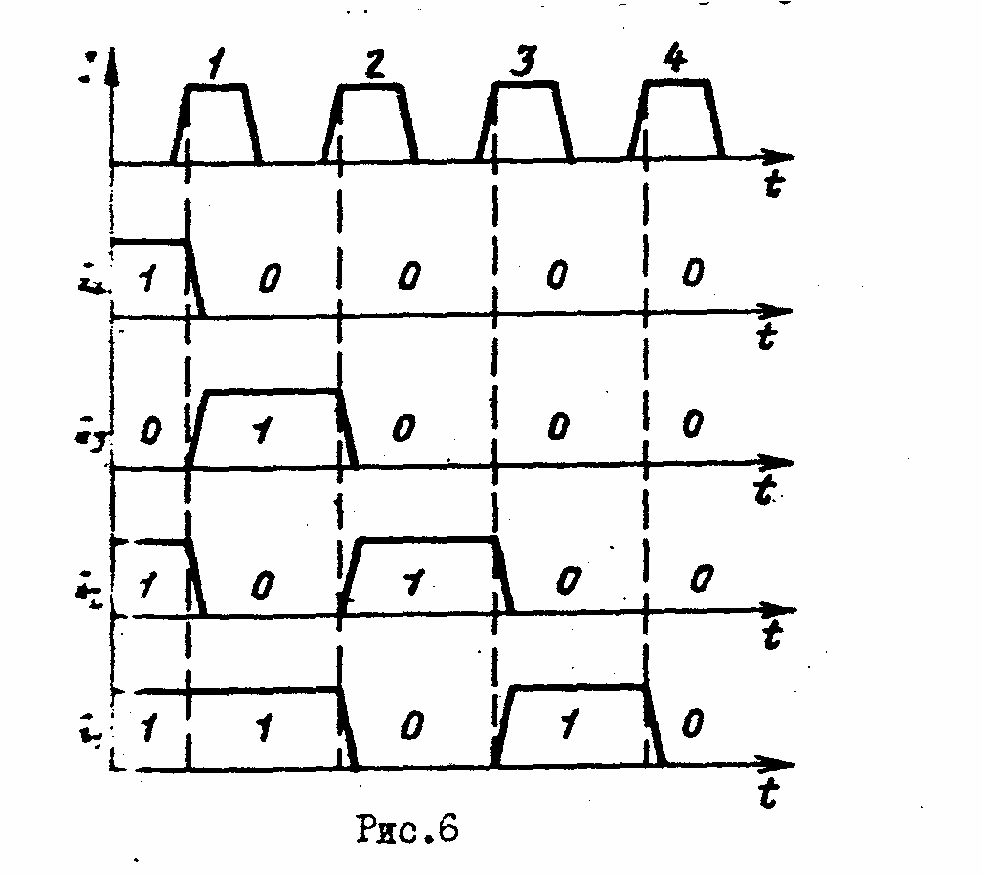

Ниже приведен вариант диаграммы .

В рассматриваемом примере в регистре в исходном состоянии записано двоичное число 1011. Пояснив пример сдвига числа на 4 разряда вправо.

Вход триггера Q4 Q3 Q2 Q1

Число сдвига 1 0 1 1

Число сдвига 1 0 1 1Число после 1-го сдвига 0 1 0 1

Число после 2-го сдвига 0 0 1 0

Число после 3-го сдвига 0 0 0 1

Число после 4-го сдвига 0 0 0 0

На вход С поступают импульсы сдвига. Сдвиг происходит в момент формирования положительного фронта импульса, так как в рассматриваемой схеме регистре вход С – прямой динамический.

3.1.7 Проектирование сумматора

Таблица 8

| № варианта | А | В | С | D | Интегральная микросхема |

| 1 | 0011 | 1100 | 11110000 | 00000001 | К155ИМ3 |

| 2 | 0100 | 1101 | 10001110 | 00000011 | К555ИМ6 |

| 3 | 0101 | 1110 | 11010001 | 01000000 | К155ИМ3 |

| 4 | 0110 | 1111 | 11100010 | 00110101 | К555ИМ6 |

| 5 | 0111 | 0010 | 11110100 | 01010010 | К155ИМ3 |

| 6 | 1000 | 0100 | 11001110 | 01100001 | К555ИМ6 |

| 7 | 1001 | 0101 | 10111000 | 10101100 | К155ИМ3 |

| 8 | 1100 | 0110 | 1010001 | 01111000 | К555ИМ6 |

| 9 | 1011 | 0111 | 10010010 | 10000011 | К155ИМ3 |

| 10 | 1100 | 1000 | 10000101 | 00110111 | К555ИМ6 |

- Объясните назначение четырехразрядного двоичного сумматора.

- Приведите условное графическое обозначение микросхемы данного двоичного сумматора (табл. 8). Укажите назначения всех выводов. Опишите принцип работы.

- Постройте логическую схему четырехразрядного сумматора параллельного действия на базе полусумматоров и логических элементов ИЛИ.

- Укажите назначение логических сигналов на входах и выходах суммы при сложении двоичных чисел A и B в соответствии с вариантом (табл.8).

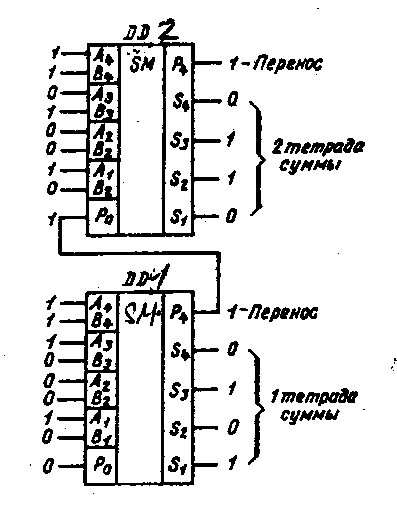

- Приведите соединения микросхем указанного варианта для построения восьмиразрядного двоичного сумматора параллельного действия.

- На всех выходах схемы проставьте значения логических сигналов при сложении двух восьмиразрядных чисел: C и D (табл.8).

- Запишите результат сложения двух восьмиразрядных чисел в шестнадцатеричной, восьмеричной и десятичной системах счисления.

Методические указания по выполнению

При построение сумматора для восьмиразрядных чисел нужно учитывать, что на входы этого сумматора слагаемые поступают параллельно, а перенос между разрядами передается последовательно.

Пример 1.

Выполните сложения двух восьмиразрядных чисел С и D.

1

1 1 1 - переносы

1 1 - переносыС = 1001 1101 - первое слагаемое

+

D = 1100 1000 - второе слагаемое

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

С

+D = 1 0110 0101 - сумма

+D = 1 0110 0101 - сумма2 тетрада 1 тетрада

1 тетрада – 4 младших разряда числа

2 тетрада – 4 старших разряда числа

В данном примере формируется переносы из 4-го разряда в 5-й, из 5-го в 6-ой, из 8-го в 9-й.

Для построения схемы восьмиразрядного сумматора используем две микросхемы К555ИМ6

Для построения схемы восьмиразрядного сумматора используем две микросхемы К555ИМ6 Для сложения старшие разряды чисел С и D поступают на информационные входы микросхемы DD2, а цифры младших разрядов – на входы DD1 параллельным способом.

Переносы из 4-го разряда в 5-й и из 8-го в 9-й отражены на схеме. Перенос из 5-го разряда в 6-й выполняется внутри микросхемы DD2.

3.1.8 Полупроводниковые запоминающие устройства

Таблица 9

| № варианта | Тип микросхемы | Режим работы | Адрес ячейки памяти |

| I 2 3 4 5 6 7 8 9 10 | К155РУ7 КР568РЕ2 К132РУ2 К1500РТ416 КР556РТ4 К561РУ2А К134РУ6 К176РУ2 К556РТ14 К573РФ1 | запись I считывание запись 1 считывание считывание запись1 запись 0 запись 0 считывание считывание | 1010011110 0100000101010 0110011011 10110101 10101111 11000111 010101000 1010011 00110001010 0010001101 |

- Выберите из таблицы 9 микросхему запоминающего устройства (ЗУ) для своего варианта:

- Приведите условное графическое обозначение (УГО) микросхемы.

- Определите, к какому типу ЗУ она относится, поясните

- Объясните назначение заданной микросхемы и укажите режимы ее работы.

- Укажите назначение всех выводов микросхемы.

- Приведите условное графическое обозначение (УГО) микросхемы.

- Определите организацию памяти данной микросхемы.

- Выполните расчет информационной емкости (М).

- Определите и укажите на рисунке УГО значения логических сигналов, подаваемых на входы микросхемы ЗУ для обеспечения заданного режима работы из табл. 9.

- Запишите адрес ячейки памяти, к которой происходит обращение в десятичной и шестнадцатеричной системах счисления.

Режим работы ЗУ и двоичный адрес ячейки памяти, к которой происходит обращение, указаны в таблице 9.

Методические указания по выполнению

Условное графическое обозначение (УГО) микросхемы ЗУ и назначение его выводов Вы найдете в Приложении. Тип ЗУ определите по функциональному обозначению микросхемы, указанному в верхней части основного поля УГО.

Число хранимых слов (N) в микросхемах ЗУ определяется по формуле:

N=2m, где m – число адресных входов.

Разрядность хранимых слов (n) определяется по числу выходов микросхемы ЗУ.

Формула для расчета информационной емкости: М = N* n, бит

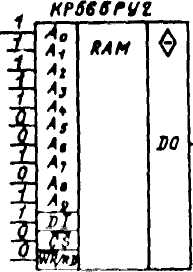

Пример 1 (для микросхемы ОЗУ).

Определим сигналы, которые надо подать на входы микросхемы ОЗУ К565РУ2, чтобы обеспечить режим записи «1» по адресу 1010011111.

-

Обозначение

Назначение

А 0 - А 9

Адресные входы

DI

Вход данных

-DO

Выход данных

cs

Выбор микросхемы

wR/RD

Сигнал запись-

считывание»

Указанный адрес поступает на адресные входы А0…A9, учитывая, что А9 - старший разряд, АО - младший разряд адреса.

Режим записи устанавливается при подаче 0 на вход WR‘/RD где WR - обозначает сигнал записи; RD - обозначает сигнал считывания.

Инверсия над WR’ означает, что запись производится при нулевом значении сигнала на этом входе.

СS - обозначение управляющего сигнала "выбор микросхемы". Инверсия над CS означает, что обращение к ячейке памяти микросхемы (в данном случае выполнение операции записи) происходит при нулевом значении сигнала на этом входе.

На информационный вход D 1 поступает «1» –запись «1».

Десятичный адрес ячейки памяти, в которую производится запись «1», определяется путем перевода двоичного адреса в десятичную систему счисления:

1010011111(2)= 1*29+1*27+1*24+1*'23+1*'22+1*21+1* 2°=671(10)

Шестнадцатеричный адрес определим, выделив тетрады и записав и шестнадцатеричными символами: 0010 1001 1111=29F(16)

3.1.9 Исследование микропроцессорного элемента

Таблица 10

| № варианта | Узлы микропроцессора | Мнемокод команды |

| | RGком, DC,УУ, PC | MVI C,98 |

| | АЛУ, А, RGпром, RGфл | MOV A,D |

| | А, РОН, БД, БА, | LDA 84F5 |

| | RGком, DC, УУ, PC | STA803A |

| | АЛУ, А, RGпром, RGфл | ADI 7F |

| | А, РОН, БД, БА | ADD H |

| | RGком,DC, УУ, PC | SUI D9 |

| | АЛУ, А, RGпром, RGфл | SUB E |

| | А, РОН, БД, БА | DCR B |

| | PC,RG ком, DC,УУ | INR L |

- Приведите структурную схему микропроцессора любого из микропроцессорных комплектов серии КР580, 589, 1804, 1810, 1816.

- Объясните какие функции выполняет микропроцессор (МП).

- На структурной схеме выделите узлы, указанные в табл. 10. для Вашего варианта.

- Кратко опишите назначение выделенного узла

- Запишите мнемокод команды, заданной в табл. 10. Укажите содержание и формат команды. Запишите шестнадцатеричный и двоичный код заданной команды.

- Приведите структурную схему контроллера или блока управления на безе данного МП

- Кратко укажите назначение основных блоков устройства.

- Приведите технические характеристики данного устройства (производительность, быстродействие, разрядность, частота, максимально адресуемый объем памяти, разрядность информационной шины, максимальная пропускная способность шины, наличие дополнительных технологий для повышения производительности)