Реферат По истории информатики на тему

| Вид материала | Реферат |

- Реферат По истории информатики на тему " Философские проблемы информатики", 141.31kb.

- Реферат По истории информатики на тему, 180.86kb.

- Реферат По истории информатики на тему, 200.63kb.

- Реферат По истории информатики на тему, 316.82kb.

- Реферат По истории информатики на тему " Электронная коммерция", 323.12kb.

- Реферат По истории информатики на тему " Эволюция понятия «информация»", 151.89kb.

- Реферат По истории информатики на тему " История развития электронных денег", 290.65kb.

- Реферат По истории информатики на тему " Поколения ЭВМ история и периодизация", 306.89kb.

- Реферат По истории информатики на тему " История развития операционных систем", 415.46kb.

- Реферат По истории информатики на тему " История развития сервис-ориентированной архитектуры.", 214.25kb.

Санкт Петербургский государственный университет информационных технологий механики и оптики

Реферат

По истории информатики на тему

“История развития ПЛИС”

-

Аспирант:

Юхта П.В.

Специальность:

05.13.05

Санкт-Петербург

2009 г.

Оглавление

Введение 3

1.История развития ПЛИС 3

2.Развитие ПЛИС (CPLD) 4

3.Развитие ПЛИС (FPGA) 7

4.Программируемые системы на кристалле Cypress PSoC 10

Заключение 12

Список литературы 12

Введение

Приборы программируемой логики, яркими представителями которых являются ПЛИС (Программируемые Логические Интегральные Схемы) применяются на протяжении нескольких десятилетий для построения разнообразных интерфейсных узлов, устройств управления и контроля и т.д. Однако, если еще 10 лет назад ПЛИС занимали весьма скромную нишу на рынке электронных компонентов - (в первую очередь из-за небольшого быстродействия и малого количества эквивалентных логических вентилей), то сейчас ситуация изменилась кардинально. Раньше о ПЛИС говорили, в основном, как об «игрушках», недостойных внимания серьезных разработчиков, но с появлением быстродействующих ПЛИС сверхвысокой интеграции, работающих на высоких тактовых частотах, их ниша на мировом рынке значительно расширилась. Современные образцы ПЛИС, выполненные по 0,04-микронной технологии, способны работать на частотах до 600 МГц и реализуют до 4 млн. логических ячеек. Столь резкое увеличение мощности ПЛИС позволяет использовать их не только для реализации простых контроллеров и интерфейсных узлов, но и для цифровой обработки сигналов, сложных интеллектуальных контроллеров и нейрочипов. Появление быстродействующих ПЛИС со сверхнизким уровнем энергопотребления открывает широкие возможности по их использованию в системах мобильной связи (в частности, непосредственно в сотовых телефонах и пейджерах), в портативных проигрывателях (например, в МР3-проигрывателях) и т.д.

-

История развития ПЛИС

История развития программируемых логических интегральных схем (ПЛИС) начинается с появления в начале 70-х годов программируемых постоянных запоминающих устройств (ППЗУ - Programmable Read Only Memory - PROM). Первое время PROM использовались исключительно для хранения данных, позже их стали применять для реализации логических функций. Однако необходимость приведения логических функций к совершенной дизъюнктивной нормальной форме (СДНФ) не позволяло применять PROM для реализации функций больших размеров.

Первые программируемые логические устройства создавались на основе технологии биполярных программируемых ПЗУ с дополнительными логическими возможностями и свойствами. Пробудить интерес к программируемой логике сумела фирма Signetics, выпустившая в 1972 году биполярную микросхему программируемой логической матрицы типа 82S100. Совершенствование архитектуры привело к созданию фирмой Monolithic Memories Inc. (MMI) в 1975–1976 годах микросхем программируемой матричной логики (PAL), монтируемых в 20- и 24-выводные корпуса и способных заменить до 20 имевшихся в продаже логических вентилей. Одновременно с PAL-микросхемами компания MMI предложила и простой язык программирования – PALASM, позволивший достаточно легко преобразовывать логические уравнения в битовую конфигурацию. Хотя сегодня компании MMI уже нет, ее разработки легли в основу современной агрессивной технологии, пригодной для масштабирования элементов ПЛИС и увеличения их быстродействия. Выпущенная в 1979 году компанией Advanced Micro Devices (AMD) микросхема типа 22V10, в которой использовалось встроенное СППЗУ с программируемыми УФ-излучением ячейками памяти, стала основной и на протяжении нескольких последующих лет воспроизводилась многими поставщиками ПЛИС. А в 1984-м фирма Altera выпустила первую микросхему CPLD на основе УФ-программируемого СППЗУ, содержащую 300 вентилей. В 1985-м Xilinx предложила хранить конфигурационные данные в ячейках СОЗУ, что позволило изменять логику путем корректировки данных, записанных в ячейки памяти. Микросхема ПЛИС типа ХС2010 этой компании, содержавшая ~2 тыс. вентилей, положила начало широко распространенным сегодня FPGA. Но и FPGA на основе СОЗУ не единственные конфигурируемые устройства, предлагаемые разработчикам. Во второй половине 90-х годов компания Gatefield, приобретенная в 2000 году фирмой Actel, создала FPGA на базе флэш-технологии. И уже сегодня логическая емкость микросхем ПЛИС с конфигурационной флэш-памятью превышает 1 млн вентилей.

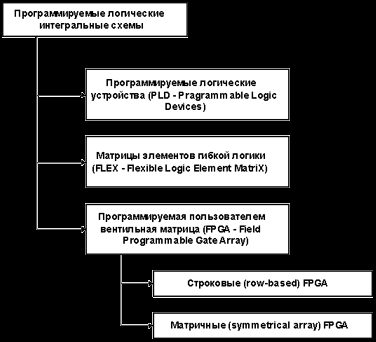

К классу программируемых логических приборов относятся простые и сложные ПЛИС (SPLD и CPLD, соответственно), а также программируемые пользователем базовые матричные кристаллы (FPGA) и программируемые системы на кристалле, PSoC.

Рисунок 1. Одна из классификаций ПЛИС

Сегодня, некоторые производители ПЛИС предлагают процессоры для своих ПЛИС, которые могут быть модифицированы под конкретную задачу, и затем встроены в ПЛИС, тем самым уменьшить место на печатной плате и упростив разработку для самой ПЛИС.

-

Развитие ПЛИС (CPLD)

CPLD – это комбинация полностью программируемых матриц вентилей И/ИЛИ и банка макроячеек (МЯ). МЯ образуют функциональные блоки, выполняющие различные комбинаторные или последовательные логические функции. Для получения достаточно высокого быстродействия в CPLD традиционно применялся аналоговый усилитель считывания, но при этом существенно возрастала потребляемая мощность. В CPLD семейства CoolRunner-II компания Xilinx отказалась от биполярного усилителя, создав полностью цифровое ядро, и сумела добиться высокой производительности при низкой потребляемой мощности. К тому же это облегчило масштабирование архитектуры и тем самым позволило существенно снизить стоимость CPLD-микросхем и успешно совершенствовать характеристики каждого нового их поколения.

Современные CPLD содержат несколько логических блоков (ЛБ), в каждый из которых могут входить до 2000 МЯ на основе программируемых логических матриц (PAL) или простых ПЛИС (SPLD). Каждая МЯ с большой нагрузочной способностью по входу обеспечивает выполнение комбинаторной логики, которая в зависимости от сложности ПЛИС поддерживает от четырех до 16 логических произведений – термов. Поскольку каждый ЛБ выполняет определенную функцию, все МЯ такого блока полностью объединены, тогда как сами ЛБ соединяются друг с другом трассировочной матрицей в зависимости от применения микросхемы. В результате 100%-ного использования имеющихся логических блоков добиться нельзя.

Основными производителями микросхем CPLD являются:

Altera

На протяжении многих лет компания практически не изменяла архитектуру микросхем ведущего семейства CPLD – MAX 7000 (появилась в 1993), добиваясь увеличения быстродействия и числа логических МЯ, а также снижения рабочего напряжения и потребляемой мощности лишь за счет совершенствования методов изготовления и уменьшения размеров элементов схемы. Пожалуй, самое существенное изменение в архитектуре микросхем компании за последние годы – введение внутрисхемного программирования, начиная с серий микросхем на напряжение питания 5 В и меньше. К достоинствам своих CPLD компания относит и технику многовольтного ввода/вывода (MultiVolt I/O), позволяющую подавать на выход и принимать на входе сигналы с уровнем напряжения ниже или выше рабочего напряжения ядра и не требующую применения связующей логики.

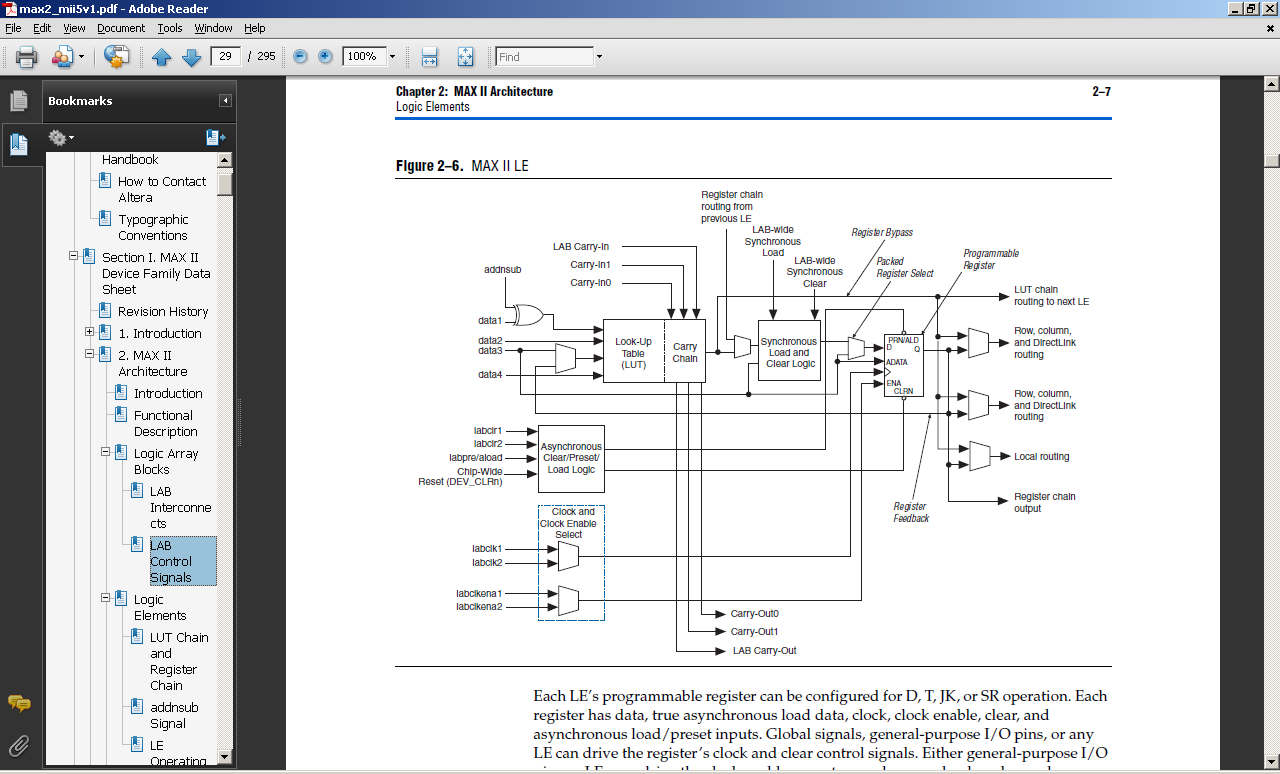

Выпущенные компанией Altera в начале 2004 года после почти 15-летнего затишья в разработке новых архитектурных решений дешевые CPLD-микросхемы семейства MAX II следует рассматривать как важный шаг на пути развития этой технологии. При разработке микросхем семейства MAX II компания поставила перед собой цель достичь малой динамической мощности, высокой плотности упаковки элементов, высокого быстродействия, энергонезависимости конфигурационной памяти, низкой стоимости и привычной для разработчиков систем на ПЛИС среды проектирования. При построении архитектуры новой микросхемы компания приняла неожиданное решение: традиционно используемые в CPLD МЯ на основе программируемой матричной логики заменить присущими FPGA таблицами соответствия (LUT). В сравнении с обычными CPLD новая микросхема характеризуется большей плотностью упаковки, меньшей динамической мощностью и более высокой производительностью.

Появление нового семейства CPLD, очевидно, свидетельствует о решении компании вернуться к изделиям, которые собственно и "сделали" ее, и вложить серьезные технические средства в развитие ПЛИС этого типа. На основе проявленного интереса потребителей к микросхемам нового семейства Altera прогнозирует существенный рост продаж CPLD, которые в конечном итоге могут возрасти с современного уровня в ~500 млн. долл. до 2 млрд. долл. ежегодно. А это значит, что CPLD будут успешно конкурировать с ПЛИС на пережигаемых перемычках и FPGA с энергонезависимой памятью. Правда, вряд ли компания пойдет на "поедание" доли рынка собственных FPGA семейства Cyclone.

Рисунок 2. Пример макроячейки семейства MAX II

Atmel

Компания Atmel выпускает как микросхемы промышленного стандарта, так и микросхемы, полностью совместимые сверху вниз с популярными ПЛИС PAL- и CPLD-типов. Микросхемы компании серии ATF1500 на основе ЭСРПЗУ с 32–512 МЯ совместимы по выводам с CPLD МAX 7000 фирмы Altera при расширенных функциональных возможностях и высокой гибкости. Принятая компанией технология Logic Doubling (удвоения логики) позволяет увеличить число входов макроячейки и соответственно подаваемых термов с пяти до 40, поддерживать многочисленные независимые цепи обратной связи, раздельное разрешение вывода данных, конфигурируемые D/T-триггеры и триггеры-защелки, а также реализовать опциональный режим защелки для триггеров МЯ. Все это, по утверждению разработчиков, позволило расширить ресурсы микросхемы на 200% и тем самым обеспечить реализацию проектов, не "умещающихся" на ПЛИС конкурентов с аналогичным числом МЯ. Напряжение питания составляет 3,3 или 5 В. Микросхемы допускают 10 тыс. циклов программирования при гарантированном сроке хранения запрограммированной конфигурации не менее 20 лет.

Xilinx

Не оставляет без внимания рынок CPLD и крупнейший производитель ПЛИС с FPGA-архитектурой, выпускающий несколько семейств таких микросхем, – компания Xilinx. CPLD серий ХС9500, CoolRunner, CoolRunner XPLA3 и CoolRunner-II. Интерес компании к ПЛИС этого типа связан с совершенствованием технологии и снижением издержек производства, улучшением производительности и надежности, благодаря чему расширяется их применение для реализации конструкций на базе устаревших "дискретных" логических микросхем. В 2003 году доля компании на рынке CPLD составила 21% против 18% в 2002-м.

-

Развитие ПЛИС (FPGA)

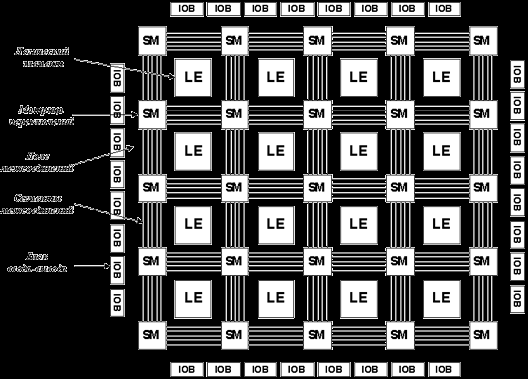

Типичная FPGA - это микросхема, которая состоит из массива абсолютно одинаковых ячеек с программируемыми соединениями. Пользователь может запрограммировать функции, которые будут выполняться каждой из логических ячеек, и соединения между ними. Такие PGA часто называются FPGA, поскольку они являются программируемыми в условиях эксплуатации.

Основу структуры FPGA составляет матрица логических элементов (LogicElement - LE), между которыми располагается поле межсоединений: совокупность горизонтальных и вертикальных каналов. В FPGA линии каналов состоят из отдельных сегментов, соединяемых программируемыми матрицами переключений. По краям кристалла FPGA расположены блоки ввода-вывода (Input/OutputBlocks - IOBs).

В 1985 произошел запуск производства первой FPGA-микросхемы, Xilinx XC2064 с 1000 вентилей. В ней применялась 3-микронная технология.

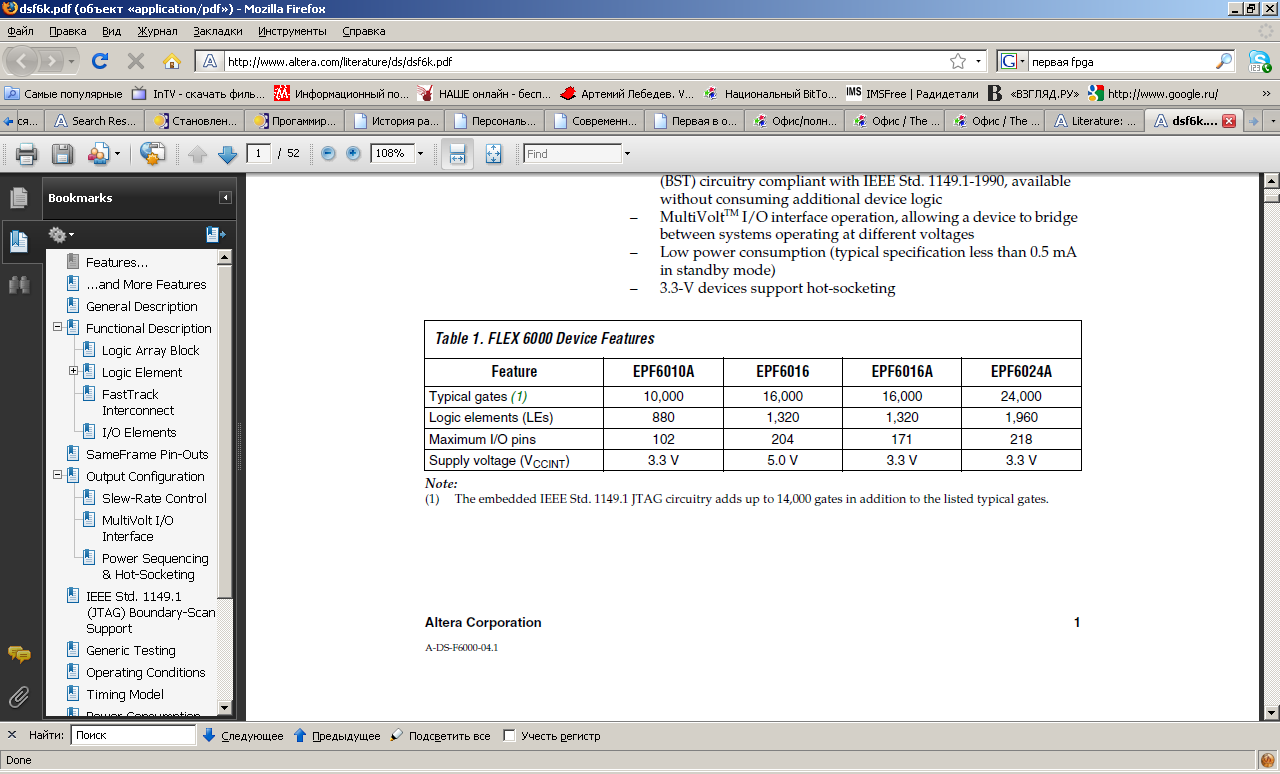

В 1994 компания Altera вышла на рынок с FPGA устройствами семейства FLEX.

Таблица 1. Характеристики семейства FLEX6000

В 1995 году, фирма алтера создала партнерство AMPP по разработке IP-ядер – готовых блоков для ПЛИС. Последныы разработка - собственный процессор Nios II корпорации Altera - единственное программное ядро среди десятка лучших процессоров, которое наиболее широко используется системными проектировщиками сегодня. В дополнение к процессору Nios, корпорация Altera предлагает большое количество комплексных IP функций системного уровня, оптимизированных для приборов корпорации Altera. Эта библиотека IP ядер содержит частные и залицензированные ядра, что дает возможность нашим потребителям дифференцировать их конструкции и эффективно формировать законченное системное решение на одном программируемом кристалле. Разработанные, перепроверенные и залицензированные корпорацией Altera функции Altera MegaCore® обеспечивают разработчиков широким набором функций от ведущих/целевых PCI интерфейсов до фильтров с конечной импульсной характеристикой (FIR). Интеллектуальную собственность можно получить через программу Altera Megafunction Partners Program (AMPP), которая подразумевает заключения договора между корпорацией Altera и разработчиками с целью оптимизации и разработки новых функций.

Современные FPGA

FPGA фирмы Altera

- Cyclone FPGA FPGA микросхемы семейства Cyclone выполнены по 0.13 мкм SRAM технологии с медной металлизацией и напряжением питания ядра 1.5В.

- Cyclone II FPGA FPGA микросхемы семейства Cyclone II выполнены по 90 нм SRAM технологии с медной металлизацией и напряжением питания ядра 1.2В.

- Cyclone III FPGA FPGA микросхемы семейства Cyclone III выполнены по 65 нм SRAM технологии фирмы Taiwan Semiconductor Manufacturing Company. Рабочий диапазон температур - от -40 до +125 градусов Цельсия. Как и в предыдущих сериях, аппаратные ядра не предусмотрены, однако, помимо синтезируемого 32-разрядного ядра процессоров NiosII, для данной архитектуры разработано специальное синтезируемое 32-разрядное ядро процессора Cortex-M1 фирмы ARM. Учёт архитектуры Cyclone III при его разработке позволяет работать данному синтезируемому ядру существенно быстрее, чем NiosII. При реализации Cortex-M1 в ПЛИС с показателем быстродействия "-6" достигается тактовая частота 100 МГц. Для задач цифровой обработки сигналов в платах реализовано до 288 18-битных умножителей, работающих на эффективной частоте 260 МГц.

- Stratix FPGA Семейство микросхем программируемой логики Stratix выполнено по технологии 0.13 мкм SRAM конфигурацией и медной металлизацией.

- Stratix GX FPGA Семейство микросхем программируемой логики Stratix GX выполнено по технологии 0.13 мкм SRAM конфигурацией и медной металлизацией, с оптимизацией для приложений, требующих передачи данных до 3.125 Гбит/с.

- Stratix II FPGA Семейство микросхем программируемой логики Stratix II выполнено по технологии 90 нм - 1.2 В.

- Stratix II GX FPGA Как и Arria GX, Stratix II GX оптимизирован для работы с протоколами ввода-вывода для обеспечения более полной загрузки системы. Технология 90 нм.

- Arria GX FPGA (2007) Arria GX - первая FPGA, оптимизированная для работы с протоколами ввода-вывода (теми же, что используются в Stratix II GX). Технология 90 нм.

- Stratix III FPGA (2006) Семейство Stratix III FPGA имеет два варианта устройств: Stratix III L - для приложений со сложной логикой, и Stratix III E - для приложений типа обработки сигналов и с активной работой оперативной памяти. Основанное на 65-нм технологии, даёт выигрыш до 50% в энергопотреблении по сравнению с предыдущим поколением - Stratix II, давая в то же время повышение скорости работы до 35%. Технология 65 нм.

FPGA фирмы Xilinx

- Virtex/E/EM FPGA Было выпущено в октябре 1999 года. Технология производства 0.18 мкм SRAM.

- Virtex-II FPGA Было выпущено в начале 2001 года. ПЛИС семейства Virtex-II реализуют новую идеологию Platform FPGA, подразумевающую что ПЛИС становится основным компонентом цифрового устройства. Технология 0.15 мкм.

- Virtex-II Pro FPGA Было выпущено в 2002 году. Архитектура основана на архитектуре семейства Virtex-II, но добавились блоки процессора PowerPC-405, что позволяет программировать непосредственно в кодах этого процессора, а также блоки последовательных приемо-передатчиков со скоростью передачи данных 3.125 ГБит/с, в кристаллах Virtex-II ProX - 10.3125 Гбит/с. Повышено внутреннее быстородействие элементов кристалла - технология 0.13 мкм.

- Virtex-4 FPGA Семейство Virtex-4 - ПЛИС фирмы Xilinx с архитектурой FPGA 90-нм. Инновационная ASMBL-архитектура (Advanced Silicon Modular Block) являлась уникальной в индустрии программируемой логики. ПЛИС семейства Virtex-4 включает три подсемейства (платформы): LX, FX и SX. Как и в Virtex-II Pro, присутствуют аппаратно реализованные блоки процессора PowerPC-405 и блоки последовательных приемо-передатчиков.

- FPGA Xilinx Virtex-5 (2007) предназначены для быстродействующих приложений, взаимодействующих с последовательными шинами с пропускной способностью от 100 Мбит/с до 3,2 Гбит/с. В состав Virtex-5 включены аппаратные блоки PCI Express (PCIe) и MAC-адаптера Ethernet 10/100/1000 Мбит/с. Virtex-5 обеспечивают на 30% более высокое быстродействие, на 65% большее количество логических узлов и потребляют на 35% меньше электроэнергии, чем 90-нм FPGA. Для обеспечения быстродействия приложений цифровой обработки сигналов вместо ядра PowerPC-405 в предшествующих сериях вставлено аппаратное ядро DSP48E, реализующее параллельное перемножение с возможностью 48-разрядного и 96-разрядного накопления на рабочей частоте 550 МГц (для 48-разрядных результатов).

- Spartan-3E FPGA Семейство Spartan-3E специально разработано для использования в электронных устройствах, рассчитанных на большие тиражи и недорогие комплектующие. Семейство Spartan-3E является дальнейшим развитием семейства Spartan-3. Увеличение отношения логической ёмкости к количеству блоков ввода-вывода позволило существенно снизить себестоимость кристаллов в перерасчете на одну логическую ячейку. Технологический процесс 90 нм. Аппаратных ядер нет, есть поддержка синтезируемых ядер микропроцессоров MicroBlaze (32-бит) и PicoBlaze (8-бит).

- Spartan-3 FPGA 1.2В серия семейства ПЛИС с архитектурой FPGA (Field-Programmable Gate Arrays) Spartan-3 специально разработана для использования в электронных устройствах, рассчитанных на большие тиражи и невысокую стоимость комплектующих. Технологический процесс 90 нм. Аппаратных ядер нет, есть поддержка синтезируемых ядер микропроцессоров MicroBlaze (32-бит) и PicoBlaze (8-бит).

Рисунок 3. Типичная структура ПЛИС FPGA

-

Программируемые системы на кристалле Cypress PSoC

С появлением программируемых систем на кристалле (PSoC) фирмы Cypress разработчики получили мощный инструмент для проектирования; система на кристалле по цене восьмибитного микроконтроллера. В чипах PSoC встроены массивы аналоговых и цифровых блоков, на порядок более функциональных, чем фиксированная периферия. Такие стандартные элементы микроконтроллеров как АЦП, ЦАПы, таймеры, счетчики,ШИМы, UART легко реализуются в PSoC. Кроме того, элементы обычно не входящие в состав 8-битных м/к, такие как фильтры, усилители, генераторы случайных чисел также можно разместьть в этих чипах. Таким образом одна микросхема PSoC заменяет несколько компонентов схемы построенной на стандартных микроконтроллерах. Все функции, внутренние соединения, внутренняя конфигурация, и даже контакты ввода вывода перепрограммируются пользователем.

Микросхемы PSoC Cypress впервые появились в 2001 году. Фактически это был прорыв в развитии микроконтроллеров, значительно упростивший процесс разработки электронных систем. На сегодняшний день выпускается несколько серий PSoC микроконтроллеров:

- CY8C21xxx

- CY8C22xxx

- CY8C24xxx

- CY8C27xxx

- CY8C29xxx

Все микросхемы построены на базе восьмиразрядного ядра М8С гарвардской архитектуры с тактовой частотой 24МГц и производительностью 4MIPS. Система команд достаточно проста в освоении и характеризуется высокой плотностью кода. Встроенные RC генераторы на 24 МГц и 32КГц позволяют приложениям некритичным к высокой стабильности частоты обойтись без внешнего кварца.

Объем ОЗУ 256-2048 байт.

Объем ПЗУ 2-64Кбайта. ПЗУ реализовано на основе перепрограммируемой флэш памяти допускающей до 100000 циклов записи/стирания. Организация флэш-ПЗУ в виде массива из секторов размером 64 байт дает дополнительную возможность для эмуляции EEPROM внутри PSoC. Но самое интересное и полезное качество микроконтроллеров PSoC состоит во внутренней аналоговой и цифровой периферии. Наиболее распространенная микросхема PSoC CY8C27443, на примере которой выше была показана возможность создания электронного компаса, содержит 12 аналоговых и 8 цифровых блоков.

Каждый цифровой блок построен на основе восьмиразрядного регистра и, на начальном этапе проектирования, представляет собой функционально неопределенный ресурс. Пользователь в программной среде PSoC Designer может доопределить топологию схемы цифрового блока, заставив его работать как восьмибитный счетчик/таймер/шим/...Использовав несколько цифровых блоков соединенных между собой можно получать модули более высокой разрядности (например те же счетчики, шимы или таймеры разрядностью 8, 16, 24 или 32 бита). Процесс конфигурации системы упрощается за счет использования библиотеки модулей пользователя, которые представляют собой заранее сконфигурированные и протестированные PSoC блоки. Пользователь осуществляет процесс построения системы на высоком уровне путем выбора готовых модулей из библиотеки.

Аналоговая часть PSoC построена на базе аналоговых блоков трех видов: аналоговый блок с операционным усилителем и программируемой матрицей резисторов в цепи обратной связи и два типа аналоговых блоков на основе операционного усилителя и переключаемых конденсаторов. Дело в том, что при некоторых допущениях резистор можно заменить конденсатором и двумя коммутируемыми ключами. И резисторная и конденсаторная топология параллельно используются внутри PSoC, так как для разных задач та или иная схема более или менее приемлема. Так, например, на основе резисторных аналоговых блоков строятся программируемые усилители и аналоговые компараторы. На основе конденсаторных аналоговых блоков внутри PSoC можно реализовать полосовой или низкочастотные фильтры. Комбинируя между собой цифровые и аналоговые блоки можно получить ЦАПы и АЦП разрядностью от 6 до 14 бит.

Еще раз хочется подчеркнуть, что весь процесс конфигурации выполняется на высоком уровне с помощью графического интерфейса и библиотеки модулей интегрированной среды PSoC Designer. Пользователю не придется задумываться какую, резисторную или конденсаторную архитектуру выбрать. В PSoC Designer этот процесс автоматизирован.

Для связи с внешними устройствами микросхемы PSoC поддерживают интерфейсы RS232, I2C, SPI, UART. Есть встроенный драйвер ЖКИ контроллера Hitachi HD44780 и внутренний датчик температуры. Без калибровки показания датчика температуры очень грубые и позволяют производить только приближенную оценку температуры без внешнего терморезистора.

В последние годы Cypress ведет интенсивную работу над созданием PSoC микросхем с USB интерфейсом и PSoC микросхем с интегрированными силовыми транзисторами (напряжение до 36В и ток до 1А на каждом силовом выходе). На сегодняшний день доступны первые образцы.

Заключение

Современные ПЛИС широко используется для построения различных по сложности и возможностям цифровых устройств.

Это приложения, где необходимо большое количество портов ввода-вывода (бывают ПЛИС с более чем 1000 выводов, цифровая обработка сигнала (ЦОС), цифровая видео-аудио аппаратура, высокоскоростная передача данных, криптография, проектирование ASIC, в качестве мостов (коммутаторов) между системами с различной логикой и напряжением питания.

Список литературы

- altera.com

- xilinx.com

- cypress.com

- altera.ru

- Cистемы автоматизированного проектирования фирмы Altera - MAX+PLUS II и QUARTUS II, Д.А. Комолов, Р.А. Мяльк, А.А. Зобенко, А.С. Филиппов, М: Радио-СОФТ, 2002