Лекция 1 История развития вычислительной техники. Цель

| Вид материала | Лекция |

СодержаниеЦель: Познакомить с основными способами представления информации в вычислительных системах.План Система счисления Представление чисел с фиксированной и плавающей запятой М — мантисса числа (|М| Особенности представления информации в ПК Физическая и функциональная структура микропроцессора Соrе — ядро МП; О Ехесutioп иnit — Сасhе); О Instruction Decode and Prefetch Unit и Branch Predictor — Устройство управления Арифметико-логическое устройство Схемы управления Микропроцессорная память Универсальные регистры Сегментные регистры Регистры смещений Регистр флагов Интерфейсная часть МП Вопросы для самопроверки Операционная часть Безадресная команда ... 3 4 Тема: «Представление информации в ЭВМ» ^ Цель: Познакомить с основными способами представления информации в вычислительных системах. План:

Системы счисления Информация в компьютере кодируется в двоичной или в двоично-десятичной системах счисления. ^ Система счисления — способ именования и изображения чисел с помощью символов, имеющих определенные количественные значения. В зависимости от способа изображения чисел системы счисления делятся:

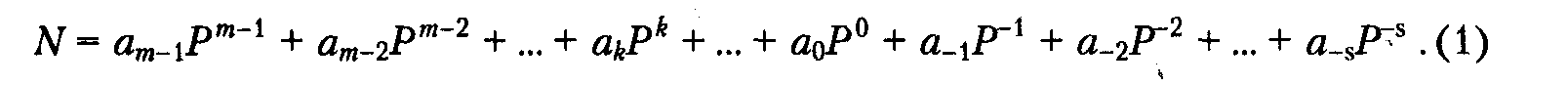

В позиционной системе счисления количественное значение каждой цифры зависит от ее места (позиции) в числе. В непозиционной системе счисления цифры не меняют своего количественного значения при изменении их расположения в числе. Количество (Р) различных цифр, используемых для изображения числа в позиционной системе счисления, называется основанием системы счисления. Значения цифр лежат в пределах от 0 до Р - 1. В общем случае запись любого смешанного числа в системе счисления с основанием Р будет представлять собой ряд  Нижние индексы определяют местоположение цифры в числе (разряд):

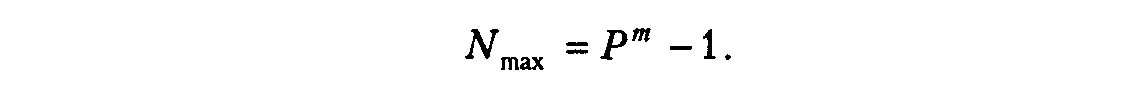

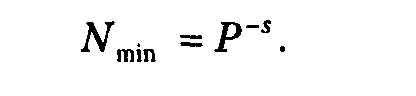

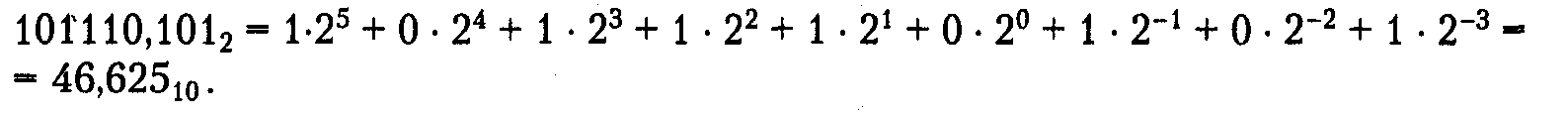

Максимальное целое число, которое может быть представлено в т разрядах,  (2) (2)Минимальное значащее, не равное 0 число, которое можно записать в S разрядах дробной части,  (3) (3)Имея в целой части числа m, а в дробной — S разрядов, можно записать всего Р m+s разных чисел. Двоичная система счисления имеет основание Р = 2 и использует для представления информации всего две цифры — 0 и 1. Существуют правила перевода чисел из одной системы счисления в другую, основанные в том числе и на соотношении (1). Например, двоичное число 101110,101 равно десятичному числу 46,625:  Практически перевод из двоичной системы в десятичную можно легко выполнить, надписав над каждым разрядом соответствующий ему вес и сложив затем произведения значений соответствующих цифр на их веса. Двоичное число 01000001; равно 6510. Действительно, 64 • 1 + 1 • 1 = 65.

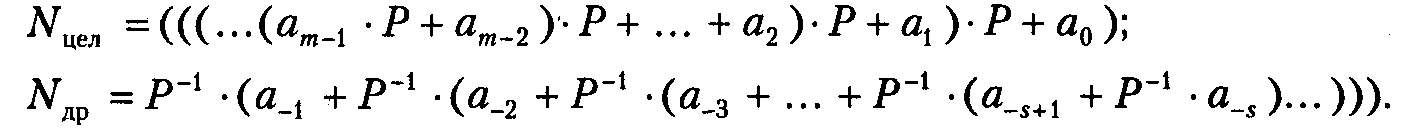

Таким образом, для перевода числа из позиционной системы счисления с любым основанием в десятичную систему счисления можно воспользоваться выражением (1). Обратный перевод из десятичной системы счисления в систему счисления с другим основанием непосредственно по формуле (1) для человека весьма затруднителен, поскольку все арифметические действия, предусмотренные этой формулой, следует выполнять в той системе счисления, в которую число переводится. Обратный перевод выполняется значительно проще, если предварительно преобразовать отдельно целую Nцел, и дробную Nдр части выражения (1) к виду  Алгоритм перевода числа из десятичной системы счисления в систему счисления с основанием Р, основанный на этих выражениях, позволяет оперировать с числами в той системе счисления, из которой число переводится, и может быть сформулирован следующим образом: 1. При переводе смешанного числа следует переводить его целую и дробную части отдельно. 2. Для перевода целой части числа ее, а затем целые части получающихся частных от деления следует последовательно делить на основание Р до тех пор, пока очередная целая часть частного не окажется равной 0. Остатки от деления, записанные последовательно справа налево, образуют целую часть числа в системе счисления с основанием Р. 3. Для перевода дробной части числа ее, а затем дробные части получающихся произведений следует последовательно умножать на основание Р до тех пор, пока очередная дробная часть произведения не окажется равной 0 или не будет достигнута нужная точность дроби. Целые части произведений, записанные после запятой последовательно слева направо, образуют дробную часть числа в системе счисления с основанием Р. Рассмотрим перевод смешанного числа из десятичной в двоичную систему счисления на примере числа 46,625. Переводим целую часть числа: 46/2 = 23 (остаток 0). 23/2 = 11 (остаток 1). 11/2 = 5 (остаток 1); 5/2 = 2 (остаток 1); 2/2 =1 (остаток 0); 1/2 = 0 (остаток 1). Записываем остатки последовательно справа-налево — 101110, то есть 4610 = 101110,1012. Переводим дробную часть числа: 0,625 • 2 = 1,250; 0,250 • 2 = 0,500; 0,500 • 2 = 1,000. Записываем целые части получающихся произведений после запятой последовательно слева направо — 0,101, то есть: 0,62510 = 0,1012. Окончательно 46,62510 = 101110,1012. ^ Представление чисел с фиксированной и плавающей запятой В вычислительных машинах применяются две формы представления двоичных чисел:

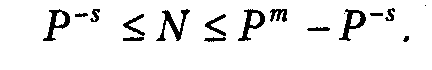

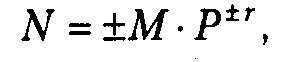

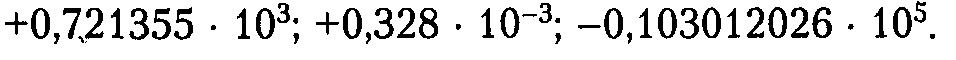

В форме представления с фиксированной запятой все числа изображаются виде последовательности цифр с постоянным для всех чисел положением запятой, отделяющей целую часть от дробной. Например: в десятичной системе счисления имеется 5 разрядов в целой части числа (до запятой) и 5 разрядов в дробной части числа (после запятой); числа, записанные в такую разрядную сетку, имеют вид: +00721,35500; +00000,000328; -10301,20260. Эта форма наиболее проста, естественна, но имеет небольшой диапазон преставления чисел и поэтому чаще всего неприемлема при вычислениях. Диапазон значащих чисел N в системе счисления с основанием Р при наличии т разрядов в целой и s разрядов в дробной части числа (без учета знака числа) 6удет таким:  Например, при Р=2,m=10 и s=6 числа изменяются в диапазоне 0,015 <М< 1024. Если в результате операции получится число, выходящее за допустимые пределы, произойдет переполнение разрядной сетки и дальнейшие вычисления потеряют смысл. В современных компьютерах естественная форма представления используется как вспомогательная и только для целых чисел. В форме представления с плавающей запятой каждое число изображается в в виде двух групп цифр. Первая группа цифр называется мантиссой, вторая — порядком, причем абсолютная величина мантиссы должна быть меньше 1, а порядок — целым числом. В общем виде число в форме с плавающей запятой может быть представлено так:  где ^ М — мантисса числа (|М| < 1); r — порядок числа (целое число); Р — основание системы счисления. Например, приведенные ранее числа в нормальной форме запишутся так:  Нормальная форма представления имеет огромный диапазон отображения чисел и является основной в современных компьютерах. Так, диапазон значащих чисел в системе счисления с основанием Р при наличии т разрядов у мантиссы и s разрядов у порядка (без учета знаковых разрядов порядка и мантиссы) будет  Приведем пример. При Р = 2, т = 22 и s = 10 диапазон чисел простирается примерно от 10-300 до 10300. Для сравнения: количество секунд, которые прошли с момента образования планеты Земля, составляет всего 1018. Следует заметить, что все числа с плавающей запятой хранятся в машине в так называемом нормализованном виде. Нормализованным называют такое число, в старшем разряде мантиссы которого стоит единица. У нормализованных двоичных чисел, следовательно,  . .^ Особенности представления информации в ПК Числовая информация внутри ПК кодируется в двоичной или в двоично-десятичной системах счисления; при вводе и выводе любой информации используются специальные коды представления информации — коды ASCII, эти же коды применяются для кодирования буквенной и символьной информации и внутри ПК. Для удобства работы введены следующие термины для обозначения совокупностей двоичных разрядов (см. табл. 1). Эти термины обычно используются в качестве единиц измерения объемов информации, хранимой или обрабатываемой в компьютере. Последовательность нескольких битов или байтов часто называют полем данных. Биты в числе (в слове, в поле и т. п.) нумеруются справа налево, начиная с 0-го разряда. В ПК могут обрабатываться поля постоянной и переменной длины. Поля постоянной длины:

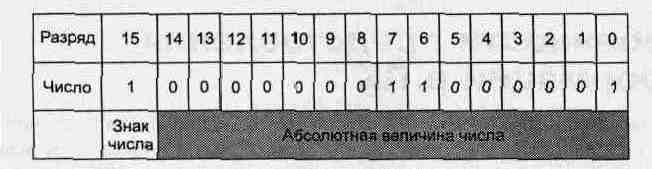

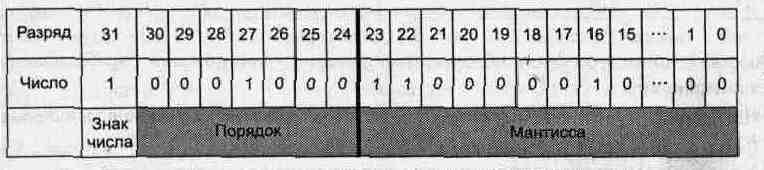

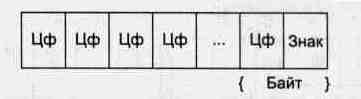

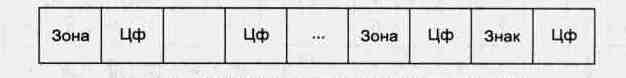

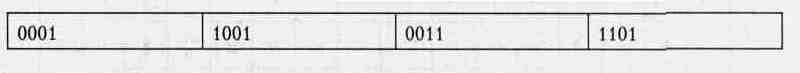

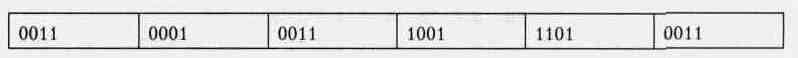

Числа с фиксированной запятой чаще всего имеют формат слова и полуслова; числа с плавающей запятой — формат двойного и расширенного слова (математические сопроцессоры IВМ РС могут работать с 10-байтными словами). Поля переменной длины могут иметь любой размер от 0 до 255 байтов, но обязательно равный целому числу байтов. Структурно запись двоичного числа -11000001(2), равного десятичному -193(ю), в разряд- ной сетке ПК, выглядит следующим образом (рис. 1, 2).  Рис. 1  Рис. 2 Двоично-кодированные десятичные числа могут быть представлены в ПК полями переменной длины в так называемых упакованном (рис. 5.3) и распакованном форматах. В упакованном формате для каждой десятичной цифры отводится по 4 двоичных разряда (полбайта), при этом знак числа кодируется в крайнем правом полубайте числа (1100 — знак «+» и 1101 — знак «-»).  Рис. 3 Здесь и далее: Цф — цифра, Знак — знак числа. Упакованный формат используется в ПК обычно при выполнении операций сложения и вычитания двоичнодесятичных чисел. В распакованном формате (рис. 4) для каждой десятичной цифры выделяется по целому байту, при этом старшие полубайты (зона) каждого байта (кроме самого младшего) в ПК заполняются кодом 0011 (в соответствии с ASCII-кодом), а в младших (левых) полубайтах обычным образом кодируются десятичные цифры. Старший полубайт (зона) самого младшего (правого) байта используется для кодирования знака числа.  Рис. 4 Распакованный формат используется в ПК при вводе-выводе информации, а также при выполнении операций умножения и деления двоично-десятичных чисел. Например, число -19310= -000110010011(2-10) в ПК будет представлено: О в упакованном формате:  О в распакованном формате:  Код ASCII (American Standart Code for Information — американский стандартный код для обмена информацией) имеет основной стандарт и его расширение. Основной стандарт для кодирования символов использует шестнадцатеричные коды 00-7F, расширение стандарта — 80-FF. Основной стандарт является международным и применяется для кодирования управляющих символов, цифр, знаков пунктуации, букв латинского алфавита и других символов; в расширении стандарта кодируются символы псевдографики и буквы национального алфавита (естественно, в разных странах разные). Пользоваться таблицей довольно просто. Следует приписать шестнадцатеричную цифру номера строки справа к шестнадцатеричной цифре номера столбца. Так получится шестнадцатеричный код символа. Вопросы для самопроверки 1. Что такое система счисления? 2. Какие системы счисления используются для представления информации в ком- пьютерах? 3. Выполните несколько операций перевода чисел из десятичной системы счис- ления в двоичную и обратно. 4. Выполните несколько операций перевода чисел из десятичной системы счис- ления в двоично-десятичную и обратно. 5. Дайте краткую характеристику форм представления информации с фиксиро- ванной и плавающей запятой (точкой). 6. Дайте краткую характеристику кодов алгебраического представления чисел (прямого, обратного, дополнительного). 7. Выполните ряд операций сложения и умножения чисел в дополнительных кодах с фиксированной и плавающей запятой (точкой). 8. Назовите наименования основных двоичных совокупностей в компьютерах и определите их размер. 9. Что такое поля данных постоянной и переменной длины? Какова их разряд- ность в персональных компьютерах? 10. Что такое ASCII-коды? Приведите их структуру и укажите назначение. 11. Рассмотрите и запомните ASCII-коды представления десятичных ци Лекция 4 Тема: ^ Физическая и функциональная структура микропроцессора Цель: Изучение физической и функциональной структуры икропроцессора Intel Pentium Знать: физическую структуру и функциональное назначение структурных элементов микропроцессора, классификацию и назначение регистров. Уметь : Изображать функциональную схему микропроцессора Физическая структура микропроцессора достаточно сложна. Ядро процессора содержит главный управляющий и исполняющие модули — блоки выполнения операций над целочисленными данными. К локальным управляющим схемам относятся: блок плавающей запятой, модуль предсказания ветвлений, модуль преобразования СISС-инструкций во внутренний RISС-микрокод, регистры микропроцессорной памяти (в МП типа VLIW до 256 регистров), регистры кэшпамяти 1-го уровня (отдельно для данных и инструкций), шинный интерфейс и многое другое. В состав микропроцессора Pentium обычно входят следующие физические компоненты: О ^ Соrе — ядро МП; О Ехесutioп иnit — исполняющий модуль; О Integer ALU — АЛУ для операций с целыми числами (с фиксированной запятой); О Registers — регистры; О Floating Point Unit — блок для работы с числами с плавающей запятой; О Primary Cashe — кэш первого уровня, в том числе кэш данных (Data Сасhе) и кэш команд (Сode ^ Сасhе); О Instruction Decode and Prefetch Unit и Branch Predictor — блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений; О Bus Interface — Интерфейсные шины, в том числе 64- и 32-битовая, и выход на системную шину к оперативной памяти. Функционально МП можно разделить на две части:

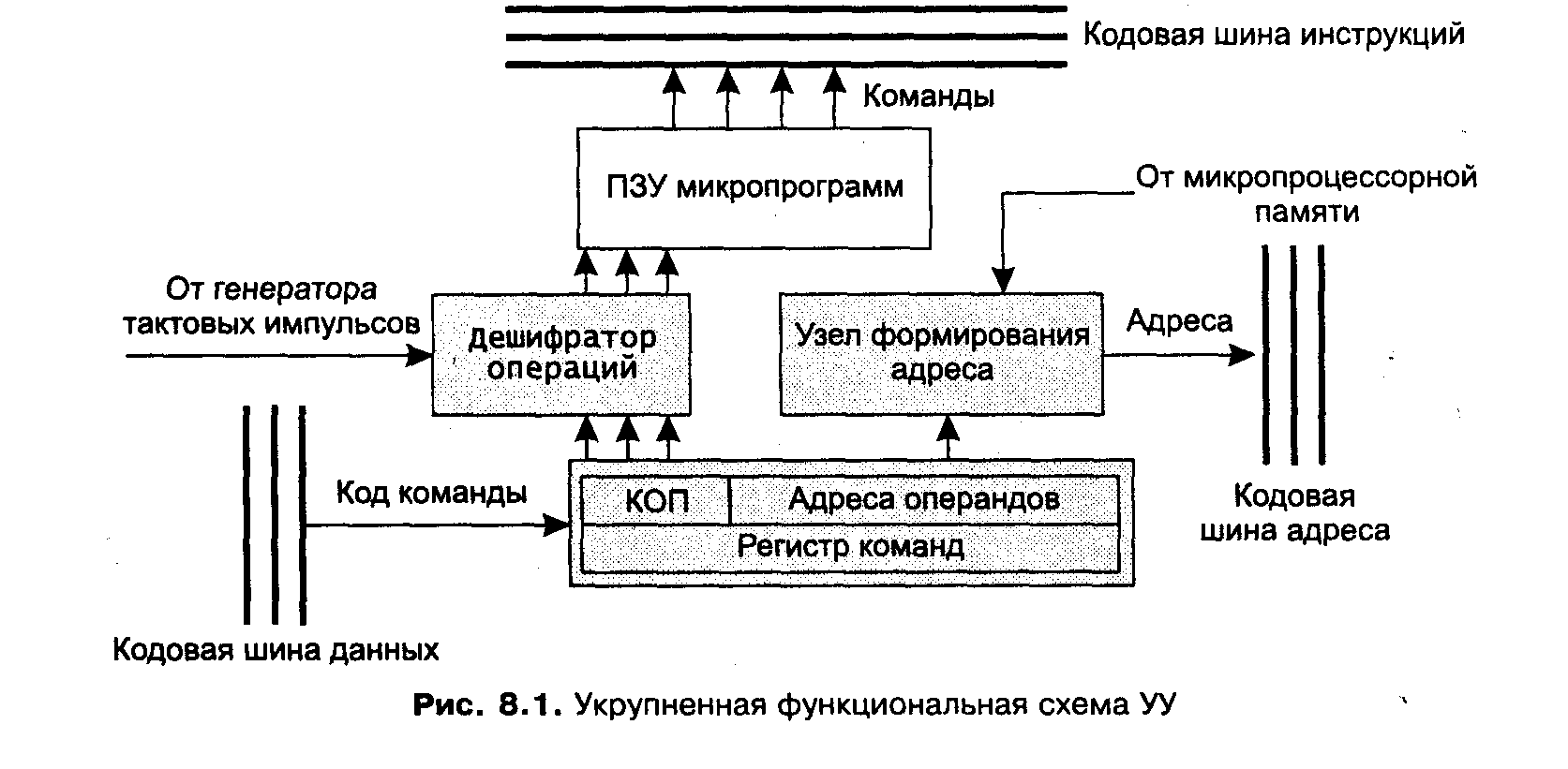

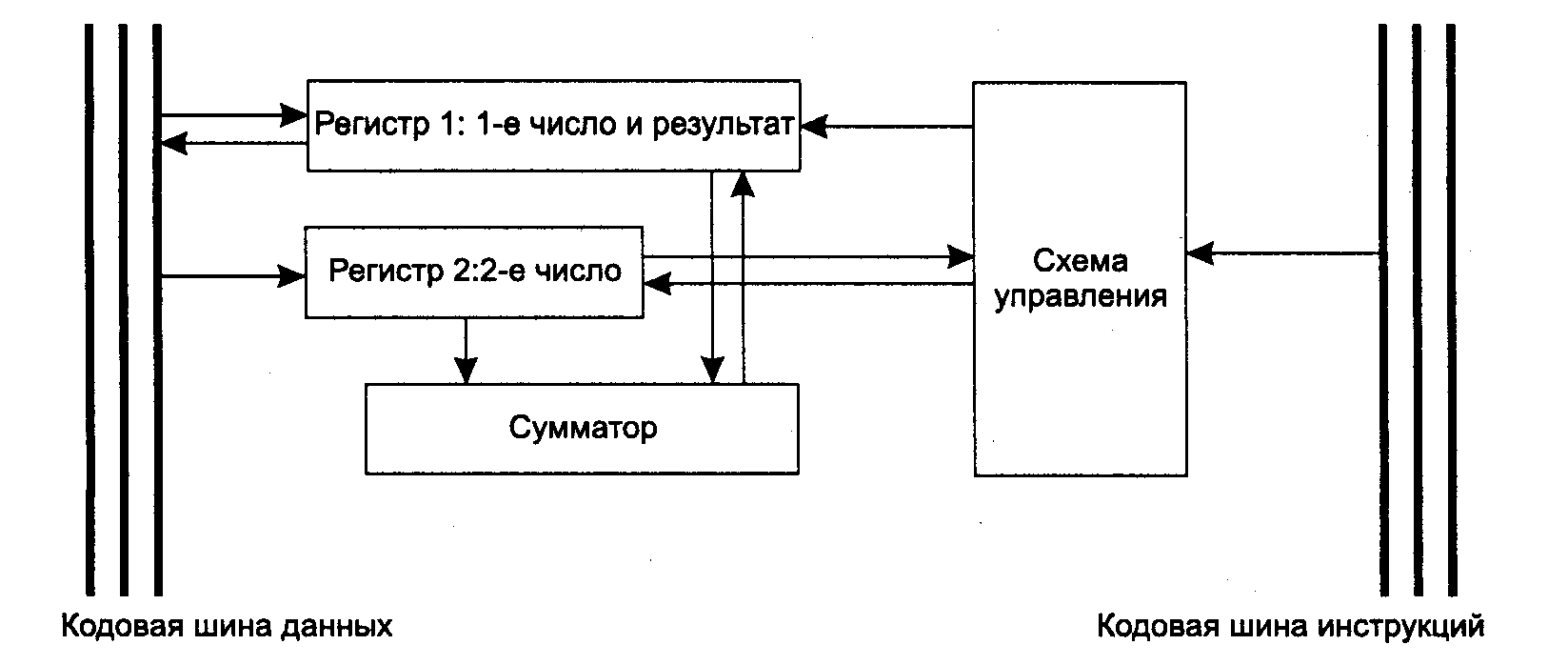

Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) выполняется во время выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие. ^ Устройство управления Устройство управления (УУ) является функционально наиболее сложным устройством ПК — оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций (КШИ) во все блоки машины. Упрощенная функциональная схема У У показана на рис. 8.1.  На рис. 8.1 представлены:

^ Арифметико-логическое устройство Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально в простейшем варианте АЛУ (рис. 8.2) состоит из двух регистров, сумматора и схем управления (местного устройства управления). Сумматор — вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова. Регистры — быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2 — разрядность слова. При выполнении операций в регистр 1 помещается первое число, участвующее в операции, а по завершении операции — результат; в регистр 2 — второе число, участвующее в операции (по завершении операции информация в нем не изменяется). Регистр 1 может и принимать информацию с кодовых шин данных, и выдавать информацию на них; регистр 2 только'получает информацию с этих шин.  ^ Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ. АЛУ выполняет арифметические операции «+»,«-», «х» и «:» только над двоичной информацией с запятой, фиксированной после последнего разряда, то есть только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется с привлечением математического сопроцессора или по специально составленным программам. Рассмотрим в качестве примера выполнение команды умножения. Перемножаются числа 1101 и 1011 (числа для простоты взяты 4-битовыми). Множимое находится в регистре 1, имеющем удвоенную по отношению к регистру 2 разрядность; множитель размещается в регистре 2. Операция умножения требует для своего выполнения нескольких тактов. В каждом такте число из регистра 1 проходит в сумматор (имеющий также удвоенную разрядность) только в том случае, если в младшем разряде регистра 2 находится 1.

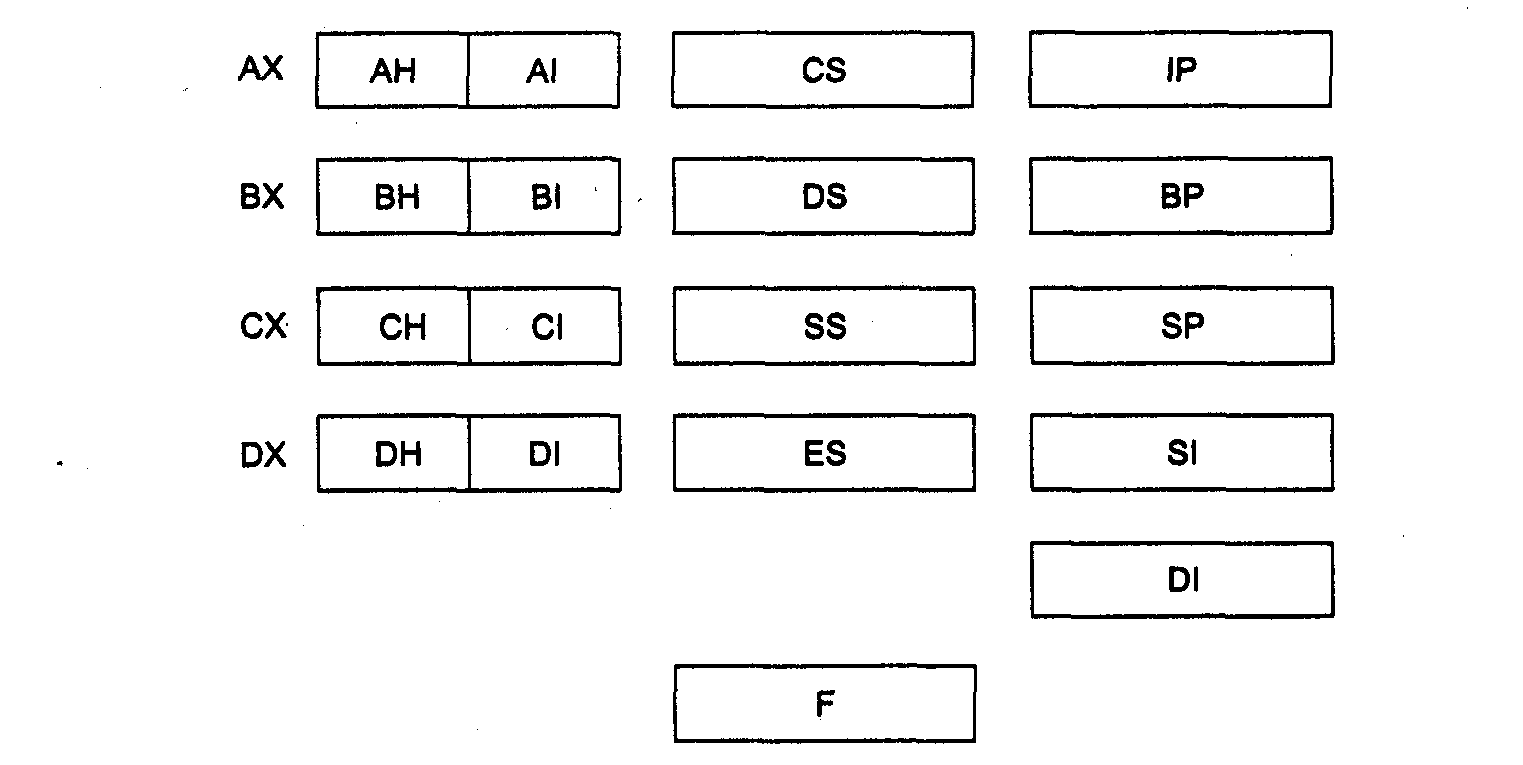

^ Микропроцессорная память Микропроцессорная память (МПП) базового МП 8088 включает в себя 14 двухбайтовых запоминающих регистров. У МП 80286 и выше имеются дополнительные регистры, например, у МП типа VLIW есть 256 регистров, из которых 128 — регистры общего назначения. У МП 80386 и выше некоторые регистры, в том числе и регистры общего назначения, — четырехбайтовые (у МП Pentium есть и восьмибайтовые регистры). Но в качестве базовой модели, в частности для языка программирования Assembler и отладчика программ Debug, используется 14-регистровая система МПП. Все регистры можно разделить на четыре группы (рис. 8.3):

Если регистры 4-байтовые или 8-байтовые, их имена несколько изменяются: например, 4-байтовые универсальные регистры АХ, ВХ, СХ, DХ именуются ЕАХ, ЕВХ, ЕСХ, ЕDХ соответственно. При этом если используется их двухбайтовая или однобайтовая часть, наименования этих частей регистров соответствуют рассматриваемым далее. ^ Универсальные регистры Регистры АХ, ВХ, СХ и DХ являются универсальными (их часто называют регистрами общего назначения — РОН); каждый из них может использоваться для временного хранения любых данных, при этом позволено работать с каждым регистром целиком, а можно отдельно и с каждой его половиной (регистры АН, ВН, СН, DН — старшие (High) байты, а регистры АL, ВL, СL, DL — младшие (Low) байты соответствующих двухбайтовых регистров). Но каждый из универсальных регистров может использоваться и как специальный при выполнении некоторых конкретных команд программы. В частности:

^ Сегментные регистры Регистры сегментной адресации СS, DS, SS, ЕS используются для хранения начальных адресов полей памяти (сегментов), отведенных в программах для хранения:

дополнительной области памяти данных при межсегментных пересылках (расширенный сегмент — ЕS), поскольку размер сегмента в реальном режиме работы МП ограничен величиной 64 Кбайт. ^ Регистры смещений Регистры смещений (внутрисегментной адресации) IP, SP, ВР, SI, DI предназначены для хранения относительных адресов ячеек памяти внутри сегментов (смещений относительно начала сегментов):

^ Регистр флагов Регистр флагов F содержит условные одноразрядные признаки-маски, или флаги, управляющие прохождением программы в ПК; флаги работают независимо друг от друга, и лишь для удобства они помещены в единый регистр. Всего в регистре содержится 9 флагов: 6 из них статусные, они отражают результаты операций, выполненных в компьютере (их значения используются, например, при выполнении команд условной передачи управления — команд ветвления программы), а 3 других — управляющие, непосредственно определяют режим ис- полнения программы. Статусные флаги:

^ Интерфейсная часть МП Интерфейсная часть МП предназначена для связи и согласования МП с,системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд. Интерфейсная часть включает в свой состав:

Некоторые из названных устройств, такие как узел формирования адреса и регистр команды, непосредственно выполняемой МП, функционально входят в состав устройства управления. Порты ввода-вывода — это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами. Всего портов у МП может быть 65 536 (равно количеству разных адресов, которые можно представить числом формата «слово»). Каждый порт имеет адрес — номер порта; по существу, это адрес ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт, а не частью основной памяти компьютера. Порту устройства соответствуют аппаратура сопряжения и два регистра памяти — для обмена данными и управляющей информацией. Некоторые внешние устройства используют и основную память для хранения больших объемов информации, подлежащей обмену. Многие стандартные устройства (НЖМД, НГМД, клавиатура, принтер, сопроцессор и т. д.) имеют постоянно закрепленные за ними порты ввода-вывода. Схема управления шиной и портами выполняет следующие функции:

Схема управления шиной и портами использует для связи с портами кодовые шины инструкций, адреса и данных системной шины: при доступе к порту МП посылает сигнал по кодовой шине инструкций (КШИ), который оповещает все устройства ввода-вывода, что адрес на кодовую шину адреса (КША) является адресом порта, а затем посылает и сам адрес порта. Устройство с совпадающим адресом порта дает ответ о готовности. После этого по кодовой шине данных (КШД) осуществляется обмен данными. Упрощенная структурая схема микропроцессора показана на рис.  ^ Вопросы для самопроверки 1. Дайте краткую характеристику микропроцессора, его структуры, назначения, основных параметров. 2. Назовите и поясните основные функции, выполняемые микропроцессором. 3. Из каких функциональных узлов состоит устройство управления 4. Назовите основные узлы АЛУ и укажите их функциональное назначение. 5. Перечислите основные группы регистров МПП. 6. Охарактеризуйте каждый из регистров МПП. 7. Каким целям служит интерфейсная часть микропроцессора. 8. Какие функционально – законченные узлы входят в состав интерфейсной части МП?. Лекция № 6 Машинные команды План лекции:

Алгоритм решения задачи, заданный в виде последовательности команд на языке вычислительной машины (в кодах машины), называется машинной программой. Команда машинной программы (иначе машинная команда) — это элементарная инструкция машине, выполняемая ею автоматически без каких либо дополнительных указаний и пояснений. Машинная команда состоит из двух частей: операционной и адресной.

^ Операционная часть команды (КОП — код операции) — это группа разрядов в команде, предназначенная для представления кода операции машины. Адресная часть команды (адреса) — это группа разрядов в команде, в которых записываются коды адреса (адресов) ячеек памяти машины, предназначенных для оперативного хранения информации, или иных объектов, задействованных при выполнении команды. Часто эти адреса называются адресами операндов, то есть чисел, участвующих в операции. По количеству адресов (а1, а2, аЗ, ...), записываемых в команде, команды делятся на безадресные, одно-, двух- и трехадресные. Типовая структура трехадресной команды:

а2 и аЗ — адреса ячеек (регистров), где расположены, соответственно, первое и второе числа, участвующие в операции, а1 — адрес ячейки (регистра), куда следует поместить число, полученное в результате выполнения операции. Типовая структура двухадресной команды:

а1 — это обычно адрес ячейки (регистра), где хранится первое из чисел, участвующих в операции, и куда после завершения операции должен быть записан результат операции; а2 — обычно адрес ячейки (регистра), где хранится второе участвующее в операции число. Типовая структура одноадресной команды:

где а1 в зависимости от модификации команды может обозначать либо адрес ячейки (регистра), в которой хранится одно из чисел, участвующих в операции, либо адрес ячейки (регистра), куда следует поместить число — результат операции. ^ Безадресная команда содержит только код операции, а информация для нее должна быть заранее помещена в определенные регистры машины. Наиболее широкое применение в ПК нашли двухадресные команды. Пример двухадресной команды, записанной на языке символического кодирования:

Эту команду следует расшифровать так: сложить число, записанное в ячейке 0103 памяти, с числом, записанным в ячейке 5102, а затем результат (то есть сумму) поместить в ячейку 0103.

Современные компьютеры автоматически выполняют несколько сотен различных команд. Например, стандартный набор современных IВМ-совместимых ПК содержит более 240 машинных команд. Все машинные команды можно разделить на группы по видам выполняемых операций: операции пересылки информации внутри компьютера; арифметические операции над информацией; логические операции над информацией; операции над строками (текстовой информацией); операции обращения к внешним устройствам компьютера; операции передачи управления; обслуживающие и вспомогательные операции. Пояснения требуют операции передачи управления (или иначе — ветвления программы), которые служат для изменения естественного порядка выполнения команд. Существуют операции безусловной передачи управления и операции условной передачи управления. Операции безусловной передачи управления всегда приводят к выполнению после данной команды не следующей по порядку, а той, адрес которой в явном или неявном виде указан в адресной части команды. Операции условной передачи управления тоже вызывают передачу управления по адресу, указанному в адресной части команды, но только в том случае, если выполняется некоторое заранее оговоренное для этой команды условие. Это условие в явном или неявном виде указано в коде операции команды. Команд условной передачи управления насчитывается обычно до нескольких десятков — по числу используемых условий. Команд безусловных передач управления обычно только три: команда передачи управления, которая просто передает управление по заданному адресу и больше никаких действий не выполняет; команда передачи управления (ее часто называют командой вызова процедуры или подпрограммы), которая кроме передачи управления процедуре еще и запоминает в специальной стековой памяти адрес следующей команды (адрес возврата из процедуры); безадресная команда передачи управления (команда возврата из процедуры), возвращающая управление по запомненному адресу возврата. Вторая и третья из названных команд безусловных передач управления работают «на пару»: одна передает управление процедуре, другая — возвращает из нее. Важную роль в выполнении этих команд передачи управления (да и при многих других ситуациях, отрабатываемых компьютером) играет специальным образом организованная область оперативной памяти — стековая память. Обращение к ячейкам этой памяти выполняется по принципу «последний записанный операнд первым считывается», или иначе «первым вошел — последним вышел» (FILO — first input, last output). Стековая память позволяет удобно реализовать процессы иерархического обращения ко многим процедурам (количество уровней иерархии практически не ограничено), последовательно записывая и выдавая по принципу FILO адреса возврата каждой из них. ^ 3 Адресация регистров и ячеек памяти в ПК Адресация операндов в командах программы может быть: непосредственной; прямой; косвенной; ассоциативной; неявной. ^ Непосредственная адресация заключается в указании в команде самого значения операнда, а не его адреса. Прямая адресация состоит в указании в команде непосредственно абсолютного или исполнительного адреса операнда. ^ Косвенная адресация подразумевает указание в команде регистра(ов) или ячейки памяти, в которых находятся абсолютный, исполнительный адрес операнда или их составляющие. ^ Ассоциативная адресация — указание в команде не адреса, а идентифицирующего содержательного признака операнда, подлежащего выборке (применяется в ассоциативных запоминающих устройствах). Неявная адресация — адрес операнда в команде не указан, но он подразумевается кодом операции. Адресация ячеек основной памяти ПК имеет две разновидности: относительную; стековую. ^ Относительная адресация Абсолютный (Аинд) адрес формируется как сумма адресов исполнительного (Аисп) и сегментного (Асенм); Аабс=Асегм+Аисп Асегм — 20-битовый начальный адрес сегмента, который является увеличенным в 16 раз (сдвинутым на 4 бит влево) 16-битовым адресом сегмента  хранящимся в одном из 16-битовых сегментных регистров. Начальный адрес сегмента в таком варианте всегда кратен 16 байтам, и он может быть полностью идентифицирован значением хранящимся в одном из 16-битовых сегментных регистров. Начальный адрес сегмента в таком варианте всегда кратен 16 байтам, и он может быть полностью идентифицирован значением  (сегмент всегда состоит из целого числа параграфов, а параграф равен 16 байт), то есть (сегмент всегда состоит из целого числа параграфов, а параграф равен 16 байт), то естьАсегм=16  = = 0000 000016-битовый исполнительный адрес может в ПК представлять собой сумму 3-х адресов: Аисп=Асмещ[+Абаз][+Аинд] где Асмещ – 16-битовый адрес смещения относительно начала сегмента (или относительно базы, если есть Абаз); Абаз – 16-битовый адрес смещения базы адреса операнда относительно начала сегмента; Аинд — адрес индекса (или просто индекс) — дополнительная составляющая адреса операнда, часто использующаяся при программировании циклических процессов с массивами и таблицами. Индекс должен быть непосредственно задан в соответствующем регистре МПП. При адресации данных могут использоваться все составляющие адреса: Аабс = Асегм + Аисп = Асегм + Асмещ [+Абаз][+Аинд] где Асегм = 16 •  ; ;  берется из регистра DS по умолчанию или из регистра ES, берется из регистра DS по умолчанию или из регистра ES,если это указано в программе; Абаз и Аинд берутся, соответственно, из регистров ВХ и индексных (SI или DI), а ^ Асмещ в явном или неявном виде указываются в программе. При адресации команд программы могут использоваться только две составляющие адреса: Аабс =Асегм + Аисп = Асегм + Асмещ =  16 + Асмещ 16 + АсмещАсегм берется из регистра CS, а Асмещ — из регистра IP. ^ Стековая адресация В стековой памяти (стеке) доступ к ячейкам памяти не произвольный, а по принципу «последний записанный операнд первым считывается» (FILO); Аабс = Асегм + [Абаз] + Асмещ 16-битовый адрес сегмента Асегм берется из регистра SS, смещения относительно начала сегмента стека автоматически считываются из регистров ВР (смещение базы стека — Абаз) и SP (смещение активной ячейки стека, в которую записывается или из которой считывается информация, — «вершины стека» относительно базы - Асмещ). В защищенном (многопрограммном) режиме работы микропроцессора начальные адреса сегментов хранятся в таблицах дескрипторов и имеют длину 24 или 32 бит (в зависимости от типа МП). В сегментных регистрах в этом режиме хранятся селекторы, содержащие адресные ссылки на соответствующие таблицы дескрипторов. Вопросы для самопроверки:

Лекция №____ |