Вопрос №3 Принципы проектирования информационного обеспечения программного комплекса

| Вид материала | Документы |

- Е. В. Чепин московский инженерно-физический институт (государственный университет), 30.11kb.

- Рабочая программа учебной дисциплины (модуля) case-средства проектирования программного, 143.56kb.

- Технология программирования, 643.21kb.

- Базы данных, 3110.93kb.

- А. А. Дюмин московский инженерно-физический институт (государственный университет), 30.84kb.

- Учебно-методический комплекс дисциплины разработка и стандартизация программных средств, 362.73kb.

- Методика выбора программного обеспечения турфирмой Антон Россихин (само-софт), 34.31kb.

- С. Д. Романин московский инженерно-физический институт (государственный университет), 24.74kb.

- Примерная программа наименование дисциплины Проектирование и архитектура программных, 182.2kb.

- Рабочая программа учебной дисциплины "системы автоматизированного проектирования электроустановок, 119.83kb.

Вопрос №35 Передача данных с прямым доступом к памяти

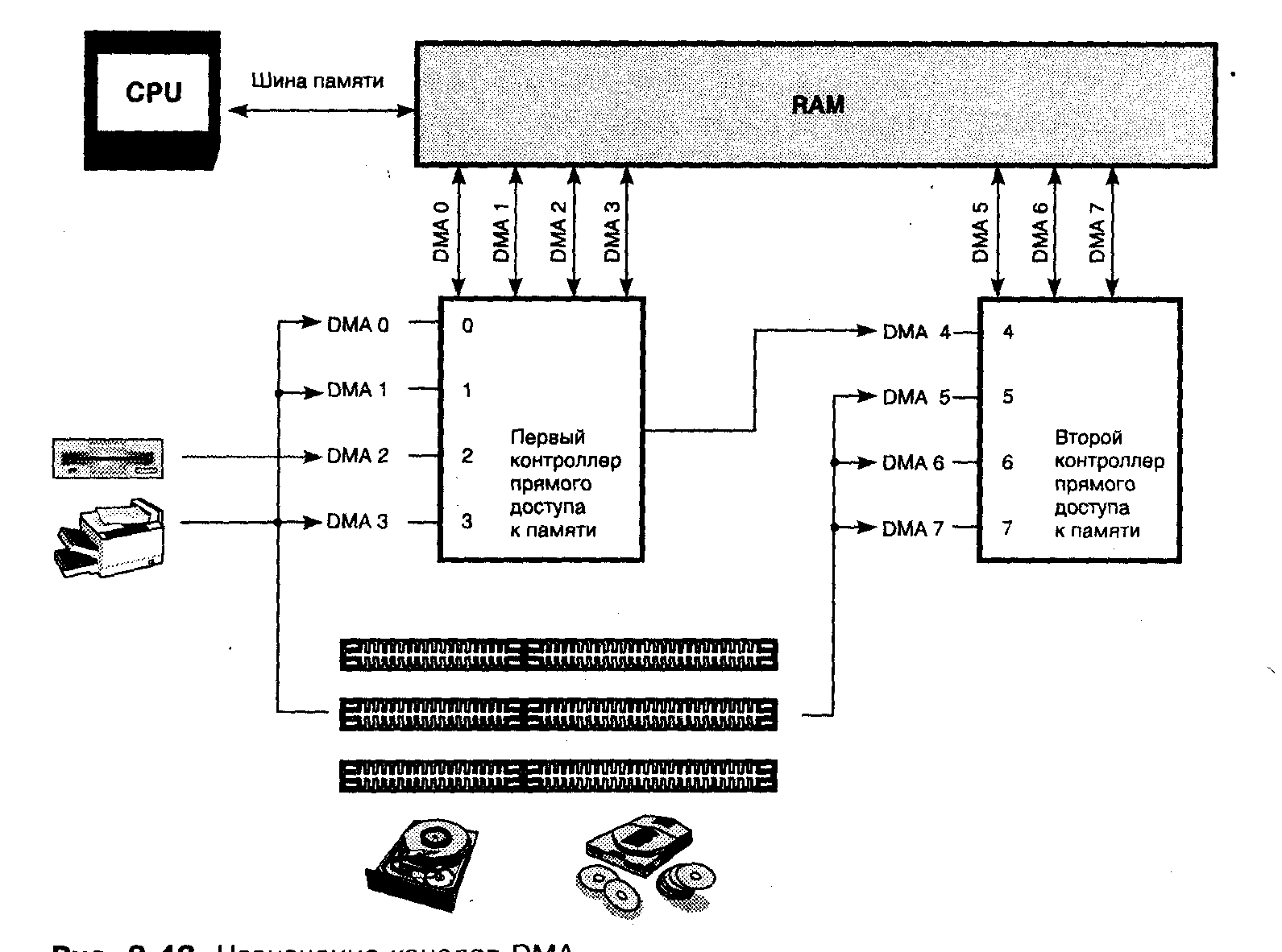

Прямой доступ к памяти используется для непосредственного обмена данными между основной памятью и быстродействующими ВУ (внешними устройствами), когда пропускной способности процессора недостаточно. В этом режиме действия процессора приостанавливаются, он отключается от системной шины и не участвует в передачах данных между памятью и ВУ.

Для осуществления прямого доступа к памяти используется механизм DMA (Direct Memory Access). В режиме прямого доступа к памяти ВУ (внешнее или периферийное устройство) связано с ОП (оперативной памятью) непосредственно через каналы прямого доступа – каналы DMA, а не через внутренние регистры МП (микропроцессора).

Рассмотрим, как работает этот механизм:

Для того чтобы какое-либо устройство, кроме процессора, могло записать информацию в память или прочитать ее из памяти, необходимо чтобы это устройство могло забрать у процессора управление локальной магистралью для выставления соответствующих сигналов на шины адреса, данных и управления. Для централизации эти обязанности обычно возлагаются не на каждое устройство в отдельности, а на специальный контроллер – контроллер прямого доступа к памяти. Контроллер прямого доступа к памяти имеет несколько спаренных линий – каналов DMA, которые могут подключаться к различным устройствам.

Перед началом использования прямого доступа к памяти этот контроллер необходимо запрограммировать, записав в его порты информацию о том, какой канал или каналы предполагается задействовать, какие операции они будут совершать, какой адрес памяти является начальным для передачи информации и какое количество информации должно быть передано. Получив по одной из линий – каналов DMA, сигнал запроса на передачу данных от внешнего устройства, контроллер по шине управления сообщает процессору о желании взять на себя управление локальной магистралью. Процессор (возможно, через некоторое время, необходимое для завершения его действий с магистралью) передает управление локальной магистралью контроллеру DMA, известив его специальным сигналом. Контроллер DMA выставляет на адресную шину адрес памяти для передачи очередной порции информации и по второй линии канала прямого доступа к памяти сообщает устройству о готовности магистрали к передаче данных. После этого, используя шину данных и шину управления, контроллер DMA, устройство ввода-вывода и память осуществляют процесс обмена информацией. Затем контроллер прямого доступа к памяти извещает процессор о своем отказе от управления магистралью, и тот берет руководящие функции на себя. При передаче большого количества данных весь процесс повторяется циклически.

При прямом доступе к памяти процессор и контроллер DMA по очереди управляют локальной магистралью. Это, конечно, несколько снижает производительность процессора, так как при выполнении некоторых команд или при чтении очередной порции команд во внутренний кэш он должен поджидать освобождения магистрали, но в целом производительность вычислительной системы существенно возрастает.

При подключении к системе нового устройства, которое умеет использовать прямой доступ к памяти, обычно необходимо программно или аппаратно задать номер канала DMA, к которому будет приписано устройство. В отличие от прерываний, где один номер прерывания мог соответствовать нескольким устройствам, каналы DMA всегда находятся в монопольном владении устройств.

Вопрос №35 Формирование адресов микрокоманд.

Существуют два основных способа задания адреса микрокоманды, соответствующих естественному и принудительному порядкам следования МК в микропрограмме.

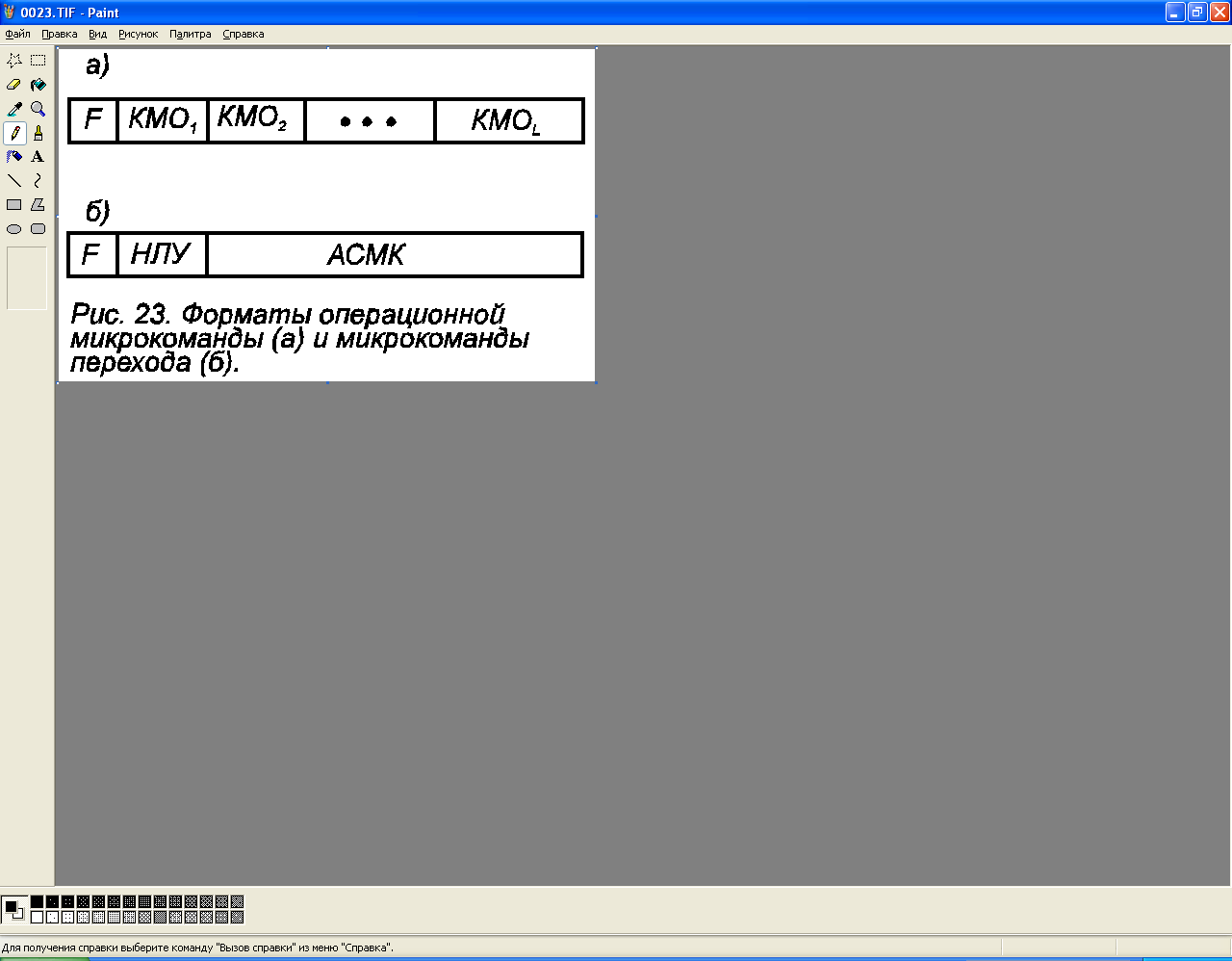

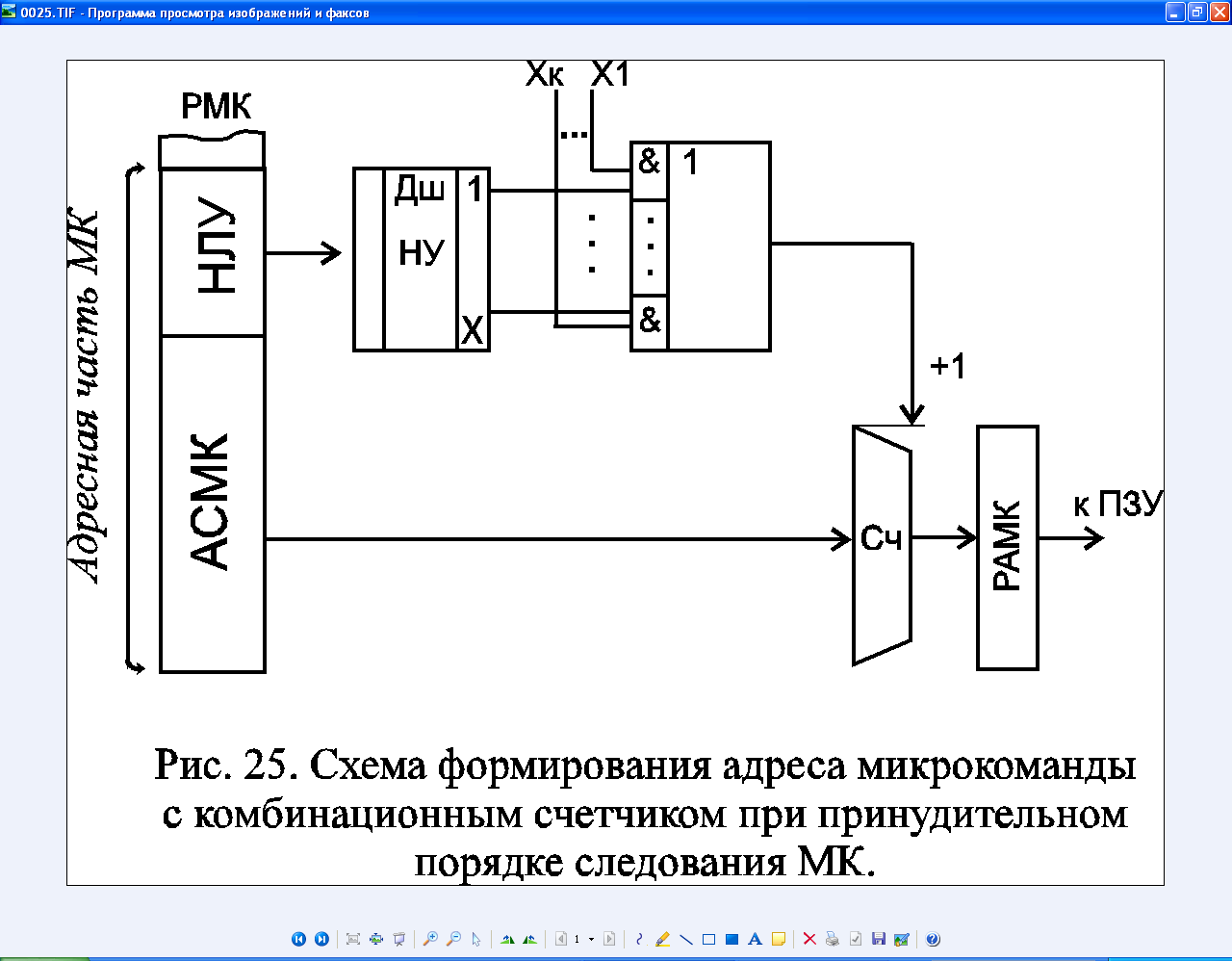

Естественный порядок следования микрокоманд. В этом случае микрокоманды любой микропрограммы располагаются в ячейках ПЗУ с последовательными адресами. Адрес очередной МК формируется посредством увеличением на единицу адреса предыдущей микрокоманды. Это позволяет не включать в каждую МК адрес следующей. Однако для организации циклов и разветвлений в микропрограммах необходимо иметь два типа микрокоманд: операционные МК и МК переходов.

Операционные МК задают выполнение некоторого набора микроопераций и содержат только операционную часть. МК переходов, используемые для изменения естественного порядка следования микрокоманд, не содержат операционной части. В них задается адрес следующей МК и, если переход должен выполняться в зависимости от значения какого-либо условия, номер (код) условия, определяющего переход. Кроме того, чтобы отличить операционные микрокоманды от МК перехода, вводится специальный признаковый разряд F, значение которого определяет тип микрокоманды. Например, для операционных МК значение разряда F равно единице, а для МК перехода F=0.

а) Формат операционной МК |  б) Формат МК перехода |

где НЛУ - номер логического условия, значение которого определяет, будет ли выполнен переход, а АСМК -- адрес следующей, подлежащей выполнению МК. В этом случае в структуру МПУУ включается счетчик адреса микрокоманд СМК, а в схему формирования адреса микрокоманды входит дешифратор номера логического условия ДшНУ и группа схем И проверки значений логических условий, выходы которых объединены схемой ИЛИ.

Рис.1 Структурная схема МПУУ при естественном порядке следования МК

(Схема формирования управляющих сигналов на рис.1 не показана).

При выполнении операционной МК адрес следующей МК формируется добавлением единицы к содержимому СМК одновременно с выработкой сигналов микроопераций. Если выполняется МК входа, то ДшНУ вырабатывает сигнал на выходе, соответствующем заданному в МК коду номера проверяемого логического условия x[i], и открывает схему И, на второй вход которой поступает сигнал x[i]. В том случае, когда значение x[i] равно нулю, переход по заданному адресу не выполняется и к содержимому СМК добавляется единица. Если же x[i] = 1, то содержимое тех разрядов РМК, в которых указан адрес следующей микрокоманды, поступает в СМК. Когда необходимо выполнить безусловный переход, в поле НЛУ обычно задается нулевой код, а на соответствующем его выходе ДшНУ вырабатывается сигнал, поступающий непосредственно на схему ИЛИ и вызывающий передачу АСМК из регистра МК в счетчик МК.

Однако естественный порядок следования микрокоманд (в отличие от естественного порядка следования команд) используется относительно редко, так как в этом случае на реализацию условной вершины микропрограммы затрачивается время, необходимое для выполнения одной микрокоманды (МК перехода). Поскольку участки, не содержащие разветвлений, в микропрограммах, как правило, включают малое число МК и переходы осуществляются часто, то время выполнения микропрограмм в МПУУ с естественным порядком следования МК значительно увеличивается. Поэтому в МПУУ более распространён принудительный порядок следования микрокоманд.

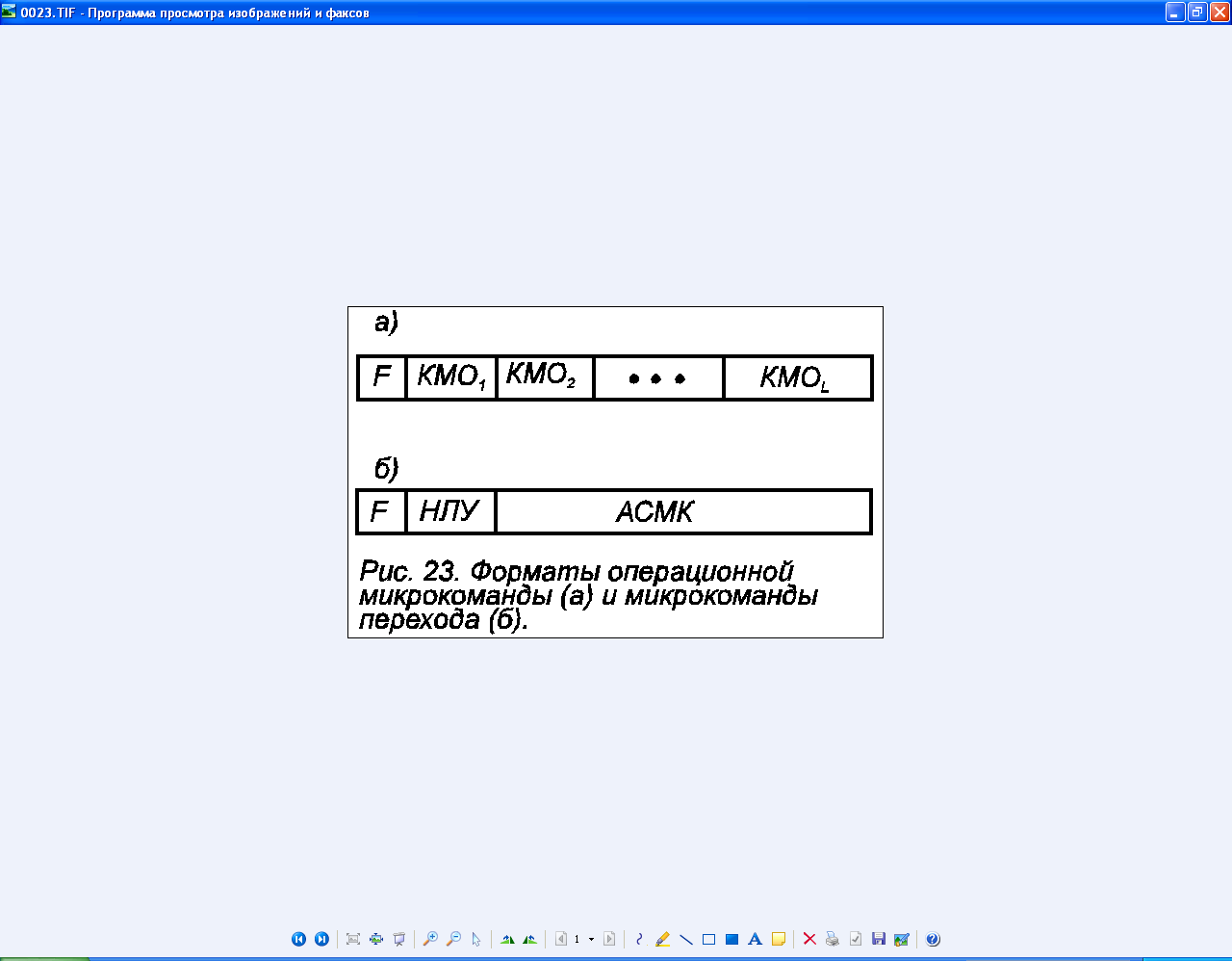

Принудительный порядок следования микрокоманд. В этом случае микрокоманды микропрограммы располагаются в произвольных ячейках ПЗУ. Адрес очередной МК указывается в адресной части выполняемой МК. В каждой микрокоманде для реализации условных переходов имеется одно или несколько полей номера логического условия (НЛУ). С целью сокращения разрядности и унификации формата МК в ее адресной части указывается только один адрес.

Для организации разветвлений в микропрограммах используют следующий прием. Если в поле НЛУ записан нулевой код, то следующей будет выполняться та микрокоманда, код адреса A которой задан в адресной части (поле АСМК) текущей МК. Если в поле НЛУ задан код, соответствующий условию xi, то адрес следующей МК определяется добавлением значения условия xi к коду A, заданному в поле АСМК выполняемой МК. Таким образом, при xi=0 адрес следующей МК равен коду A, а при xi=1 -- коду (A+1).

Существуют два основных способа добавления значения проверяемого логического условия к коду, задаваемого в микрокоманде адреса следующей МК при выполнении условного перехода. Первый из них основан на использовании дополнительного счетчика, желательно комбинационного типа. Такая схема требует введения счетчика в МПУУ и увеличивает время реализации МК в случае выполнения микрооперации добавления единицы в счетчике при формировании адреса следующей МК.

Рис.2 Схема формирования адреса МК с комбинационным счётчиком при принудительном порядке следования МК

Чаще используется другой способ, позволяющий обойтись без счетчика при некотором ограничении на значения задаваемых в поле АСМК кодов адресов A тех микрокоманд, в которых необходимо выполнить условный переход. Сущность этого способа состоит в том, что в таких МК допускается указывать только коды, имеющие нуль в младшем разряде. Тогда добавление значения проверяемого логического условия xi к коду A можно осуществить установкой значения xi в младшем разряде регистра адреса МК одновременно с передачей в него старших разрядов кода A из поля АСМК.

Рис.3 Схема формирования адреса МК с установкой младшего разряда РАМК при принудительном порядке следования МК

На этой схеме управление цепью передачи младшего (m-го) разряда адреса следующей микрокоманды АСМК из регистра микрокоманд РМК в регистр адреса микрокоманд РАМК осуществляется отдельно. Если в поле условия задан код, равный нулю, то в такой микрокоманде не производится проверка логических условий и все m-разрядов поля АСМК передаются в РАМК в качестве адреса очередной МК. При этом передачей m-го разряда управляет сигнал на нулевом (соответствующем всем нулям на входе) выходе дешифратора номера условия ДшНУ. Если выполняется МК с условным переходом, то старшие (m-1) разрядов поля АСМК передаются в старшие (m-1) разрядов РАМК, а в m-ый разряд РАМК заносится значение проверяемого логического условия x[i]. Таким образом, код адреса следующей МК будет зависеть от проверяемого логического условия.

Рис.4 Схема формирования адреса МК, допускающая разветвления по

напрвлениям

напрвлениямЧасто переходы в микропрограммах определяются несколькими логическими условиями, причём в качестве условий, определяющих переход, могут выступать не только одноразрядные двоичные переменные. Например, в микропрограммах выборки и декодирования команд разветвления осуществляются в зависимости от значения сразу нескольких разрядов кода операции, указываемого в команде.

Если переход зависит от значений нескольких логических условий, а структура МПУУ предусматривает проверку только одного из них в одной микрокоманде (Рис 2, 3), то для анализа каждого из условий перехода нужна отдельная МК. Причем только в первой из таких микрокоманд одновременно с проверкой первого условия могут быть выполнены микрооперации, непосредственно предшествующие разветвлению. Все последующие МК в операционной части не будут содержать никаких МО. Поэтому на переход придется затратить довольно большое время, в течение которого операционное устройство процессора будет простаивать.

Для того чтобы избежать этих потерь времени, схема формирования адреса МК организуется так, что в ней можно выполнить проверку нескольких условий перехода одновременно. С этой целью в схему вводятся два дополнительных узла: первый аналогичен рассмотренному в предыдущем случае (Рис.3) и управляет установкой предпоследнего разряда РАМК; второй предназначен для занесения многоразрядного условия-кода в средние разряды РАМК (Рис.4).

В этом случае в адресной части микрокоманды выделяются четыре поля: AS - поле старших m1 разрядов (с первого по m1-й) адреса следующей МК, AM - поле средних m2 разрядов (c (m1+1)-го по (m1+m2)-й ) и два одноразрядных поля A и B, задающих последний m-й и предпоследний (m-1)-й (где m=m1+m2+2) разряды адреса следующей микрокоманды соответственно. Кроме того, в МК вводятся три поля условий. В двух из них -- в поле номера условия A (НУА) и поле номера условия B (НУВ) -- указываются коды номеров логических условий x[i](A), i=1…k и x[j](B), j=1…l, используемых для установки последнего и предпоследнего разрядов РАМК соответственно. Третье поле -- поле номера условия M (НУМ) -- задает код номера условия-кода ~x[s](M), s=1…r (точнее, узла-источника средних m2 разрядов адреса следующей микрокоманды, передаваемых в РАМК). Условный переход по группе условий ~x[s](M) иначе называют функциональным.

Функционирование схемы формирования адреса микрокоманды, представленной на Рис.4, аналогично работе ранее рассмотренных схем.

Старшие разряды адреса следующей МК во всех случаях передаются в РАМК из поля AS РМК. Если в полях НУА, НУВ и НУМ указаны нулевые коды, то в РАМК будет передано содержимое всей адресной части текущей МК, и адрес следующей микрокоманды будет равен (AS).(AM).(B).(A), где круглые скобки указывают на то, что берется содержимое соответствующего поля, а точка является сцеплением. Если в полях НУА, НУВ и НУМ заданы коды, отличные от нуля, то в соответствующие разряды РАМК будут занесены значения определяемых этими кодами логических условий, и адрес следующей микрокоманды будет равен (AS).~x[s](M).x[j](B).x[i](A), где ~x[s](M), x[j](B), x[i](A) -- условия, номера которых указаны кодами полей НУА, НУВ и НУМ. Узел, обозначенный на Рис.4 как МП, представляет собой мультиплексор, используемый для передачи всех разрядов условия-кода от любого источника (в том числе и из РМК) в регистр адреса МК.

Рассмотренная схема позволяет организовать за один такт разветвление микропрограммы по

направлениям, так как в зависимости от значений проверяемых условий устанавливаются сразу (m2+2) разрядов адреса следующей МК.

направлениям, так как в зависимости от значений проверяемых условий устанавливаются сразу (m2+2) разрядов адреса следующей МК.Существуют схемы формирования адреса МК с более сложной взаимосвязью между разрядами адресной части микрокоманды и ее полей условий.