ATmega128, atmega128L 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

| Вид материала | Документы |

| Интерфейс JTAG и встроенная отладочная система Порт доступа к функциям тестирования – TAP |

- Белорусский Государственный Университет Биологический факультет Биореакторы Бабицкий, 198.24kb.

- Решение принятое в P6, 278.08kb.

- Микропроцессор P6, 276.15kb.

- Микропроцессоры семейства Intel, 288.88kb.

- Nano-накопитель от Imation, 8.65kb.

- Граммируемой логики, взяла старт по разработке risc-микроконтроллеров в середине 90-х, 161.19kb.

- Ринципов построения устройств микропроцессорной техники и приобретение практических, 46.61kb.

- Контрольная работа «Единицы измерения информации. Кодирование информации» Задание, 67.16kb.

- Лекция №7 «Программно-аппаратные средства защиты по с электронными ключами» Этот вид, 59.79kb.

- Инструкция по ремонту москва, 1699.67kb.

Интерфейс JTAG и встроенная отладочная система

Отличительные особенности:

- Интерфейс JTAG (совместимость со стандартом IEEE 1149.1)

- Функции граничного сканирования в соответствии с IEEE 1149.1 (JTAG)

- Отладчик имеет доступ к следующим блокам микроконтроллера:

– Все внутренние периферийные блоки

– Внутреннее и внешнее ОЗУ

– Внутренний файл регистров

– Программный счетчик

– ЭСППЗУ и флэш-память

- Отладочная система поддерживает обширные условия прерывания, в т.ч.:

– Прерывания по инструкциям AVR-микроконтроллера

– Прерывание по изменению потока памяти программ

– Пошаговое прерывание

– Точки прерывания памяти программ по одиночному адресу или адресному диапазону

– Точки прерывания памяти данных по одиночному адресу или адресному диапазону

- Программирование флэш-памяти, ЭСППЗУ, конфигурационных бит и бит защиты программы через интерфейс JTAG

- Встроенная отладочная система поддерживается AVR Studio

Введение

Интерфейс JTAG микроконтроллеров семейства AVR совместим со стандартом IEEE 1149.1 и может использоваться в следующих целях:

- Тестирование печатных плат с помощью функции граничного сканирования

- Программирование энергонезависимой памяти, конфигурационных бит и бит защиты программы

- Встроенная отладка

Встроенная отладочная система управляется через специальные JTAG-инструкции, которые известны только внутри корпорации ATMEL и выбранным ATMEL сторонним поставщикам отладочных средств.

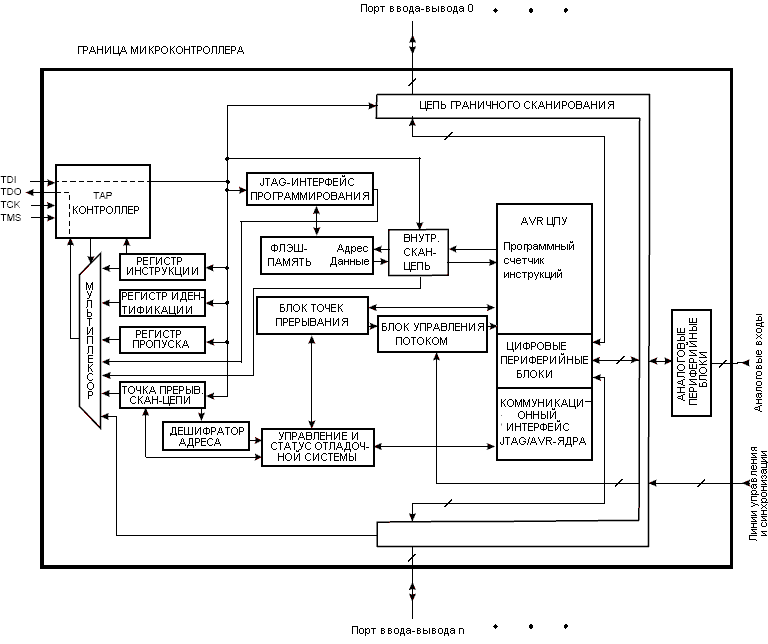

На рисунке 120 представлена функциональная схема интерфейса JTAG и встроенной отладочной системы. TAP-контроллер – цифровой автомат, который управляется сигналами TCK и TMS. TAP-контроллер выбирает в качестве сканируемой цепи (сдвигового регистра) между входом TDI и выходом TDO или регистр JTAG-инструкции или один из нескольких регистров данных. В регистре инструкции сохраняются JTAG-инструкции, которые управляют поведением регистра данных.

Идентификационный (ID) регистр, регистр пропуска и регистры цепи граничного сканирования и данных используются для тестирования на уровне проверки печатной платы. Интерфейс JTAG-программирования (фактически состоит из нескольких физических и виртуальных регистров данных) используется для последовательного программирования через интерфейс JTAG. Цепь внутреннего сканирования и точки прерывания сканируемой цепи используются только встроенной системой отладки.

Порт доступа к функциям тестирования – TAP

JTAG-интерфейс задействует 4 вывода AVR-микроконтроллера. По JTAG-терминологии эти выводы в совокупности называются "Порт доступа к функциям тестирования" (TAP). В состав этого порта входят следующие сигналы:

- TMS – Выбор режим тестирования. Данный вывод используется для навигации по цифровому автомату TAP-контроллера.

- TCK: Синхронизация тестирования. JTAG-интерфейс работает синхронно по отношению TCK.

- TDI: Тестовый ввод данных. Последовательный ввод данных сдвигом в регистр инструкции или регистр данных (цепи сканирования).

- TDO: Тестовый вывод данных. Последовательный вывод данных из регистра инструкции или регистра данных.

По стандарту IEEE 1149.1 также определен опциональный TAP-сигнал: TRST – сброс тестирования, который у AVR-микроконтроллеров отсутствует.

Если конфигурационный бит JTAGEN незапрограммирован, то четыре TAP-вывода выполняют функции обычного порта ввода-вывода, а TAP-контроллер находится в состоянии сброса. Если же бит JTAGEN запрограммирован, а также сброшен бит JTD в регистре MCUCSR, то к входным сигналам порта TAP подключаются внутренние подтягивающие к плюсу питания резисторы и разрешается работа интерфейса JTAG для граничного сканирования и программирования. В тех случаях, когда TAP-контроллер не выполняет сдвиг данных, выход порта TAP (вывод TDO) находится в третьем состоянии и, поэтому, должен быть подключен к внешнему подтягивающему резистору или к другому аппаратному компоненту, который содержит свой подтягивающий резистор (например, вход TDI следующего устройства в цепи сканирования). В состоянии поставки конфигурационный бит JTAGEN запрограммирован. Системой встроенной отладки в дополнении к сигналам интерфейса JTAG используется вывод RESET, состояние которого оценивает отладчик для определения возникновения условия внешнего сброса. Кроме того, отладчик может установить низкий уровень на выводе RESET, поэтому, необходимо следить, чтобы источник внешнего сброса в исполнительном каскаде содержал только открытый коллектор (сток).

Рисунок 120 – Функциональная схема интерфейса JTAG и отладочной системы

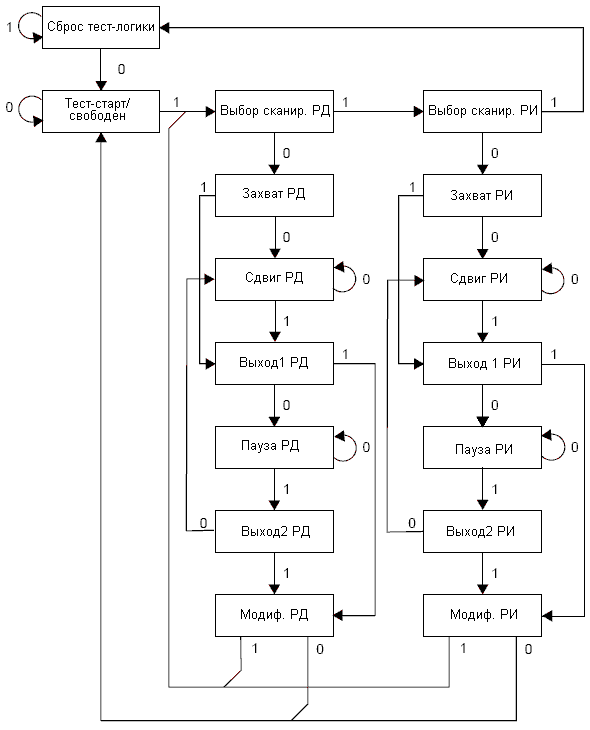

Рисунок 121 – Граф-автомат TAP-контроллера

TAP-контроллер

TAP-контроллер – цифровой автомат с 16 состояниями, который управляет работой схемой граничного сканирования, схемой JTAG-программирования или встроенной системой отладки. Граф-автомат, представленный на рисунке 121, зависит от сигнала TMS (его значение показывается рядом с переходом на другое состояние) в момент возникновения нарастающего фронта на TCK. Исходным состоянием после сброса при подаче питания является СБРОС ТЕСТ-ЛОГИКИ.

Все сдвиговые регистры выполняют первым ввод/вывод младших разрядов. Допустим, что текущим состоянием является ТЕСТ-СТАРТ/СВОБОДЕН, тогда типичным сценарием использования интерфейса JTAG является:

Формирование на входе TMS последовательности 1, 1, 0, 0 синхронно с нарастающим фронтом TCK для перевода в состояние сдвига регистра инструкции– СДВИГ ИР. Находясь в этом состоянии, выполняется сдвиг 4 разрядов JTAG-инструкции в регистр инструкции с входа TDI синхронно с нарастающим фронтом TCK. На входе TMS должен присутствовать низкий логический уровень в процессе ввода 3 младших разрядов для того, чтобы остаться в состоянии Сдвиг РИ. Старший разряд инструкции вводится сдвигом при выходе из данного состояния установкой лог. 1 на TMS. В процессе ввода инструкции через вывод TDI на выходе TDO выводится сдвигом код 0х01, означающий нахождение в состоянии СДВИГ РИ. JTAG-инструкция выбирает специфический регистр данных в качестве сдвигового регистра между выводами TDI и TDO, а также управляет схемой, связанной с регистром данных.

- Формирование на входе TMS последовательности 1, 1, 0 для повторного ввода в состояние ТЕСТ-СТАРТ/СВОБОДЕН. В состоянии МОДИФ. ИР инструкция защелкивается на параллельном выходе сдвигового регистра. Состояния ВЫХОД1 ИР, ПАУЗА ИР и ВЫХОД2 ИР используются только для навигации по цифровому автомату.

- Формирование на входе TMS последовательности 1, 0, 0 синхронного с нарастающими фронтами TCK для ввода состояния сдвига регистра данных – Сдвиг РД. Находясь в этом состоянии, загружается регистр данных (какой именно регистр определяется действующей инструкцией в регистре инструкции) с входа TDI нарастающим фронтом TCK. Для удержания состояния СДВИГ РД вход TMS должен оставаться в низком состоянии в процессе ввода всех разрядов за исключением последнего (старшего). Старший разряд вводится при выходе из этого состояния при установке высокого уровня на входе TMS. Во время последовательной записи в сдвиговый регистр с вывода TDI параллельные входы регистра данных захватываются в состоянии ЗАХВАТ РД и передаются сдвигом на выводе TDO.

- Формирование на входе TMS последовательности 1, 1, 0 для повторного ввода состояния ТЕСТ-СТАРТ/СВОБОДЕН. Если у выбранного регистра данных параллельный выход содержит защелку, то защелкивание происходит в состоянии МОДИФ. РД. Состояния ВЫХОД1 РД, ПАУЗА РД и ВЫХОД2 РД используются только для навигации по граф-автомату.

Как показано на граф-автомате состояние ТЕСТ-СТАРТ/СВОБОДЕН не должно вводиться между выбором JTAG-инструкции и использованием регистров данных, а также некоторые JTAG-инструкции активизируют функции, которые работают даже в состоянии ТЕСТ-СТАРТ/СВОБОДЕН, что делает это состояние неприемлемым в качестве свободного состояния.

Прим.: Независимо от исходного состояния TAP-контроллера перейти в состояние СБРОС ТЕСТ-ЛОГИКИ можно путем удержания входа TMS в высоком состоянии в течение 5 тактов TCK.

Более детальная информация по техническим требованиям к JTAG приведена в специализированной литературе (см. "Список литературы").