ATmega128, atmega128L 8-разрядный avr-микроконтроллер с внутрисистемно программируемой флэш-памятью емкостью 128 кбайт

| Вид материала | Документы |

| Модулятор выходов таймеров (OCM1C2) Пример временной диаграммы Аналогово-цифровой преобразователь |

- Белорусский Государственный Университет Биологический факультет Биореакторы Бабицкий, 198.24kb.

- Решение принятое в P6, 278.08kb.

- Микропроцессор P6, 276.15kb.

- Микропроцессоры семейства Intel, 288.88kb.

- Nano-накопитель от Imation, 8.65kb.

- Граммируемой логики, взяла старт по разработке risc-микроконтроллеров в середине 90-х, 161.19kb.

- Ринципов построения устройств микропроцессорной техники и приобретение практических, 46.61kb.

- Контрольная работа «Единицы измерения информации. Кодирование информации» Задание, 67.16kb.

- Лекция №7 «Программно-аппаратные средства защиты по с электронными ключами» Этот вид, 59.79kb.

- Инструкция по ремонту москва, 1699.67kb.

Модулятор выходов таймеров (OCM1C2)

Введение

Модулятор выходов таймеров (OCM) позволяет генерировать прямоугольные импульсы, промодулированные несущей частотой. Модулятор использует выходы канала сравнения С 16-разр. таймера-счетчика 1 и выход блока сравнения 8-разр. таймера-счетчика 2. Обратите внимание, что данная функция не поддерживается в режиме совместимости с ATmega103.

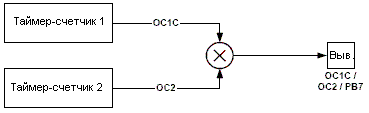

Если работа модулятора разрешена, то сигналы с выходов каналов сравнения объединяются в один в соответствии с рис. 72.

Рисунок 72. Принцип выполнения модуляции

Описание

Блоки сравнения 1C и 2 использует один и тот же вывод порта PB7 в качестве своего выхода. Выходы блоков сравнения (OC1C и OC2) блокируют обычную функцию регистра PORTB7 после разрешения работы одного из них (в т.ч., если COMnx1:0 не равны 0). После разрешения работы OC1C и OC2 автоматически разрешается работа модулятора.

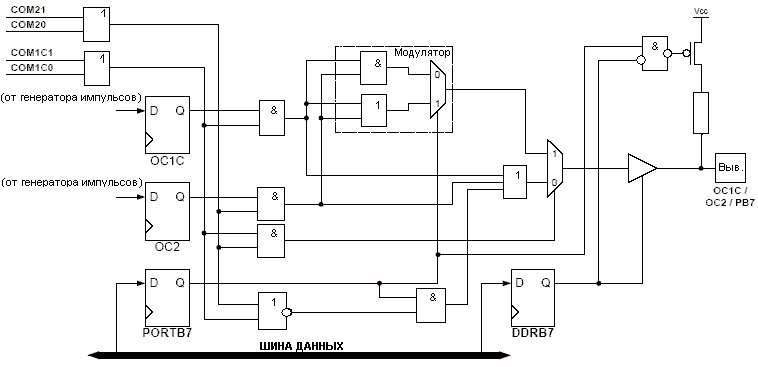

Эквивалентная функциональная схема модулятора представлена на рисунке 73. Схема содержит часть блоков таймеров-счетчиков и схему выходного драйвера линии 7 порта B.

Рисунок 73. Эквивалентная функциональная схема модулятора выходов таймеров

После разрешения работы модулятора необходимо выбрать тип модуляции (лог. И или ИЛИ) с помощью регистра PORTB7. Обратите внимание, что DDRB7 управляет направлением независимо от установок бит COMnx1:0.

Пример временной диаграммы

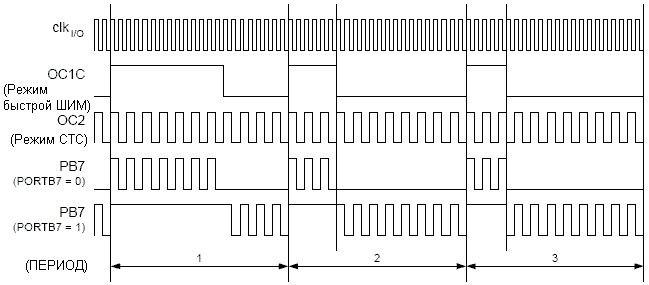

Рисунок 74 иллюстрирует работу модулятора. В данном примере таймер-счетчик 1 настроен на работу в режиме быстрой ШИМ (без инверсии), а таймер-счетчик 2 генерирует импульсы в режиме СТС (сброс таймера при совпадении) с переключением выходного состояния выхода компаратора при совпадении (COMnx1:0 = 1).

Рисунок 74. Временная диаграмма работы модулятора

В данном примере таймер-счетчик 2 генерирует несущий сигнал, а модулирующий сигнал генерируется каналом С блока сравнения таймера-счетчика 1.

Разрешающая способность ШИМ-сигнала (OC1C) снижается за счет модуляции. Коэффициент снижения эквивалентен числу тактовых импульсов системной синхронизации в течение одного периода несущего сигнала (OC2). В данном примере разрешение снижено с коэффициентом 2. Причина снижения разрешения показана ни рисунке 74 во 2 и 3 периоде сигнала на выходе PB7, когда состояние PORTB7 равно нулю. Длительность единичного импульса 2-го периода (OC1C) на один такт дольше длительности единичного импульса 3-го периода, но форма сигнала на выводе PB7 одинакова на каждом из этих периодов.

Аналогово-цифровой преобразователь

Отличительные особенности:

- 10-разрядное разрешение

- Интегральная нелинейность 0.5 мл. разр.

- Абсолютная погрешность ±2 мл. разр.

- Время преобразования 65 - 260 мкс.

- Частота преобразования до 15 тыс. преобр. в сек. при максимальном разрешении

- 8 мультиплексированных однополярных входов

- 7 дифференциальных входных каналов

- 2 дифференциальных входных канала с опциональным усилением на 10 и 200

- Представление результата с левосторонним или правосторонним выравниванием в 16-разр. слове

- Диапазон входного напряжения АЦП 0…VCC

- Выборочный внутренний ИОН на 2.56 В

- Режимы одиночного преобразования и автоматического перезапуска

- Прерывание по завершении преобразования АЦП

- Механизм подавления шумов в режиме сна

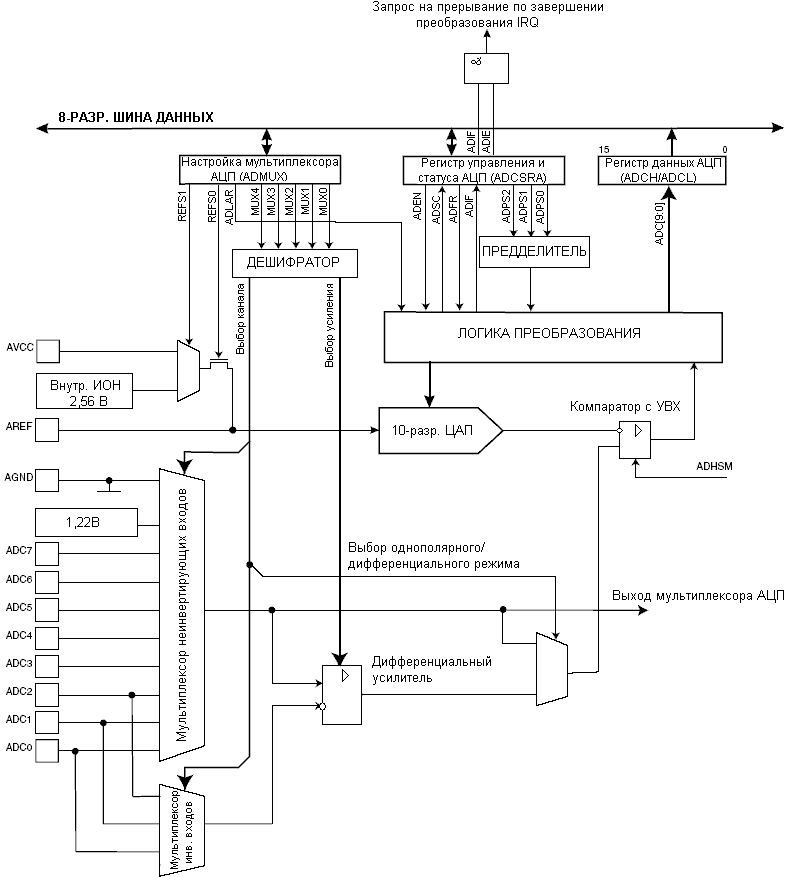

ATmega128 содержит 10-разр. АЦП последовательного приближения. АЦП связан с 8-канальным аналоговым мультиплексором, 8 однополярных входов которого связаны с линиями порта F. Общий входных сигналов должен иметь потенциал 0В (т.е. связан с GND). АЦП также поддерживает ввод 16 дифференциальных напряжений. Два дифференциальных входа (ADC1, ADC0 и ADC3, ADC2) содержат каскад со ступенчатым программируемым усилением: 0 дБ (1x), 20 дБ (10x), или 46 дБ (200x). Семь дифференциальных аналоговых каналов используют общий инвертирующий вход (ADC1), а все остальные входы АЦП выполняют функцию неинвертирующих входов. Если выбрано усиление 1x или 10x, то можно ожидать 8-разр. разрешение, а если 200x, то 7-разрядное.

АЦП содержит УВХ (устройство выборки-хранения), которое поддерживает на постоянном уровне напряжение на входе АЦП во время преобразования. Функциональная схема АЦП показана на рисунке 108.

АЦП имеет отдельный вывод питания AVCC (аналоговое питание). AVCC не должен отличаться более чем на ± 0.3В от VCC. См. параграф “Подавитель шумов АЦП”, где приведены рекомендации по подключению этого вывода.

В качестве внутреннего опорного напряжения может выступать напряжение от внутреннего ИОНа на 2.56В или напряжение AVCC. Если требуется использование внешнего ИОН, то он должен быть подключен к выводу AREF с подключением к этому выводу блокировочного конденсатора для улучшения шумовых характеристик.

Рисунок 108- Функциональная схема аналогово-цифрового преобразователя