Методические указания и описание лабораторной работы по дисциплине "Вычислительная техника и информационные технологии" "Исследование триггеров на логических схемах" г. Нижний Новгород 2010 год

| Вид материала | Методические указания |

СодержаниеЦель работы Лабораторное задание 2 Порядок выполнения работы |

- Методические указания и описание лабораторной работы по дисциплине "Вычислительная, 62.39kb.

- Методические указания и описание лабораторной работы по дисциплине "Вычислительная, 151.65kb.

- Методические указания по выполнению лабораторной работы №12 для студентов специальности, 141.78kb.

- Методические указания по выполнению лабораторной работы №14 для студентов специальности, 187.8kb.

- Методические указания по выполнению лабораторной работы №3 для студентов специальности, 177.77kb.

- Методические указания Нижний Новгород 2010 Печатается по решению редакционно-издательского, 434.35kb.

- Методические указания к выполнению лабораторной работы для студентов дневной формы, 287.23kb.

- Методические указания по выполнению курсовой работы по дисциплине «Комплексный экономический, 895.22kb.

- Методические указания по проведению лабораторной работы для студентов Vкурса специальности, 364.3kb.

- Методические указания к выполнению лабораторной работы №1 «Анализ доходности и риска, 95.2kb.

ФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ

Государственное образовательное учреждение

высшего профессионального образования

Московский технический университет связи и информатики

Волго-Вятский филиал

Кафедра Общепрофессиональных дисциплин

«УТВЕРЖДАЮ»

Заведующий кафедрой ОПД

доцент________ Ю.М. Туляков

ЛАБОРАТОРНАЯ РАБОТА № 4

Методические указания и описание лабораторной работы

по дисциплине "Вычислительная техника и информационные технологии" "Исследование триггеров на логических схемах"

г. Нижний Новгород – 2010 год.

Исследование триггеров на логических схемах

Составитель старший преподаватель Конев А.Ю.

Издание одобрено на заседании кафедры «___» _____________ 200__ г.

Протокол № ____

Цель работы: Изучение принципов построения и функционирования, а также экспериментальное исследование асинхронного и синхронного триггеров на интегральных логических схемах (ИЛС).

Оборудование: ПК с учебной программой Microcap 7,0.

Лабораторное задание:

1. Собрать схему асинхронного RS-триггер на элементах Пирса (ИЛИ-НЕ). Составить таблицу истинности (выделить свое число). Собрать схему асинхронного RS-триггер на элементах Шеффера (И-НЕ)

3. Составить аналитическое выражение, описывающее триггер.

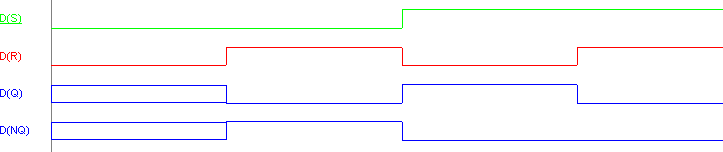

4. Отобразить временные диаграммы триггера.

5. Составить отчёт по работе.

Основные теоретические сведения.

Теория

Асинхронным триггером называется бистабильная ячейка (ячейка, имеющая два устойчивых состояния «0» и «1»), изменения состояния которой могут происходить в произвольный момент времени под воздействием входных сигналов.

Синхронным триггером называется триггер, у которого изменения состояния, соответствующие данной комбинации входных сигналов, могут происходить только в момент действия синхронизирующего (тактового) сигнала.

Асинхронный и синхронный триггеры относятся к классу элементарных последовательных автоматов, т.е. автоматов, в которых выходные сигналы являются функциями не только внешних сигналов, но и функциями предшествующих собственных состояний.

Асинхронный триггер – бистабильную ячейку на интегральных логических схемах можно построить либо из двух клапанов И-НЕ, либо из двух клапанов ИЛИ-НЕ, замкнутых в регенеративное кольцо положительной обратной связи.

Триггер любого типа имеет два выхода:

(основной выход) и

(основной выход) и  (инверсный выход). На информационные выходы подаются внешние входные управляющие сигналы-аргументы. Состояние триггера и значение хранимой в нем информации определяется сигналом на основном выходе

(инверсный выход). На информационные выходы подаются внешние входные управляющие сигналы-аргументы. Состояние триггера и значение хранимой в нем информации определяется сигналом на основном выходе  . Так, если

. Так, если  =1, то триггер находится в состоянии 1; при этом на инверсном выходе

=1, то триггер находится в состоянии 1; при этом на инверсном выходе  =0,

=0, Законы функционирования триггеров задаются таблицами переходов, показывающими, в какое состояние переходит триггер в момент времени tn+1 в зависимости от его состояния в предыдущий момент tn и от наличия той или иной комбинации на его информационных входах. Таблица переходов полностью определяет принцип функционирования конкретного типа триггера. Отметим, что таблицы переходов составляются без учета переходных процессов в клапанах триггеров.

Для облегчения прослеживания порядка переключения клапанов в сложных системах триггеров введем понятия активного и пассивного сигналов.

Под активным сигналом будем понимать то из двух возможных входных уровней (0 или 1), который, активизируя данный вход клапана, обеспечивает определенное состояние выхода вне зависимости от характера сигналов на других входах данного клапана. Под пассивным сигналом на том или ином входе клапана будем считать тот уровень, который не влияет на состояние его выходов; подача пассивного сигнала на тот или иной вход исключает участие данного входа в определении выходного состояния клапана.

Для схем И и И-НЕ активным сигналом является 0, а пассивным 1 (при подаче нуля на один из входов – на выходе клапана И всегда будет 0, а на выходе клапана И-НЕ – 1). Для схем ИЛИ и ИЛИ-НЕ активным сигналом является 1, а пассивным – 0 (при подаче единицы на один из входов – на выходе ИЛИ всегда будет 1, а на выходе ИЛИ-НЕ – 0). В самом деле, из аксиом алгебры логики вытекает:

,

,  активен «0»

активен «0» ,

,  активен «0»

активен «0» ,

,  активна «1»

активна «1» ,

,  активна «1»

активна «1»Асинхронный RS-триггер

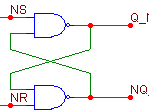

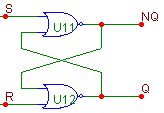

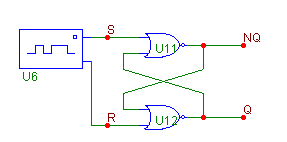

Асинхронный RS- триггер на интегральных логических схемах может быть построен либо с помощью двух двухвходовых клапанов, выполняющих логическую функцию И-НЕ (элементах Шеффера), схема и условие изображения триггера показаны на рис. 1, либо с помощью двухвходовых клапанов, выполняющих логическую функцию ИЛИ-НЕ (элементах Пирса), рис. 2.

Информационными входами являются S и R: S (Set) – установка 1 на основном выходе

, R (Rest) – установка 1 на инверсном

, R (Rest) – установка 1 на инверсном  (сброс в 0 на выходе

(сброс в 0 на выходе ). На выходы S и R подаются внешние входные управляющие сигналы (аргументы). Внутренние входные сигналы подаются непосредственно с выходов, образуя обратную связь.

). На выходы S и R подаются внешние входные управляющие сигналы (аргументы). Внутренние входные сигналы подаются непосредственно с выходов, образуя обратную связь.

Рис 1. Рис 2.

Обратите внимание:

Логическое НЕ (Инверсия) обозначается «N» (запись NQ и эквивалентна

)

)Логическое ИЛИ обозначается «+», возможно обозначение «1»

Логическое И обозначается «

», возможно обозначение «and», «&»

», возможно обозначение «and», «&»Обозначения логических элементов выполнены в соответствии с Американским стандартом.

Для триггера, построенного на элементах Шеффера (И-НЕ) Рис 1, активным сигналом «0» служит низкий уровень напряжения, а для триггера на элементах Пирса (ИЛИ-НЕ) Рис 2. активным является сигнал «1» (высокий уровень). Покажем, что в отсутствие внешних сигналов (R = 0, S = 0) в схемах имеются два устойчивых состояния.

= 1,

= 1,  = 0. В схеме рис. 1 на внутренний вход верхнего клапана попадает активный сигнал «0», вызывающий

= 0. В схеме рис. 1 на внутренний вход верхнего клапана попадает активный сигнал «0», вызывающий  = 1, что соответствует исходному состоянию; в то же время на внутренний вход нижнего клапана попадает пассивный сигнал «1», оставляющий неизменный состояние инверсного выхода

= 1, что соответствует исходному состоянию; в то же время на внутренний вход нижнего клапана попадает пассивный сигнал «1», оставляющий неизменный состояние инверсного выхода  = 0. В схеме рис. 2 на внутренний вход верхнего клапана подает пассивный сигнал «0», не оказывающий влияние на состояние

= 0. В схеме рис. 2 на внутренний вход верхнего клапана подает пассивный сигнал «0», не оказывающий влияние на состояние  = 1; в то же время на внутренний вход нижнего клапана поступает активный сигнал «1», вызывающий

= 1; в то же время на внутренний вход нижнего клапана поступает активный сигнал «1», вызывающий  = 0, что соответствует исходному состоянию триггера.

= 0, что соответствует исходному состоянию триггера.  = 0,

= 0,  = 1. Рассуждения аналогичны: в схеме рис. 1 попадание активного сигнала на внутренний вход нижнего клапана вызывает подтверждение

= 1. Рассуждения аналогичны: в схеме рис. 1 попадание активного сигнала на внутренний вход нижнего клапана вызывает подтверждение  = 1, а в схеме рис. 2 попадание активного сигнала на внутренний вход верхнего клапана вызывает подтверждение

= 1, а в схеме рис. 2 попадание активного сигнала на внутренний вход верхнего клапана вызывает подтверждение  = 0.

= 0.Мы видим, что каждое из состояний в обеих схемах само себя подтверждает, т.е. является устойчивым. Функционирование RS – триггера под воздействием комбинаций входных сигналов описывается таблицей переходов. Принятое обозначение входных сигналов дает возможность получить объединенную таблицу переходов RS – триггера (табл. 1), не зависимую от типа примененных клапанов.

Табл1.

| R | S |  |  | Применение |

| 0 | 0 |  |  | Хранение (блокировка) |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1/0 | 1/0 | запрещено |

Рассмотрим первую строчку таблицы 1. При подаче на оба входа схемы рис. 1 инвертированной информации S = 1, R = 1, а на входы схемы рис. 2 S = 0, R = 0, на выходах

и

и  сохраняются прежние уровни, так как входные сигналы в этом случае пассивны и не влияют на состояние триггера.

сохраняются прежние уровни, так как входные сигналы в этом случае пассивны и не влияют на состояние триггера.Вторая и третья строчки таблицы предполагают подачу на входы S и R противоположных сигналов. При S = 1, R = 0 имеется полностью определенное устойчивое состояние

= 1,

= 1,  = 0,. Заметим, что всегда, если S и R противоположны, выход

= 0,. Заметим, что всегда, если S и R противоположны, выход  принимает значение S; второй выход

принимает значение S; второй выход  принимает значение R, т.е. является парафазным основному выходу.

принимает значение R, т.е. является парафазным основному выходу.Последняя строчка табл. 1 является запрещенной. Действительно, при подаче на оба входа активных уровней (S = 0, R = 0 для схемы рис. 1 и S = 1, R = 1 для схемы рис. 2) на выходах

и

и  должны установиться одинаковые уровни (

должны установиться одинаковые уровни ( = 1,

= 1,  = 1 для схемы рис. 1 и

= 1 для схемы рис. 1 и  = 0,

= 0,  = 0 для схемы рис. 2). Это противоречит принципу работы бистабильной ячейки, характеризующейся наличием двух состояний, при которых на выходах устанавливаются уровни, противоположные друг другу. Поэтому комбинация аргументов S = 1, R = 1 должна быть запрещена, тем более, что она сама себя не поддерживает обратной связью.

= 0 для схемы рис. 2). Это противоречит принципу работы бистабильной ячейки, характеризующейся наличием двух состояний, при которых на выходах устанавливаются уровни, противоположные друг другу. Поэтому комбинация аргументов S = 1, R = 1 должна быть запрещена, тем более, что она сама себя не поддерживает обратной связью.На примере схемы рис. 1 рассмотрим более подробно процесс переключения RS – триггера. Пусть в исходном состоянии

= 0,

= 0,  = 1 и комбинация аргументов S = R = 0, что соответствует наличию на входе клапанов пассивных сигналов

= 1 и комбинация аргументов S = R = 0, что соответствует наличию на входе клапанов пассивных сигналов  =

=  = 1.

= 1. Чтобы перевести триггер в состояние «1» (

= 1,

= 1,  = 0), следует иметь комбинацию S = 1 и R = 0, что соответствует подаче на информационные входы сигналов S = 0 и R = 1.

= 0), следует иметь комбинацию S = 1 и R = 0, что соответствует подаче на информационные входы сигналов S = 0 и R = 1. Так при этом на управляющем входе верхнего клапана появился активный сигнал «0», то на его выходе в соответствии с логикой работы клапана И-НЕ через время задержки t3 установится «1» (

= 1). Эта единица по цепи обратной связи подается на внутренний вход нижнего клапана; на обоих входах нижнего клапана оказываются единицы, поэтому еще через время t3 он переходит в состояние «0» (

= 1). Эта единица по цепи обратной связи подается на внутренний вход нижнего клапана; на обоих входах нижнего клапана оказываются единицы, поэтому еще через время t3 он переходит в состояние «0» ( = 0).

= 0).Если теперь сменить комбинацию аргументов S = 0, R = 1, т.е. подать на информационные выходы сигналы

= 1 и

= 1 и  = 0, то триггер вновь вернется в исходное нулевое состояние. Очевидно, что время установки триггера в новое состояние примерно равно 2 t3, т.е. быстродействие интегрального триггера ниже быстродействия логических элементов, на которых он построен.

= 0, то триггер вновь вернется в исходное нулевое состояние. Очевидно, что время установки триггера в новое состояние примерно равно 2 t3, т.е. быстродействие интегрального триггера ниже быстродействия логических элементов, на которых он построен.Аналогичные рассуждения применимы к схеме, построенной на элементах Пирса (рис. 2). Отличие заключается лишь в том, что активным здесь является

высокий уровень (сигнал «1»).

Аналитически схемы асинхронных RS- триггеров описываются системой двух булевых уравнений.

Для схемы на элементах Шеффера (рис 1)

Для схемы на элементах Пирса (рис. 2)

Здесь предшествующие состояния выходов триггера и его входов рассматриваются в момент времени tn, а последующие состояния выходов – в момент времени tn+1.

На входы триггеров нельзя подавать одновременно два активных сигнала, образующих запрещенную комбинацию. Активные входные сигналы должны быть разнесены во времени, т.е. не должны перекрываться. В этом случае информация, записанная на выход триггера подачей на один из входов (вход записи) активного импульсного сигнала, запоминается триггером в том смысле, что и после снятия сигнала записи состояние выходов триггера остается неизменным. Переключение триггера произойдет при подаче активного импульсного сигнала на другой выход (вход считывания); состояние выходов, приобретенное триггером под влиянием сигнала считывания, сохранится и по его окончании вплоть до прихода следующего импульса записи. Поэтому асинхронные RS- триггеры находят применение в качестве ячеек памяти в системах, где входные сигналы имеют импульсную форму представления, например, в асинхронных системах с импульсными записью и считыванием информации (импульсно-потенциальный триггер с раздельным запуском). При этом под импульсными, понимаются сигналы не обязательно кратковременные.

2 Порядок выполнения работы

2.1. Запустить программу моделирования Micro Cap 7 demo.

Собрать схему асинхронного RS-триггер на элементах Пирса (ИЛИ-НЕ)

(Открыть файл RS_ИЛИ-НЕ_статика_динамика.cir)

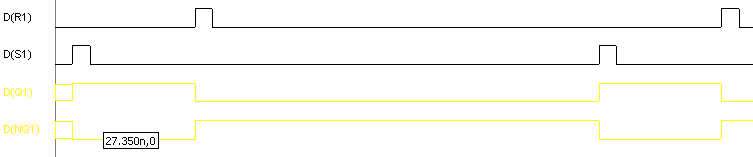

Рис. 30 Рис. 31

Запустить моделирование Analisis.... Transient.... Ran.

Внимание! Для элементов ИЛИ-НЕ активный входной сигнал логическая 1.

R - установка выхода Q в состояние 0

S - установка выхода Q в состояние 1

По ВД составить таблицу переходов, изменяя условия моделирования или по ВД.

| Вход | Выход | ||

| R | S | Q | nQ |

| 0 | 0 | Заполнить | Заполнить |

| 0 | 1 | Заполнить | Заполнить |

| 1 | 0 | Заполнить | Заполнить |

| 1 | 1 | Заполнить | Заполнить |

Аналитическое описание триггера булевыми уравнениями

Qi+1=n(nQi+Ri)

nQi+1=n(Qi+Si)

Изучить другую часть ВД (логические элементы с нулевыми задержками). Рис. 32.

Рис. 32

Выход из режима анализа.

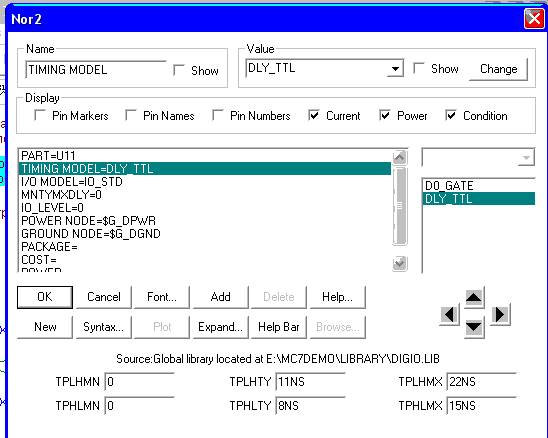

Изменить задержки распространения сигнала в логического элемента на TTL, заменив D0_GATE на DLY_TTL (См. рис 33.)

Запустить моделирование Analisis.... Transient.... Ran.

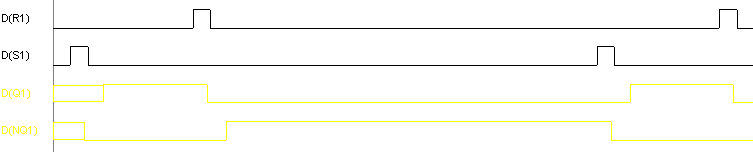

Изучить другую часть ВД (логические элементы с ненулевыми задержками)

Выход из режима анализа.

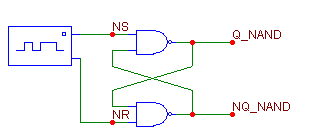

2.2. Собрать схему асинхронного RS-триггер на элементах Шеффера (И-НЕ)

(Открыть файл RS_И-НЕ_статика_динамика.cir)

Рис. 34

Рис. 34Аналитическое описание триггера булевыми уравнениями

Qi+1=n{(nQi)and( nSi)}

nQi+1=n{(Qi)and(nRi)}

Повторить действия описанные для RS триггера на элементах ИЛИ-НЕ

Внимание! Для элементов И-НЕ активный входной сигнал логического 0.

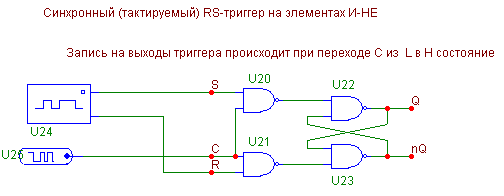

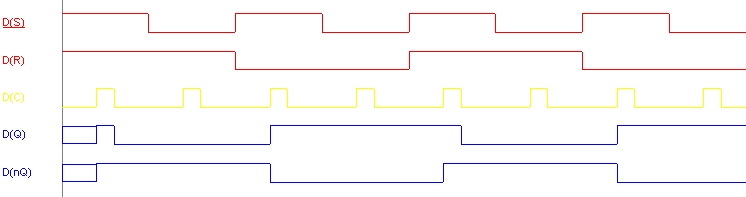

2.3. Собрать схему синхронного RS-триггер на элементах Шеффера (И-НЕ)

(Открыть файл RS_И-НЕ_синхро_D.cir)

Рис. 35 Рис. 36

Запустить моделирование Analisis.... Transient.... Ran.

Составить по ВД таблицу переходов.

| Вход | Выход | |||

| R | S | С | Q | nQ |

| 0 | 0 | 0 | Заполнить | Заполнить |

| 0 | 0 | 1 | Заполнить | Заполнить |

| 0 | 1 | 0 | Заполнить | Заполнить |

| 0 | 1 | 1 | Заполнить | Заполнить |

| 1 | 0 | 0 | Заполнить | Заполнить |

| 1 | 0 | 1 | Заполнить | Заполнить |

| 1 | 1 | 0 | Заполнить | Заполнить |

| 1 | 1 | 1 | Заполнить | Заполнить |

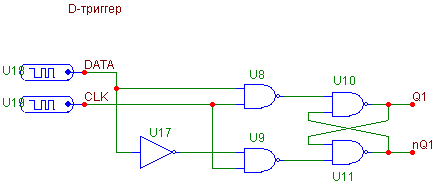

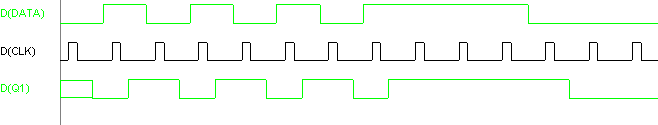

Изучить D-триггер., добавив в схему рис.35 инвертор, получится схема рис. 37

Рис. 37 Рис. 38

Изучить его работу по ВД изменяя задержки в логических элементах. Результат работы с задержками рис. 38.

Выход из режима анализа, изменить задержки и снова запустить моделирование.

3 Содержание отчета

3.1 Схемы RS-триггеров на элементах Пирса и элементах Шеффера (по ЕСКД).

3.2 ВД триггеров (динамический режим).

3.3 Таблицу переходов (статический режим).

3.4 Схемы синхронного RS-триггера и D-триггера.

3.4 ВД RS-триггера и D-триггера с комментариями.

4 Список литературы

4.1 В.А. Прянишников. «Электроника. Полный курс лекций» -С.Пб.: Корона 2003г.

4.2 В.Д. Разевиг. «Система схемотехнического моделирования Micro-Cap V» - М.: 1997г или более поздние издания.

4.3 Приложение к описанию лабораторных работ.