Многофункциональный вычислительный комплекс для обработки радиолокационных сигналов андреев Н. А., Животов А. В., Компаниец Ю. И., Рыбаков В. Ю

| Вид материала | Документы |

- Обработка сигналов в радиотехнических системах, 152.49kb.

- Вопросы к экзамену по дисциплине "Теория и проектирование алгоритмов цифровой обработки, 33.28kb.

- Ю. В. Смирнов московский инженерно-физический институт (государственный университет), 13.81kb.

- Рабочая программа дисциплины "Алгоритмы и средства цифровой обработки сигналов" для, 61.24kb.

- «Обработка изображений» Общая трудоемкость изучения дисциплины составляет, 15.75kb.

- Радиолокационных сигналов, 243.57kb.

- Программа учебной дисциплины «Теория сигналов» Специальности 071500, 013900 (СД. 05), 82.24kb.

- Т. Н. Зайченко Россия, Томск, Томский государственный университет систем управления, 85.43kb.

- Тема пространство и метрология сигналов физическая величина более точно определяется, 595.48kb.

- Н. Г. Чернышевского кафедра радиофизики и нелинейной динамики рабочая программа, 145.34kb.

Проектирование и техническая реализация систем ЦОС

- M.C. Valenti, S. Cheng, R. Seshdri, Turbo and LDPC codes for digital video broadcasting // Chapter 12 of Turbo Code Applications: A Journey from a Paper to Realization, Springer, 2005.

LDPC DECODER FPGA IMPLEMENTATION FOR DVB-S2

Chikin A.

NII Radio, Moscow, e-mail: avchikin@mail.ru

Abstract. The Low-Density Parity-Check (LDPC) decoding algorithm is gaining increased attention in DVB-S2 applications because of its excellent bit-error-rate performance. In the article we show results of FPGA algorithm implementation known as min-sum. For the required performance it takes 130 BRAM, 37700 Slice LUTs for 20 iterations and 100MHz system clock (60 iterations for 300MHz respectively).

МНОГОФУНКЦИОНАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ

Андреев Н.А., Животов А.В., Компаниец Ю.И., Рыбаков В.Ю.

ФГУП Государственный Рязанский приборный завод

Многофункциональный вычислительный комплекс (ВК) предназначен для управления блоками бортовой радиолокационной станции (БРЛС), аналого-цифрового преобразования, обработки радиолокационной информации, поступающей с высокочастотного приемника БРЛС, и отображения графической информации на внешней системе индикации.

Производительность ВК по обработке данных составляет 3200 МИПС, и по обработке сигналов – 115 ГФЛОПС.

По условиям эксплуатации, конструкция ВК должна обеспечивать компактность изделия, высокую стойкость к механическим воздействиям, эффективный отвод тепла от элементов, электромагнитную экранировку и защиту от попадания пыли и влаги.

Сравнительная сложность ВК требует его деления на функционально законченные устройства, выполненные в виде отдельных функционально-конструктивных модулей. Конструкция модуля выполнена на основе многослойно печатной платы размером 160х100 мм, соответствующей формату 3U стандарта «Евромеханика» IEEE Std 1101.2 1992, с кондуктивным отводом тепла через боковые теплосъемные клинья.

Конструкция герметизированного корпуса типоразмера 4К по ГОСТ 26765.16-87 размером 275х195х318 мм, обеспечивает размещение модулей в двух отсеках. В одном отсеке размещаются аналого-цифровые, в другом – цифровые модули ВК. Такое исполнение обеспечивает небольшие габариты корпуса и улучшение внутренней и внешней электромагнитной совместимости. Внешние кабели, включая радиочастотные, подключаются к ВК с помощью установленных на лицевой панели герметизированных цилиндрических соединителей байонетного или резьбового типа.

Отвод тепла от корпуса ВК осуществляется посредством принудительного воздушного охлаждения, для продувания воздуха, подаваемого от внешнего вентилятора, в боковых стенках корпуса выполнены сквозные каналы. Аналогично выполнена стенка, разделяющая отсеки ВК.

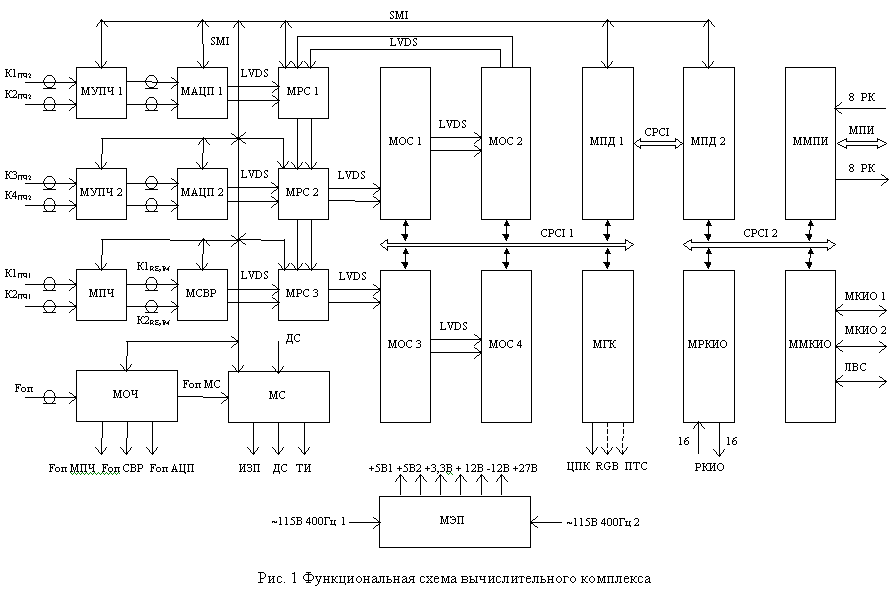

Функциональная схема вычислительного комплекса представлена на рисунке 1. В состав ВК входят следующие модули:

- модуль опорных частот (МОЧ);

- модуль синхронизации (МС);

- модуль усилителей промежуточной частоты (МУПЧ) – 2 шт.;

- модуль АЦП (МАЦП) – 2 шт.;

- модуль преобразователя частоты (МПЧ);

- модуль сверхвысокого разрешения (МСВР);

- модуль регистрации сигналов (МРС) – 3 шт.;

- модуль обработки сигналов (МОС) – 4 шт.;

- модуль графического контроллера (МГК);

- модуль процессоров данных (МПД) – 2 шт.;

- модуль магистрального параллельного интерфейса (ММПИ);

- модуль магистральных каналов информационного обмена (ММКИО);

- модуль радиальных каналов информационного обмена (МРКИО);

- модуль источника электропитания (МЭП).

Большинство применяемых в ВК комплектующих входят в «Номенклатуру высокотехнологичных ИЭТ, рекомендуемых к разработке в РФ и применению в РЭА двойного назначения» («Номенклатура-1»). Для реализации универсального процессора выбран RISC-процессор, а для реализации процессора цифровой обработки сигнала – специализированный сигнальный процессор. Схемы сложных логических узлов выполнены на основе программируемым интегральным логическим схемам, что обеспечивает возможность последующей реализации этих узлов на БМК.

Устройство управления, представленное двумя модулями процессоров данных, должно иметь функциональные связи со всеми устройствами ВК. Для управления цифровой частью ВК используется стандартная системная шина. С конструктивом модуля «Евромеханика» 3U хорошо сочетается системная шина CompactPCI (CPCI) [1]. При выбранной тактовой частоте 33 МГц и разрядности 32 эта шина обеспечивает пиковую производительность передачи данных в 132 Мбайт/с. Характеристики шины CompactPCI позволяют подключить к ней все цифровые модули ВК (МОС, МГК, МПД, ММПИ, ММКИО, МРКИО).

Для управления цифро-аналоговой частью ВК (МОЧ, МУПЧ, МПЧ, МАЦП, МСВР, МРС, МС) высокая производительность управляющего интерфейса не нужна, однако важными являются требования электромагнитной совместимости с аналоговыми устройствами. Для управления этими модулями используется последовательный управляющий интерфейс SMI (стандарт IEEE 802.3u) со скоростью передачи данных до 2,5 Мбит/с [2].

Учитывая большой объем цифровых данных, выдаваемых МАЦП и МСВР, в ВК используется специализированный высокоскоростной параллельно-последовательный интерфейс LVDS по ANSI/TIA/EIA 644, при тактовой частоте 60 МГц обеспечивающий скорость передачи данных 120 Мбайт/с для одного позиционного (или двух квадратурных) канала.

Модуль опорных частот осуществляет прием сигнала опорной частоты от генератора БРЛС и выработку сигналов опорных частот для модулей ВК.

Основные технические характеристики МОЧ:

- значение входной опорной частоты не менее 60 Мгц;

- значения выходных опорных частот – 1 * Fвх, 2 * Fвх, 4 * Fвх, 12 * Fвх.

Модуль преобразования частоты осуществляет прием аналогового сигнала двух каналов первой промежуточной частоты ПЧ1. МПЧ обеспечивает демодуляцию сигнала с получением двух сигналов квадратурных составляющих ДМ_Re, ДМ_Im по каждому каналу с последующей фильтрацией и усилением этих сигналов.

Основные технические характеристики МПЧ:

- значение центральной частоты входного сигнала не менее 1440 МГц;

- количество входных каналов – 2;

- количество выходных каналов – 4.

Модуль сверхвысокого разрешения осуществляет прием аналоговых сигналов двух каналов демодулятора (ДМ_Re1, ДМ_Im1, ДМ_Re2, ДМ_Im2). МСВР обеспечивает аналого-цифровое преобразование сигналов, буферизацию полученной цифровой информации и выдачу ее в модуль регистрации сигналов по интерфейсу LVDS.

Основные технические характеристики МСВР:

- количество входных каналов – 4;

- частота дискретизации не менее 240 Мгц.

- разрядность преобразователей не менее 10.

Модуль усилителей промежуточной частоты осуществляет прием аналогового сигнала двух каналов второй промежуточной частоты (далее ПЧ2). Сигнал каждого канала проходит через полосовой усилитель с программно управляемым коэффициентом усиления и переключаемой полосой пропускания пассивного полосового фильтра.

Основные технические характеристики МУПЧ:

- количество каналов – 2;

- значение центральной частоты сигнала не менее 90 МГц;

- пределы изменения коэффициента пропускания – 31 дБ.

Модуль АЦП осуществляет прием аналоговых сигналов двух каналов ПЧ2. Модуль обеспечивает аналого-цифровое преобразование сигналов, цифровую демодуляцию, предварительную цифровую фильтрацию, накопление сигналов, буферизацию полученной цифровой информации и выдачу ее в модуль регистрации сигналов по интерфейсу LVDS.

Основные технические характеристики МАЦП:

- количество входных каналов – 2;

- частота дискретизации не менее 120 Мгц.

- разрядность преобразователей не менее 14.

Модуль синхронизации обеспечивает функционирование БРЛС в соответствии с заданной циклограммой. МС получает опорную частоту от МОЧ. Модуль синхронизации осуществляет выработку тактового импульса ТИ, а также других синхронизирующих и управляющих сигналов для модулей из состава изделия ВК и блоков БРЛС.

Основные технические характеристики МС:

- количество выходных низкочастотных каналов – 32;

- количество выходных высокочастотных каналов – 8.

- количество входных/выходных дискретных сигналов – 16;

- количество выходных дискретных сигналов – 16.

Модуль регистрации сигналов осуществляет прием цифровой информации от МАЦП, МСВР или МОС по интерфейсу LVDS, передачу ее в МОС или другой МРС по интерфейсу LVDS в соответствии с режимом работы изделия, при необходимости регистрацию информации в собственной перепрограммируемой памяти, а также выдачу зарегистрированной информации в МОС для последующей обработки или передачи в инструментальную машину.

Основные технические характеристики МРС:

- скорость регистрации данных не менее 150 Мбайт/с;

- объем ПЗУ (флэш-памяти) не менее 64 Гбайт.

Модуль обработки сигналов осуществляет прием цифровой информации по интерфейсу LVDS, преобразование радиолокационной информации в соответствии с алгоритмом обработки, и передачу информации по интерфейсу LVDS в другой МОС или МРС, выдачу обработанной информации в МПД или данных изображения в режиме ПДП в МГК по шине CompactPCI [3].

Основные технические характеристики МОС:

- цифровой сигнальный процессор – ADSP–TS201S;

- тактовая частота сигнального процессора - 600 МГц;

- количество сигнальных процессоров – 8;

- объем динамического ОЗУ модуля -512 Мбайт;

- объем ППЗУ (флэш-памяти) - 8 Мбайт.

Модуль графического контроллера формирует и выдает видеосигнал для отображения графической информации на внешнюю систему индикации. Вывод цифрового видеосигнала осуществляется в соответствии с ARINC-818.

Основные технические характеристики МГК:

- скорость передачи - 1062 Мбит/с по симметричной и 266 Мбит/с по коаксиальной линии;

- максимальное разрешение изображения – 1600 x 1200 пикселей;

- глубина цвета – 24 бит/пиксель;

- объём внутреннего ОЗУ - 32 Мбайт.

Имеются модификации МГК с видеосигналом ПЦТС по ГОСТ 7845 92 или RGB (RS-343A).

Модуль процессора данных осуществляет управление модулями вычислительного комплекса по системной шине CompactPCI и интерфейсу SMI. МПД поддерживает обмен с инструментальной ПЭВМ по каналу технологического интерфейса (ТхИ).

Основные технические характеристики МПД:

- центральный процессор архитектуры MIPS R7000;

- тактовая частота не менее 800 МГц;

- внутренняя шина – 64 разряда, 100 МГц;

- две системных шины – CompactPCI, 32 разряда, 33 МГц;

- последовательный интерфейс SMI, 2,5 МГц;

- объём ОЗУ не менее 384 Мбайт;

- объём ППЗУ (флаш-память) не менее 2 Гбайт.

- скорость обмена по технологическому интерфейсу не менее 140 Кбайт/с.

Интерфейсные модули ММПИ, ММКИО и МРКИО обеспечивают сопряжение вычислительного комплекса с внешними устройствами бортового радиоэлектронного комплекса.

Модуль магистрального параллельного интерфейса реализует магистральный параллельный интерфейс МПИ в соответствии с ГОСТ 26765.51-86. Помимо этого модуль обеспечивает 8 выходных и 8 входных разовых команд в соответствии с требованиями ГОСТ 18977-79.

Модуль обеспечивает следующие виды взаимодействия на магистрали:

- адресный (одиночный или блочный) обмен словами;

- обмен по прерываниям;

- передача управления магистралью.

Модуль магистральных каналов информационного обмена реализует последовательный обмен данными по двум резервированным каналам в соответствии ГОСТ Р 52070 2003. ММКИО дополнительно поддерживает обмен по одному резервированному каналу локальной вычислительной сети в соответствии с IEEE802.3u 10BASE-T/100BASE-TX (Ethernet).

Модуль обеспечивает следующие режимы магистрального канала:

- режим контроллера канала;

- режим оконечного устройства.

Модуль контроллера радиальных каналов информационного обмена реализует обмен последовательными биполярными кодами в соответствии с ГОСТ 18977 79 и РТМ 1495-75.

Цифровая обработка сигналов и ее применение

Digital signal processing and its applications