Темы для сообщений Управляющие восьмиразрядные микроконтроллеры семейства avr

| Вид материала | Контрольные вопросы |

- Граммируемой логики, взяла старт по разработке risc-микроконтроллеров в середине 90-х, 161.19kb.

- Темы сообщений по предмету «Физическая культура» Темы сообщений делятся по секциям,, 116.56kb.

- Темы и направления курсовых работ Преподаватель: Бондарь Оксана Петровна, 22.19kb.

- Ходимы для реализации в составе «систем на кристалле» блоков управления, спроектированных, 48.74kb.

- 5. Однокристальные микроконтроллеры серии pic:, 354.07kb.

- Положение семейства в системе органического мира. Общая характеристика семейства Астровые, 118.43kb.

- Бюллетень новых поступлений Гуманитарная и прочая литература за март – апрель 2011, 132.13kb.

- В. Г. Косачев, Е. А. Дегальцева, О. В. Кадомцева, 628.29kb.

- Темы для кратких сообщений. Индекс конкурентоспособности (World Economic Forum), 41.73kb.

- Кий отчет, который содержит количественный и качественный анализ сообщений, попавших, 4199.36kb.

ФСПО. «МК и МП» Конспект лекции №1.3

Структурная организация МК. Память и регистры МК. Ассемблер. Группа команд передачи данных

План лекции:

Структурная организация МК. Память и регистры МК. Ассемблер. Группа команд передачи данных

Контрольные вопросы

Темы для сообщений

1.Управляющие восьмиразрядные микроконтроллеры семейства AVR

Концепция новых скоростных микроконтроллеров была разработана группой разработчиков исследовательского центра ATMEL в Норвегии, инициалы которых затем сформировали марку AVR. Первые микроконтроллеры AVR AT90S1200 появились в середине 1997 г. и быстро снискали расположение потребителей.

AVR-архитектура, на основе которой построены микроконтроллеры семейства AT90S, объединяет мощный гарвардский RISC-процессор с раздельным доступом к памяти программ и данных, 32 регистра общего назначения, каждый из которых может работать как регистр- аккумулятор, и развитую систему команд фиксированной 16-бит длины. Большинство команд выполняются за один машинный такт с одновременным исполнением текущей и выборкой следующей команды, что обеспечивает производительность до 1 MIPS на каждый МГц тактовой частоты.

32 регистра общего назначения образуют регистровый файл быстрого доступа, где каждый регистр напрямую связан с АЛУ. За один такт из регистрового файла выбираются два операнда, выполняется операция, и результат возвращается в регистровый файл. АЛУ поддерживает арифметические и логические операции с регистрами, между регистром и константой или непосредственно с регистром.

Регистровый файл также доступен как часть памяти данных. 6 из 32-х регистров могут использоваться как три 16-разрядных регистра-указателя для косвенной адресации. Старшие микроконтроллеры семейства AVR имеют в составе АЛУ аппаратный умножитель.

Базовый набор команд AVR содержит 120 инструкций. Инструкции битовых операций включают инструкции установки, очистки и тестирования битов.

Все микроконтроллеры AVR имеют встроенную FLASH ROM с возможностью внутрисхемного программирования через последовательный 4-проводной интерфейс.

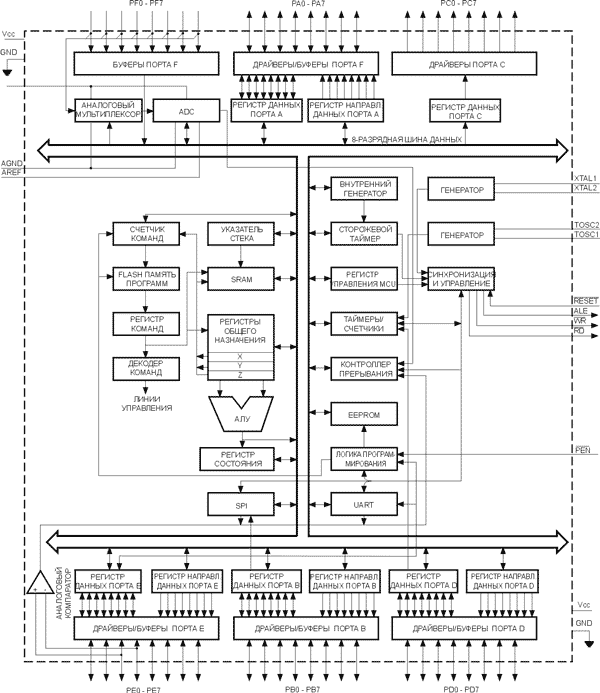

Периферия МК AVR включает: таймеры-счётчики, широтно-импульсные модуляторы, поддержку внешних прерываний, аналоговые компараторы, 10-разрядный 8-канальный АЦП, параллельные порты (от 3 до 48 линий ввода и вывода), интерфейсы UART и SPI, сторожеой таймер и устройство сброса по включению питания. Все эти качества превращают AVR-микроконтроллеры в мощный инструмент для построения современных, высокопроизводительных и экономичных контроллеров различного назначения.

В рамках единой базовой архитектуры AVR-микроконтроллеры подразделяются на подсемейства:

mega AVR с производительностью 1–16 MIPS для сложных приложений, требующих большого обьёма памяти, FLASH ROM программ 4–128 Кбайт, ЕEPROM данных 64–512 байт, SRAM 2–4 Кбайт, SRAM 4 Кбайт, встроенный 10-разрядный 8-канальный АЦП, аппаратный умножитель 8x8;

tiny AVR — низкостоимостные микроконтроллеры в 8-выводном исполнении имеют встроенную схему контроля напряжения питания, что позволяет обойтись без внешних супервизорных микросхем.

AVR-микроконтроллеры поддерживают спящий режим и режим микропотребления. В спящем режиме останавливается центральное процессорное ядро, в то время как регистры, таймеры-счётчики, сторожевой таймер и система прерываний продолжают функционировать. В режиме микропотребления сохраняется содержимое всех регистров, останавливается тактовый генератор, запрещаются все функции микроконтроллера, пока не поступит сигнал внешнего прерывания или аппаратного сброса. В зависимости от модели, AVR-микроконтроллеры работают в диапазоне напряжений 2,7–6 В либо 4–6 В (исключение составляет ATtiny12V с напряжением питания 1,2 В).

Средства отладки. ATMEL предлагает программную среду AVR-studio для отладки программ в режиме симуляции на программном отладчике, а также для работы непосредственно с внутрисхемным эмулятором. AVR-studio доступен с WEB-страницы ATMEL, содержит ассемблер и предназначен для работы с эмуляторами ICEPRO и MegaICE. Ряд компаний предлагают свои версии Си-компиляторов, ассемблеров, линковщиков и загрузчиков для работы с микроконтроллерами семейства AVR. Как и продукция MICROCHIP, микроконтроллеры ATMEL широко применяются в России и, как следствие, программируются многими отечественными программаторами. Ряд российских фирм предлагает также различные аппаратные средства отладки AVR-микроконтроллеров.

Отличительные особенности:

- Производительность, приближающаяся к 1 MIPS/МГц

- Усовершенствованная AVRa RISC архитектура

- Раздельные шины памяти команд и данных, 32 регистра общего назначения

- Внутрисхемно программируемая Flash-память программ, 1000 циклов записи/стирания

- Память данных EEPROM, 100000 циклов записи/стирания

- Блокировка режима программирования

- Встроенные аналоговый компаратор, сторожевой таймер, порты SPI и UART, таймеры/счетчики

- Полностью статические приборы - работают при тактовой частоте от 0 Гц до 20 МГц

- Диапазон напряжений питания от 1,8 В до 6,0 В

- Режимы энергосбережения: пассивный (idle) и стоповый (power down)

2.Структурная организация микроконтроллера AVR

Рисунок 1 – Структурная схема микроконтроллера семейства AVR

Архитектура микроконтроллеров ATmega603/ATmega103

Файл регистров быстрого доступа, содержит 32 8-разрядных рабочих регистра общего назначения связанных непосредственно с ALU. За один тактовый цикл из файла регистров выбираются два операнда, выполняется операция и результат вновь возвращается в файл регистров.

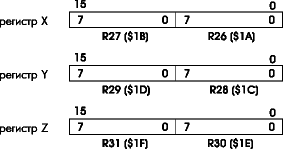

Шесть из 32 регистров могут быть использованы как три 16-разрядных регистра указателя косвенной адресации адресного пространства данных, обеспечивающие эффективное вычисление адресов. Один из этих указателей адреса используется, также, как указатель адреса для функции непрерывного просмотра таблиц. Эти 16-разрядные дополнительные регистры обозначаются X-регистр, Y-регистр и Z-регистр.

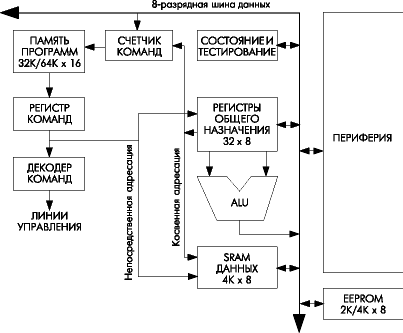

ALU поддерживает арифметические и логические операции между регистрами или между константой и регистром. Выполняются в ALU и операции с отдельными регистрами. На Рис. 2 показана AVR расширенная RISC архитектура микроконтроллеров ATmega603/103.

Рис. 2. AVR Enhanced RISC архитектура микроконтроллеров ATmega603/103

В дополнение к операциям с регистрами, регистровый файл может использоваться и для обычной адресации памяти. Это объясняется тем, что файл регистров располагается по 32 самыми младшими адресами пространства данных, и к ним можно обращаться как к обычным ячейкам памяти.

Пространство памяти I/O содержит 64 адреса периферийных функций CPU таких как: регистры управления, таймеры/счетчики, аналого-цифровые преобразователи и другие I/O функции. К памяти I/O можно обращаться непосредственно или как к ячейкам пространства памяти соответствующим адресам регистра файлов $20 - $5F.

В микроконтроллерах AVR использованы принципы Гарвардской архитектуры - отдельные память и шины для программ и данных. При работе с памятью программ используется одноуровневый конвейер - в то время, как одна команда выполняется, следующая команда выбирается из памяти программ, Такой прием позволяет выполнять команду в каждом тактовом цикле. Памятью программ является внутрисистемно программируемая Flash память. За малым исключением AVR команды имеют формат одного 16-разрядного слова, в связи с чем каждый адрес памяти программ содержит одну 16-разрядную команду.

В процессе обработки прерываний и вызовов подпрограмм адрес возврата счетчика команд (PC) сохраняется в стеке. Стек размещается в SRAM данных и, следовательно размер стека ограничен только общим размером SRAM и уровнем ее использования. Все пользовательские программы в подпрограммах возврата (прежде, чем подпрограммы или прерывания будут выполняться) должны инициализировать указатель стека (SP). 16-разрядный указатель стека, с возможностью чтения/записи располагается в пространстве I/O.

AVR архитектура поддерживает пять различных режимов адресации 4000 байт SRAM данных.

Гибкий модуль обработки прерываний имеет в пространстве I/O свой управляющий регистр с дополнительным битом разрешения глобального прерывания в регистре статуса. Все прерывания имеют свои векторы прерывания в таблице векторов прерывания, располагаемой в начале памяти программ. Приоритеты прерываний соответствуют положению векторов прерываний - прерывание с наименьшим адресом вектора имеет наивысший приоритет.

Все пространства памяти AVR архитектуры линейны и регулярны.

ALU - Арифметико-логическое устройство

Высокопроизводительное AVR ALU соединено непосредственно со всеми 32 быстродействующими регистрами общего назначения. За один тактовый цикл ALU выполняет операцию между регистрами этого регистрового файла. Операции ALU подразделяются на три основные категории: арифметические, логические и операции над битами.

Внутрисистемно программируемая Flash память программ

Коды программ микроконтроллеров ATmega603/103 записываются в 64/128 Кбайт встроенной внутрисистемно программируемой Flash памяти. Поскольку все команды имеют формат одного или двух 16-разрядных слов, то и память программ имеет организацию 32/64Кx16. Flash память обеспечивает не менее 1000 циклов стирания/записи.

Таблицы констант могут быть размещены в любом месте всего пространства памяти программ (см. описания команд LPM (Load Program Memory) - Загрузить байт памяти программ и ELPM (Extended Load Program Memory) - Загрузить байт памяти программ в расширенном режиме).

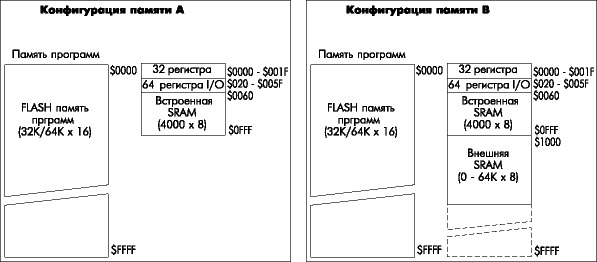

Конфигурация памяти

Микроконтроллеры ATmega603/103 поддерживают две конфигурации, как показано в таблице 1.

Таблица 1. Конфигурация памяти

| Конфигурация | Встроенная SRAM данных | Внешняя SRAM данных |

| A | 4000 байт | Нет |

| B | 4000 байт | До 64Кбайт |

По первым 4096 адресам памяти данных размещаются регистровый файл, пространство памяти I/O и встроенная SRAM данных. Из них первые 96 адресов занимают регистровый файл и пространство памяти I/O, в следующих 4000 адресов размещается встроенная SRAM.

Рис. 3. Конфигурация памяти

Микроконтроллеры конфигурации B позволяют использовать дополнительную внешнюю память данных. Внешняя память будет адресоваться оставшимся до 64К пространством адресов, т.е. оно будет начинаться следом за пространством адресов встроенной SRAM. При использовании внешней SRAM емкостью 64К будут потеряны 4К внешней памяти, поскольку адреса этого объема будут заняты встроенной памятью.

При обращении по адресам памяти данных за пределами встроенной SRAM используются те же команды, что для обращения к встроенной SRAM. При обращении к встроенной памяти данных выводы стробов управления внешней памятью данных (RD и WR) остаются неактивными во время всего цикла обращения.

Работа внешней SRAM разрешается установкой бита SRE в регистре MCUCR. По сравнению с обращением к встроенной памяти данных, обращение к внешней памяти данных требует дополнительного цикла на каждый байт. Это означает, что для выполнения команд LD, ST, LDS, STS, PUSH и POP требуется дополнительный тактовый цикл. Если стек размещен во внешней SRAM, то прерывания, вызов подпрограмм и возвраты потребуют два дополнительных цикла, поскольку в стеке будет опускаться и подниматься содержимое двухбайтового счетчика команд. Если интерфейс с внешней SRAM используется с состоянием ожидания, то на каждый байт необходимо еще два дополнительных тактовых цикла. Это приводит к следующему эффекту. Командам пересылки данных необходимо два дополнительных тактовых цикла, тогда как при обработке прерывания, вызове подпрограммы и при возврате из подпрограмм потребуется на четыре тактовых цикла больше, чем это указано в описании системы команд.

При адресации памяти данных используются пять режимов адресации: непосредственная адресация, косвенная со смещением, косвенная, косвенная с преддекрементом и косвенная с постдекрементом. Регистры с R26 по R31 регистрового файла работают как X, Y и Z регистры указатели косвенной адресации.

Косвенной адресации со смещением доступны 63 адреса относительно базовых адресов, находящихся в регистрах Y или Z. При использовании косвенной адресации с автоматическим преддекрементом и постдекрементом автоматически декрементируются и инкрементируются адреса записанные в регистры X, Y и Z. Всеми этими режимами перекрывается все адресное пространство данных, включая 32 регистра общего назначения и 64 регистра I/O. Подробное описание всех режимов адресации приведено в следующем разделе.

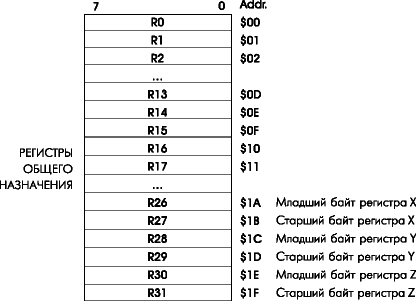

3.Файл регистров общего назначения

На Рис. 3 представлена структура 32 регистров общего назначения.

Рис. 3. Регистры общего назначения CPU микроконтроллеров AVR

Все регистровые команды обращаются непосредственно к регистрам в течение одного тактового цикла. Исключением являются пять логических и арифметических операций с константами (SBCI, SUBI, CPI и ANDI) и операция ORI между константой и содержимым регистра, и команда непосредственной загрузки константы LDI. Эти команды используют вторую половину регистров регистрового файла - R16..R31.

Самые общие команды SBC, SUB, CP, AND и OR и все прочие операции между двумя регистрами или с одним регистром используют для записи результата регистровый файл.

Как показано на Рис. 3, каждому регистру соответствует адрес памяти данных, отображающий их в первых 32 ячейках пользовательского пространства данных. Хотя они не используются как физические ячейки SRAM, такая организация памяти обеспечивает гибкое обращение к регистрам, поскольку X,Y и Z регистры могут быть использованы для индексации любого регистра в файле.

SRAM данных имеет объем 4 Кбайт и занимает адресное пространство от $0060 до $0FFF.

Регистр X, регистр Y и регистр Z

Шесть регистров (с R26 по R31) регистрового файла, кроме обычной для прочих регистров функций, выполняют функцию 16-разрядных регистров указателей адреса при косвенной адресации SRAM. Эти три регистра косвенной адресации определяются как регистры X,Y и Z.

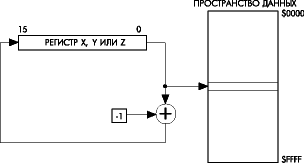

Рис. 6. Регистры X, Y и Z

В различных режимах адресации эти регистры выполняют функции фиксированного смещения, автоматического инкремента и декремента (см. описания команд).

4.Режимы адресации памяти программ и данных

При обращении к Flash памяти программ и памяти данных (SRAM, регистровому файлу и памяти I/O) AVR Enhanced RISC микроконтроллерами ATmega603/103 используются мощные и эффективные режимы адресации. В данном разделе описываются режимы адресации, поддерживаемые AVR архитектурой. На рисунках OP обозначает часть слова команды, соответствующую операционному коду.

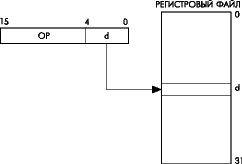

Непосредственная адресация, одиночный регистр Rd

Рис. 8. Непосредственная адресация одного регистра

Операнд содержится в регистре d (Rd).

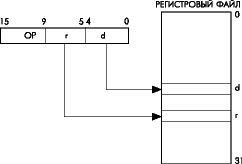

Непосредственная адресация, два регистра Rd и Rr

Рис. 9. Непосредственная регистровая адресация двух регистров

Операнды содержатся в регистрах r (Rr) и d (Rd).

Результат сохраняется в регистре d (Rd).

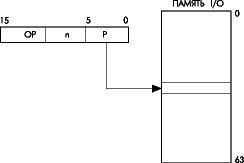

Непосредственная адресация I/O

Рис. 10. Непосредственная адресация I/O

Адрес операнда содержится в 6 битах слова команды. Величина n определяет адрес регистра источника или регистра назначения.

Непосредственная адресация данных

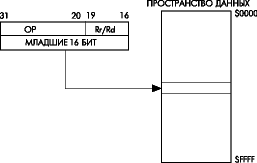

Рис. 11. Непосредственная адресация данных

16-разрядный адрес данных содержится в 16 младших разрядах 32-разрядной команды. Rd/Rr определяют регистр источник или регистр назначения.

Косвенная адресация данных со смещением

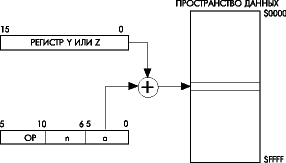

Рис. 12. Косвенная адресация данных со смещением

Адрес операнда вычисляется суммированием содержимого регистра Y или Z с 6 битами адреса, содержащимися в слове команды.

Косвенная адресация данных

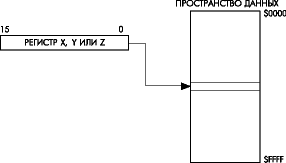

Рис. 13. Косвенная адресация данных

Адрес операнда содержится в регистре X, Y или Z.

Косвенная адресация данных с преддекрементом

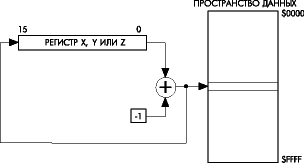

Рис. 14. Косвенная адресация данных с преддекрементом

Перед выполнением операции регистр X, Y или Z декрементируется. Декрементированное содержимое регистра X, Y или Z является адресом операнда.

Косвенная адресация данных с постинкрементом

Рис. 15. Косвенная адресация данных с постинкрементом

После выполнения операции регистр X, Y или Z инкрементируется. Адресом операнда является содержимое X, Y или Z регистра предшествовавшее инкрементированию.

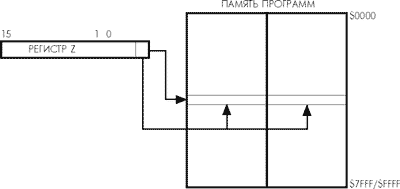

Адресация константы с использованием команд LPM и ELPM

Рис. 16. Адресация константы кода памяти

Адрес байта константы определяется содержимым регистра Z. Старшие 15 битов определяют слово адреса (от 0 до 32К). Состояние младшего бита определяет выбор младшего байта (LSB = 0) или старшего байта (LSB = 1). При использовании команды ELPM младший бит (RAM Page) регистра Z - RAMPZ используется для выбора страницы памяти (RAMPZ0 = 0:младшая страница, RAMPZ0 = 1:старшая страница). Команда ELPM не используется микроконтроллером ATmega603.

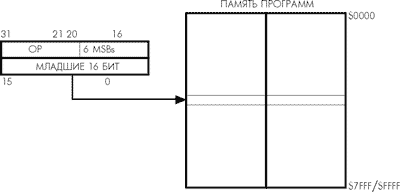

Непосредственная адресация памяти программ, команды JMP и CALL

Рис. 17. Непосредственная адресация памяти программ

Выполнение программы продолжается с адреса, записанного непосредственно в адресе команды.

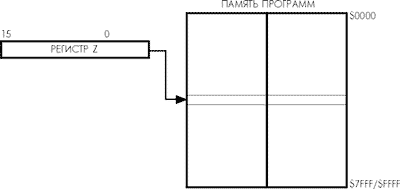

Косвенная адресация памяти программ, команды IJMP и ICALL

Рис. 18. Косвенная адресация памяти программ

Выполнение программы продолжается с адреса, содержащегося в регистре Z (т.е. счетчик команд загружается содержимым регистра Z).

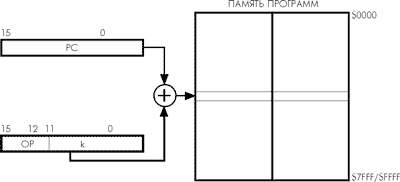

Относительная адресация памяти программ, команды RJMP и RCALL

Рис. 19. Относительная адресация памяти программ

Выполнение программы продолжается с адреса PC + k + 1. Значение относительного адреса может быть от -2048 до 2047.

5.Ассемблер

Машинный код – это набор чисел, которые интерпретируются центральным процессором компьютера и определяют выполняемые им действия. Машинный код состоит исключительно из двоичных чисел.

Язык ассемблера состоит из набора операторов, понятных человеку. Язык ассемблера однозначно связан с машинным кодом, т.е. каждый оператор языка ассемблера соответствует одной команде машинного кода.

Язык ассемблера тесно связан с архитектурой процессоров определенного семейства, т.е. он является не переносимым.

Исходную программу, написанную на языке ассемблера, нельзя непосредственно запустить на компьютере. Сначала ее нужно оттранслировать или, как говорят, ассемблировать в исполняемый код. По сути, программа ассемблер выполняет функции компилятора.

Компилятор работает с исходными файлами, содержащими инструкции, метки и директивы. Инструкции и директивы, как правило, имеют один или несколько операндов.

Строка кода не должна быть длиннее 120 символов.

Любая строка может начинаться с метки, которая является набором символов заканчивающимся двоеточием. Метки используются для указания места, в которое передаётся управление при переходах, а также для задания имён переменных.

Входная строка может иметь одну из четырёх форм:

[метка:] директива [операнды] [Комментарий]

[метка:] инструкция(мнемоника) [операнды] [Комментарий]

Комментарий

Пустая строка

Комментарий имеет следующую форму:

; [Текст]

Примеры:

label: .EQU var1=100 ; Устанавливает var1 равным 100 (Это директива)

.EQU var2=200 ; Устанавливает var2 равным 200

test: rjmp test ; Бесконечный цикл (Это инструкция)

; Строка с одним только комментарием

; Ещё одна строка с комментарием

Компилятор не требует чтобы метки, директивы, комментарии или инструкции находились в определённой колонке строки.

Директивы ассемблера

Компилятор поддерживает ряд директив. Директивы не транслируются непосредственно в код. Вместо этого они используются для указания положения в программной памяти, определения макросов, инициализации памяти и т.д.

Метка

По сути, метка является обычным идентификатором, с помощью которого в программе помечается некоторый участок кода или данных. В процессе обработки исходного текста программы ассемблер назначает каждому оператору программы числовой адрес. Таким образом, метке, размещенной непосредственно перед командой, также назначается адрес этой команды. Аналогично, если поместить метку перед переменной, ей будет назначен адрес этой переменной.

Метки кода. Метки, расположенные в коде программы, должны заканчиваться символом двоеточия (:). Подобные метки обычно используются для указания участка программы, которому будет передано управление в командах перехода или организации циклов. Метка в коде программы может находиться на одной строке с командой, либо занимать самостоятельную строку.

Метки данных. При использовании метки в сегменте данных программы (т.е. там, где размещаются и определяются переменные), она не должна заканчиваться символом двоеточия. Ниже приведен пример определения переменной под именем first.

При выборе имен меток следует учитывать общие правила для имен идентификаторов. Кроме того, имя, выбранное для метки, должно быть уникальным в пределах одного исходного файла программы. Например, если в файле с исходным кодом вашей программы уже есть метка с именем first, вы не можете присвоить это же имя другой метке, расположенной в том же файле.

Мнемоники команд

Мнемоникой команды называется короткое имя, с помощью которого определяется тип выполняемой процессором операции. В английском толковом словаре слово мнемоника определяется как методика запоминания чего-либо. По этой причине мнемоникам команд назначены короткие, но в тоже время осмысленные имена, такие как mov, add, sub, mul, jmp или call…

Операнды

В любой команде языка ассемблера может содержаться от одного до трех операндов. Кроме того, существует ряд команд, в которых нет операндов. В качестве операнда в команде может использоваться название регистра, ссылка на участок памяти, константное выражение или адрес порта ввода-вывода. Ссылка на участок памяти указывается в команде либо с помощью имени переменной, либо с помощью названия регистра, в котором содержится адрес нужной переменной. Вместо имени переменной ассемблер подставляет ее адрес. При этом он генерирует команду процессору на обращение к содержимому памяти, расположенной по данному адресу.

Комментарии

Комментарии очень важны для документирования программы. По сути, они являются средством общения разработчика программы с тем, кто будет сопровождать эту программу впоследствии.

Комментарии начинаются с символа точки с запятой (;). При этом все символы расположенные после точки с запятой и до конца текущей строки, игнорируются компилятором.

Выражения

Компилятор позволяет использовать в программе выражения которые могут состоять операндов, операторов и функций. Все выражения являются 32-битными.

Операнды

Могут быть использованы следующие операнды:

- Метки определённые пользователем (дают значение своего положения).

- Переменные определённые директивой SET

- Константы определённые директивой EQU

- Числа заданные в формате:

- Десятичном (принят по умолчанию): 10, 255

- Шестнадцатеричном (два варианта записи): 0x0a, $0a, 0xff, $ff

- Двоичном: 0b00001010, 0b11111111

- Восьмеричном (начинаются с нуля): 010, 077

- Десятичном (принят по умолчанию): 10, 255

- PC - текущее значение программного счётчика (Programm Counter)

Операторы

Компилятор поддерживает ряд операторов которые перечислены в таблице (чем выше положение в таблице, тем выше приоритет оператора). Выражения могут заключаться в круглые скобки, такие выражения вычисляются перед выражениями за скобками.

Функции

Определены следующие функции:

- LOW(выражение) возвращает младший байт выражения

- HIGH(выражение) возвращает второй байт выражения

- BYTE2(выражение) то же что и функция HIGH

- BYTE3(выражение) возвращает третий байт выражения

- BYTE4(выражение) возвращает четвёртый байт выражения

- LWRD(выражение) возвращает биты 0-15 выражения

- HWRD(выражение) возвращает биты 16-31 выражения

- PAGE(выражение) возвращает биты 16-21 выражения

- EXP2(выражение) возвращает 2 в степени (выражение)

- LOG2(выражение) возвращает целую часть log2(выражение)

6.Система команд микроконтроллера семейства AVR

Система команд микроконтроллеров ATMEL семейства AVR очень большая и в то же время эффективная. Одной из отличительных особенностей микроконтроллеров AVR является то, что почти все команды выполняются за 1 тактовый цикл. Исключение составляют команды перехода. Это существенно увеличивает производительность микроконтроллера даже при относительно невысокой тактовой частоте.

Все команды можно классифицировать на 5 типов:

- арифметические команды;

- логические команды;

- команды перехода;

- команды передачи данных;

- побитовые команды и команды тестирования битов.

Микроконтроллер имеет в своем составе 32 регистра. Первая их половина (R0-R15) не может быть использована в операциях с непосредственным операндом. Во второй половине есть специфические регистровые пары, которые могут использоваться в операциях пересылки данных между регистрами и памятью и некоторых других действий (X,Y и Z). Заметим к тому же, что "возможности" этих регистровых пар различны!

Кроме регистров, микроконтроллер может иметь память данных (ОЗУ), обращение к которой производится при помощи регистровых пар (индексная адресация) или указанием 16-ти разрядного адреса. Микроконтроллер может только прочесть память данных в регистр или записать туда из регистра, никакие арифметические или логические операции с памятью данных невозможны.

Регистры ввода-вывода (I/O). Можно прочитать данные из I/O в регистр общего назначения и записать из регистра общего назначения в I/O. Кроме этого, у части регистров ввода-вывода, а точнее - у тех, чей адрес не превышает 0x1F, возможна установка отдельных бит в состояние 0 или 1.

Обозначения, используемые при описании команд

Rd Результирующий (и исходный) регистр в регистровом файле

Rr Исходный регистр в регистровом файле

b Константа (3 бита), может быть константное выражение

s Константа (3 бита), может быть константное выражение

P Константа (5-6 бит), может быть константное выражение

K6 Константа (6 бит), может быть константное выражение

K8 Константа (8 бит), может быть константное выражение

k Константа (размер зависит от инструкции), может быть константное выражение

q Константа (6 бит), может быть константное выражение

Rdl R24, R26, R28, R30. Для инструкций ADIW и SBIW

X,Y,Z Регистры косвенной адресации (X=R27:R26, Y=R29:R28, Z=R31:R30)

Команды пересылки данных микроконтроллера 8051

| MOV Rd,Rs | Эта команда копирует содержимое регистра Rs в регистр Rd. Содержимое Rs не изменяется, предыдущее содержимое Rd теряется. Пример: mov R3,R19 ; содержимое R19 копируется в R3 Работает со всеми регистрами. Биты признаков не изменяет. |

| LDI Rd,K | Загружает в регистр Rd 8-ми разрядную константу. Работает со старшими регистрами (R16-R31). Пример: ldi R16,1 ; загружает в R16 значение 1 Биты признаков не изменяет. Если необходимо загрузить константу в младший регистр, то это делается двумя командами: ldi R16,1 ; загружает в R16 значение 1 mov R4,R16; и копирует в R4 |

| LD Rd,X | Загружает в регистр Rd байт из памяти данных, адрес ячейки памяти в регистровой паре X. Содержимое регистровой пары X не изменяется. Например: ldi XL,0 ; загружает младший байт регистровой пары Х ldi XH,2 ; -//- старший байт регистровой пары Х ld R5,X ; байт из ОЗУ с адресом 0x200 загружается в R5 Биты признаков не изменяет. |

| LD Rd,X+ | Аналогично предыдущей команде, но содержимое регистровой пары X после выполнения пересылки данных увеличивается на 1. Например: ldi XL,0 ; загружает младший байт регистровой пары Х ldi XH,2 ; -//- старший байт регистровой пары Х ld R5,X+ ; байт из ОЗУ с адресом 0x200 загружается в R5 ld R6,X+ ; байт из ОЗУ с адресом 0x201 загружается в R6 Биты признаков не изменяет. |

| LD Rd,-X | Аналогично предыдущей команде, но содержимое регистровой пары X перед выполнением пересылки данных уменьшается на 1. Например: ldi XL,0 ; загружает младший байт регистровой пары Х ldi XH,2 ; -//- старший байт регистровой пары Х ld R5,-X ; байт из ОЗУ с адресом ox1FF загружается в R5 ld R6,-X ; байт из ОЗУ с адресом 0x1FE загружается в R6 Биты признаков не изменяет. |

| LD Rd,Y LD Rd,Y+ LD Rd,-Y LD Rd,Z LD Rd,Z+ LD Rd,-Z | Эти команды работают абсолютно идентично трем ранее описанным, за исключением того, что индексным регистром является не X, а Y и Z. Наличие трех пар регистров дает возможность эффективной работы с блоками памяти, например: ldi XL,0x00 ;\первый блок памяти ldi XH,0x02 ; регистровая пара X указывает на адрес 0x200 ldi YL,0x80 ;\второй блок памяти ldi YH,0x01 ; регистровая пара Y указывает на адрес 0x180 ldi R16,10 ; счетчик на 10 LOOP: ld R5,X+ ; в R5 из первого блока, X указывает на следующий! st Y+,R5 ; из R5 во второй блок, Y также - на следующий dec R16 ; и так - 10 раз! brne LOOP В результате выполнения этого цикла 10 байт памяти, начиная с адреса 0x200 будут скопированы в область памяти с адресом 0x180 |

| LDD Rd,Y+q LDD Rd,Z+q | Регистровые пары Y и Z, кроме вышеописанных методов обращения к памяти данных, имеют еще один. В этом случае в регистр Rd загружается байт из ячейки памяти, чей адрес вычисляется как содержимое регистровой пары плюс 6-ти разрядное смещение. Содержимое регистровой пары не изменяется! Например: ldi YL,0 ; \ ldi YH,2 ; регистровая пара Y указывает на адрес 0x200 ldd R5,Y+5 ; байт из ОЗУ с адресом 0x205 загружается в R5 ldd R6,Y+10 ; байт из ОЗУ с адресом 0x210 загружается в R6 Такой режим адресации невозможен для регистровой пары X. Значение смещения q - от 0 до 63. |

| Мы рассмотрели команды LD и LDD, которые обеспечивают пересылку данных из памяти данных в регистр общего назначения. Естественно, что для каждой команды LD и LDD имеется "обратная" ей команда - записи в память данных из регистра. Эти команды имеют мнемоники соотвественно ST и STD (store). Например: ldd R5,Y+5 ; байт из ОЗУ с адресом 0x205 загружается в R5 std Y+6,R5 ; байт из R5 записывается в ОЗУ с адресом 0x206 Думаю, что совершенно нет необходимости расписывать каждую из них в отдельности... | |

| LDS Rd,A STS A,Rs | Команда LDS загрузит в регистр Rd содержимое ячейки памяти данных с адресом A, где A - шестнадцатиразрядная константа. В этом случае нет необходимости предварительно загружать регистровую пару, но сама команда займет два слова программной памяти, а не одно, как предыдущие. Например: lds R5,0x240 ; байт из ОЗУ с адресом 0x240 загружается в R5 sts 0x060,R5 ; байт R5 в ОЗУ с адресом 0x060 Парой для команды LDS является команда STS - записывающая содержимое регистра в память. |

| LPM | К командам пересылки данных надо отнести и очень специфичную команду LPM, которая пересылает в R0 байт памяти программ, на который указывает региcтровая пара Z. Напомню, что память программ и память данных между собой никак не пересекаются. Данная команда используется в основном для чтения таблиц констант, располагаемых в памяти программ. Например: TABLE: db 4,6,8,2,3,5,0 ;...... ldi ZL,low(TABLE*2) ldi ZH,hi(TABLE*2) LPM ; в R0 будет занесено число 4 Содержимое регистровой пары Z не изменяется, биты признаков - тоже. Вообще, ни одна команда пересылки данных не изменяет признаков. Важно! Поскольку для команды LPM адресация побайтная, а память программ адресуется словами (слово = 2 байта), то необходимо при загрузке адреса таблицы адрес умножить на 2! |

| IN Rd, I/O | Команда IN прочтет байт из регистра ввода-вывода в регистр общего назначения, например: in R18,PINA ; прочитать состояние входных линий порта A в R18 in R1,TCCR0 ; прочитать в R1 счетчик таймера 0 Работает со всеми регистрами, биты признаков не изменяет. |

| OUT I/O, Rs | А эта - из регистра выведет в порт. |

| PUSH Rs POP Rd | Эти команды предназначены для работы со стеком. Команда PUSH поместит Rs в стек, после выполнения команды указатель стека уменьшается на единицу. Команда POP извлечет байт из стека и поместит его в Rd. Соответственно, указатель стека увеличится на единицу. Указатель стека должен быть установлен (как правило - на последний байт ОЗУ) при старте программы! |

Контрольные вопросы

- Арифметико-логическое устройство.

- Память программ, память данных МК семейства AVR.

- Что такое машинный код? Как его получают?

- Что вы понимаете под Ассемблером?

- Формат команд языка ассемблер.

- Какие группы команд выделяют для МК семейства AVR?

- Какие режимы адресации используются в МК семейства AVR?

- Какие регистры есть в МК семейства AVR?

Темы для сообщений

- Представление отрицательных чисел в дополнительном коде.

- Булева алгебра