Лекция №6 Базовые матриЧные кристаллы бмк и библиотеки функциональных блоков

| Вид материала | Лекция |

- Лекция Геометрия (текстура) пористых тел, 291.61kb.

- Модулей, которые предназначены для модернизации электронной аппаратуры путем ее перевода, 24.38kb.

- Тематика лекций, презентаций, консультаций специалистов Национальной библиотеки Республики, 108.17kb.

- Александр Китайгородский: «Кристаллы», 619.42kb.

- Реферат по химии Тема: кристаллы, 109.08kb.

- А. М. Горького состоится лекция Директора библиотеки Наций, Председателя Комитета, 14.93kb.

- В. М. Красильщикова Советник отдела библиотек, 110.39kb.

- Методика устанавливает регламент поверки блоков на заводе-изготовителе, после ремонта, 85.36kb.

- Правила и порядок проверки теплосчетчика перед эксплуатацией (опробование). 13 3 Эксплуатация, 697.56kb.

- Лекция №15 «Выбор плис для реализации проекта», 104.99kb.

Лекция №6

Базовые матриЧные кристаллы БМК и библиотеки функциональных блоков

Особенности БИС на основе БМК

БИС на основе БМК часто называют матричными БИС или МаБИС. Для реализации МаБИС требуются:

а) Заготовки в пластинах с физическими структурами БМК;

б) Исходные данные для проектирования, включающие описание структуры БМК и библиотеки функциональных элементов.

в) САПР, настроенная на проектирование МаБИС на основе исходных данных БМК.

г) Функциональная схема конкретной МаБИС, построенная на элементах библиотеки БМК.

Если функциональная схема содержит новые функциональные блоки, то требуется доработка исходных данных.

Элементная база БМК

Для быстродействующих БИС используются биполярные логические элементы ЭСЛ или арсенид-галлиевые элементы на основе полевых транзисторов с затвором Шоттки.

Наибольшее распространение имеют БМК на КМОП структурах, обеспечивающие низкую стоимость и самую наименьшую потребляемую мощность.

Биполярные элементы ТТЛ появляются только в схемах с аналоговыми блоками или с мощными биполярными драйверами, так как легко реализуются на любых биполярных транзисторах.

Структуры на n-МОП транзисторах уже практически полностью потеряли конкурентоспособность.

Структура БМК.

Структура БМК включает в себя:

а) Периферийную зону, в которой размещены контактные площадки, входные трансляторы и выходные формирователи, элементы защиты от электростатического разряда, источники опорных напряжений и цепи питания.

б) Регулярную матрицу топологических ячеек.

Топологическая ячейка (ТЯ) - набор элементов (транзисторов, резисторов, диодов), регулярно повторяющийся на кристалл и достаточный для реализации функциональных элементов из библиотеки БМК. Иногда в БМК присутствуют две разных матрицы топологических ячеек. Например, одна для аналоговых функциональных элементов, другая - для цифровых.

в) Дополнительные цифровые блоки.

Базовые кристаллы могут иметь определенную специализацию и включать в свой состав универсальные блоки: ОЗУ, ПЗУ, ПЛМ.

Уровень сложности или степень интеграции БМК измеряется в эквивалентных вентилях. Уровень сложности - это количество простейших двухвходовых вентилей 2ИЛИ/НЕ (2И/НЕ) в самой сложной функциональной схеме, которая может быть реализована на данном БМК. В ЭСЛ схемах эквивалентных вентилей больше, чем физических, так как сами ЭСЛ вентили выполняют сложные функции. В КМОП БМК с плотной упаковкой топологических ячеек число эквивалентных вентилей меньше числа физических, так как никакая функциональная схема не может объединить все вентили без достаточного места для электрических соединений. Достигнутый уровень сложности для ЭСЛ БМК - 50 тысяч эквивалентных вентилей. Однако очень сложные схемы эффективнее реализуются на основе библиотеки функциональных блоков. Реально используемый уровень сложности до 3000 эквивалентных вентилей. Для КМОП достигнут уровень 300 тысяч эквивалентных вентилей. Реально используемый - 10 тысяч. Для БМК на арсениде галлия также достигнут уровень 300 тысяч эквивалентных вентилей. Реально используемый - 5 тысяч.

Сложность реально используемых БМК ограничена отнюдь не возможностями технологии, а условиями их проектирования и применения:

- эффективностью САПР;

- наличием многовыводных корпусов и технологии сборки;

- возможностями охлаждения МаБИС в аппаратуре;

- более высокой эффективностью реализации БИС на основе библиотеки функциональных блоков.

Избыточность БМК

В реальных МаБИС никогда не удается использовать все 100 % эквивалентных вентилей. При заполнении матрицы функциональными ячейками на 50 % САПР удается спроектировать топологию без вмешательства разработчика. При заполнении матрицы более чем на 50 % топология разрабатывается в интерактивном режиме с участием разработчика. Чем плотнее заполнение - тем сложнее проектировать, но кристалл будет меньше и производство дешевле. Для уменьшения избыточности БМК разрабатывают сериями. В серию входят несколько кристаллов разной сложности, но использующие общую библиотеку функциональных элементов. Сложность увеличивается примерно вдвое для каждого типа БМК в серии.

БМК на основе ЭСЛ вентилей

ЭСЛ схемотехника характеризуется высоким быстродействием, большой потребляемой мощностью, малым логическим перепадом. Из-за малого логического перепада помехоустойчивость схем низкая. Повышение помехозащищенности ЭСЛ схем достигается использованием низкоомных (50 Ом) линий связи и подключением большого числа выводов корпуса к цепям питания. Отдельные цепи питания используются для выходных каскадов.

Внешние логические уровни в цепях связи ЭСЛ микросхем бывают только двух сортов:

- нетермокомпенсированная серия (серии 100, 500 в СССР, F10K в США) с логическим перепадом в 0.8 В;

- термокомпенсированная серия (серии 1500 в СССР, F100K в США) с логическим перепадом 0.65 В.

Внутренний логический перепад обычно еще меньше: 0.40.5 В при передаче сигнала по одному проводнику и 0.15 В при передаче парафазного сигнала по двум проводникам.

В ЭСЛ схемотехнике обычно используются двухярусные и трехярусные переключатели тока. Типовой двухярусный вентиль достаточно сложен и включает около 15 элементов. Функциональные возможности ЭСЛ схемотехнике очень велики и позволяют выполнять логические функции проводным объединением коллекторных или эмиттерных нагрузок разных вентилей. Эффективно использование сложных логических элементов. Топологическая ячейка должна содержать элементы не менее чем для двух двухярусных переключателей тока, т.е. около 30 элементов.

В ЭСЛ БМК достаточно высокой степени интеграции (>1000 эквивалентных вентилей) часто используются топологические макроячейки, содержащие элементы для реализации 1020 вентилей. На базе макроячеек разрабатываются функциональные блоки сложностью 50100 эквивалентных вентилей. При этом достигается эффективность примерно 3 элемента топологической ячейки на эквивалентный вентиль.

Для реализации МаБИС на ЭСЛ БМК средней сложности (до 10 тысяч эквивалентных вентилей) используются 2 или 3 уровня металлизированных соединений, причем программируемых уровней только два. Если присутствует третий уровень, то он используется для подключения системы питания. Для МаБИС сложнее 10 тысяч эквивалентных вентилей применяются три программируемых уровня электрических соединений и четвертый уровень электропитания. Для двух программируемых уровней соединений требуется три заказных фотошаблона, а для четырех уровней - пять заказных фотошаблонов.

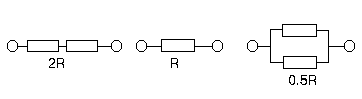

При работе внутренних ЭСЛ вентилей на различные нагрузки требуется управление их нагрузочной способностью. Управление нагрузочной способностью осуществляется изменением тока выходных эмиттерных повторителей. Для подключения генератора тока к эмиттерному повторителю в составе ТЯ предусмотрено два одинаковых резистора. Подключение резисторов тремя разными способами дает три разных уровня тока. Увеличение тока выходных эмиттерных повторителей в 2 или 4 раза приводит и к соответствующему изменению их нагрузочной способности.

рис. 6.1.

БМК на основе КМОП вентилей.

КМОП схемотехника характеризуется сравнительно невысоким быстродействием. Задержки вентилей в реальной схеме в 810 раз больше, чем для ЭСЛ схемотехники. Главные достоинства КМОП схемотехники - это малая потребляемая мощность и высокая помехоустойчивость (Uл=Uпит). Из этих достоинств вытекают и преимущества аппаратуры на этих микросхемах:

- дешевые малогабаритные корпуса;

- плотная упаковка корпусов на плате;

- отсутствие специального охлаждения аппаратуры или простота охлаждения с одним вентилятором;

- простота реализации линий связи между ИМС в многослойной плате;

- отсутствие дополнительных резисторов в линиях связи между ИМС на плате.

Внешние логические уровни в цепях связи КМОП микросхем соответствуют напряжению источника питания (0 В и +Uпит). В большинстве случаев Uпит=5 В. В новых разработках КМОП БИС используется источник питания +3 В. Соответственно изменяется и выходное напряжение высокого уровня. Внутренние логические уровни соответствуют внешним и нет необходимости во входных трансляторах.

Логический вентиль очень прост и содержит 4 транзистора. Схемы с проводными объединениями не используются. Сложные логические функции реализуются путем последовательного выполнения простых. Топологические ячейки КМОП БМК содержат от 4 до 10 транзисторов. На 10-транзисторной ТЯ можно развести 5-входовой логический вентиль И-ИЛИ/НЕ. Библиотека функциональных элементов строится по иерархическому принципу:

- первый уровень - простые вентили на одной ТЯ;

- второй уровень - функциональные элементы на нескольких ТЯ (макроэлементы);

- третий уровень - функциональные блоки.

Проектирование МаБИС ведется уже на уровне элементов второго и третьего уровней.

Матрица топологических ячеек обычно очень плотно упакована, включает трассировочные каналы или полностью заполнена ячейками по принципу “море вентилей”. Для структуры типа “море вентилей” трассировочные каналы назначаются разработчиком в необходимых местах прямо на неподключенных ячейках.

Для реализации МаБИС используется 23 уровня электрических соединений. Однако для снижения цены разработки часто используется только 23 программируемых фотошаблона. И только для самых сложных кристаллов используются четыре программируемых фотошаблона.

Управление нагрузочной способностью КМОП функциональных элементов осуществляется путем параллельного включения нескольких обычных инверторов, построенных на элементах ТЯ.

БМК на арсениде галлия.

Логические элементы на арсениде галлия построены на полевых транзисторах с затвором Шоттки и каналом n-типа. Вентили потребляют ток в статическом режиме. Вентили на арсениде галлия обладают высоким быстродействием и самым лучшим фактором качества (произведением мощности на время задержки). Стоимость кристаллов с микросхемами на GaAs примерно в 10 раз больше стоимости ЭСЛ биполярных кристаллов. Стоимость МаБИС в значительной степени определяется затратами на проектирование, подготовку производства, сборку и контроль, которые не зависят от материала кристалла. Поэтому цена МаБИС на арсениде галлия в 23 раза больше, чем для ЭСЛ МаБИС при той же степени интеграции. Применяются микросхемы на арсениде галлия в устройствах с рекордным быстродействием или в быстродействующих блоках с ограниченной потребляемой мощностью.

Внешние логические уровни ИМС на арсениде галлия обычно соответствуют требованиям к ЭСЛ микросхемам. Иногда применяют и ТТЛ-совместимые ИМС. Соответственно используются GaAs ИМС совместно с ЭСЛ или ТТЛ микросхемами. Самостоятельного применения в цифровой электронике эти изделия не имеют. Логический перепад для внутренних логических элементов 0.60.7В.

Схемотехника логических элементов на арсениде галлия очень похожа на схемотехнику n-канальных МОП транзисторов. Вентиль содержит 34 транзистора. Принципы выбора топологических ячеек БМК соответствуют МОП-схемотехнике. Библиотечные элементы БМК строятся по иерархическому принципу на основе небольшого количества простейших вентилей. Часто используется плотноупакованная матрица типа “море вентилей”.

Основное отличие БМК на арсениде галлия от изделий на МОП транзисторах - это высокая стоимость кристаллов, которая диктует другую стратегию проектирования системы электрических соединений. Для уменьшения площади ИМС используется от 3 до 6 уровней разводки электрических соединений. Программируемых уровней от 2 до 4, а число заказных фотошаблонов, соответственно, от 4 до 8. Уменьшение площади кристалла требуется и для увеличения системного быстродействия логических вентилей.

Управление нагрузочной способностью GaAs-вентилей осуществляется как и в КМОП параллельным объединением нескольких инверторов.

Принципы проектирования БИС на библиотечных блоках.

Проектирование БИС на библиотечных блоках эффективно только для изделий достаточно высокой интеграции (3000 вентилей и более), а также при наличии самой библиотеки крупных блоков, достаточной для реализации конкретной функциональной схемы. На вентильном уровне проектирование легче вести на регулярной матрице БМК.

Эффективность метода библиотечных блоков проявляется при использовании в БИС разнородных функциональных устройств: ОЗУ, ПЗУ, аналоговые блоки, мощные выходные драйверы и т.д. В качестве библиотечных блоков могут использоваться фрагменты матрицы БМК или разработанные ранее заказные БИС. В ряде случаев необходима разработка новых дополнительных блоков для расширения библиотеки. Нет резкой границы между методом библиотечных блоков и методом заказного проектирования. Отличия только количественные в объеме подготовительной работы по созданию библиотеки блоков.

Снижение стоимости изделия при проектировании достигается не только за счет автоматизации, но и за счет унификации конструктивных решений на основе базовых конструкций. Как и для БМК, в методе библиотечных блоков используют ряд базовых конструкций, объединенных типом корпуса, размером кристалла, расположением питающих и сигнальных выводов. Базовые конструкции очень снижают затраты на подготовку производства.