Адресная структура команд микропроцессора и планирование ресурсов > 4 Виртуальная память > Система прерываний ЭВМ глава центральные устройства ЭВМ 1 Основная память

| Вид материала | Документы |

- Лекция Понятие об архитектуре компьютера, 241.89kb.

- Структура 32-разрядного универсального микропроцессора, 36.41kb.

- Реферат по курсу : «эвм и периферийные устройства» на тему: Микропроцессор В1801ВМ1, 162.43kb.

- Реферат на тему: "Внешние устройства персонального компьютера.", 375.1kb.

- Общая структура мпс, 582.11kb.

- Программа курса «unix», 18.71kb.

- 1 История развития компьютерной техники, поколения ЭВМ и их классификация Развитие, 1329.92kb.

- Малых ЭВМ (СМ эвм), 153.2kb.

- Тематическое планирование «Информатика» в 5 класс, 131.73kb.

- Лекция 5 Внутренняя память, 178.2kb.

Состав, устройство и принцип действия основной памяти

Комплекс технических средств, реализующих функцию памяти, называется запоминающим устройством (ЗУ). ЗУ необходимы для размещения в них команд и данных. Они обеспечивают центральному процессору доступ к программам и информации.

Запоминающие устройства делятся на:

основную память,

сверхоперативную память (СОЗУ)

внешние запоминающие устройства.

Основная память включает в себя два типа устройств: оперативное запоминающее устройство (ОЗУ или RAM - Random Access Memory) и постоянное запоминающее устройство (ПЗУ или ROM - Read Only Memory).

ОЗУ предназначено для хранения переменной информации. Оно допускает изменение своего содержимого в ходе выполнения процессором вычислительных операций с данными и может работать в режимах записи, чтения, хранения.

ПЗУ содержит информацию, которая не должна изменяться в ходе выполнения процессором вычислительных операций, например стандартные программы и константы. Эта информация заносится в ПЗУ перед установкой микросхемы в ЭВМ. Основными операциями, которые может выполнять ПЗУ, являются чтение и хранение.

Функциональные возможности ОЗУ шире, чем ПЗУ Но ПЗУ сохраняет информацию при отключении питания (т.е. является энергонезависимой памятью) и может иметь более высокое быстродействие, так как ограниченность функциональных возможностей ПЗУ и его специализация на чтении и хранении позволяют сократить время выполнения реализуемых им операций считывания.

В современных ЭВМ микросхемы памяти (ОП и СОЗУ) изготавливают из кремния по полупроводниковой технологии с высокой степенью интеграции элементов на кристалле (микросхемы памяти относятся к так называемым “регулярным” схемам, что позволяет сделать установку элементов памяти в кристалле (чипе) настолько плотной, что размеры элементов памяти становятся сопоставимыми с размерами отдельных атомов).

Основной составной частью микросхемы является массив элементов памяти (ЭП), объединенных в матрицу накопителя.

Каждый элемент памяти может хранить 1 бит информации и имеет свой адрес. ЗУ, позволяющие обращаться по адресу к любому ЭП в произвольном порядке, называются запоминающими устройствами с произвольным доступом.

При матричной организации памяти реализуется координатный принцип адресации ЭП, в связи с чем адрес делится на две части (две координаты) - Х и Y. На пересечении этих координат находится элемент памяти, чья информация должна быть прочитана или изменена.

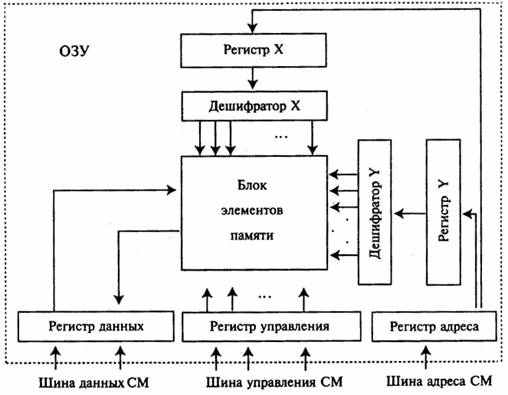

ОЗУ связано с остальным микропроцессорным комплектом ЭВМ через системную магистраль (рис.5.1).

Рис. 5.1. Структурная схема ОЗУ

По шине управления передается сигнал, определяющий, какую операцию необходимо выполнить.

По шине данных передается информация, записываемая в память или считываемая из нее.

По шине адреса передается адрес участвующих в обмене элементов памяти (поскольку данные передаются машинными словами, а один ЭП может воспринять только один бит информации, блок элементов памяти состоит из n матриц ЭП, где n - количество разрядов в машинном слове). Максимальная емкость памяти определяется количеством линий в шине адреса системной магистрали: если количество линий обозначить от, то емкость памяти (т.е. количество элементов памяти, имеющих уникальные адреса) определяется как 2m. Так, в IBM PC XT шина адреса СМ содержит 20 линий. Поэтому максимальный объем ОП в этих машинах равен 220 = 1 Мбайт. В IBM PC AT (с микропроцессором i80286) СМ содержит 24 линии, поэтому объем ОП может быть увеличен до 16 Мбайт. Начиная с МП i80386, шина адреса содержит 32 линии. Максимальный объем ОП увеличился до 232= 4Гб.

Микросхемы памяти могут строиться на статических (SRAM) и динамических (DRAM) ЭП. В качестве статического ЭП чаще всего выступает статический триггер. В качестве динамического ЭП может использоваться электрический конденсаторб сформированный внутри кремниевого кристалла.

Статические ЭП способны сохранять свое состояние (0 или 1) неограниченно долго (при включенном питании). Динамические ЭП с течением времени записанную в них информацию теряют (например, из-за саморазряда конденсатора), поэтому они нуждаются в периодическом восстановлении записанной в них информации - в регенерации.

Микросхемы элементов памяти динамических ОЗУ отличаются от аналогичных ЭП статических ОЗУ меньшим числом компонентов в одном элементе памяти, в связи с чем имеют меньшие размеры и могут быть более плотно упакованы в кристалле. Однако из-за необходимости регенерации информации динамические ОЗУ имеют более сложные схемы управления.

Основными характеристиками ОЗУ являются объем и быстродействие.

В современных ПЭВМ ОЗУ имеет модульную структуру. Сменные модули могут иметь различное конструктивное исполнение (SIP, ZIP, SIMM, DIMM). Увеличение объема ОЗУ обычно связано с установкой дополнительных модулей, которые выпускаются в 30-контактном (30-pin) и 72-контактном исполнениях на 1,4, 8, 16, 32 и 64 Мбайта. Время доступа к модулям DRAM составляет 60 - 70 нc.

На производительность ЭВМ влияет не только время доступа, но и такие параметры (связанные с ОЗУ), как тактовая частота и разрядность шины данных системной магистрали. Если тактовая частота недостаточно высока, то ОЗУ простаивает в ожидании обращения. При тактовой частоте, превышающей возможности ОЗУ, в ожидании будет находиться системная магистраль, через которую поступил запрос в ОЗУ.

Разрядность шины данных (8, 16, 32 или 64 бита) определяет длину информационной единицы, которой можно обменяться с ОЗУ за одно обращение.

Интегральной характеристикой производительности ОЗУ с учетом частоты и разрядности является пропускная способность, которая измеряется в Мегабайтах в секунду. Для ОП с временем доступа 60-70 не и разрядностью шины данных 64 бита максимальная (теоретическая) пропускная способность при тактовой частоте СМ 50 МГц составляет 400 Мбайт/с, при частоте 60 МГц - 480 Мбайт/с, при 66 МГц - 528 Мбайт/с в режиме группового обмена, реализуемом, например, при прямом доступе к памяти. Для группового обмена характерно (и это является еще одной характеристикой ОЗУ), что при каждом обращении к памяти для считывания первого слова необходимо больше времени, чем для последующих. Так, при использовании стандартной динамической памяти FPM (Fust Page Mode) DRAM на 60-70 не каждое обращение к памяти в групповом режиме описывается формулой 7-3-3-3, т.е. для обработки первого слова необходимо 7 тактов (в течение 6 из которых СМ простаивает в ожидании), а для обработки следующих трех слов - по 3 такта, по 2 из которых СМ простаивает. Память типа EDO (Extended Data Output)-DRAM позволяет уменьшить количество циклов ожидания (х-2-2-2, где х - количество тактов, необходимое для обработки первого слова). Память типа BEDO (Burst EDO) DRAM обеспечивает обмен по формуле х-1-1-1 для первого обращения и1-1-1-1- для последующих. Приведенные формулы характерны для тактовых частот до 60 МГц. Синхронная динамическая память (SDRAM - Synchronous DRAM) способна обмениваться блоками данных на рабочей тактовой частоте (внешняя частота процессора) без циклов ожидания: при времени доступа 10 не - до 100 МГц, 12 нс - до 83МГц 15 нс - до 66 МГц.

Микросхемы ПЗУ также построены по принципу матричной структуры накопителя. Функции элементов памяти в них выполняют перемычки в виде пероводников, полупроводниковых диодов или транзисторов. В такой матрице наличие перемычки может означать “I”, а ее отсутствие - “О”. Занесение формации в микросхему ПЗУ называется ее программированием, а устройство, с помощью которого заносится информация, - программатором. программирование ПЗУ заключается в устранении (прожигании) перемычек по тем адресам, где должен храниться “О”. Обычно схемы ПЗУ допускают только одно программирование, но специальные микросхемы - репрограммируемые ПЗУ (РПЗУ) - допускают их многократное стирание и занесение новой информации. Этот вид микросхем также относится к энергозависимым, т.е. может длительное время сохранять информацию при выключенном питании (стирание микросхемы происходит либо за счет подачи специального стирающего напряжения, либо за счет воздействия на кристалл ультрафиолетового излучения, для этого в корпусе микросхемы оставляется прозрачное окно).

Сверхоперативные ЗУ используются для хранения небольших объемов формации и имеют значительно меньшее время (в 2 - 10 раз) считывания/запииси, чем основная память. СОЗУ обычно строятся на регистрах и регистровых структурах.

Регистр представляет собой электронное устройство, способное хранить несенное в него число неограниченно долго (при включенном питании). Наиболыпее распространение получили регистры на статических триггерах.

По назначению регистры делятся на регистры хранения и регистры сдвига. Информация в регистры может заноситься и считываться либо параллельно, азу всеми разрядами, либо последовательно, через один из крайних разрядов с последующим сдвигом занесенной информации.

Сдвиг записанной в регистр информации может производиться вправо или влево. Если регистр допускает сдвиг информации в любом направлении, он называется реверсивным.

Регистры могут быть объединены в единую структуру. Возможности такой структуры определяются способом доступа и адресации регистров.

Если к любому регистру можно обратиться для записи/чтения по его адресу, такая регистровая структура образует СОЗУ с произвольным доступом.

Безадресные регистровые структуры могут образовывать два вида устройств памяти: магазинного типа и память с выборкой по содержанию (ассоативные ЗУ).

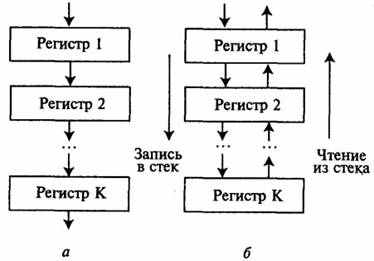

Память магазинного типа образуется из последовательно соединенных регистров (рис. 5.2).

Если запись в регистровую структуру (рис.5.2,д) производится через один регистр, а считывание - через другой, то такая память является аналогом нии задержки и работает по принципу “первым вошел - первым вышел” (FIFO - first input, first output).

Если же запись и чтение осуществляются через один и тот же регистр (рис.5.2,6), такое устройство называется стековой памятью, работающей по принципу “первым вошел — последним вышел” (FILO - first input, last output). При записи числа в стековую память сначала содержимое стека сдвигается в сторону последнего, К-го регистра (если стек был полностью заполнен, то число из К-го регистра теряется), а затем число заносится в вершину стека -регистр 1. Чтение осуществляется тоже через вершину стека, после того как число из вершины прочитано, стек сдвигается в сторону регистра 1.

Рис.5.2. Регистровая структура магазинного типа: а - типа FIFO; б - типа FILO

Стековая память получила широкое распространение. Для ее реализации в ЭВМ разработаны специальные микросхемы. Но часто работа стековой памяти эмулируется в основной памяти ЭВМ: с помощью программ операционной системы выделяется часть памяти под стек (в IBM PC для этой цели выделяется 64 Кбайта). Специальный регистр микропроцессора (указатель стека) постоянно хранит адрес ячейки ОП, выполняющей функции вершины стека. Чтение числа всегда производится из вершины стека, после чего указатель стека изменяется и указывает на очередную ячейку стековой памяти (т.е. фактически стек остается неподвижным, а перемещается вершина стека). При записи числа в стек сначала номер ячейки в указателе стека модифицируется так, чтобы он указывал на очередную свободную ячейку, после чего производится запись числа по этому адресу. Такая работа указателя стека позволяет реализовать принцип “первым вошел - последним вышел”. В стек может быть загружен в определенной последовательности ряд данных, которые впоследствии считываются из стека уже в обратном порядке, на этом свойстве построена система арифметических преобразований информации, известная под названием “логика Лукашевича”.

Память с выборкой по содержанию является безадресной. Обращение к ней осуществляется по специальной маске, которая содержит поисковый образ. Информация считывается из памяти, если часть ее соответствует поисковому образу, зафиксированному в маске. Например, если в такую память записана информация, содержащая данные о месте жительства (включая город), и необходимо найти сведения о жителях определенного города, то название этого города помещается в маску и дается команда чтение - из памяти выбираются все записи, относящиеся к заданному городу.

В микропроцессорах ассоциативные ЗУ используются в составе кэш-памяти для хранения адресной части команд и операндов исполняемой программы. При этом нет необходимости обращаться к ОП за следующей командой или требуемым операндом: достаточно поместить в маску необходимый адрес, если искомая информация имеется в СОЗУ, то она будет сразу выдана. Обращение к ОП будет необходимо лишь при отсутствии требуемой информации в СОЗУ. За счет такого использования СОЗУ сокращается число обращений к ОП, а это позволяет экономить время, так как обращение к СОЗУ требует в 2 - 10 раз меньше времени, чем обращение к ОП.

Кэш-память может быть размещена в кристалле процессора (так называемая “кэш-память I уровня”) или выполнена в виде отдельной микросхемы (внешняя кэш-память или кэш-память II уровня). Встроенная кэш-память (I уровня) в процессорах Pentium имеет объем около 16 Кбайт, время доступа - 5 - 10 не, работает с 32-битными словами и при частотах 75-166 МГц обеспечивает пропускную способность от 300 до 667 Мбайт/с. Внешняя кэшпамять (П уровня) имеет объем 256 Кбайт - 1 Мбайт, время доступа - 15 не, работает с 64-битными словами и при частоте 66 МГц обеспечивает максимальную пропускную способность 528 Мбайт/с. Конструктивно исполняется либо в виде 28-контактной микросхемы, либо в виде модуля расширения на 256 или 512 Кбайт.

Размещение информации в основной памяти IBM PC

Адресуемой единицей информации основной памяти IBM PC является байт. Это означает, что каждый байт, записанный в ОП, имеет уникальный номер (адрес). При использовании 20-битной шины адреса абсолютный (физический) адрес каждого байта является пятиразрядным шестнадцатеричным числом, принимающим значения от 00000 до FFFFF. В младших адресах располагаются блоки операционной системы (векторы прерываний, зарезервированная область памяти BIOS), в этой же части могут размещаться драйверы устройств, дополнительные обработчики прерываний DOS и BIOS, командный процессор операционной системы. Затем располагается область памяти, отведенная пользователю. Область памяти пользователя заканчивается адресом 9FFFF. Этот адрес является физической границей оперативного ЗУ, последним адресом 640-Кбайтной основной памяти. Остальное адресное пространство (128 Кбайт с адреса АОООО по BFFFF) отведено под видеопамять, которая физически размещается не в ОП, а в адаптере дисплея. После видеопамяти расположено адресное пространство (256Кбайт) постоянного запоминающего устройства (ПЗУ), хранящего программы базовой системы ввода-вывода (BIOS - “Basic Input — Output System”). Эта часть ОП еще называется ROM-BIOS. Из отведенных 256 Кбайт непосредственно ПЗУ занимает 64 Кбайта, а остальные 192 Кбайт оставлены для расширения ПЗУ. Поскольку большая часть оставленной для расширения BIOS части адресного пространства не используется, в этих адресах часто располагается информация, необходимая для работы сетевых карт, графических расширителей и др.

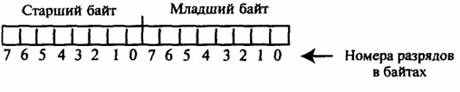

Запись в ОП (и чтение из нее) может осуществляться не только байтами, но и машинными словами. При этом машинное слово при размещении в памяти занимает несколько смежных байтов. Каждый байт ОП имеет свой адрес. Но машинное слово характеризуется не всеми адресами занятых байтов, а только одним - адресом младшего байта слова. Обычно графически машинное слово изображается так, что младший байт находится

Рис.5.3. Стереотипное представление машинного слова

При записи слова младший байт размещается по адресу, который является адресом машинного слова, старший байт машинного слова размещается в следующем по порядку байте ОП, имеющем номер, увеличенный на 1 (здесь действует мнемоническое правило “младший байт - по младшему адресу”).

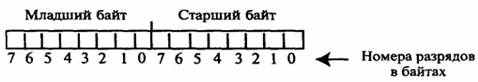

Рис. 5.4. “Вращение” байтов при чтении машинного слова из ОП

При чтении из ОП двух следующих подряд байтов машинного слова их принято размещать слева направо: сначала первый из прочитанных байтов (с меньшим адресом), а затем - следующий. В результате происходит “вращение” байтов (рис.5.4), которое психологически трудно воспринимается. Необходимо помнить, что при записи отдельных байтов каждый байт располагается в ОП по своему адресу, при чтении никакого вращения не происходит. При записи же в ОП единиц информации, имеющих в своем составе больше одного байта, адресом информационной единицы является адрес самого младшего байта, запись в ОП ведется побайтно, начиная с самого младшего байта, каждый последующий байт располагается в ячейке, адрес которой на 1 больше предыдущего. Иными словами, запись машинного или двойного слова производится справа налево, тогда как при чтении считанные байты обычно располагаются слева направо - происходят “вращение” байтов, перестановка их местами, что необходимо учитывать при работе с ОП на физическом уровне.

Расширение основной памяти IBM PC

Рабочая концепция фирмы IBM при создании IBM PC содержала гипотезу, что объем основной памяти ЭВМ, предназначенной для персонального использования в любой предметной области, не должен превышать 640 Кбайт. Поэтому в базовую модель IBM PC заложили 20-разрядную шину адреса системной магистрали. Наличие 20 линий в шине адреса позволяло адресовать память большего объема, чем было предусмотрено концепцией (220 = 1 Мбайт). “Излишек” адресного пространства в 384 Кбайт был поделен между видеопамятью (128 Кбайт) и ПЗУ (256 Кбайт).

Физически увеличить объем памяти несложно, для этого необходимо только подключить к системной магистрали дополнительные модули. Такая возможность в IBM PC была предусмотрена. Но каждый байт дополнительной памяти должен иметь уникальный адрес, а адресного пространства для дополнительной памяти нет.

Существует несколько способов разрешения таких конфликтов. Один из них - банкирование памяти: вся память делится на блоки (банки), емкость которых не выходит за пределы допустимого адресного пространства; во время работы специальными командами можно переключать банки, делая активным любой из них или осуществляя групповую перепись информации из одного банка в другой.

В ЮМ PC XT фирма IВМ применила другой способ: 256 Кбайт было сначала оставлено для ПЗУ, в котором размещалась базовая система ввода-вывода (BIOS). Анализ программ BIOS показал, что в оставленном для ПЗУ адресном пространстве (UMB - Upper Memory Block) имеются “окна” - неиспользуемые участки. Четыре таких участка (paqe frames) по 16 Кбайт были выделены, и их адреса стали использоваться для адресации дополнительной памяти, подключенной к системной магистрали. Таким образом общий объем ОП удалось увеличить на 64 Кбайта. Специальная программа (драйвер дополнительной памяти) “перехватывала” обращение к “окнам” ПЗУ и вместо них “подставляла” дополнительный модуль памяти (Expended Memory).

Дополнительная память не обязательно должна была иметь объем 64 Кбайта. Ее объем мог быть и большим (фирма IBM выпускала модули дополнительной памяти объемом 8 и 32 Мбайта). При этом драйвер дополнительной памяти делил ее на блоки по 16 Кбайт и “отображал” каждое окно UMB на один из блоков Expended Memory. Из-за этого память такого вида получила название отоброжаемой.

Но развитие персональных ЭВМ привело к необходимости более серьезной корректировки рабочей концепции. Поэтому в IBM AT с микропроцессором i80286 разрядность шины адреса увеличили до 24, что позволило увеличить ее объем до 16 Мбайт. В МП i80386 разрядность шины адреса и адресных регистров микропроцессора увеличена до 32, в результате чего допустимый объем ОП увеличился до 4 Гбайт.

Наряду с этим изменился принцип формирования абсолютного адреса ОП, в результате чего утрачена совместимость с программным обеспечением, разработанным для IBM PC XT.

Чтобы обеспечить совместимость AT с XT, было решено реализовать два режима работы микропроцессоров, имеющих номер, больший 80286: реальный и защищенный.

В реальном режиме дополнительные разряды шины адреса заблокированы, что обеспечивает совместимость с микропроцессором 18086 и позволяет использовать операционную систему MS DOS и программное обеспечение, разработанное для XT. Но при этом остается неиспользованной вся дополнительная память, находящаяся за пределами 1 Мбайта. В защищенном режиме применяется другой принцип формирования абсолютного адреса ОП, благодаря чему возможно использование всей имеющейся в наличии дополнительной (расширенной) памяти, но возникают трудности с использованием программного обеспечения, разработанным для MS DOS.

В IBM PC XT 20-битный адрес формировался из двух машинных слов: базового адреса сегмента (16 бит) и смещения (16 бит). Это было связано с тем, что вся ОП делилась на сегменты емкостью 64 Кбайта. Адресация байтов внутри сегмента начиналась с 0 и заканчивалась адресом FFFF. Внутрисегментный адрес байта называется смещением (т.е. смещением относительно начала сегмента). Начало же сегмента (т.е. его базовый 20-битный адрес) однозначно определялось 16-битовым адресом, который преобразовывался в 20-битный адрес дописыванием справа четырех нулей. В машинных командах абсолютный (физический) адрес задавался либо прямым указанием базового адреса сегмента и смещения (которые разделялись двоеточием, например, OA12:F4B2, где ОА12 - 20-битовый адрес начала сегмента; F4B2 -16-битное смещение внутри сегмента), либо по умолчанию (базовые адреса сегментов программы, данных, стека запоминаются в специальных регистрах микропроцессора), либо указанием регистра, в котором содержится необходимый базовый адрес (например, если регистр называется CS, то абсолютный адрес в машинной команде может быть задан в виде: CS:F4B2).

Начиная с МП i80386, благодаря увеличению длины всех регистров для смещений до 32 бит, реализована возможность работы “с плоской памятью”, не разделяемой на сегменты. Это допускает адресацию 232 байта или 4 Гбайга ОП.

Кроме того, в защищенном режиме (начиная с МП i80286) можно использовать и сегментированную память, но сегментные регистры не суммируются со смещением, а предназначены в качестве указателя на управляющие таблицы, содержащие необходимую информацию о сегментах. Поскольку длина записей в этих таблицах может превышать 16 бит, появляется возможность увеличить количество и размеры сегментов, а следовательно, и максимальный объем виртуальной памяти (так как 32-битовая шина адреса СМ ограничивает допустимый объем физической памяти, виртуальная память реализуется за счет замены страниц в физической ОП слотами, т.е. образами страниц, из внешнего ЗУ).

Желание использовать в реальном режиме всю фактически имеющуюся в наличии дополнительную память привело к созданию двух виртуальных режимов, один из которых стандарт EMS (Expended Memory Specifications), реализующий принцип банкирования дополнительной памяти. Вся дополнительная память делится на страницы (банки) емкостью по 16 Кбайт; выбираются четыре страницы и объявляются активными. Выбранные активные страницы отображаются на четыре окна UMB, теперь при обращении к одному из окон UMB вместо него подставляется отображенная на него страница дополнительной памяти. Поскольку любое окно UMB можно отобразить на любую страницу дополнительной памяти (объявив ее активной), то, изменяя отображение в процессе работы, можно использовать всю дополнительную память любого объема.

Стандарт EMS реализуется программным путем - с помощью драйвера дополнительной памяти, который “перехватывает” каждое обращение к окну, имеющемуся в адресном пространстве ПЗУ, и “подставляет” вместо ПЗУ соответствующий участок дополнительной памяти.

В соответствии с этим стандартом работают драйверы XMA2EMS.SYS, EMM386.SYS и дp.

Стандарт EMS несколько снижает производительность системы, но не накладывает никаких ограничений на размещение в дополнительной памяти программ и данных.

Другой виртуальный режим основан на том, что за счет разблокирования на время дополнительных (по сравнению с XT) линий шины адреса системной магистрали удается увеличить доступное MS DOS адресное пространство еще почти на 64 Кбайта, начиная с'адреса FFFFF (т.е. за пределами адресного пространства 1 Мбайт). Эта область адресного пространства (64 Мбайта, начиная с 1 Мбайта) получила название НМА (Hiqh Memory Area) -пая область памяти. Ее также можно использовать, работая в MS DOS, хранения и программ, и данных.

Блоки памяти, расположенные выше границы НМА, называются ЕМВ Extended Memory Blocks) - расширенные блоки памяти, хотя часто расширенной памятью (ЕМ - Extended Memory) называют всю дополнительную память, расположенную в адресном пространстве выше 1 Мбайта, иногда !ляя в ней область НМА.

Кратковременное разблокирование дополнительных линий шины адреса емной магистрали позволяет реализовать стандарт XMS (eXtended Memory ification), при котором разделенная на страницы ЕМ отображается на , но в этом стандарте программные модули могут располагаться только ИА, а остальная память может использоваться лишь для хранения данных. Стандарт XMS реализуется драйвером HIMEM.SYS, который способен гать с шиной адреса, имеющей до 32 линий.

Структура базового микропроцессора

Основу центрального процессора ПЭВМ составляет микропроцессор -обрабатывающее устройство, служащее для арифметических и логических преобразований данных, для организации обращения к ОП и ВнУ и для управления ходом вычислительного процесса. В настоящее время существует большое число разновидностей микропроцессоров, различающихся назначении, функциональными возможностями, структурой, исполнением. Чаще всего наиболее существенным, классификационным различием между ними является количество разрядов в обрабатываемой информационной единице:8-битовые, 16-битовые, 32-битовые и др.

К группе 8-битовых микропроцессоров относятся i8080, i8085 (с буквы i начинаются названия МП, выпускаемых фирмой Intel - INTegrated Electronics), Z80 (с буквы Z начинаются названия МП фирмы Zilog) и др. Наиболыпее распространение среди 16-битовых микропроцессоров поли i8086, i8088, 32-битовых - i80386, i80486, которые совместимы по идам и форматам данных снизу вверх. Эти микропроцессоры используются в различных модификациях ЮМ PC. Два из этих микропроцессоров: i8086 и i8088 по назначению и функционым возможностям одинаковы. Различаются они только разрядностью шины данных системной магистрали: МП i8086 имеет 16-битовую шину даных, а i8088 - 8-битовую. В связи с этим выборка команд и операндов из оперативной памяти производится за разное число машинных циклов. С точки зрения функциональных возможностей существенного значения эти различия не имеют, поэтому и упоминают о них, как правило, вместе: 8086/8088. Этот тип МП является базовым для IBM совместимых машин. Все последующие типы МП основываются на нем и лишь развивают его архитектуру.

МП 8086/8088 имеет базовую систему команд. В следующей модификации МП фирмы Intel - 80186 реализована расширенная система команд. Расширение системы команд продолжается во всех новых моделях, но кроме этого в каждой новой модели вводятся дополнительные архитектурные решения: в 80286 введены встроенный блок управления ОП, работающий в виртуальном режиме (что позволило увеличить предельно допустимый объем виртуальной памяти до 4 Гбайт при 16 Мбайт физической), и блоки, позволяющие реализовать мультизадачность: блок защиты ОП и блок проверки уровня привилегий, присваиваемых каждой задаче. Кроме того, во всех последующих моделях вводятся и совершенствуются средства, позволяющие повысить производительность МП: совершенствуются конвейер команд и встроенный блок управления ОП, вводятся микропрограммное управление операциями, прогнозирование переходов по командам условной передачи управления, скалярная архитектура ЦП (арифметический конвейер) и мультискалярная архитектура (несколько параллельно работающих арифметических конвейеров, одновременно выполняющих несколько машинных операций, благодаря чему появляется возможность за один такт МП выполнять более одной машинной операции). Начиная с 80486, в кристалле МП размещается арифметический сопроцессор для операций с плавающей точкой. Фирма Intel разработала специальный микропроцессор Over Drive, который предназначен для параллельной работы с основным микропроцессором (для этого на системной плате предусматривается специальное гнездо).

Все эти усовершенствования позволяют сделать персональную ЭВМ IBM PC мультипрограммной, многопользовательской (МП 80286 позволял работать с 10 терминалами; 80386 - с 60) и многозадачной. С помощью операционной системы стало возможным реализовать работу в режиме SVM (системы виртуальных машин), т.е. на одной ПЭВМ реализовать множество независимых виртуальных машин (МП 803 86 позволял в этом режиме реализовать работу до 60 пользователей, каждому из которых предоставлялась отдельная виртуальная ПЭВМ IBM PC на МП 8086).

Некоторые характеристики МП фирмы intel приведены в табл 5.1. В обозначениях микропроцессоров появились дополнительные элементы: буквы SL, SX, DX и цифры. Буквы обозначают:

SL - микропроцессор изготовлен для работы с пониженным потреблением энергии (питание на те или иные блоки МП подается только в те моменты, когда они включаются в работу, в результате снижается потребление энергии и увеличивается срок службы источников питания, сокращается выделение энергии в кристалле МП и снижается его температура, благодаря чему увеличивается срок службы микропроцессора);

SX - данный микропроцессор является переходным - длина машинного слова в нем осталась без изменения от предыдущей модели;

DX - длина машинного слова увеличена вдвое по сравнению с МП предыдущей модели.

Цифры обозначают, во сколько раз изменилась тактовая частота по сравнению с МП предыдущей модели. Иногда (при наличии модификаций) дополнительно указывается тактовая частота МП.

Разработан новый микропроцессор - Реntiun ММХ (MultiMedia Extention), в котором реализована архитектура вычислительных систем класса SIMD, введено 57 новых команд, необходимых для обработки аудио-, видео- и телекоммуникационной информации.

Таблица 5.1

Характеристики микропроцессоров фирмы Intel

| Наименование МП | Тактовая частота, Мгц | Индекс iCOMP | Разрядность ШД (внутренняя/ внешняя) | Адресуемая память/ разрядность ША | Сопроцессор | Снижение потребления энергии | Примечание |

| 8086 | | | 16/16 | 1 Мб/20 | | | 40000 транз |

| 8088 | | | 16/8 | l Мб/20 | | | |

| 80286 | | | 16/16 | 16 Мб/24 | | | 130000 трата |

| 80386SL | | | 16/16 | 16 Мб/24 | | Есть | |

| 80386SX | | | 32/32 | 16 Мб/24 | | | |

| 80386DX | | | 32/32 | 4 Г6/32 | | | |

| 80486SL | | | 32/32 . | 4 Г6/32 | Нет | Есть | |

| 80486SX | 25 | 100 | 32/32 | 4 Г6/32 | Нет | | |

| 80486SX2 | 40 | - | 32/32 | 4 Г6/32 | | | |

| 80486SX2 | 50 | 180 | 32/32 | 4 Г6/32 | | | |

| 80486DX | | | 32/32 | 4 Г6/32 | Встр. | | |

| 80486DX2 | 50 | 231 | 32/32 | 4 Г6/32 | Встр. | | 1,2 млн транз. |

| 80486DX2 | 66 | 297 | 32/32 | 4 Г6/32 | Встр. | | |

| 80486DX4 | 75 | 319 | 32/32 | 4 Г6/32 | Встр. | | |

| 80486DX4 | 100 | 435 | 32/32 | 4 Г6/32 | Встр. | | |

| Over Drive | | | 32/32 | 4 Г6/32 | Встр. | | Аналог 486DX2 |

| Pentium | 60 | 510 | 64,32/64 | 4 Г6/32 | Встр. | | 6,7 млн транз. |

| Pentium | 66 | 567 | 64,32/64 | 4 Г6/32 | Встр. | | |

| Pentium | 90 | 735 | 64,32/64 | 4 Г6/32 | Встр. | | |

| Pentium | 100 | 815 | 64,32/64 | 4 Г6/32 | Встр. | | |

| Pentium | 133 | - | 64,32/64 | 4 Г6/32 | Встр. | | |

| Pentium | 166 | | 64,32/64 | 4 Г6/32 | Встр. | | |

| Pentium Pro | о 150 | | | | | | |

| Pentium Pro | о 200 | | | | | | |

В персональных ЭВМ нашли применение не только микропроцессоры фирмы Intel. Крупнейшими производителями аналогов микропроцессорам Intel (клонов) являются фирмы Cyrix и AMD.

Фирма Cyrix выпускает микропроцессоры М-1 и М-2, аналогичные Pentium, но превосходящие его по производительности. Так, М-1 с тактовой частотой 150 МГц по производительности эквивалентен МП Pentium с тактовой частотой 200 МГц.

Фирма AMD, завоевавшая около 30% рынка МП в России, выпускает микропроцессоры К-5 и К-6, являющиеся соответственно аналогами Pentium и Pentium Pro.

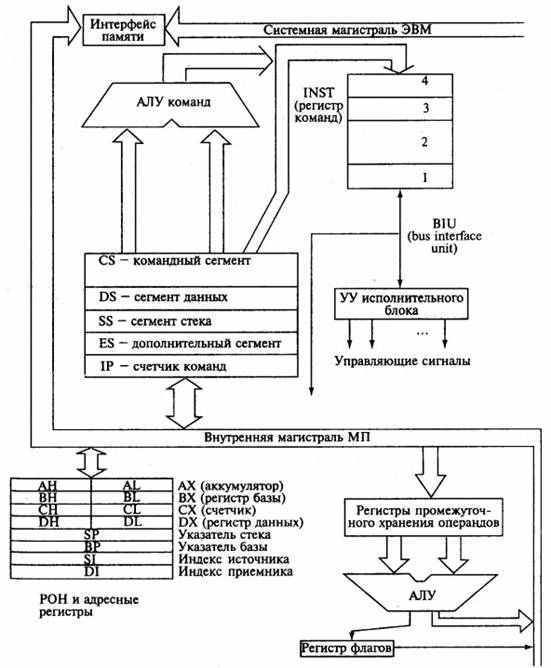

Структурная схема базовой модели МП фирмы Intel приведена на рис.5.5.

Рис.5.5. Структурная схема микропроцессора

Условно микропроцессор можно разделить на две части: исполнительный блок (Execution Unit - EU) и устройство сопряжения с системной магистралью (Bus Interface Unit - ВШ).

В исполнительном блоке находятся: арифметический блок и регистры общего назначения (РОН). Арифметический блок включает арифметико-логическое устройство, вспомогательные регистры для хранения операндов и регистр флагов.

Восемь регистров исполнительного блока МП (АХ, ВХ, СХ, DX, SP, ВР, SI, DI), имеющих длину, равную машинному слову, делятся на две группы. Первую группу составляют регистры общего назначения: АХ, ВХ, СХ и DX, каждый из которых представляет собой регистровую пару, составленную из двух регистров длиной в 0.5 машинного слова: аккумулятор, или регистр АХ состоит из регистров АН и AL. Регистр базы (Base Register) ВХ состоит из регистров ВН и BL. Счетчик (Count Register) СХ включает регистры СН и CL. Регистр данных (Data Register) DX содержит регистры DH и DL. Каждый из коротких регистров может использоваться самостоятельно или в составе регистровой пары. Условные названия (аккумулятор, регистр базы, счетчик, регистр данных) не ограничивают применения этих регистров - эти названия говорят о наиболее частом использовании их или об особенности использования того или иного регистра в той иди иной команде.

Вторую группу составляют адресные регистры SP, BP, SI и DI (в старших моделях количество адресных регистров увеличено). Эти регистры активно используются по функциональному назначению и в других целях их применятъ не рекомендуется. В качестве адресного регистра часто используется РОН ВХ. Программно допускается использование регистров BP, DI и SI в качестве регистров для хранения операндов, но отдельные байты в этих регистрах недоступны. Основное их назначение - хранить числовые значения, реализуемые при формировании адресов операндов.

Устройство сопряжения с системной магистралью содержит управляющие регистры, конвейер команд, АЛУ команд, устройство управления исполнительным блоком МП и интерфейс памяти (соединяющий внутреннюю магистраль МП с системной магистралью ПЭВМ).

Управляющие регистры BIU: CS (указатель командного сегмента), DS указатель сегмента данных), SS (указатель сегмента стека), ES (указатель дополнительного сегмента) и др. служат для определения физических адресов ОП - операндов и команд. Регистр IP (Instruction Pointer) является указателем адреса команды, которая будет выбираться в конвейер команд в качестве очередной команды (в отечественной литературе такое устройство называется счетчик команд). Конвейер команд МП хранит несколько команд, что позволяет при выполнении линейных программ совместить подготовку очередной команды с выполнением текущей.

К управляющим регистрам МП относится и регистр флагов, каждый разряд которого имеет строго определенное назначение. Обычно разряды регистра флагов устанавливаются аппаратно при выполнении очередной операции в зависимости от получаемого в АЛУ результата. При этом фиксируются такие свойства получаемого результата, как нулевой результат, отрицательное число, переполнение разрядной сетки АЛУ и т.д. Но некоторые разряды регистра флагов могут устанавливаться по специальным командам. Некоторые разряды имеют чисто служебное назначение (например, хранят разряд, (выпавший” из АЛУ во время сдвига) или являются резервными (т.е. не используются).

Все флаги младшего байта регистра устанавливаются арифметическими или логическими операциями МП. Все флаги старших байтов, за исключением флага переполнения, устанавливаются программным путем, для этого в МП имеются команды установки флагов (STC, STD, STI), сброса (CLC CLD, CLI), инвертирования (CMC).

Взаимодействие элементов при работе микропроцессора

Работой МП управляет программа, записанная в ОП ЭВМ. Адрес очередной команды хранится в счетчике команд IP (Instruction Pointer) и в одном из сегментных регистров, чаще всего в CS. Каждый из них в реальном режиме имеет длину 16 бит, тогда как физический адрес ОП должен иметь длину 20 бит. Несогласованность длины машинного слова (16 бит) и длины физического адреса ОП (20 бит) приводит к тому, что в командах невозможно указать физический адрес ОП - его приходится формировать, собирать из разных регистров МП в процессе работы.

В реальном режиме вся ОП делится на сегменты (длина сегмента - 64 Кбайта). Адрес ОП разделяется на две части: номер сегмента в ОП (база сегмента) и номер ячейки внутри данного сегмента (смещение относительно начала сегмента). Базовый адрес сегмента образуется добавлением к номеру сегмента справа четырех нулей. Поскольку последние четыре разряда абсолютного (физического) адреса сегмента всегда нулевые, сегмент может начинаться не с любой ячейки ОП, а только с “параграфа” - начала 16-байтного блока ОП. В структуре микропроцессора имеется несколько регистров сегментов, например в i8086 - четыре:

С S - программный сегмент;

DS - сегмент данных (информационный сегмент);

SS - стековый сегмент;

ES - расширенный сегмент (дополнительный сегмент данных).

Номер ячейки внутри сегмента (смещение) называется также исполнительным адресом. В большинстве случаев в адресной части команды указывается именно исполнительный адрес - номер сегмента чаще всего подразумевается по умолчанию. Однако допускается указание и полного адреса ОП в виде префиксной структуры: “сегмент: смещение”. Если сегмент в команде не указывается, значит, работа ведется внутри текущего сегмента (характер выполняемой работы и какой из сегментных регистров определяет текущую базу сегмента, зависят от вида выполняемой команды).

Номер сегмента так же, как и смещение, имеет длину 2 байта. При вычислении физического адреса ОП сегмент и смещение суммируются, но сегмент перед суммированием сдвигается влево на 4 бита. В результате суммирования образуется физический адрес ОП длиной 20 бит.

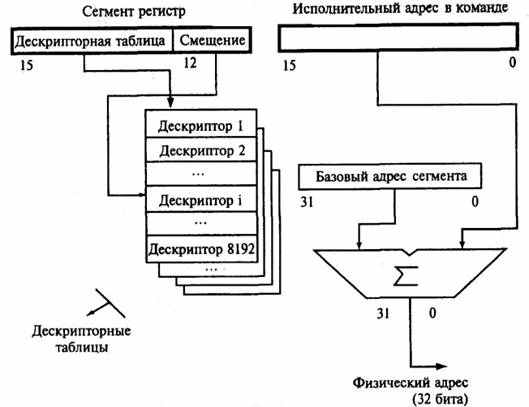

В защищенном режиме базовые адреса сегментов хранятся в дескрипторных таблицах и имеют длину 24 или 32 бита (в зависимости от типа МП). В сегментных же регистрах хранится селектор, содержащий номер дескрипторной таблицы и дескрипторное смещение, т.е. порядковый номер дескриптора (в котором и хранится базовый адрес сегмента) в данной дескрипторной таблице (рис.5.6).

Рис. 5.6. Формирование физического адреса ОП в защищенном режиме

Физический адрес очередной команды через внутреннюю магистраль МП и интерфейс памяти поступает на шину адреса системной магистрали. Одновременно из устройства управления (УУ) исполнительного блока на шину управления выдается команда (управляющий сигнал) в ОП, предписывающая выбрать число, находящееся по адресу, указанному в системной магистрали. Выбранное число, являющееся очередной командой, поступает из ОП через шину данных системной магистрали, интерфейс памяти, внутреннюю магистраль МП на регистр команд (INST).

Из команды в регистре команд выделяется код операции, который поступает в УУ исполнительного блока для выработки управляющих сигналов, настраивающих микропроцессор на выполнение требуемой операции.

В зависимости от используемого в команде режима адресации организуется выборка необходимых исходных данных.

Работа микропроцессора при выполнении программного прерывания

Программы-обработчики прерываний могут находиться в различных частях основной памяти (место их расположения в разных версиях операционной системы может быть различным). Для обеспечения совместимости программ под разными версиями DOS обращение к обработчикам прерываний осуществляется по их номерам.

Связь между номером прерывания и адресом основной памяти, соответствующим точке входа в обработчик прерывания, осуществляется через таблицу векторов прерываний, занимающую 1 Кбайт сегмента 0 основной памяти.

Поскольку адрес любого байта основной памяти определяется базовым адресом сегмента (2 байта) и смещением в сегменте (2 байта), вектор прерываний разделен на четверки байтов, имеющие структуру, показанную на рис.5.7.

| 1байт | 2 байта | 3 байта | 4 байта |

| Смещение | Сегмеит | ||

Рис. 5.7. Структура записи в векторе прерываний

Для получения адреса обработчика прерывания № nh необходимо:

по номеру прерывания определить адрес первого байта “четверки” в векторе прерываний (он равен п*4);

выбрать 4 байта из 0 сегмента основной памяти, начиная с байта 4nh;

два последних байта поместить в регистр CS;

два первых байта поместить в счетчик команд IP.

После этого начнет выполняться первая команда обработчика прерывания № nh.

Таблица векторов прерываний используется не только для хранения адресов обработчиков прерываний, но и для указания на места хранения в ОП служебной информации. Для этой цели служат векторы прерываний IDh, lEh, IFh, 41h, 43h, 46h, 4Ah. Так, вектор IDh содержит адрес таблицы параметров видеосистемы (а не обработчика прерывания); вектор lEh - таблицы параметров дискет; 1Fh - адрес знакогенератора адаптера CGA и т.д.

Команда ЮТ, кроме определения адреса обработчика прерывания, выполняет следующие действия:

• сохраняет в стеке часть слова состояния процессора:

(SP) <— (SP)-2

(вершина стека) <—— (регистр флагов)

(SP) <—— (SP)-2

(вершина стека) <—— (CS)

(SP) <—— (SP) – 2

(вершина стека) <—— (IP)

• сбрасывает флаги разрешения прерывания и трассировки:

(IF) <—— О

(TF) <—— О

• заносит адрес точки входа обработчика прерываний в регистры CS и IP:

(CS) <—— (номер_прерывания * 4 + 2)

(IP) <—— (номер_прерывания * 4)

Команда INT относится к парным командам - каждый обработчик прерывания заканчивается командой IRET (возврат из прерывания).

По команде IRЕТ (без параметров) выполняются следующие действия:

(IP) <—— (вершина стека)

(SP) <—— (SP)+2

(CS) <—— (вершина стека)

(SP) <—— (SP)+2

(регистр флагов) <—— (вершина стека)

(SP) <—— (SP)+2

Каждый обработчик прерываний BIOS и DOS может выполнять несколько различных функций. В команде INT никак не определяется, какую именно функцию должен выполнить обработчик прерываний. Поэтому перед обращением к команде INT в регистры микропроцессора должна быть занесена информация, определяющая, какую функцию необходимо выполнить.

Например, по команде INT 13h могут быть выполнены следующие функции:

00h - сброс дисковой системы;

0lh - определение состояния дисковой системы (успешное завершение, некорректная команда, не найдена адресная метка и т.д.);

02h - чтение секторов в основную память;

03h - запись секторов из основной памяти;

04h - контроль секторов (есть ошибка - нет ошибки);

05h- форматирование дорожки;

06h - для жесткого диска - форматирование дорожки с установкой флагов плохих секторов;

07h - для жесткого диска - форматирование диска, начиная с указанной

дорожки;

08h - определение типа и текущих параметров диска...

и т.д.

Нужно иметь в виду, что одни и те же номера функций могут обозначать разные операции для различных устройств; некоторые функции отсутствуют в ранних версиях операционной системы, а некоторые — претерпели изменения в последующих версиях.

При выполнении команды INT номер функции должен содержаться в регистре АН микропроцессора. Остальные регистры должны включать необходимые для этой функции параметры. Например, для функции 02h остальные регистры микропроцессора должны содержать:

AL - число читаемых секторов;

СН - номер дорожки, на которой расположены читаемые сектора;

CL - номер сектора;

DH - номер головки;

DL - номер дисковода;

ES:BX - адрес буфера для чтения.

В результате выполнения этой функции при возникновении ошибки флаг CF устанавливается в 1; в регистр AL заносится число считанных секторов, в регистр АН записывается код состояния, сформированный после окончания операции:

00 - успешное завершение;

01 - некорректная команда;

02 - адресная метка не найдена;

FF - сбой операции опроса (для жесткого диска).

Кроме команд INT и IRET в IBM PC, с прерываниями работают команды CLI (запрещение маскируемых прерываний) и STI (отмена запрета прерывания).