Д. Ю. Гольдберг, И. И. Шагурин, В. А

| Вид материала | Документы |

- Шагурин, М. Мокрецов, В. Ванюлин,, 313.64kb.

- Бюллетень новых поступлений в нб согу за 01. 01. 05. 05 2011, 388.67kb.

- И. И. Шагурин архитектура, программирование и применение, 883.66kb.

- Московский государственный инженерно-физический институт (технический университет), 947.05kb.

- Строительные нормы и правила инженерная защита территории от затопления, 848.03kb.

- И. И. Шагурин московский инженерно-физический институт ( государственный университет, 33.18kb.

Д.Ю. ГОЛЬДБЕРГ, И.И. ШАГУРИН, В.А. ШАЛТЫРЕВ

Московский инженерно-физический институт (государственный университет)

RTL-МОДЕЛЬ 32-РАЗРЯДНОГО МИКРОПРОЦЕССОРА

ДЛЯ СПЕЦИАЛЬНЫХ ПРИМЕНЕНИЙ

В работе описывается модель 32-разрядного микропроцессора. Представлена его общая структура, краткое описание набора команд и характеристики размещения на кристалле.

В настоящее время существует множество различных типов 32-разрядных микропроцессоров класса soft-core, реализующих различные системы команд. Однако в большинстве случаев наборы команд этих микропроцессоров унифицированы и для многих задач оказываются избыточными, а сами процессорные ядра достаточно сложны и занимают много места на кристалле СБИС или ПЛИС. Представленное процессорное ядро разрабатывалось для решения задач первичной инициализации входящих в состав систем на кристалле периферийных устройств и других блоков, а также дальнейшего управления ими в процессе обработки информации. При этом учитывалось, что создаваемый микропроцессор должен занимать минимум места на кристалле и выполнять при этом все необходимые операции, используемые при инициализации и последующем контроле за состоянием некоторых регистров периферийных устройств. Поскольку серьезной вычислительной нагрузки на процессорное ядро при выполнении подобных задач не предвидится, тактовая частота и производительность ядра могут быть минимальными. Подобный микропроцессор может быть использован при построении систем потоковой обработки данных, где все необходимые вычислительные операции выполняются аппаратно специальными блоками.

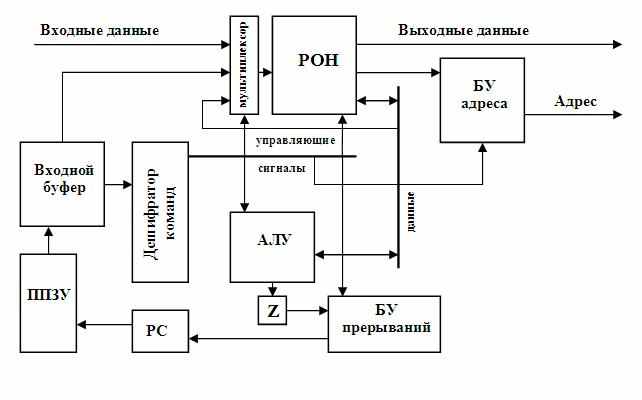

С учетом всех вышеизложенных требований для процессора была выбрана RISC-архитектура, количество регистров общего назначения ограничено четырьмя. Структура микроконтроллера изображена на рис. 1.

Все команды выполняются за один такт (если не требуется предварительная выборка из памяти команд константы, адреса или величины сдвига, в случае, если они указаны непосредственно в команде), АЛУ реализует только логические побитовые операции и логический сдвиг. Регистр флагов состоит из одного разряда – признака нуля. Память данных непосредственно в составе микропроцессора отсутствует, при необходимости можно использовать внешнюю память. Объем памяти команд строго не фиксирован, длина команды – от 8 бит. Обработку прерываний текущая версия микроконтроллера не поддерживает.

Рис. 1. Общая структура микропроцессора

Система команд представляет собой ограниченный набор из 17 команд, среди которых есть несколько логических побитовых операций, логический сдвиг вправо/влево, чтение и запись по внешнему адресу (адрес при этом может находиться в регистре или непосредственно в памяти команд), запись константы в регистр непосредственно из памяти команд. Также присутствуют команды безусловного перехода и ветвления при получении нулевого результата (адрес перехода может находиться в регистре или в памяти команд).

Модель микропроцессора успешно прошла тестирование, все команды и их последовательности выполняются корректно.

Размер процессорного ядра при его размещении его на ПЛИС составляет около 700 LUT, проводится оптимизация размещения ядра на кристалле.

Список литературы

- Шагурин И., Шалтырев В., Волов А. “Большие” FPGA как элементная база для реализации систем на кристалле. //Электронные компоненты, #5, 2006, c.83-88.