Проектирование и техническая реализация систем цос

| Вид материала | Документы |

СодержаниеDigital computing synthesizer for integrated performance Цифровой вычислительный синтезатор Цель работы |

- Проектирование и техническая реализация систем цос, 214.36kb.

- Проектирование и техническая реализация систем цос, 369.52kb.

- Проектирование и техническая реализация систем цос, 325.58kb.

- Описание содержания электронного умк дисциплины «Проектирование встроенных систем цос», 84.2kb.

- В. Р. Васильев, А. Г. Волобой, Н. И. Вьюкова,, 209.37kb.

- Методические указания к курсовому проектированию по дисциплине проектирование автоматизированных, 690.29kb.

- Учебно-методический комплекс по дисциплине дс. 01 -проектирование и надежность систем, 688.46kb.

- Учебно-методический комплекс дисциплины проектирование информационных систем Для студентов, 466.59kb.

- М. В. Красильникова проектирование информационных систем раздел: Теоретические основы, 1088.26kb.

- Рабочая программа учебной дисциплины (модуля) Программная реализация экспертных систем, 94.38kb.

Проектирование и техническая реализация систем ЦОС

- двоичный код синусоидального колебания при SEF 0=1, SEF 1=1.

14-ти разрядный сумматор фазового сдвига предназначен для формирования фазоманипулированных колебаний с дискретностью сдвига фазы выходного сигнала =3600/214.

D-триггер со схемой «исключающее или» обеспечивает синхронное изменение фазы выходного колебания на 1800.

Выходным сигналом ЦВС Q0... Q11 является 12-разрядный двоичный код амплитуды синтезируемого колебания.

Особенностью предлагаемого интегрального ЦВС является наличие в его составе (на рис.2 не показаны) устройств самотестирования, с помощью которых можно осуществлять автоматизированный контроль ЦВС на этапах его разработки и серийного производства.

В результате сопоставительного анализа различных методов самодиагностики цифровых схем для контроля ЦВС по рис. 2 был выбран метод сравнения с кодовым эталоном.

В качестве анализатора в блоке самотестирования применен параллельный многоканальный сигнатурный анализатор, реализованный на выходном регистре и дополнительно введенными в структуру ЦВС коммутаторе и схеме сравнения полученной сигнатуры с эталоном.

В качестве генератора тестовых воздействий было предложено использовать НК, что позволило существенно упростить задачу проектирования устройств самотестирования, сведя ее к выбору кодовых эталонов, т. е. констант подаваемых на вход НК. В результате моделирования структуры ЦВС по рис.2 было установлено, что для контроля «основного тракта» ЦВС (НК и ФП «фаза-синус») достаточно выбрать период пересчета НК равным 16384. Это позволяет проверить более 85% узлов ЦВС. Однако при этом останутся непроверенными: 10-ть младших разрядов НК, сумматор сдвига фазы и D-триггер сдвига фазы на 180 градусов. Для их проверки было предложено подать на вход НК и вход сумматора фазового сдвига чередующиеся коды: 0101...01 в течение первых 4-х тактов тестирования 1010...10 в течение вторых 4-х тактов и в последние четыре такта - код 1111...11.

Включение ЦВС в режим тестирования осуществляется схемой управления, которая выделяет последний такт тестирования для сравнения полученной сигнатуры с эталонной.

Для обеспечения оперативного доступа к внутренним блокам ЦВС организовано три сдвиговых регистра: на выходе блока НК, на выходе блока сумматора кода фазы и на выходе ФП «фаза-синус». При этом вход тестовых кодов предложено совместить с входом сдвига фазы на

, а выход результатов тестирования осуществлять через коммутатор.

, а выход результатов тестирования осуществлять через коммутатор.Результаты моделирования ЦВС в режиме самотестирования показали, что предложенный алгоритм тестирования обеспечивает функциональный контроль ЦВС в объеме 100 %.

Заключение

В работе делается попытка заинтересовать отечественную микроэлектронную промышленность (МЭП) производством конкурентоспособных с зарубежными аналогами [3] БИС ЦВС, выполненных на основе предложенных автором высокоэффективных схемотехнических решений построения быстродействующих синтезаторов частот данного класса.

По мнению автора появление первой отечественной БИС ЦВС позволит, во-первых заменить интегральные DDS иностранного производства в ряде РТС специального назначения, что обеспечит информационную защиту многих отечественных разработки, и во-вторых, стимулирует как разработчиков систем цифрового синтеза частот, так и широкий круг инженеров МЭП в создании, в том числе и на основе новых наносекундных технологий, серии отечественных БИС ЦВС, превосходящих лучшие мировые образцы интегральных DDS.

Литература

- Cooper H. Why complicate frequency Synthesis/ Electronic Design/1974, vol/22? №15. Р.80-84.

- В.С. Станков, Я.А. Измайлова Методы построения высокоэффективных структур вычислительных синтезаторов. Системы и средства сязи, телевидения и радиовещания. Выпуск 1,2. 2007г., стр. 41-47.

- Каталог фирмы Analog Devices. One Technology Way P.O. Box 9106 Norwood.

- Станков В.С., Брагина Я.А. Проектирование интегральных узлов вычислительных синтезаторов повышенного быстродействия. Проектирование и технология электронных средств. №1, 2006г., стр. 13-17

- Станков В.С., Брагина Я.А. Проектирование преобразователей «фаза-синус» для интегральных вычислительных синтезаторов частот. Проектирование и технология электронных средств. №3, 2006г., стр. 26-31

- V.S.Stankov. Method hightening working frequencies of digital computing synthesizers of frequencies and signals. Proceedings 1996 International Symposium 17-19 September 1996, Moscow, Russia, pp. 249...255.

- Курейчик В.М., Родзин С.И. Контролепригодное проектирование и самотестирование СБИС: проблемы и перспективы – М.: Радио и связь, 1994г., стр. 171…173.

DIGITAL COMPUTING SYNTHESIZER FOR INTEGRATED PERFORMANCE

Izmailova J.

FGUP "NPP" Polyot"

The major tendencies of development of perspective systems of communication and radio engineering systems (RES) as a whole are development of higher frequencies and transition to use of complex noiseproof signals. Last years realization of these tendencies to become technically probable due to use as sources of fluctuations precise highstable digital computing g synthesize (DCS).

DCS are peculiar high adaptability to manufacture, reliability, stability to influence destabilizing of the factors, small time of switching of frequencies at a continuity of a phase of formed fluctuations, ability of formation of complex signals, programming and good repeatability of parameters at duplicating, opportunity of realization in integrated performance in the form BIS.

However, for today one of lacks DCS is the rather low speed, which limits on the part of high frequencies a range synthesized DCS of fluctuations. The given lack essentially constrains application synthesizers of frequencies of the given class in perspective RES of a meter and decimeter range.

The synthesis high-speed DCS at a structural - schematic level is conducted on two basic directions.

First is a search of ways of increase of speed of functional units DCS: the accumulator of codes (AC), functional converter (FC) «phase- sine", digital-to-analog converter (DAC).

The second direction of synthesis high-speed DCS with extended in area of high frequencies by a range of synthesized fluctuations is based on creation of new structures synthesizers of the raised{*increased*} speed.

In this paper discuss t he question of creation competitive of able with foreign analogues high-speed BIS of DCS constructed on a method of parallel calculation of readout of synthesized fluctuation is offered in [1] with use schematic of the decisions of construction high-speed AC and FC «phase- sine" considered in works [2, 3].

To integrated performance the structure two-channel DCS of the increased quick-action with built-in by devices of testing and diagnostics allowing to ensure 100 % the functional control synthesizer at a stage of hisdevelopment and manufacture is offered.

The basic advantages of the offered structure integrated DCS are marked which, in opinion of the author, will allow to make given synthesizer at identical technology of manufacturing particularly capable with the best foreign analogues integrated DDS [4].

The literature

1. V.S.Stankov. Method hightening working frequencies of digital computing synthesizers of frequencies and signals. Proceedings 1996 International Symposium 17-19 September 1996, Moscow, Russia, pp. 249... 255.

2. Stankov V.S., Bragina J.А. Designing of converters «phase "- sine" for integrated computing synthesizers of frequencies. Designing and technology of electronic means. №4, 2006г., page 26-31.

3. Stankov V.S., Bragina J.А. Designing of integrated units computing synthesizers of the increased speed. Designing and technology of electronic means. №1, 2006г., page 13-17.

4. Catalogue of firm Analog Devices. One Techvology Way P.O. Box 9106 Norwood, MA 02062-9106 U.S.A. CD-DES-REF-2004.

ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР

Рябов И.В., Юрьев П.М.

Марийский государственный технический университет

В последние годы возрождается интерес к радиотехнологиям, бурно развиваются средства радиосвязи, радиолокации и навигации. Одним из основных функциональных узлов современных радиосистем являются синтезаторы частот, поэтому задача формирования высокостабильной сетки частот крайне актуальна, поскольку точность формирования колебаний обеспечивает высокие точностные характеристики РЭС.

Быстродействующие цифровые вычислительные синтезаторы (ЦВС) с тактовыми частотами выше 1 ГГц, малым шагом по частоте (доли Гц) и малым временем переключения с одной частоты на другую (десятки нс) на 90 % удовлетворят потребности радиотехнических систем различного назначения.

Такие достоинства ЦВС как технологичность, надежность, устойчивость к воздействию дестабилизирующих факторов, малое время переключения частот при непрерывности фазы формируемых колебаний, способность формирования сложных сигналов, возможность полной микроминиатюризации и программируемость параметров, хорошая повторяемость параметров при тиражировании позволяют существенно повысить технико-экономические характеристики РЭС.

Цель работы заключается в расширении функциональных возможностей цифровых вычислительных синтезаторов, повышении их быстродействия, снижении уровня фазовых и амплитудных шумов.

Разработанный ЦВС относится к электронно-вычислительной технике, предназначен для синтеза частотно - и фазомодулированных сигналов и может использоваться в радиолокации, навигации и адаптивных системах связи.

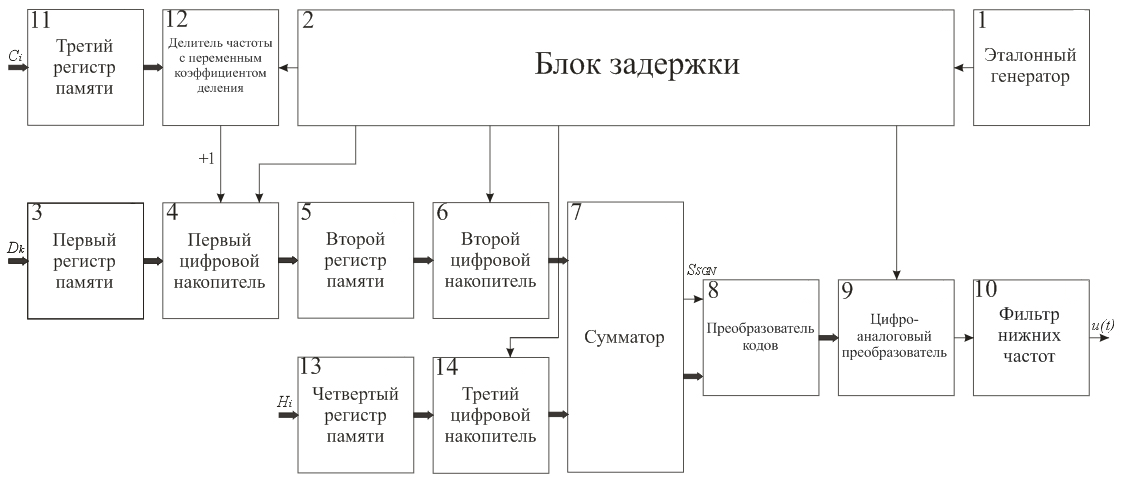

Рис. 1. Цифровой вычислительный синтезатор

Цифровая обработка сигналов и ее применение

Digital signal processing and its applications