Ведение два класса ЭВМ. Принцип действия ЭВМ

| Вид материала | Документы |

- 1 История развития компьютерной техники, поколения ЭВМ и их классификация Развитие, 1329.92kb.

- Малых ЭВМ (СМ эвм), 153.2kb.

- Программы общего назначения в решении медицинских задач. История развития средств вычислительной, 59.78kb.

- Рабочая программа по дисциплине "Схемотехника эвм" для специальности 22. 01 "эвм, комплексы,, 87.32kb.

- План 1 ЭВМ в управлении производством. 2 Гибкие производственные системы, 326.3kb.

- Программа дисциплины по кафедре Вычислительной техники Cхемотехника ЭВМ, 731.86kb.

- Программа по кафедре Вычислительной техники основы Cхемотехники ЭВМ, 492.8kb.

- Реферат на тему: "Внешние устройства персонального компьютера.", 375.1kb.

- Вопросы к экзамену по дисциплине «Микропроцессорные средства» для студентов 3-го курса, 16.07kb.

- Адресная структура команд микропроцессора и планирование ресурсов > 4 Виртуальная память, 3223.66kb.

Регистры общего назначения

31 23 15 7 0 16бит 32бита

| | | AH | AL | AX | EAX |

| | | DH | DL | DX | EDX |

| | | CH | CL | CX | ECX |

| | | BH | BL | BX | EBX |

| | | BP | | EBP | |

| | | SI | | ESI | |

| | | DI | | EDI | |

| | | SP | | ESP | |

Регистры сегментов

15 0

CS |

| SS |

| DS |

| ES |

| FS |

| GS |

Регистр состояния (регистр системных флагов) и управляющий регистр (указатель команд):

31 0

EFLAGS |

EIP |

Все регистры общего назначения могут использоваться для адресных вычислений и для получения результатов большинства арифметических и логических операций. Однако, некоторые команды используют фиксированные регистры для хранения операндов. Например, команды обработки строк используют в качестве операндов содержимое регистров ECX, ESI и EDI. Использование фиксированных регистров для некоторых операций позволяет более компактно кодировать набор команд. Следующие команды используют фиксированные регистры: умножение и деление с двойной точностью, ввод/вывод, обработка строк, перекодирование, цикл, сдвиг и циклический сдвиг, операции со стеком.

Регистры сегментов

Сегментирование позволяет разработчикам систем выбирать различные модели организации памяти.

Регистры сегментов содержат 16 разрядные селекторы сегментов, которые указывают на таблицу распределения памяти. Данная таблица содержит базовые адреса сегментов и другую информацию, регламентирующую доступ к памяти. При использовании плоской (несегментированной) модели все сегменты отображаются в единое пространство физической памяти.

В каждый момент времени непосредственно доступны не более 6 и сегментов. Их селекторы содержатся в регистрах CS, DS, SS, ES, FS и GS. Каждый регистр ассоциируется с сегментом, который соответствует одному из возможных типов доступа к памяти (коды, данные или стек).

Каждый регистр указывает на конкретный сегмент, используемый программой и имеющий определенный тип доступа.

Остальные сегменты могут быть использованы после загрузки соответствующих селекторов в сегментные регистры.

Сегмент, содержащий последовательность исполняемых команд, называется сегментом кода. Селектор этого сегмента содержится в регистре CS. Процессор i486 выбирает команды из этого сегмента, используя содержимое счетчика команд (регистр EIP) как относительный адрес внутри сегмента. Содержимое регистра CS изменяется в результате выполнения межсегментных команд управления потоком (CALL, IRET и JMP), прерываний и исключений.

Вызовы подпрограмм, записи параметров и активизация процедур обычно требует области памяти, резервируемой под стек. Все операции со стеком используют регистр SS при обращении к стеку. В отличие от регистра CS, регистр SS может быть загружен явно с помощью команды программы.

Остальные четыре регистра являются регистрами сегментов данных (DS, ES, FS и CS), каждый из которых используется текущей исполняемой программой. Доступ к четырем раздельным областям данных имеет целью повысить эффективность программ и безопасность доступа при обращении к различным типам структур данных. Например, имеет смысл разнести по разным сегментам собственные данные программного модуля, данные полученные из модуля более высокого уровня, динамически создаваемые структуры данных и данные, разделяемые текущим модулем с другими модулями. Механизм сегментации позволяет ограничить разрушения неправильно работающей неправильно работающей в следствии ошибки программы только теми сегментами, которые выделены текущей программе. Операнды, расположенные внутри сегмента данных адресуются указанием их смещения непосредственно внутри команды или в регистре общего назначения.

В некоторых случаях (при сложной структуре данных) может возникнуть необходимость иметь доступ более чем к четырем сегментам данных. Доступ к дополнительным сегментам осуществляется путем перезагрузки регистров DS, ES, FS и GS прикладной программой в процессе выполнения. Загрузка нужного сегментного регистра должна происходить до обращения к данным соответствующего сегмента.

При использовании регистров сегментов, с каждым выбранным сегментом связывается базовый адрес. При адресации единицы данных внутри сегмента, к базовому адресу сегмента добавляется 32 разрядный относительный адрес. Если сегмент выбран загрузкой селектора сегмента в регистр сегмента, то командам манипуляции данными нужен только этот относительный адрес.

Шина в вычислительной системе — это среда, через которую компоненты ЭВМ связываются друг с другом, т.е. это соответствующим образом выполненные линии связи. Большинство ЭВМ имеют шинную структуру, что позволяет существенно сократить общее число линий связи между блоками ЭВМ. Как показано на рис.1.3, шина ЭВМ функционально делится на три группы: адресную шину, шину данных и шину управления. Адресная шина переносит информацию о том, где искать инструкции (команды) или данные в памяти ЭВМ; шина данных переносит эти данные или инструкции для центрального процессора; шина управления обеспечивает передачу сигналов управления между процессором и подключенными к ЭВМ устройствами.

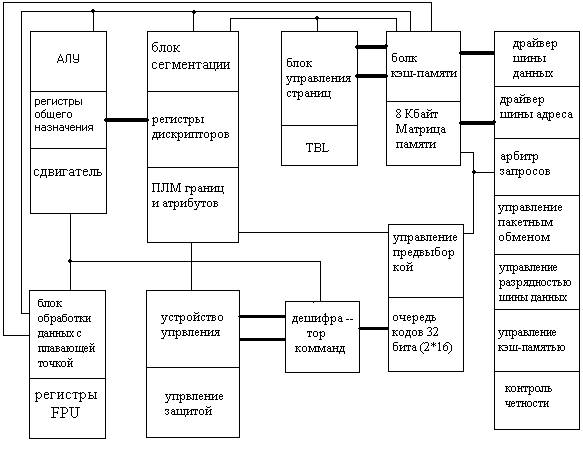

Тема 1.2. Структурная схема процессора, временные диаграммы, параметры.

Объединяя более, чем 3.1 миллион транзисторов на одной кремниевой подложке, 32-разрядный Pentium процессор характеризуется высокой производительностью с тактовой частотой 60 и 66 МГц. Его суперскалярная архитектура использует усовершенствованные способы проектирования, которые позволяют выполнять более, чем одну команду за один период тактовой частоты, в результате чего Pentium в состоянии выполнять огромное количество PC-совместимого программного обеспечения быстрее, чем любой другой микропроцессор. Кроме существующих наработок программного обеспечения, высокопроизводительный арифметический блок с плавающей запятой Pentium процессора обеспечивает увеличение вычислительной мощности до необходимой для использования недоступных ранее технических и научных приложений, первоначально предназначенных для платформ рабочих станций. Также, как локальные и глобальные сети продолжают вытеснять устаревшие иерархические сети, управляемые большими ЭВМ, преимущества мультипроцессорности и гибкость операционной системы Pentium процессора - идеал для Хост-компьютера для современных приложений клиент-серверов, применяемых в промышленности.

Поскольку Pentium процессор способен достигать уровня производительности равного или более высокого, чем современные рабочие станции высокого уровня, он обладает преимуществами, которых лишены обычные рабочие станции: полная совместимость с более, чем 50 000 программных приложений со стоимостью миллиарды долларов, которые были написаны под архитектуру фирмы INTEL. В дополнение, Pentium процессор позволяет использовать все основные операционные системы, которые доступны современным настольным персональным компьютерам, рабочим станциям и серверам, включая UNIX, Windows-NT, OS/2, Solaris и NEXTstep.

Pentium процессор. Технические нововведения.

Многочисленные нововведения - характерная особенность Pentium процессора в виде уникального сочетания высокой производительности, совместимости, интеграции данных и наращиваемости. Это включает:

- Суперскалярную архитектуру;

- Раздельное кэширование программного кода и данных;

- Блок предсказания правильного адреса перехода;

- Высокопроизводительный блок вычислений с плавающей запятой;

- Расширенную 64-битовую шину данных;

- Поддержку многопроцессорного режима работы;

- Средства задания размера страницы памяти;

- Средства обнаружения ошибок и функциональной избыточности;

- Управление производительностью;

- Наращиваемость с помощью Intel OverDrive процессора.

Суперскалярная архитектура Pentium процессора представляет собой совместимую только с INTEL двухконвейерную индустриальную архитектуру, позволяющую процессору достигать новых уровней производительности посредством выполнения более, чем одной команды за один период тактовой частоты. Термин "суперскалярная" обозначает микропроцессорную архитектуру, которая содержит более одного вычислительного блока. Эти вычислительные блоки, или конвейеры, являются узлами, где происходят все основные процессы обработки данных и команд.

Появление суперскалярной архитектуры Pentium процессора представляет собой естественное развитие предыдущего семейства процессоров с 32-битовой архитектурой фирмы INTEL. Например, процессор Intel486 способен выполнять несколько своих команд за один период тактовой частоты, однако предыдущие семейства процессоров фирмы INTEL требовали множество циклов тактовой частоты для выполнения одной команды.

Возможность выполнять множество команд за один период тактовой частоты существует благодаря тому, что Pentium процессор имеет два конвейера, которые могут выполнять две инструкции одновременно. Так же, как и Intel486 с одним конвейером, двойной конвейер Pentium процессора выполняет простую команду за пять этапов: предварительная подготовка, первое декодирование (декодирование команды), второе декодирование (генерация адреса), выполнение и обратная выгрузка. Это позволяет нескольким командам находиться в различных стадиях выполнения, увеличивая тем самым вычислительную производительность.

Каждый конвейер имеет свое арифметическо-логическое устройство (ALU), совокупность устройств генерации адреса и интерфейс кэширования данных. Так же как и процессор Intel486, Pentium процессор использует аппаратное выполнение команд, заменяющее множество микрокоманд, используемых в предыдущих семействах микропроцессоров. Эти инструкции включают загрузки, запоминания и простые операции АЛУ, которые могут выполняться аппаратными средствами процессора, без использования микрокода. Это повышает производительность без затрагивания совместимости. В случае выполнения более сложных команд, для дополнительного ускорения производительности выполнения расширенного микрокода Pentium процессора для выполнения команд используются обе конвейера суперскалярной архитектуры.

В результате этих архитектурных нововведений, по сравнению с предыдущими микропроцессорами, значительно большее количество команд может быть выполнено за одно и то же время.

Раздельное кэширование программного кода и данных.

Другое революционное важнейшее усовершенствование, реализованное в Pentium процессоре, это введение раздельного кэширования. Кэширование увеличивает производительность посредством активизации места временного хранения для часто используемого программного кода и данных, получаемых из быстрой памяти, заменяя по возможности обращение к внешней системной памяти для некоторых команд. Процессор Intel486, например, содержит один 8-KB блок встроенной кэш-памяти, используемой одновременно для кэширования программного кода и данных.

Проектировщики фирмы INTEL обошли это ограничение использованием дополнительного контура, выполненного на 3.1 миллионах транзисторов Pentium процессора (для сравнения, Intel486 содержит 1.2 миллиона транзисторов) создающих раздельное внутреннее кэширование программного кода и данных. Это улучшает производительность посредством исключения конфликтов на шине и делает двойное кэширование доступным чаще, чем это было возможно ранее. Например, во время фазы предварительной подготовки, используется код команды, полученный из КЭШа команд. В случае наличия одного блока кэш-памяти, возможен конфликт между процессом предварительной подготовки команды и доступом к данным. Выполнение раздельного кэширования для команд и данных исключает такие конфликты, давая возможность обеим командам выполняться одновременно. Кэш-память программного кода и данных Pentium процессора содержит по 8 KB информации каждая, и каждая организована как набор двухканального ассоциативного КЭШа - предназначенная для записи только предварительно просмотренного специфицированного 32-байтного сегмента, причем быстрее, чем внешний кэш. Все эти особенности расширения производительности потребовали использования 64-битовой внутренней шины данных, которая обеспечивает возможность двойного кэширования и суперскалярной конвейерной обработки одновременно с загрузкой следующих данных. Кэш данных имеет два интерфейса, по одному для каждого из конвейеров, что позволяет ему обеспечивать данными две отдельные инструкции в течение одного машинного цикла. После того, как данные достаются из КЭШа, они записываются в главную память в режиме обратной записи. Такая техника кэширования дает лучшую производительность, чем простое кэширование с непосредственной записью, при котором процессор записывает данные одновременно в кэш и основную память. Тем не менее, Pentium процессор способен динамически конфигурироваться для поддержки кэширования с непосредственной записью.

Таким образом, кэширование данных использует два различных великолепных решения: кэш с обратной записью и алгоритм, названный MESI (модификация, исключение, распределение, освобождение) протокол. Кэш с обратной записью позволяет записывать в кэш без обращения к основной памяти в отличие от используемого до этого непосредственного простого кэширования.

Эти решения увеличивают производительность посредством использования преобразованной шины и предупредительного исключения самого узкого места в системе. В свою очередь MESI-протокол позволяет данным в кэш-памяти и внешней памяти совпадать - великолепное решение в усовершенствованных мультипроцессорных системах, где различные процессоры могут использовать для работы одни и те же данные.

Рекомендуемый объем общей кэш-памяти для настольных систем, основанных на Pentium процессоре, равен 128-256 K, а для серверов - 256 K и выше.

Высокопроизводительный блок вычислений с плавающей запятой. Нарастающая волна 32-разрядных программных приложений включает много интенсивно вычисляющих, графически ориентированных программ, которые занимают много процессорных ресурсов на выполнение операций с плавающей запятой, обеспечивающих математические вычисления. Поскольку требования к персональным компьютерам со стороны программного обеспечения по вычислениям с плавающей запятой постоянно возрастают, удовлетворить эти потребности могут усовершенствования в микропроцессорной технологии. Процессор Intel486 DX, например, был первым микропроцессором, интегрированным на одной подложке с математическим сопроцессором. Предыдущие семейства процессоров фирмы INTEL, при необходимости использования вычислений с плавающей запятой, использовали внешний математический сопроцессор.

Pentium процессор позволяет выполнять математические вычисления на более высоком уровне благодаря использованию усовершенствованного встроенного блока вычислений с плавающей запятой, который включает восьми тактовый конвейер и аппаратно реализованные основные математические функции. Четырех тактовые конвейерные команды вычислений с плавающей запятой дополняют четырех тактовую целочисленную конвейеризацию. Большая часть команд вычислений с плавающей запятой могут выполняться в одном целочисленном конвейере, после чего подаются в конвейер вычислений с плавающей запятой. Обычные функции вычислений с плавающей запятой, такие как сложение, умножение и деление, реализованы аппаратно с целью ускорения вычислений.

В результате этих инноваций, Pentium процессор выполняет команды вычислений с плавающей запятой в пять раз быстрее, чем 33-МГц Intel486 DX, оптимизируя их для высокоскоростных численных вычислений, являющихся неотъемлемой частью таких усовершенствованных видеоприложений, как CAD и 3D-графика.

Pentium процессор на тактовой частоте 66 МГц работает как "числодробилка" с рейтингом 64.5 по тесту SPECint92, практически не уступая RISC-процессору Alpha компании Digital, но с тактовой частотой вдвое более высокой.

Общая производительность Pentium процессора превосходит в 6 раз 25 МГц Intel486 SX и в 2.6 раз - 66 МГц Intel486 DX2.

Индекс по рейтингу iCOMP для 66 МГц Pentium процессора, который выполняет 112 миллионов операций в секунду, составляет 567. Индекс по iCOMP (Intel COmparative Microprocessor Peformance) выполняет относительное сравнение производительности 32-битовых процессоров фирмы INTEL.

Расширенная 64-битовая шина данных.

Pentium процессор снаружи представляет собой 32-битовое устройство. Внешняя шина данных к памяти является 64-битовой, удваивая количество данных, передаваемых в течение одного шинного цикла. Pentium процессор поддерживает несколько типов шинных циклов, включая пакетный режим, в течение которого происходит порция данных из 256 бит в кэш данных и в течение одного шинного цикла.

Шина данных является главной магистралью, которая передает информацию между процессором и подсистемой памяти. Благодаря этой 64-битовой шине данных, Pentium процессор существенно повышает скорость передачи по сравнению с процессором Intel486 DX - 528 MB/сек для 66 МГц, по сравнению со 160 MB/сек для 50 МГц процессора Intel486 DX. Эта расширенная шина данных способствует высокоскоростным вычислениям благодаря поддержке одновременной подпитки командами и данными процессорного блока суперскалярных вычислений, благодаря чему достигается еще большая общая производительность Pentium процессора по сравнению с процессором Intel486 DX.

В общем, имея более широкую шину данных, Pentium процессор обеспечивает конвейеризацию шинных циклов, что способствует увеличению пропускной способности шины. Конвейеризация шинных циклов позволяет второму циклу стартовать раньше завершения выполнения первого цикла. Это дает подсистеме памяти больше времени для декодирования адреса, что позволяет использовать более медленные и менее дорогостоящие компоненты памяти, уменьшая в результате общую стоимость системы. Ускорение процессов чтения и записи, параллелилизм адреса и данных, а также декодирование в течение одного цикла - все вместе позволяет улучшить пропускную способность и повышает возможности системы.

Тема 1.3. Регистры управления памятью и адресацией.

Управляющие регистры CR0, CR1, CR2 и CR3. В большинстве систем загрузка управляющих регистров из прикладных программ невозможна (хотя в незащищенных системах такая загрузка разрешается). Прикладные программы имеют возможность считывать эти регистры для определения наличия математического сопроцессора. Некоторые разновидности команды MOV позволяют загружать управляющие регистры из регистров общего назначения, и наоборот. Например,

MOV EAX, CR0

MOV CR3, EBX

Регистр CR0 содержит системные управляющие флаги, которые управляют режимами или указывают на состояние процессора в целом, а не относительно выполнения конкретных задач. Программа не должна пытаться изменить состояние каких-либо битов в зарезервированных позициях. Эти зарезервированные биты всегда должны устанавливаться в то состояние, которое они имели ранее при считывании

Команда LMSW может модифицировать только младшие 16 битов регистра CR0.

PG (Подкачка страниц, бит 31)

Данный бит разрешает подкачку страниц, если он установлен, и запрещает ее, если он очищен.

Когда при подкачке страниц возникает исключение, в регистр CR2 помещается 32-разрядный линейный адрес, вызвавший это исключение.

При использовании подкачки страниц регистр CR3 содержит 20 наиболее значащих битов адреса страничного каталога (таблицы страниц первого уровня). Регистр CR3 также называется базовым регистром страничного каталога (PDBR). Отметим, что страничный каталог должен быть выровнен по границе страницы, поэтому 12 младших битов регистра игнорируются. В отличие от процессора 386 DX, процессор i486 назначает функции двум из этих битов. Это:

PCD (Запрещение кэширования на уровне страниц, бит 4 регистра CR3)

Состояние этого бита устанавливается в зависимости от состояния штырька PCD во время циклов шины, не работающих со страницами (например, циклов квитирования прерывания), когда подкачка страниц разрешена. Если подкачка страниц запрещена, то состояние этого бита устанавливается в любых циклах шины. Штырек PCD используется для управления работой внешнего КЭШа по циклам.

PWT (Прозрачность записи на уровне страниц, бит 3 регистра CR3)

Состояние этого бита устанавливается в зависимости от состояния штырька PWT во время циклов шины, не работающих со страницами (например, циклов квитирования прерывания), когда подкачка страниц разрешена. Если подкачка страниц запрещена, то состояние этого бита устанавливается в любых циклах шины. Штырек PWT используется для управления сквозной записью во внешний кэш по циклам.

CD (Запрещение кэширования, бит 30)

Данный бит разрешает внутреннее кэширование, если он очищен, и запрещает, если он установлен. Когда данный бит установлен, несовпадения КЭШа не вызывают заполнения строки КЭШа. Отметим, что совпадения КЭШа при этом не отменяются; для полного запрещения КЭШа он должен быть очищен.

NW (Сквозная запись не происходит, бит 29)

Данный бит разрешает сквозную запись и циклы аннулирования КЭШа, если он очищен, и запрещает циклы аннулирования и сквозную запись, ищущую совпадения КЭШа, если он установлен. Отмена сквозной записи позволяет хранить в КЭШе данные о состоянии.

AM (Маска выравнивания, бит 18)

Этот бит позволяет выполнять контроль выравнивания, если он установлен, и запрещает этот контроль, если он очищен. Контроль выравнивания выполняется только когда бит AM установлен, флаг AC установлен, а CLP имеет значение 3 (режим пользователя).

WP (Защита записи, бит 16)

Если этот бит установлен, то он защищает от записи страницы уровня пользователя при доступе в режиме супервизора. Если этот бит очищен, то страницы уровня пользователя, предназначенные только для чтения, могут быть затерты записью процессом супервизора. Это свойство может быть полезным для реализации метода "записи в копию" создания нового процесса (ветвления параллельных процессов), используемого некоторыми операционными системами (например, UNIX).

NE (Числовая ошибка, бит 5)

Этот бит разрешает стандартный механизм сообщений об ошибках при числовых операциях с плавающей точкой, если он установлен. Когда NE очищен, а вход IGNNE# активен, числовые ошибки игнорируются. Когда бит NE очищен, а вход IGNNE# не активен, числовая ошибка ведет к останову процессора и ожиданию прерывания. Прерывание генерируется при помощи штырька FERR#, формирующего ввод в контроллер прерываний (штырек FERR# эмулирует штырек ERROR# сопроцессоров 80287 и 387 DX). Бит NE, штырек IGNNE # и штырек FERR# используются внешними логическими схемами для реализации сообщений об ошибках в стиле PC.

ET (Тип расширения, бит 4)

Этот бит служит для того, чтобы указывать на поддержку команд математического сопроцессора 387 DX (Intel резервируется).

TS (Переключение задачи, бит 3)

Процессор устанавливает бит TS при каждом переключении задачи и проверяет его при интерпретации арифметических команд с плавающей точкой. Данный бит позволяет откладывать сохранение/восстановление числовых данных до их фактического использования. Команда CLTS очищает этот бит.

EM (Эмуляция, бит 2)

Если установлен один из битов, EM или TS, то выполнение команды WAIT или числовой команды генерирует исключение "сопроцессор недоступен". EM может быть установлен для получения исключения 7 для каждой команды WAIT или числовой команды.

MP (Математический сопроцессор присутствует, бит 1)

В случае процессоров 80286 и 386 DX бит MP управляет работой команды WAIT, используемой для синхронизации с сопроцессором. При выполнении программ на процессоре i486 данный бит должен быть установлен.

PE (Разрешение защиты, бит 0)

Установка бита PE разрешает защиту на уровне сегмента.

Регистры управления памятью

Четыре регистра процессора задают расположение структур данных, которые управляют организацией сегментированной памяти. Для загрузки и сохранения этих регистров имеются специальные команды. Регистры GDTR и IDTR могут быть загружены при помощи команд, извлекающих из памяти шести байтовые блоки. Регистры LDTR и TR могут быть загружены при помощи команд, принимающих в качестве операнда 16-битовый селектор сегмента. Затем остальные байты этих регистров загружаются процессором автоматически из дескриптора, на который ссылается переданный операнд.

Большинство систем защищает команды, загружающие регистры организации памяти от использования в прикладных программах (хотя возможна и система, не имеющая такого рода защиты).

Тема 1.4. Защищенный режим работы процессора.

Процессор Intel поддерживает два режима работы: реальный (Real Mode) и защищенный (Protected Mode).

Реальный режим (его еще называют режимом процессора 8086) это однопрограммный режим. Все свободное адресное пространство основной памяти распределяется работающему приложению. Принятая схема адресации ограничивает максимальный размер памяти пределом (1М + 64К - 16). Использование адресов, превышающих этот предел, возможно только косвенными методами через специализированные драйверы управления основной памятью. Особенности реального режима:

- адрес памяти, формируемый МП, является физическим адресом;

- все машинные команды системы команд разрешены для использования любой программой;

- объем адресуемой памяти не превышает 1М (исключение для 286/386/486/...: линия А20 дает дополнительно (64К -16) байт сверх 1М).

В защищенном режиме активизируются средства организации виртуальной памяти (внутреннее устройство управления памятью MMU).

Все инструкции разбиваются на привилегированные (только для ОС) и непривилегированные. Обеспечивается защита памяти, выделенной приложениям от несанкционированного доступа. Особенности защищенного режима:

- возможность непосредственной адресации памяти свыше 1 Мб;

- механизм виртуальной памяти (начиная с процессора 80386);

- аппаратная поддержка мультизадачности;

- использование виртуального режима процессора 8086

В защищенном режиме применяются две схемы адресации: одноступенчатая и двухступенчатая. В любом случае оперируют понятиями логического и физического адреса.

Физический адрес получается из логического при одноступенчатой схеме за одно преобразование, а при двухступенчатой - за два.

Логический адрес состоит из двух компонент: селектора и смещения. Селектор содержит индекс в таблице дескрипторов (описатель) сегментов. Селектор имеет следующую структуру:

F 3 2 1 0

| индекс в таблице | | | |

TI

RPL

- RPL - запрашиваемый уровень привилегий (2 бита);

- TI - индикатор таблицы: 0- поиск дескриптора выполняется в глобальной дескрипторной таблице GDT, 1 - поиск осуществляется в локальной дескрипторной таблице LDT.

GDT содержит дескрипторы сегментов ОС, а также адреса локальных таблиц. В системе может быть только одна глобальная таблица дескрипторов. Для адресации таблиц используются регистры GDTR и LDTR.

Формат GDTR:

27h 10h Fh 0

| базовый адрес GDT | Предел (размер GDT-1) |

32 бита 20 бит

Предел хранит протяженность таблицы. Поле предела позволяет контролировать обращение к таблице по индексу. Базовый адрес таблицы показывает реальный адрес расположения таблицы в основной памяти.

Регистр LDTR имеет аналогичную структуру. Регистр глобальной таблицы загружен постоянным содержимым, а значение локального регистра меняется при переключениях между локальными дескрипторной таблицами.

Записи с нулевым индексом в таблицах не используются.

P, A - предназначены для организации виртуальной памяти; А – бит обращения к сегменту, устанавливается в 1 для тех сегментов, к которым было обращение. сбрасывается в 0 процессором; Р - бит присутствия сегментов в памяти; DPL - двух битовое поле - номер кольца защиты сегмента (допустимый уровень привилегий), максимальная привилегия 0, минимальная - 3; С - бит подчинения. С=0 - сегмент может быть вызван только программой с не менее высоким приоритетом, чем у самого сегмента, С=1 сегмент может быть вызван любой программой, но уровень привилегий выставляется как у вызывающей программы; R - бит разрешения чтения. D - направление расширения сегмента. D=1 - сегмент расширяется вниз от старших адресов к младшим (стек), D=0 - наоборот; W - возможность записи в сегмент. W=1 - запись разрешена, W=0 -разрешено только чтение. С помощью этого бита можно установить дополнительный уровень защиты сегмента.

TYPE - тип того или иного сегмента. Код, который задан в этом поле, определяет назначение сегмента. Различают следующие виды:

- TSS - сегмент состояния задачи;

- LDT - сегмент локальной дескрипторной таблицы;

- вентиль вызова;

- вентиль прерывания;

- вентиль исключения.

Вентиль - точка входа или адрес в ту или иную функцию или подпрограмму. Исключение - особая ситуация, возникающая при исполнении приложения: деление на 0, исчезновение порядка, отсутствие страницы в основной памяти.

Тема 1.5. Дескрипторы, таблица дескрипторов.

Дескриптор сегмента представляет собой структуру данных в памяти, которая сообщает процессору размер и расположение в памяти сегмента, а также управляющую информацию и информацию о состоянии сегмента. Дескрипторы обычно создаются компиляторами, компоновщиками, загрузчиками или операционной системой, но не прикладными программами.

Все типы дескрипторов системы имеют один из этих форматов.

База: Определяет расположение сегмента в пределах 4 гигабайтного физического адресного пространства. Процессор располагает вместе три поля базового адреса, которые образуют одно 32-битовое значение. Значения базы сегмента должны быть выровнены по кратным 16 байтам адресам памяти, что позволяет программам максимизировать их быстродействие, выравнивая в свою очередь по кратным 16 байтам адресам памяти код/данные.

Бит грануляции: включает масштабирование поля границы масштабным коэффициентом 4096(2**12). Если этот бит очищен, то граница сегмента интерпретируется в блоках по 4Кб (т.е. в страницах). Отметим, что двенадцать наименее значащих битов адреса в случае, если используется масштабирование, не тестируются. Например, граница 0 при установленном бите грануляции дает допустимые смещения от 0 до 4095. Отметим также, что этот коэффициент действует только на значение поля Границы. Базовый адрес остается гранулированным по байтам.

Дескрипторы, используемые для сегментов кода и данных прикладных программ:

2 2 2 2 2 1 1 1 1 1 1 1 1 1 1

31 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 0

| BASE 31:24 | | DPL | TYPE | BASE 23:16 | |

| Базовый адрес 15:00 | Граница сегмента 15:00 | ||||

Дескрипторы, используемые для специальных системных сегментов:

2 2 2 2 2 1 1 1 1 1 1 1 1 1 1

31 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 0

| BASE 31:24 | | D P L | TYPE | BASE 23:16 | |

| Базовый адрес 15:00 | Граница сегмента 15:00 | ||||