Задание на курсовое проектирование по дисциплине «Схемотехника эвм»

| Вид материала | Документы |

СодержаниеОписания последовательных кодов В коде без возвращения к нулю с инверсией |

- Рабочая программа по дисциплине "Схемотехника эвм" для специальности 22. 01 "эвм, комплексы,, 87.32kb.

- Задание на проектирование Ф. И. О. стдуента гр. Ем 042, 16.64kb.

- Методические указания для проведения практических занятий и выполнения курсового проекта, 1404.08kb.

- Программа дисциплины по кафедре Вычислительной техники Cхемотехника ЭВМ, 731.86kb.

- Литература Саньков В. М., Кержиманов Е. С., Слободкин В. А. Курсовое и дипломное проектирование, 13.31kb.

- Курсовой проект по дисциплине "Схемотехника эвм", 121.85kb.

- Учебно-методический комплекс по дисциплине схемотехника ЭВМ (название), 505.95kb.

- Задание на курсовое проектирование Общая характеристика объекта автоматизации > Анализ, 57.75kb.

- Курс Семестр Нагрузка в семестре Курсовое проектирование, 86.23kb.

- Кафедра Вычислительной Техники проектирование дискретного устройства методические указания, 224.3kb.

Задание на курсовое проектирование по дисциплине «Схемотехника ЭВМ»

Разработать принципиальную схему устройства для параллельного суммирования двух двоичных чисел на ИС заданной серии (см. табл. 2). Числа по модулю меньше единицы, поступают в прямом коде, форма представления с фиксированной точкой. Последовательность поступления разрядов при последовательном коде приведена в табл. 1.

Таблица №1

| Назначение разрядов | Контрольный разряд | Информационные разряды | Знаковый разряд | ||||||

| Младший бит | . | Старший бит | |||||||

| Тактовый интервал | t9 | t8 | t7 | t6 | t5 | t4 | t3 | t2 | t1 |

Числа на суммирование поступают последовательно друг за другом. Результат выдаётся после завершения процесса суммирования.

При суммировании использовать инверсный код, заменяющий вычитание суммированием, указанный в варианте задания (см. табл. 2).

В разработанной схеме предусмотреть контроль переполнения разрядной сетки; при переполнении должен выдаваться сигнал.

Предусмотреть контроль безошибочности приёма согласно варианту задания. При обнаружении ошибки выдаётся сигнал передающему устройству, при этом суммирование не выполняется.

При передаче от источника числа сопровождаются синхронизирующими сигналами для каждого бита, поступающие только во время передачи. Синхросигналы поступают по специальной линии.

В вариантах задания, где числа на вход поступают последовательно, предусмотреть оптоэлектронную развязку. Уровни логического нуля и единицы сигналов последовательного кода приведены далее при описании используемых в задании последовательных кодов.

При приёме параллельным кодом используется ТТЛ – уровни логического нуля и единицы; код числа сопровождается синхросигналом.

В вариантах заданий с выдачей результата суммирования последовательным кодом предусмотреть выдачу синхросигналов, сопровождающих последовательный код.

Студент выполняет вариант задания из табл. 1 согласно своему порядковому номеру в журнале.

Таблица №1

| Номер варианта | Серия ИС | Суммирование осуществляется | Числа поступающие | Использовать метод контроля | Результат выдать |

| 1 | К155 | В дополнительном коде | В последовательном коде без возвращения к нулю с синхронизацией | Контроль по нечету входного кода, формирование контрольного разряда в выходном коде | Прямым параллельным кодом в уровне ТТЛ с 3 состояниями выхода |

| 2 | К530 | В обратном коде | |||

| 3 | К531 | В модифицированном дополнительном коде | |||

| 4 | К533 | В модифицированном обратном коде | |||

| 5 | К555 | В дополнительном коде | |||

| 6 | К1531 | В обратном коде | |||

| 7 | К1533 | В модифицированном дополнительном коде | |||

| 8 | К155 | В модифицированном дополнительном коде | В последовательном коде без возвращения к нулю с инверсией (синхронный) | ||

| 9 | К530 | В модифицированном обратном коде | |||

| 10 | К531 | В дополнительном коде | |||

| 11 | К533 | В обратном коде | |||

| 12 | К555 | В модифицированном дополнительном коде | |||

| 13 | К1531 | В модифицированном обратном коде | |||

| 14 | К1533 | В дополнительном коде | |||

| 15 | К155 | В обратном коде | В параллельном коде с синхросигналом | Контроль по нечету входного кода, формирование контрольного разряда в выходном коде | Последовательным кодом без возвращения к нулю с синхросигналом |

| 14 | К530 | В модифицированном дополнительном коде | |||

| 15 | К531 | В модифицированном обратном коде | |||

| 16 | К533 | В дополнительном коде | |||

| 17 | К555 | В обратном коде | Последовательным кодом без возвращения к нулю с инверсией (синхронный) | ||

| 18 | К1531 | В модифицированном дополнительном коде | |||

| 19 | К1533 | В модифицированном обратном коде | |||

| 20 | К530 | В дополнительном коде | |||

| 21 | К531 | В обратном коде |

Содержание расчётно-пояснительной записки

- Словесное описание проектируемой схемы.

- Функциональная схема и описание её работы с использованием временных диаграмм.

- Необходимые расчёты элементов принципиальной схемы.

- Принципиальная схема, оформленная в соответствии с ЕСКД со спецификацией.

- Требования к источнику питания для разработанной схемы.

Описания последовательных кодов

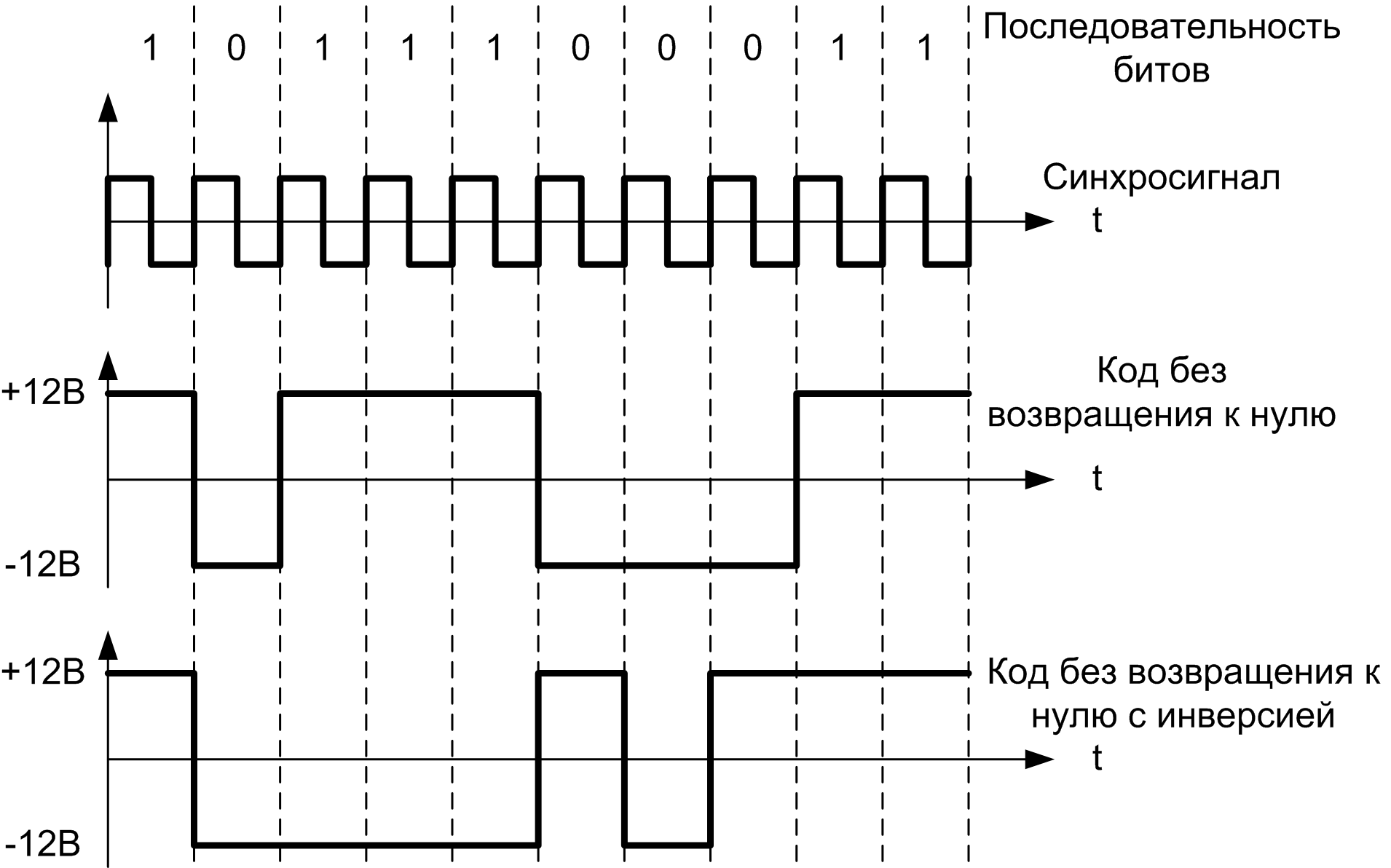

Код без возвращения к нулю отображает последовательность двоичных битов последовательностью уровней напряжения, постоянных на интервале передаваемого двоичного разряда.

В коде без возвращения к нулю с инверсией логическая единица передаётся отсутствием изменения уровня предшествующего бита, а логический ноль - инверсией этого уровня. Таким образом «1» и «0» в этом коде могут быть представлены в одной последовательности как низким, так и высоким уровнями напряжения, причём длинная последовательность «1» образует постоянный уровень, а длительная последовательность «0» - биполярный периодический сигнал.

Рекомендуемые источники

- Степанян, А. А. Цифровые вычислительные машины / А. А. Степанян. – Куйбышев : Книжное изд-во, 1966. – 191 с.

- Потемкин, Игорь Семенович. Функциональные узлы цифровой автоматики / И. С. Потемкин. — М. : Энергоатомиздат, 1988. — 320 с.

- Иванов, Владимир Иванович. Полупроводниковые оптоэлектронные приборы : Справочник / В. И. Иванов, А. И. Аксенов, А. М. Юшин. — 2-е изд., перераб. и доп. — М. : Энергоатомиздат, 1988. — 446 с.

- Цифровые интегральные микросхемы : Справочник / П. П. Мальцев, Н. С. Долидзе, М. И. Критенко, С. Н. Пономарев. — М. : Радио и связь, 1994. — 240 с.

- Шило, Валерий Леонидович. Популярные микросхемы ТТЛ : Серии: КР 1533, КР 1531, К 531, К 555, К 155 / В. Л. Шило. — М. : Аргус, 1993. — 64 с.